VLSI Physical Design Automation Detailed Routing I Prof

- Slides: 31

VLSI Physical Design Automation Detailed Routing (I) Prof. David Pan dpan@ece. utexas. edu Office: ACES 5. 434 11/1/2020 1

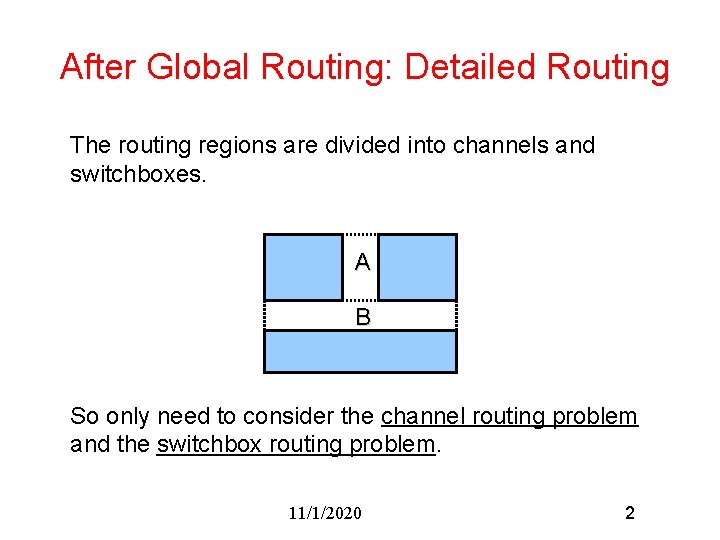

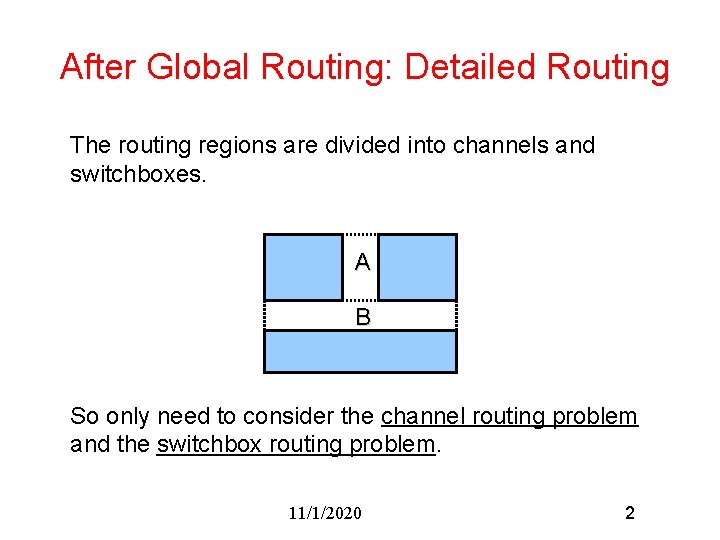

After Global Routing: Detailed Routing The routing regions are divided into channels and switchboxes. A B So only need to consider the channel routing problem and the switchbox routing problem. 11/1/2020 2

Channel Routing for Different Styles • For Gate-array design, channel widths are fixed. The goal is to finish routing of all the nets. • For Standard-cell and Full-custom design, channels are expandable. The goal is to route all nets using the minimum channel width. • We will consider the case when the channels are expandable. 11/1/2020 3

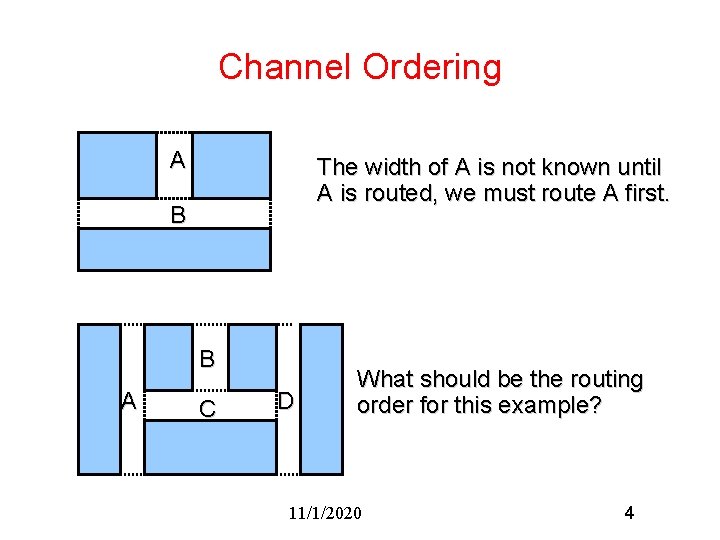

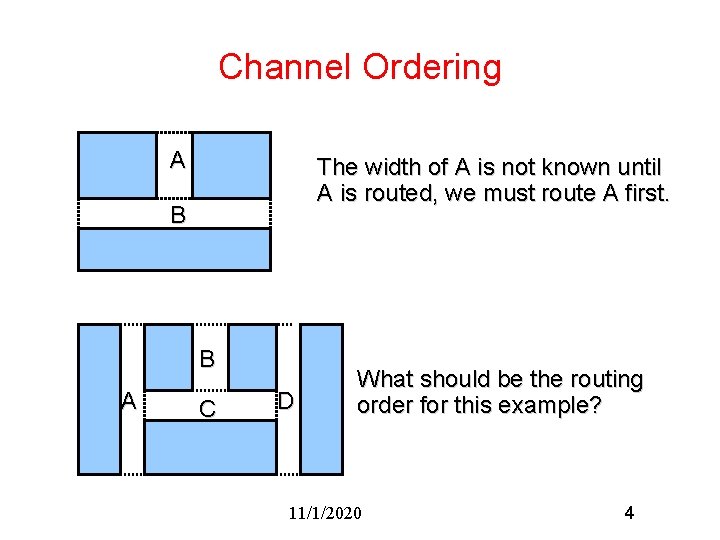

Channel Ordering A The width of A is not known until A is routed, we must route A first. B B A C D What should be the routing order for this example? 11/1/2020 4

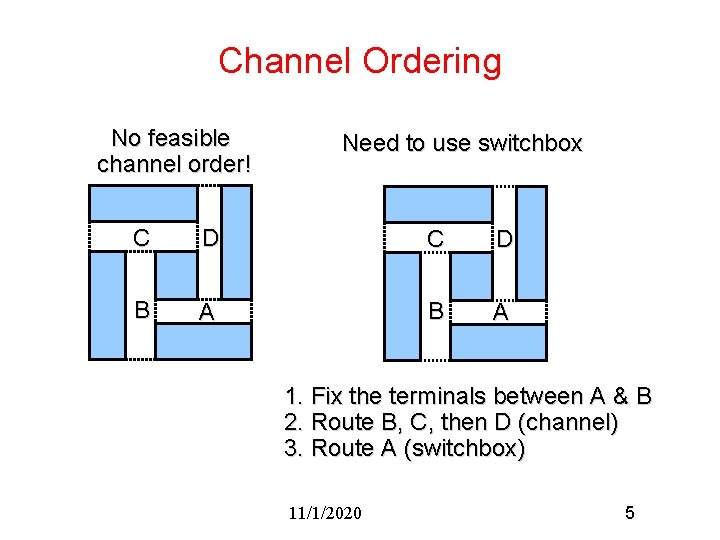

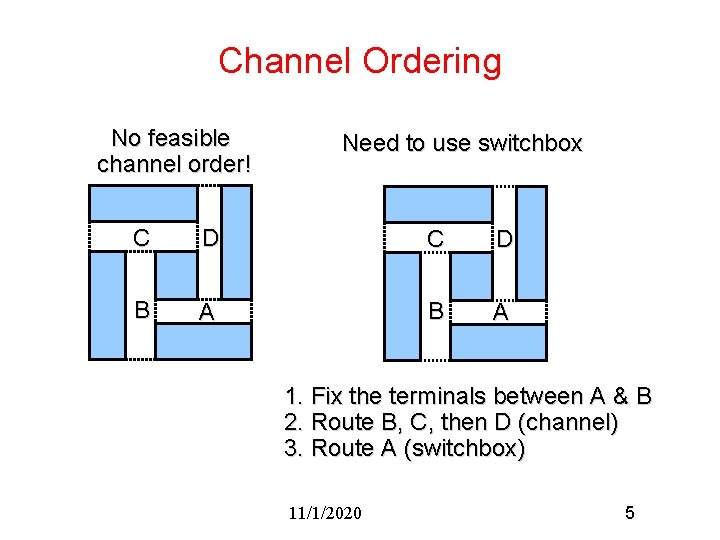

Channel Ordering No feasible channel order! Need to use switchbox C D B A 1. Fix the terminals between A & B 2. Route B, C, then D (channel) 3. Route A (switchbox) 11/1/2020 5

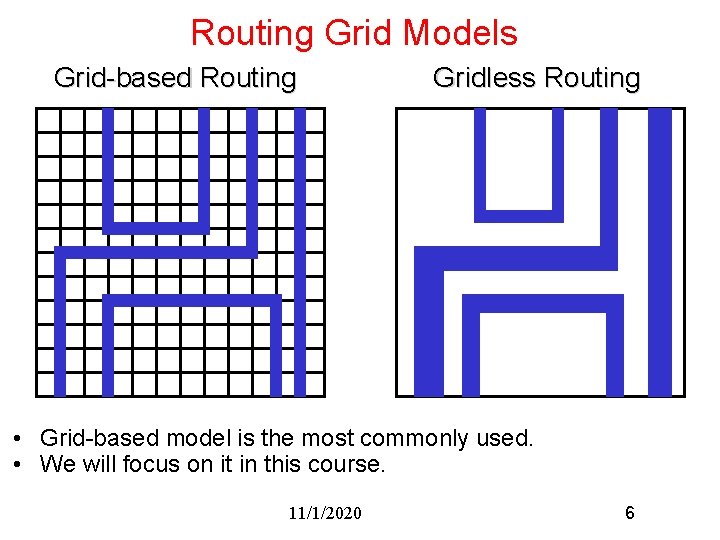

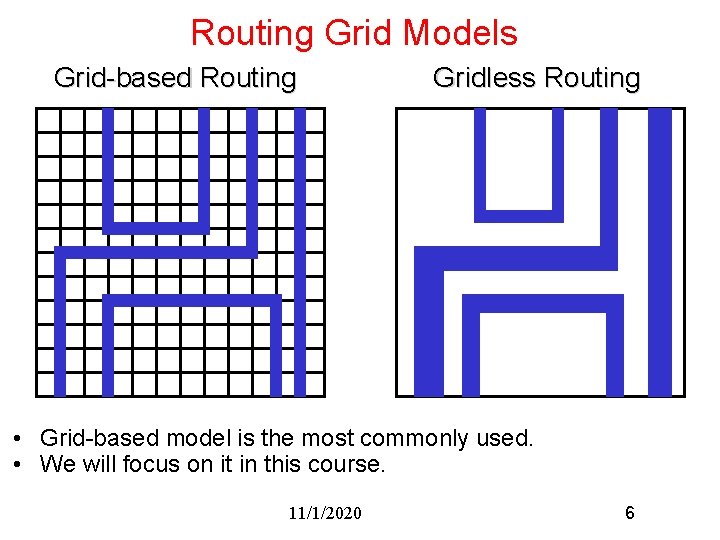

Routing Grid Models Grid-based Routing Gridless Routing • Grid-based model is the most commonly used. • We will focus on it in this course. 11/1/2020 6

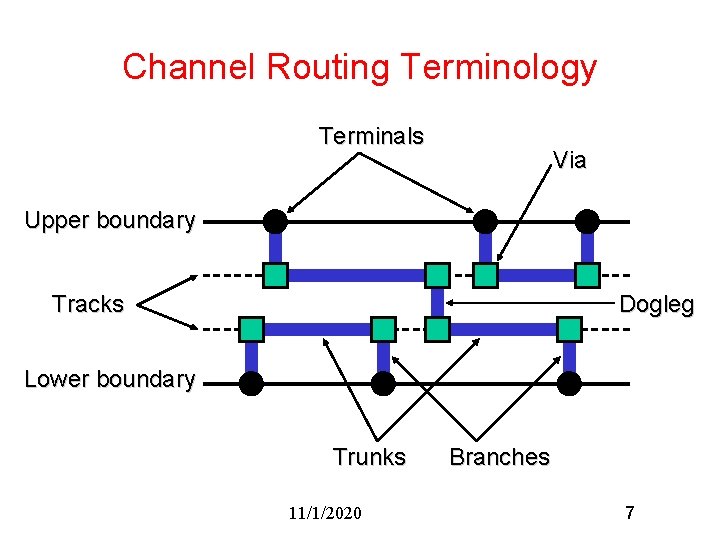

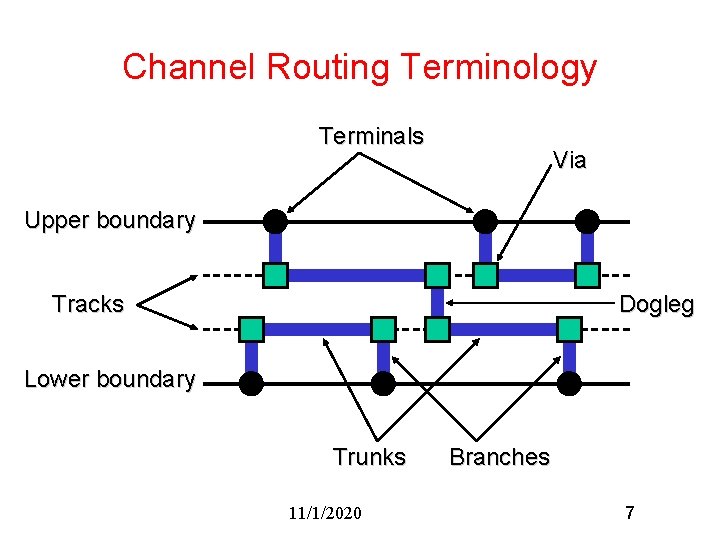

Channel Routing Terminology Terminals Via Upper boundary Tracks Dogleg Lower boundary Trunks 11/1/2020 Branches 7

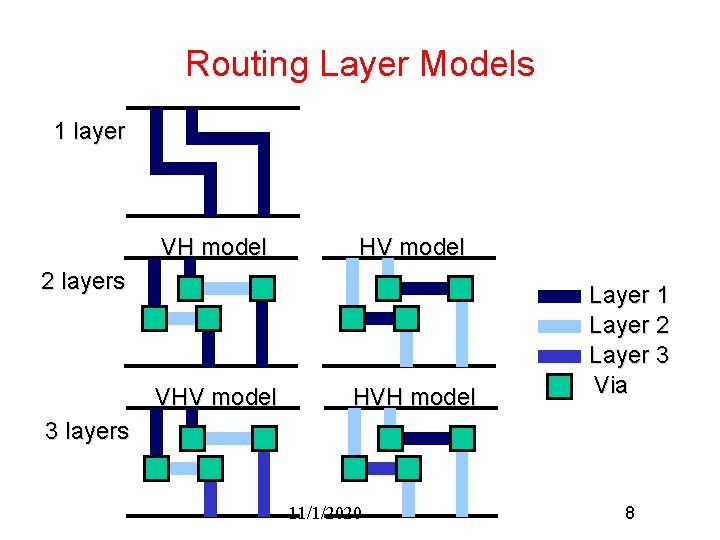

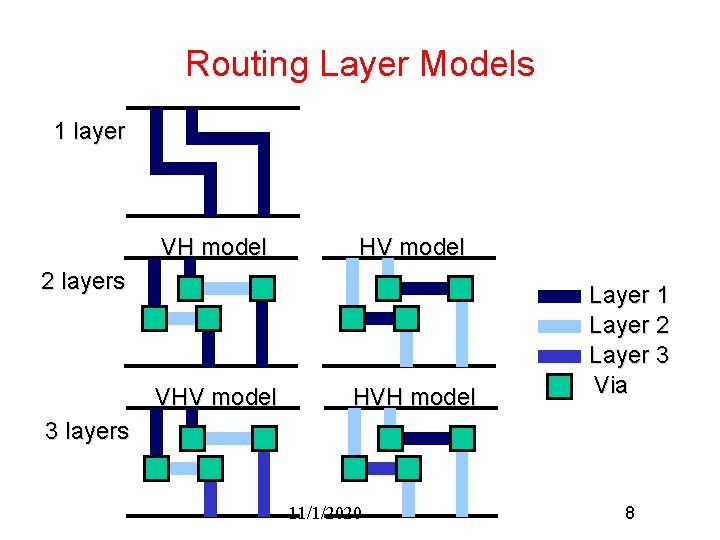

Routing Layer Models 1 layer VH model HV model 2 layers VHV model HVH model Layer 1 Layer 2 Layer 3 Via 3 layers 11/1/2020 8

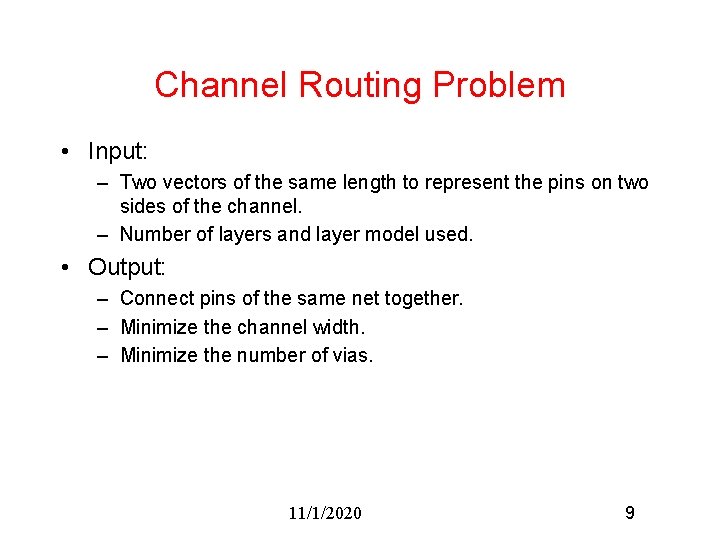

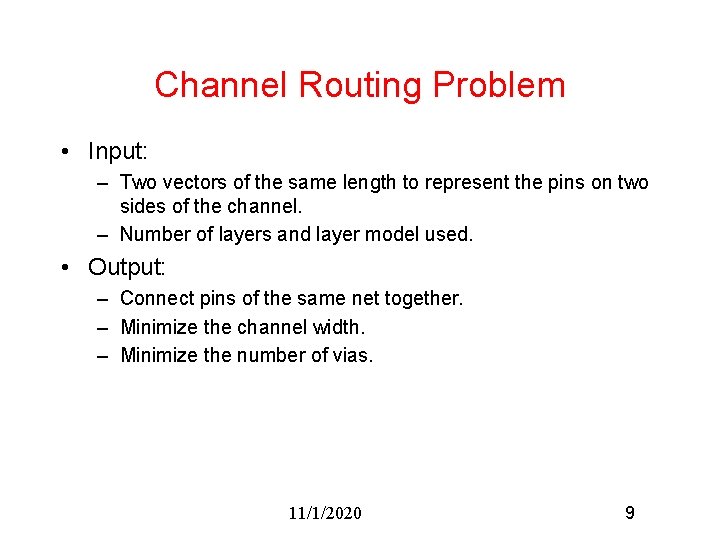

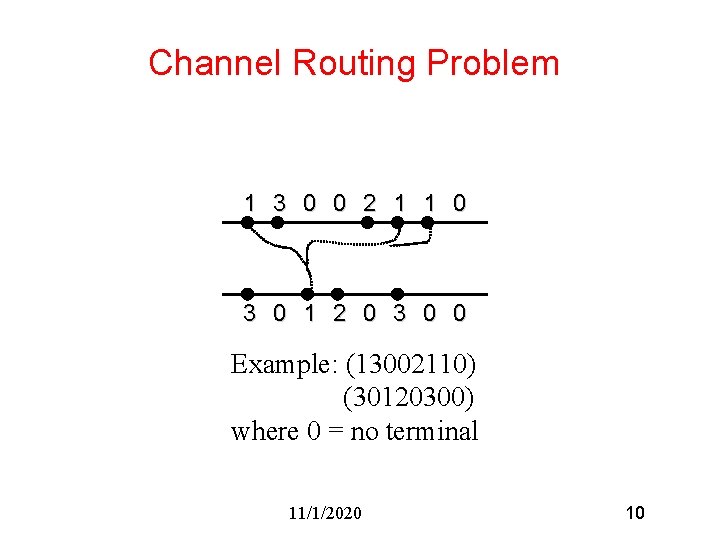

Channel Routing Problem • Input: – Two vectors of the same length to represent the pins on two sides of the channel. – Number of layers and layer model used. • Output: – Connect pins of the same net together. – Minimize the channel width. – Minimize the number of vias. 11/1/2020 9

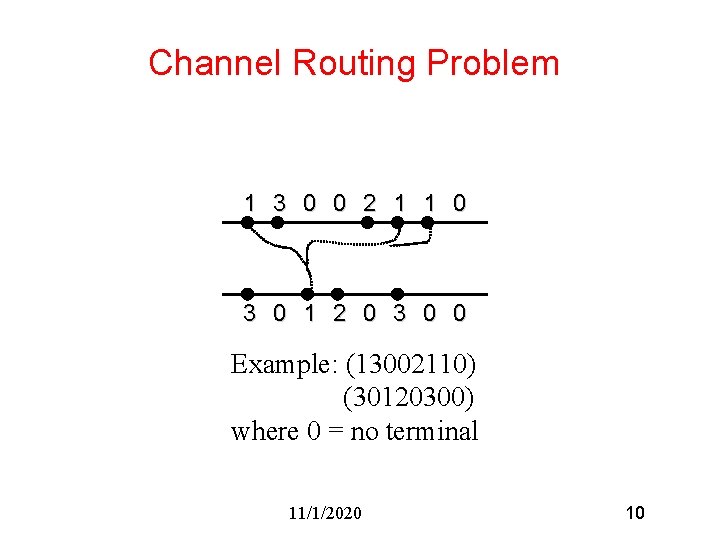

Channel Routing Problem 1 3 0 0 2 1 1 0 3 0 1 2 0 3 0 0 Example: (13002110) (30120300) where 0 = no terminal 11/1/2020 10

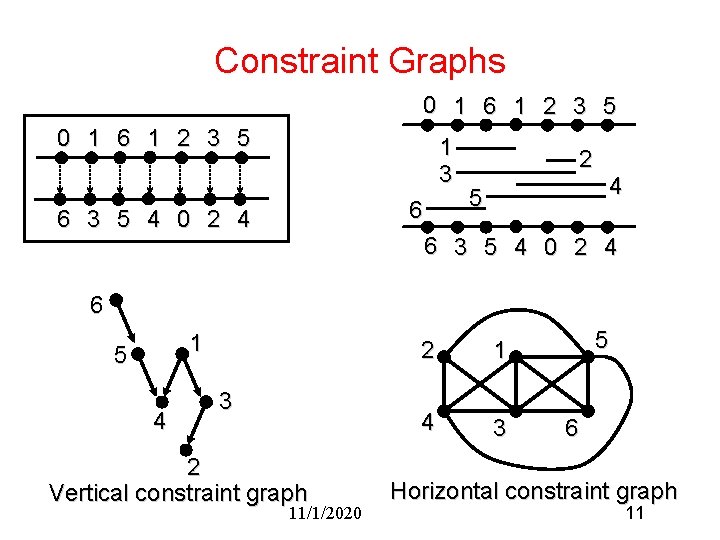

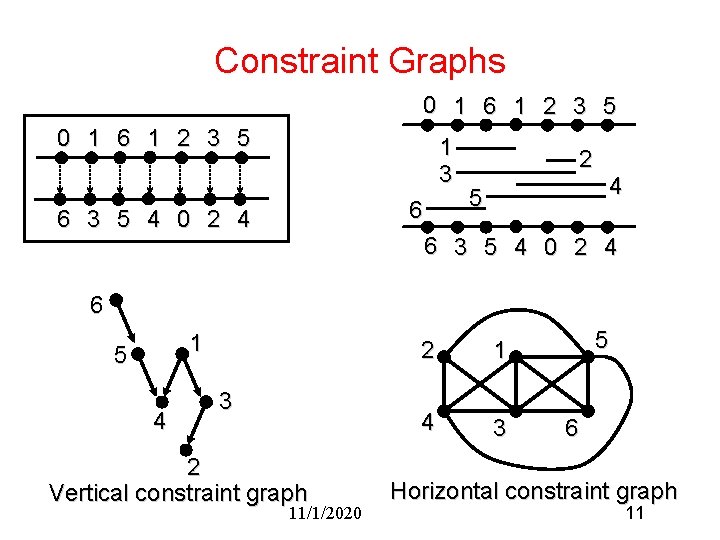

Constraint Graphs 0 1 6 1 2 3 5 1 3 6 6 3 5 4 0 2 4 2 5 4 6 3 5 4 0 2 4 6 1 5 4 3 2 Vertical constraint graph 11/1/2020 2 1 4 3 5 6 Horizontal constraint graph 11

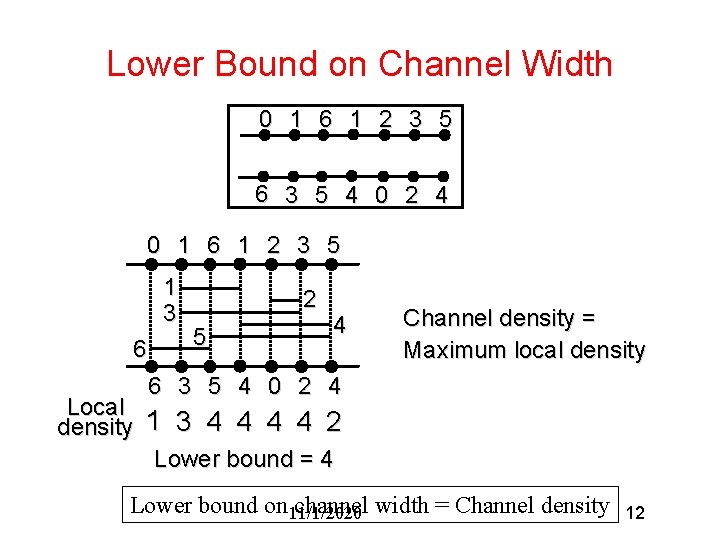

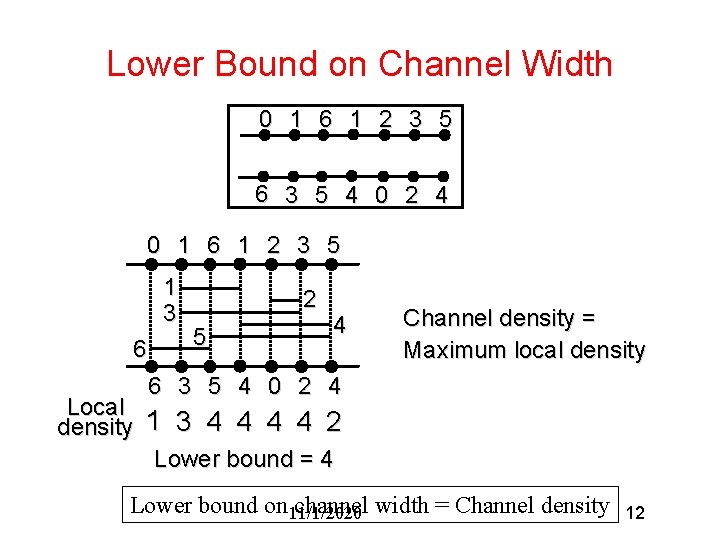

Lower Bound on Channel Width 0 1 6 1 2 3 5 6 3 5 4 0 2 4 0 1 6 1 2 3 5 1 3 6 2 5 4 Channel density = Maximum local density 6 3 5 4 0 2 4 Local density 1 3 4 4 2 Lower bound = 4 Lower bound on 11/1/2020 channel width = Channel density 12

Left-edge Channel Routing Algorithm “Wire Routing by Optimizing Channel Assignment within Large Apertures”, A. Hashimoto and J. Stevens, DAC 1971, pages 155 -169. 11/1/2020 13

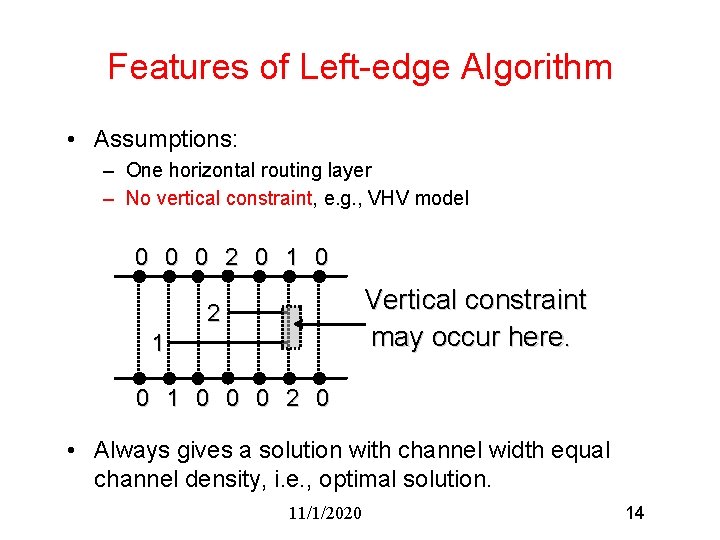

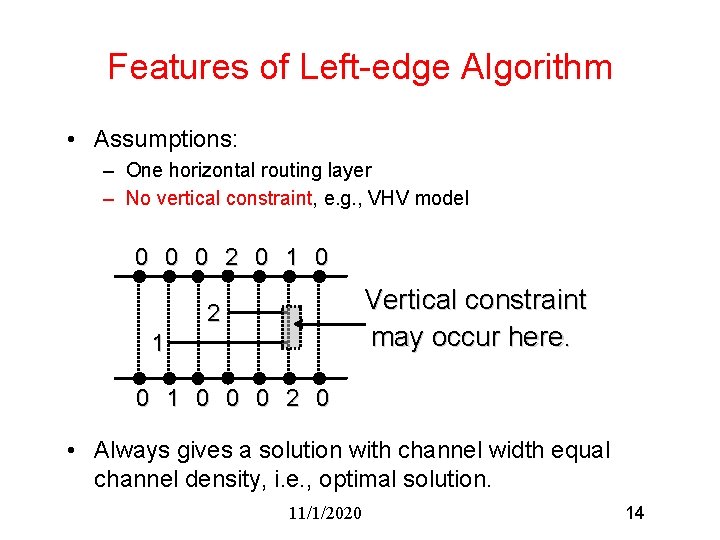

Features of Left-edge Algorithm • Assumptions: – One horizontal routing layer – No vertical constraint, e. g. , VHV model 0 0 0 2 0 1 0 Vertical constraint may occur here. 2 1 0 0 0 2 0 • Always gives a solution with channel width equal channel density, i. e. , optimal solution. 11/1/2020 14

Left-edge Algorithm 1. Sort the horizontal segments of the nets in increasing order of their left end points. 2. Place them one by one greedily on the bottommost available track. 11/1/2020 15

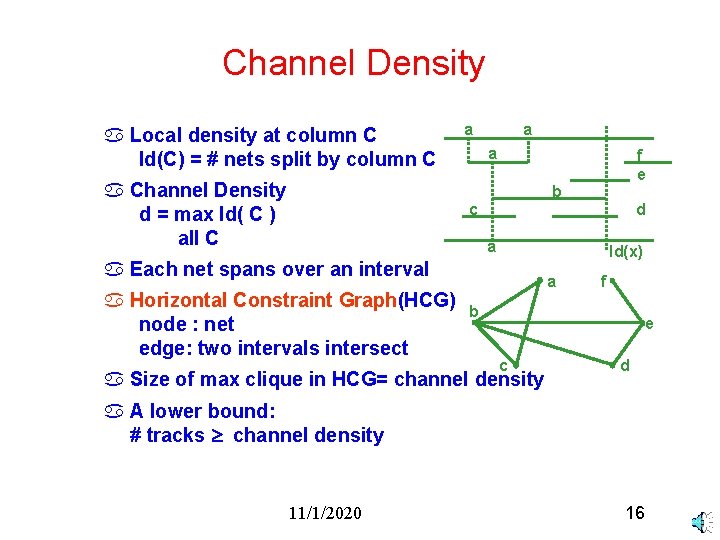

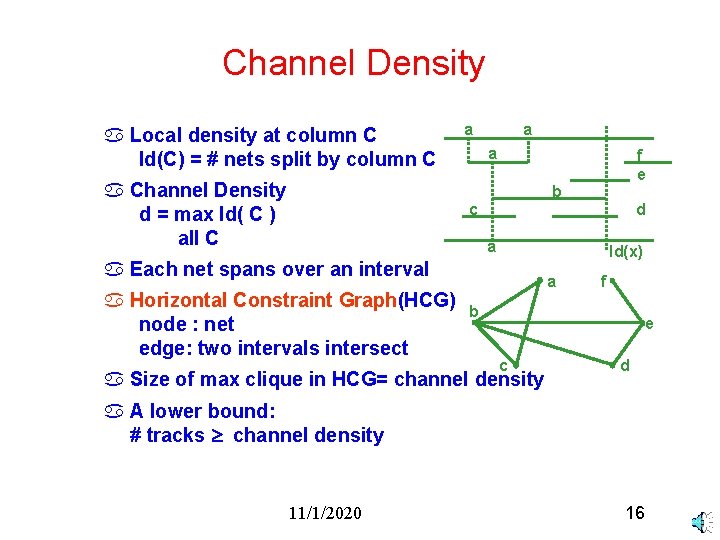

Channel Density a Local density at column C ld(C) = # nets split by column C a Channel Density d = max ld( C ) all C a a a f e b c d a ld(x) a Each net spans over an interval a Horizontal Constraint Graph(HCG) node : net edge: two intervals intersect a f b e c a Size of max clique in HCG= channel density d a A lower bound: # tracks channel density 11/1/2020 16

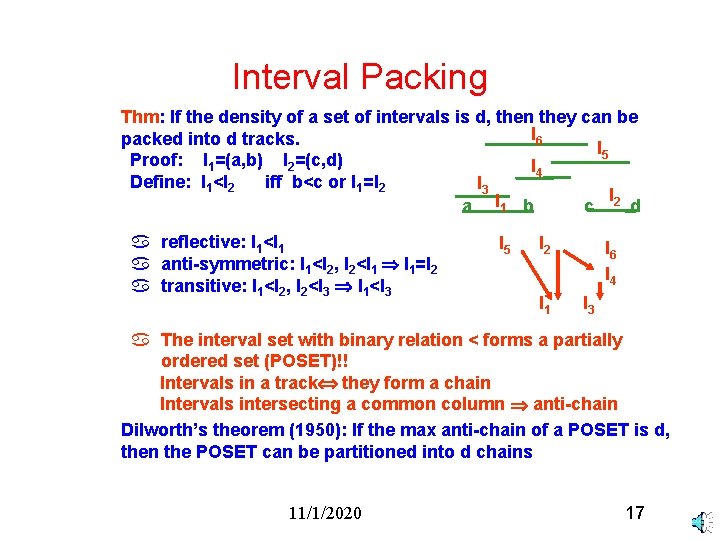

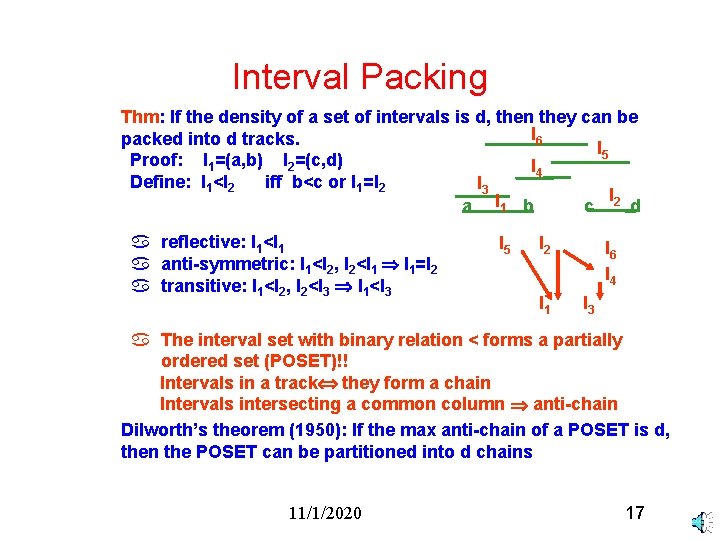

Interval Packing Thm: If the density of a set of intervals is d, then they can be I 6 packed into d tracks. I 5 Proof: I 1=(a, b) I 2=(c, d) I 4 Define: I 1<I 2 iff b<c or I 1=I 2 I 3 I a I 1 b c 2 d a reflective: I 1<I 1 a anti-symmetric: I 1<I 2, I 2<I 1 I 1=I 2 a transitive: I 1<I 2, I 2<I 3 I 1<I 3 I 5 I 2 I 1 I 6 I 4 I 3 a The interval set with binary relation < forms a partially ordered set (POSET)!! Intervals in a track they form a chain Intervals intersecting a common column anti-chain Dilworth’s theorem (1950): If the max anti-chain of a POSET is d, then the POSET can be partitioned into d chains 11/1/2020 17

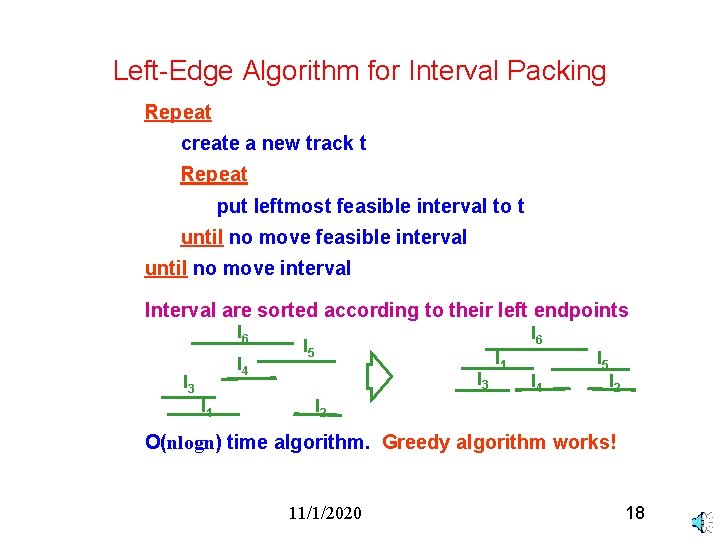

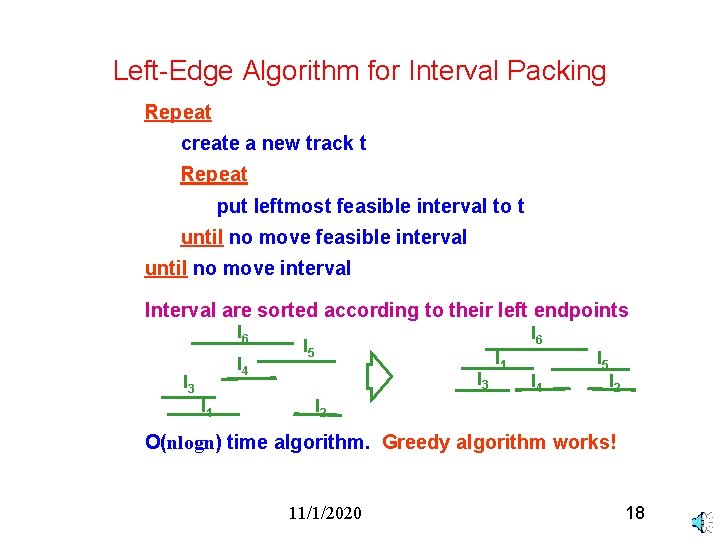

Left-Edge Algorithm for Interval Packing Repeat create a new track t Repeat put leftmost feasible interval to t until no move feasible interval until no move interval Interval are sorted according to their left endpoints I 6 I 4 I 3 I 1 I 6 I 5 I 3 I 1 I 4 I 5 I 2 O(nlogn) time algorithm. Greedy algorithm works! 11/1/2020 18

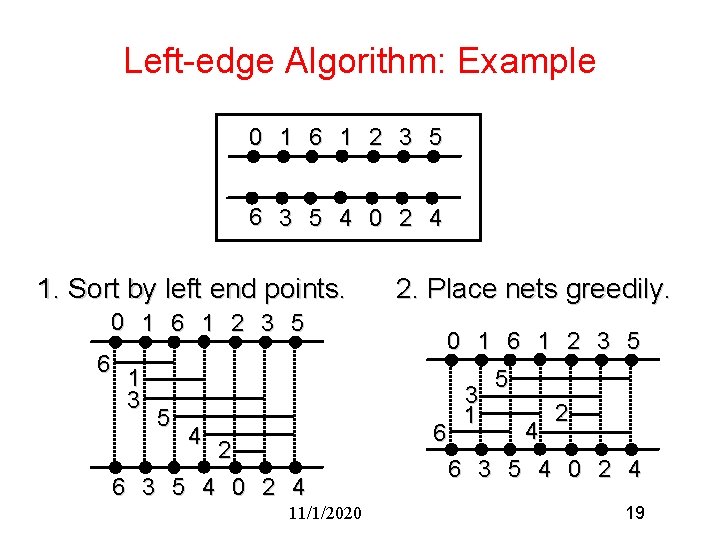

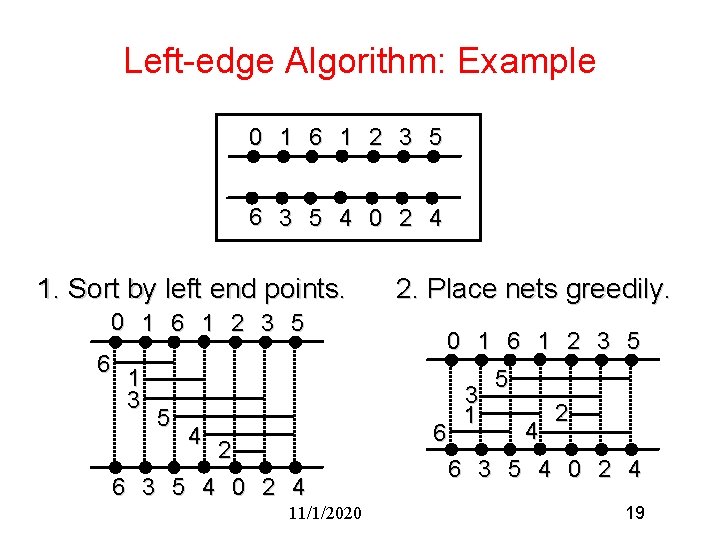

Left-edge Algorithm: Example 0 1 6 1 2 3 5 6 3 5 4 0 2 4 1. Sort by left end points. 0 1 6 1 2 3 5 6 1 3 5 4 2. Place nets greedily. 0 1 6 1 2 3 5 6 2 6 3 5 4 0 2 4 11/1/2020 3 1 5 4 2 6 3 5 4 0 2 4 19

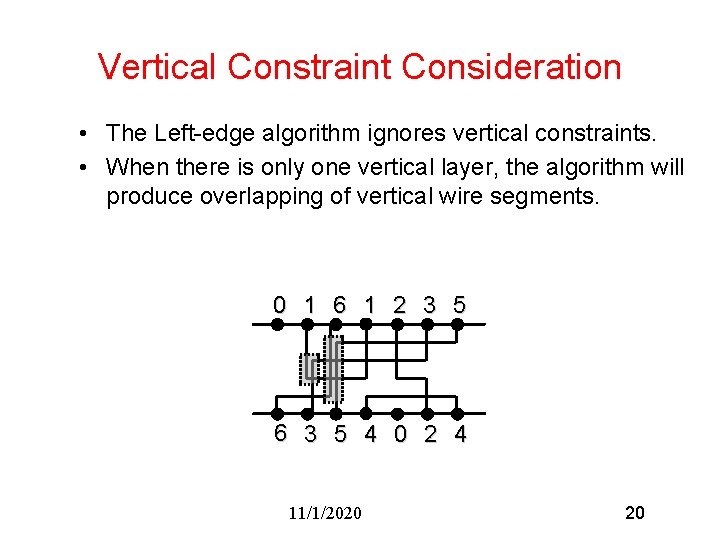

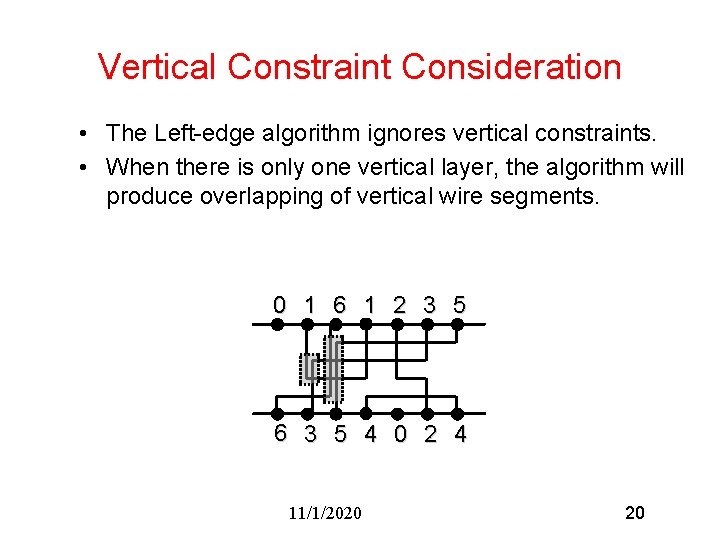

Vertical Constraint Consideration • The Left-edge algorithm ignores vertical constraints. • When there is only one vertical layer, the algorithm will produce overlapping of vertical wire segments. 0 1 6 1 2 3 5 6 3 5 4 0 2 4 11/1/2020 20

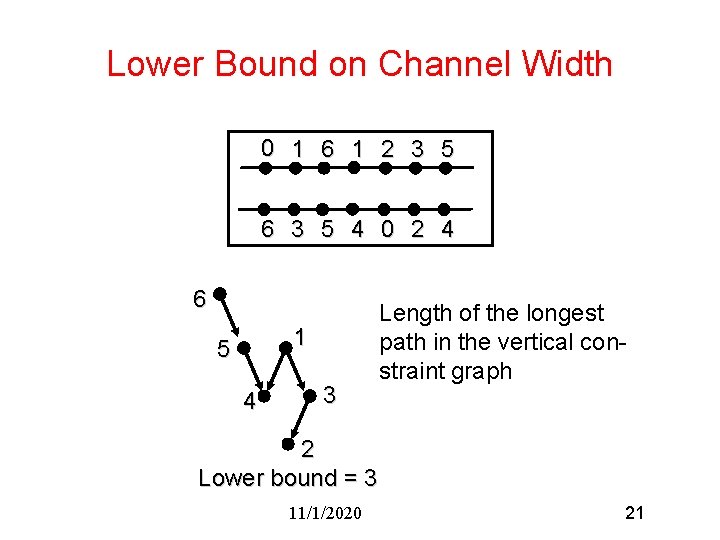

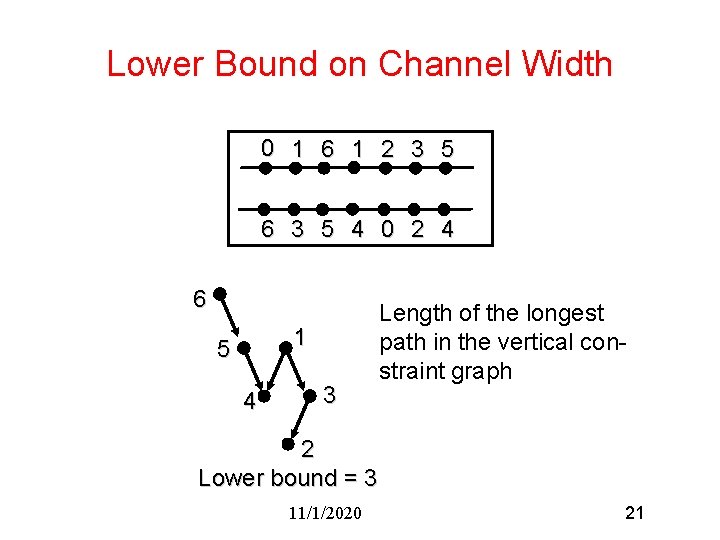

Lower Bound on Channel Width 0 1 6 1 2 3 5 6 3 5 4 0 2 4 6 1 5 4 3 Length of the longest path in the vertical constraint graph 2 Lower bound = 3 11/1/2020 21

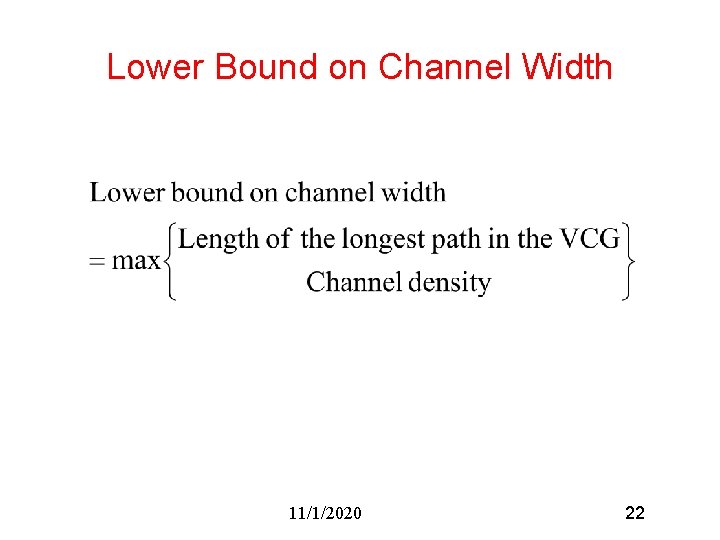

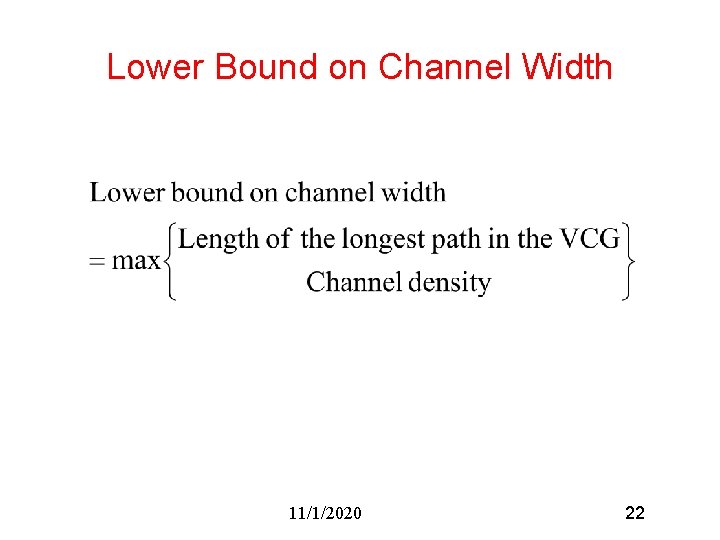

Lower Bound on Channel Width 11/1/2020 22

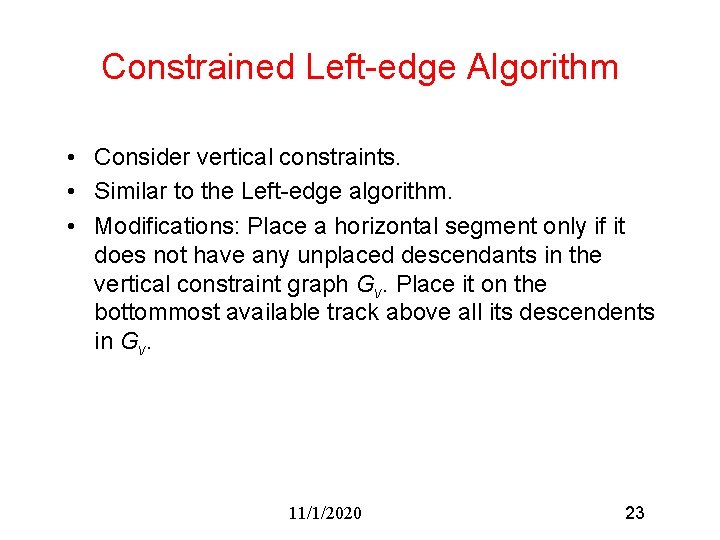

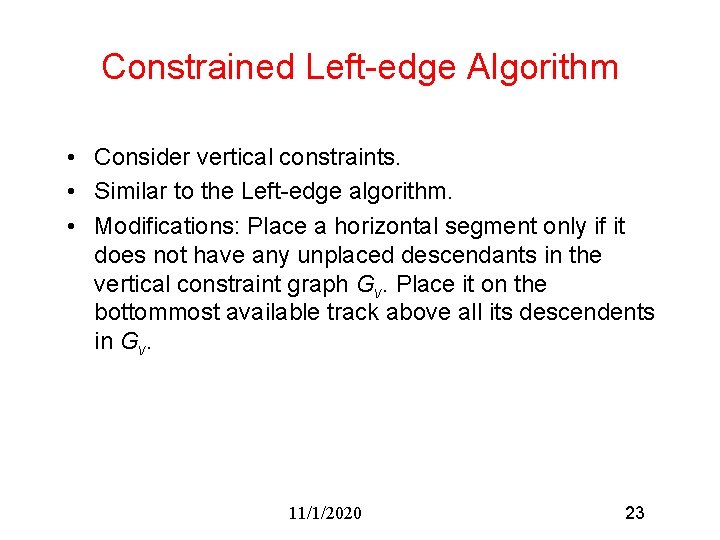

Constrained Left-edge Algorithm • Consider vertical constraints. • Similar to the Left-edge algorithm. • Modifications: Place a horizontal segment only if it does not have any unplaced descendants in the vertical constraint graph Gv. Place it on the bottommost available track above all its descendents in Gv. 11/1/2020 23

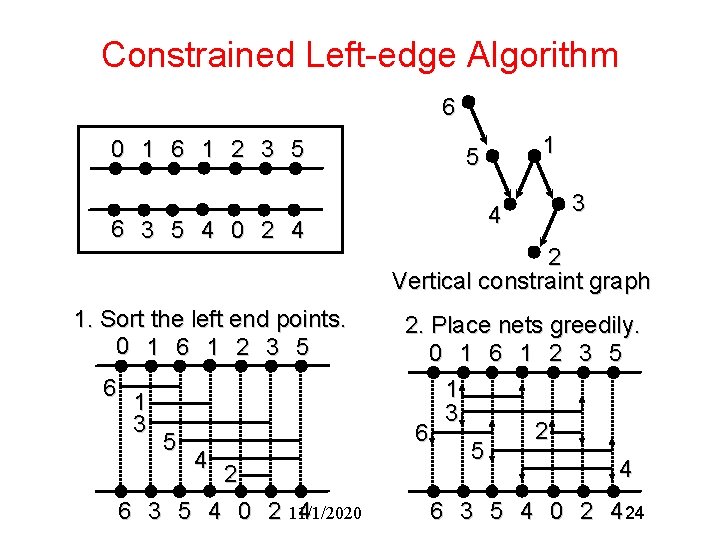

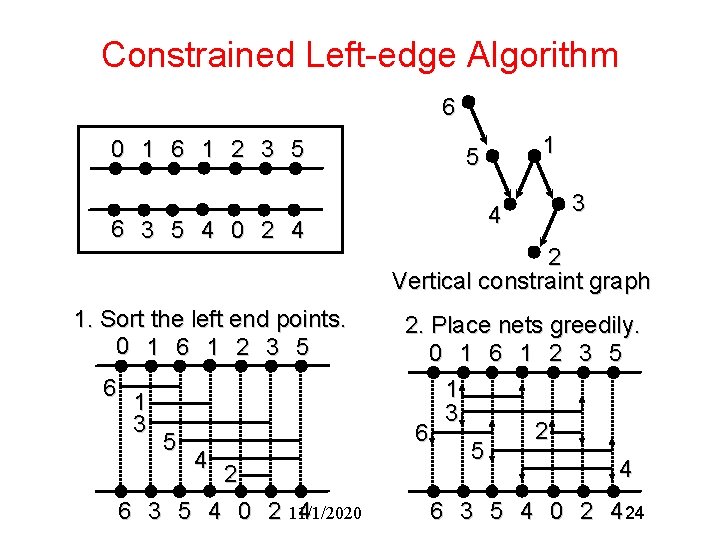

Constrained Left-edge Algorithm 6 0 1 6 1 2 3 5 6 3 5 4 0 2 4 1. Sort the left end points. 0 1 6 1 2 3 5 6 1 3 5 4 2 6 3 5 4 0 2 11/1/2020 4 1 5 4 3 2 Vertical constraint graph 2. Place nets greedily. 0 1 6 1 2 3 5 1 3 2 6 5 4 6 3 5 4 0 2 4 24

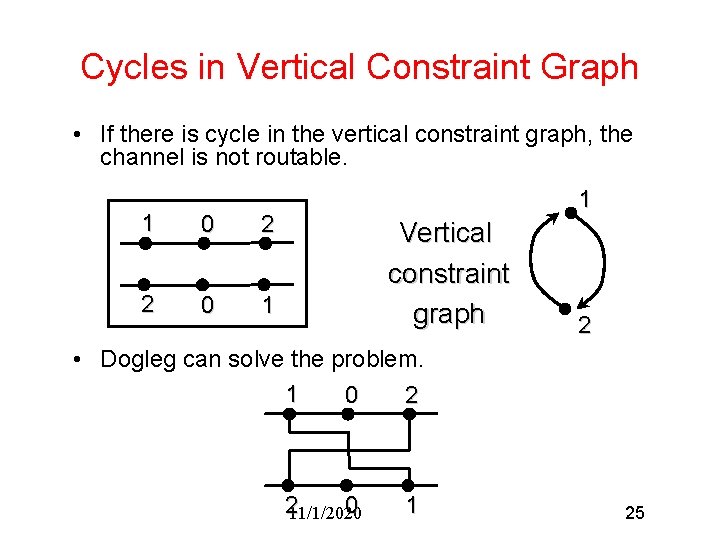

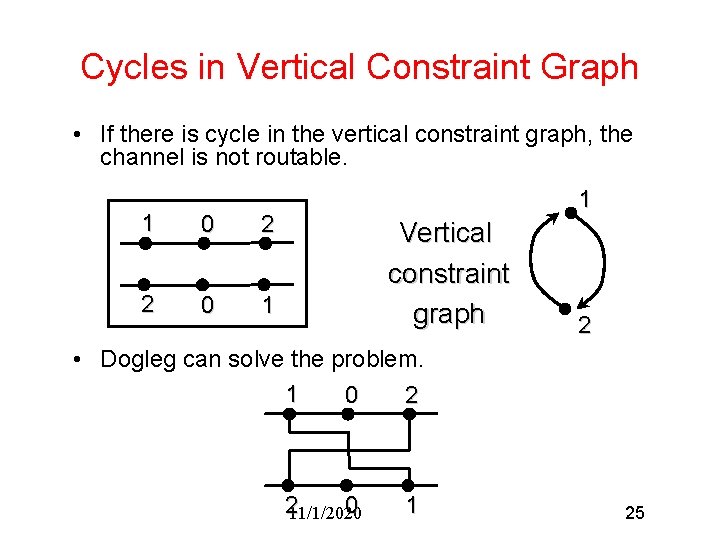

Cycles in Vertical Constraint Graph • If there is cycle in the vertical constraint graph, the channel is not routable. 1 0 2 2 0 1 1 Vertical constraint graph 2 • Dogleg can solve the problem. 1 0 2 211/1/2020 0 1 25

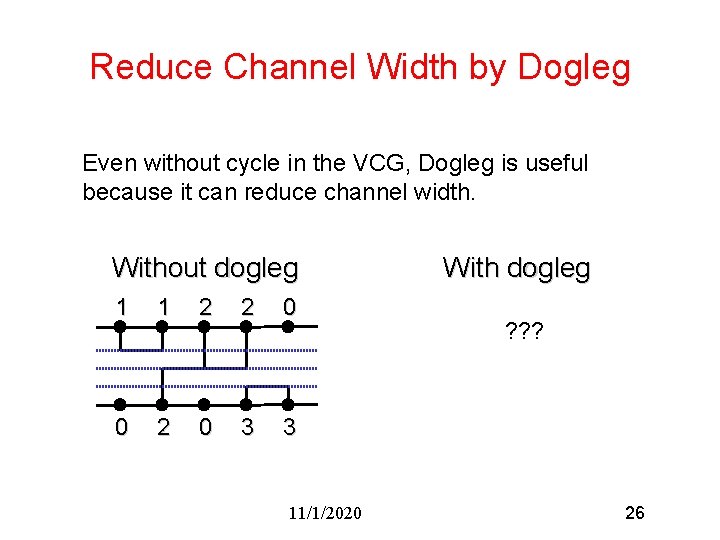

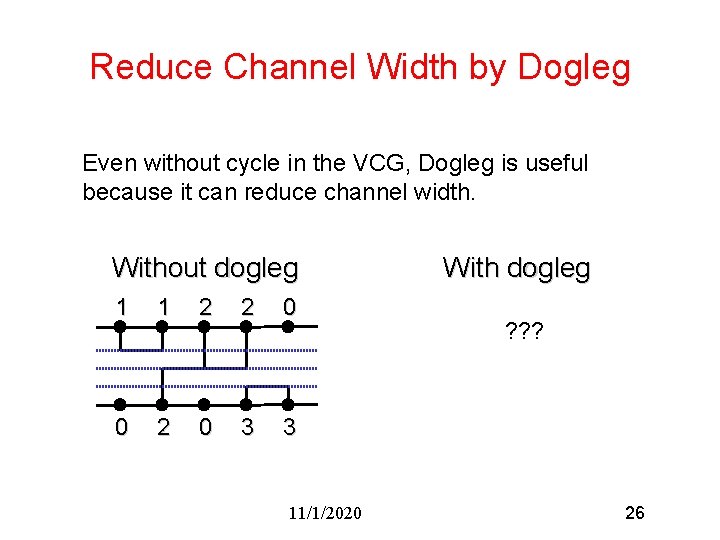

Reduce Channel Width by Dogleg Even without cycle in the VCG, Dogleg is useful because it can reduce channel width. Without dogleg 1 1 2 2 0 0 2 0 3 3 11/1/2020 With dogleg ? ? ? 26

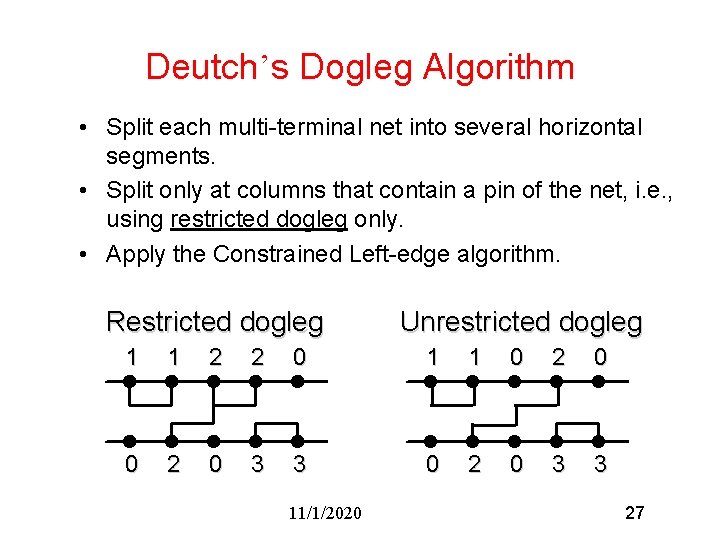

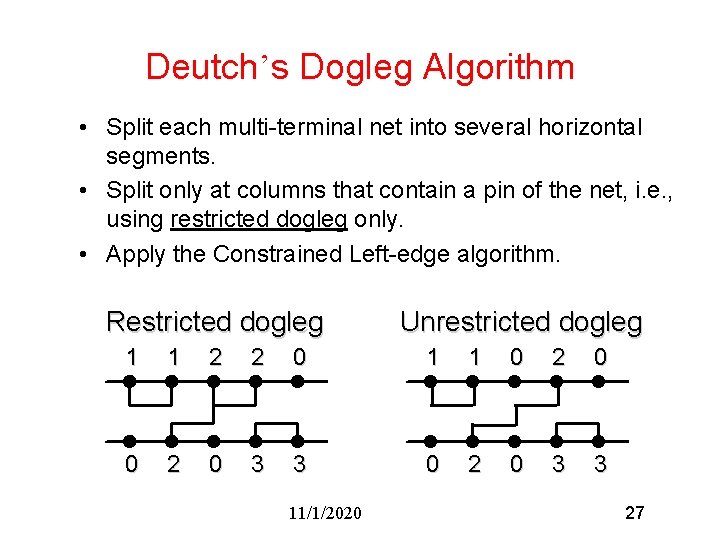

Deutch’s Dogleg Algorithm • Split each multi-terminal net into several horizontal segments. • Split only at columns that contain a pin of the net, i. e. , using restricted dogleg only. • Apply the Constrained Left-edge algorithm. Restricted dogleg Unrestricted dogleg 1 1 2 2 0 1 1 0 2 0 3 3 11/1/2020 27

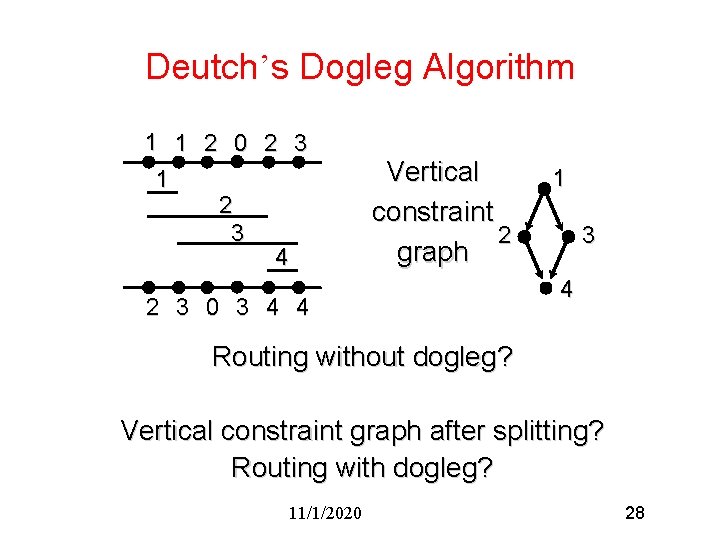

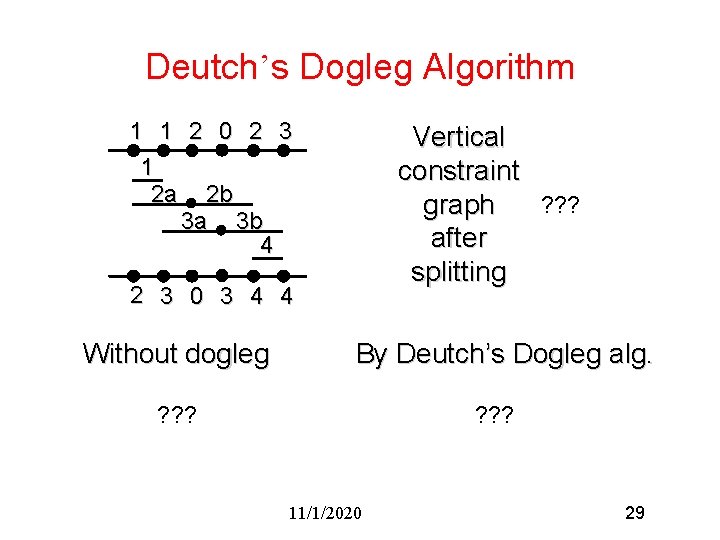

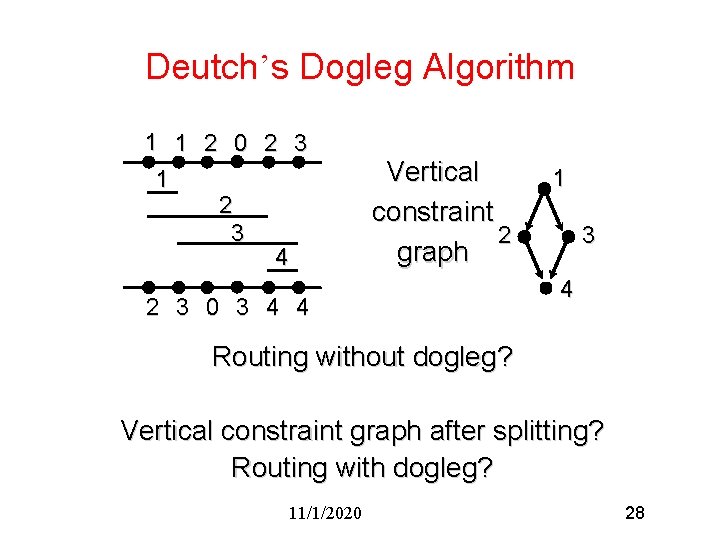

Deutch’s Dogleg Algorithm 1 1 2 0 2 3 1 2 3 4 Vertical constraint 2 graph 2 3 0 3 4 4 1 3 4 Routing without dogleg? Vertical constraint graph after splitting? Routing with dogleg? 11/1/2020 28

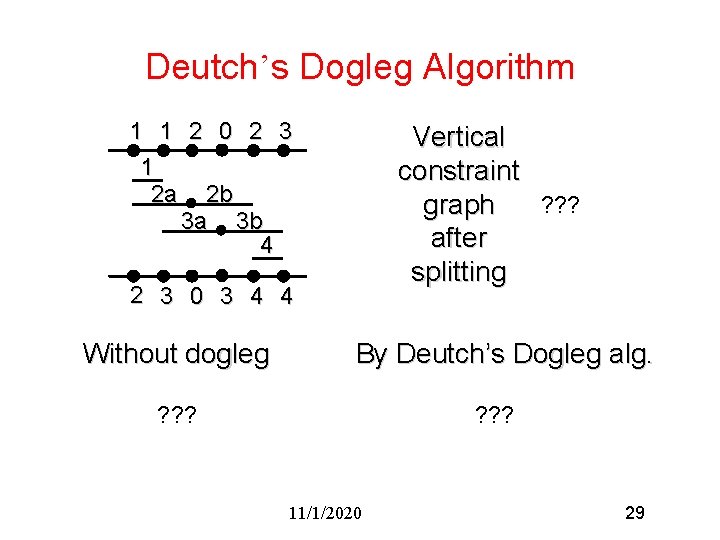

Deutch’s Dogleg Algorithm 1 1 2 0 2 3 1 2 a 2 b 3 a 3 b 4 Vertical constraint ? ? ? graph after splitting 2 3 0 3 4 4 Without dogleg By Deutch’s Dogleg alg. ? ? ? 11/1/2020 29

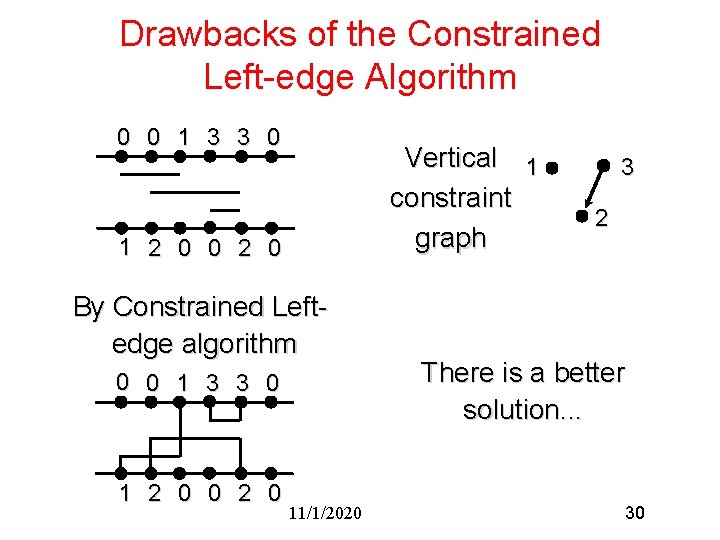

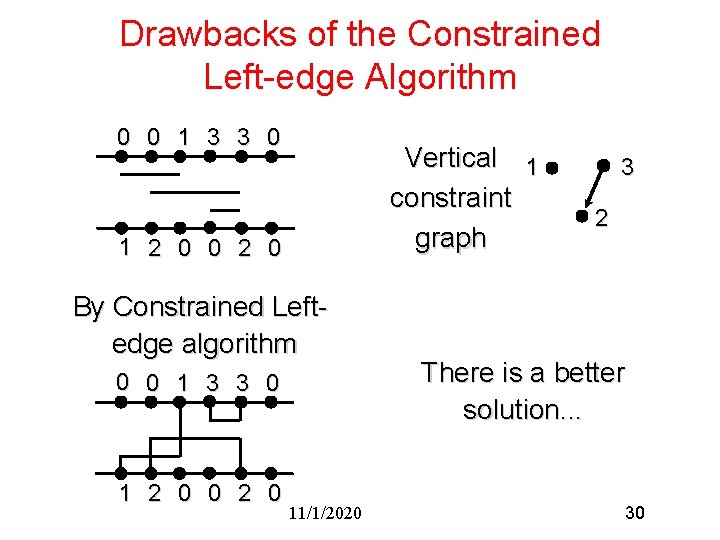

Drawbacks of the Constrained Left-edge Algorithm 0 0 1 3 3 0 Vertical 1 constraint graph 1 2 0 0 2 0 By Constrained Leftedge algorithm 0 0 1 3 3 0 1 2 0 0 2 0 11/1/2020 3 2 There is a better solution. . . 30

Drawbacks of the Constrained Left-edge Algorithm What’s wrong with the Constrained Left-edge algorithm? The Constrained Left-edge algorithm does not take care of the vertical and horizontal constraints together optimally. 11/1/2020 31