VLSI eszkzk fizikja Egyelektron eszkzk s alkalmazsaik Ksztette

- Slides: 62

VLSI eszközök fizikája „Egy-elektron” eszközök és alkalmazásaik Készítette: Katona József Átdolgozta: Szabó Péter, Somlay Gergely

A tartalomból • Alapjelenségek ismertetése • Alapeszközök bemutatása • Analóg felhasználási terület • Digitális megoldások • Az alkalmazhatóság fő problémái

A kezdetek • „transfer of single electrons between small conducting ‘islands’ ” • A gondolat régi (20. század eleje) • A megvalósítás a technológia problémák miatt csak a 80’-as években Alapjelenségek

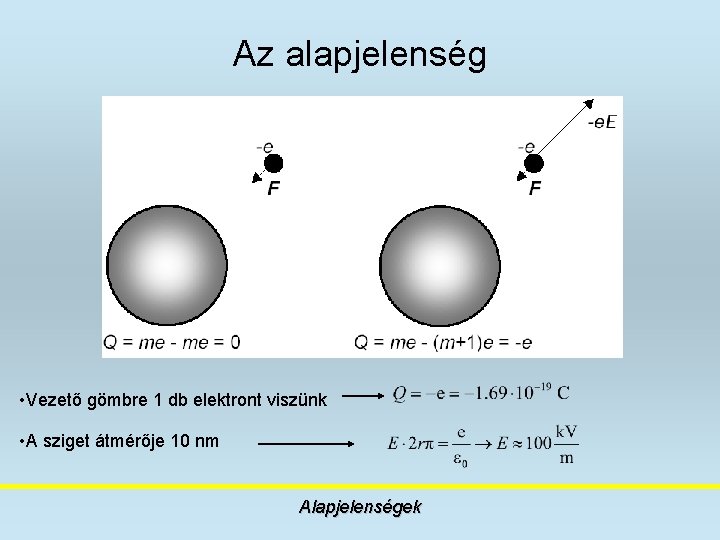

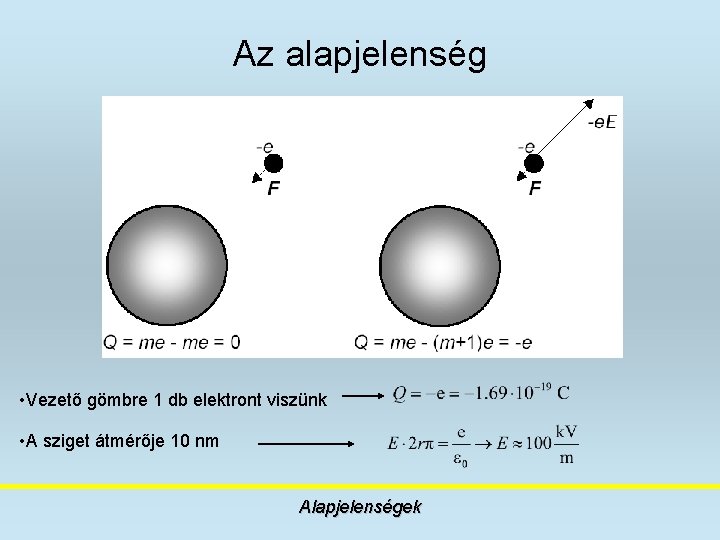

Az alapjelenség • Vezető gömbre 1 db elektront viszünk • A sziget átmérője 10 nm Alapjelenségek

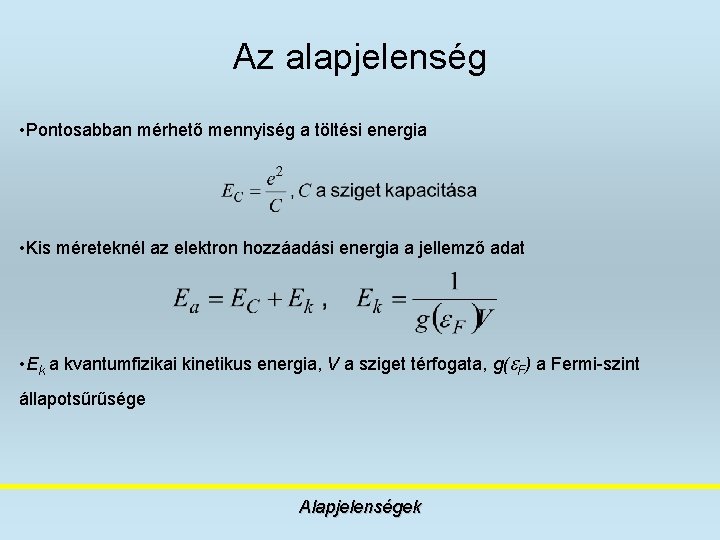

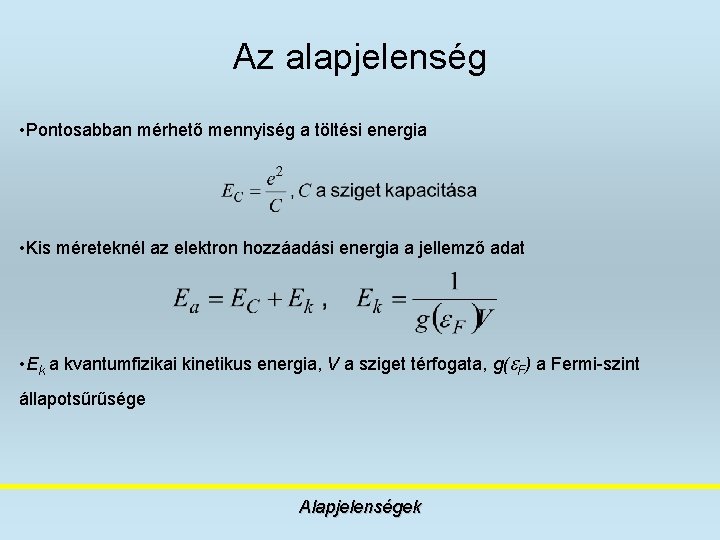

Az alapjelenség • Pontosabban mérhető mennyiség a töltési energia • Kis méreteknél az elektron hozzáadási energia a jellemző adat • Ek a kvantumfizikai kinetikus energia, V a sziget térfogata, g( F) a Fermi-szint állapotsűrűsége Alapjelenségek

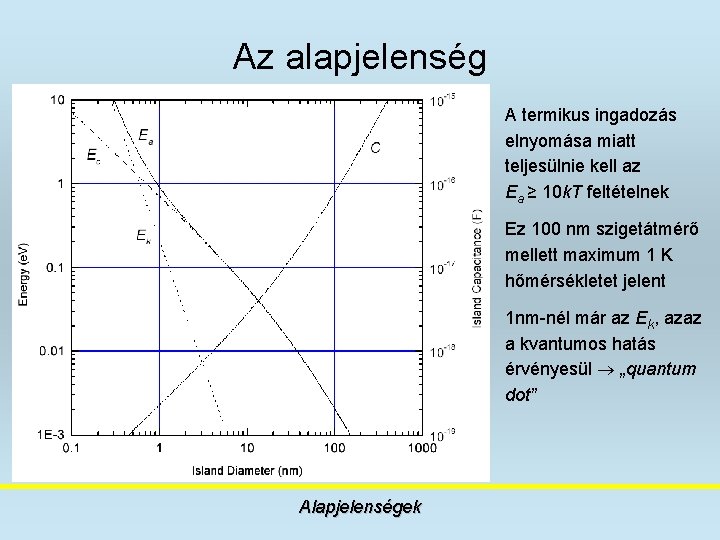

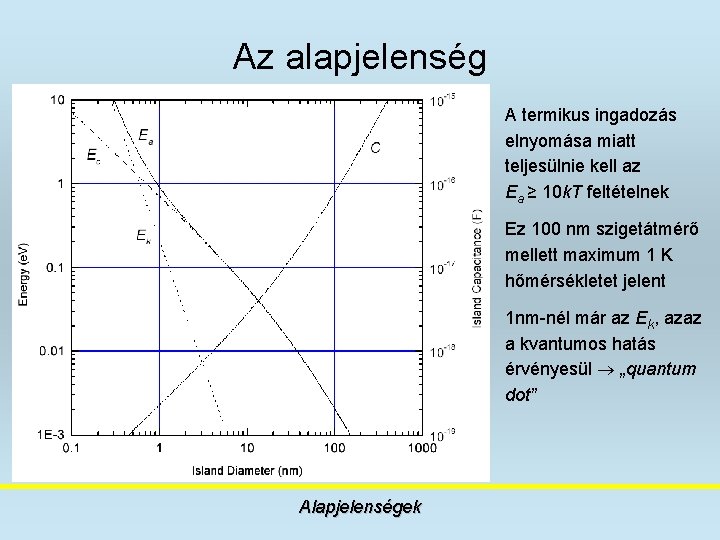

Az alapjelenség A termikus ingadozás elnyomása miatt teljesülnie kell az Ea ≥ 10 k. T feltételnek Ez 100 nm szigetátmérő mellett maximum 1 K hőmérsékletet jelent 1 nm-nél már az Ek, azaz a kvantumos hatás érvényesül „quantum dot” Alapjelenségek

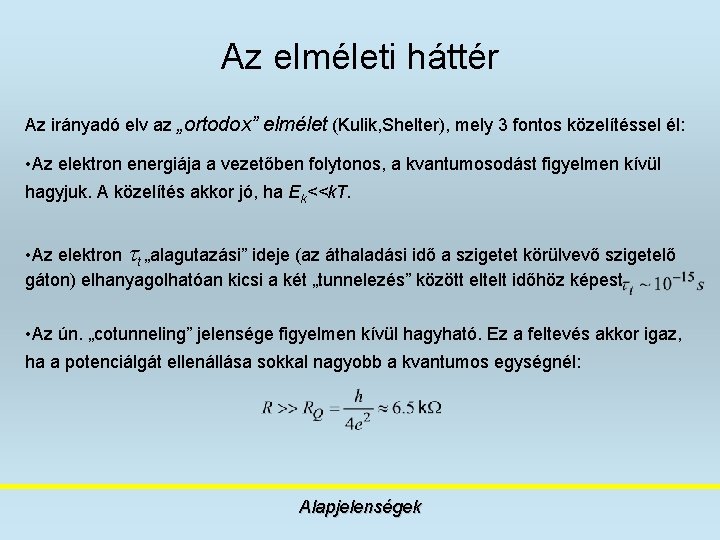

Az elméleti háttér Az irányadó elv az „ortodox” elmélet (Kulik, Shelter), mely 3 fontos közelítéssel él: • Az elektron energiája a vezetőben folytonos, a kvantumosodást figyelmen kívül hagyjuk. A közelítés akkor jó, ha Ek<<k. T. • Az elektron t „alagutazási” ideje (az áthaladási idő a szigetet körülvevő szigetelő gáton) elhanyagolhatóan kicsi a két „tunnelezés” között eltelt időhöz képest • Az ún. „cotunneling” jelensége figyelmen kívül hagyható. Ez a feltevés akkor igaz, ha a potenciálgát ellenállása sokkal nagyobb a kvantumos egységnél: Alapjelenségek

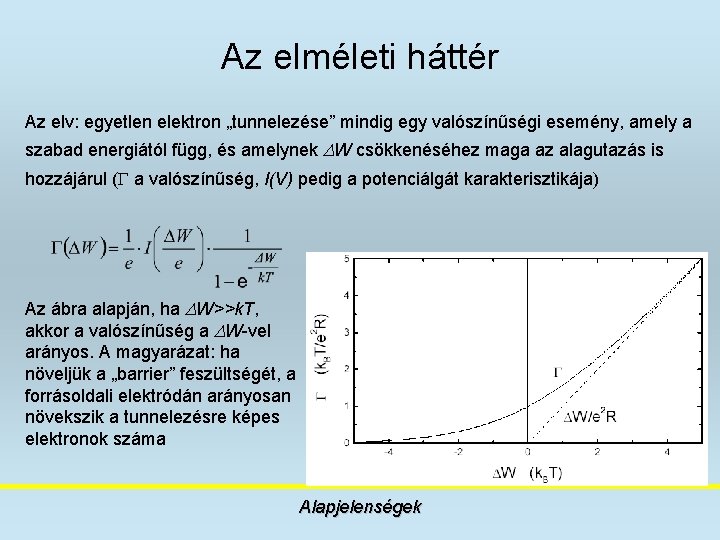

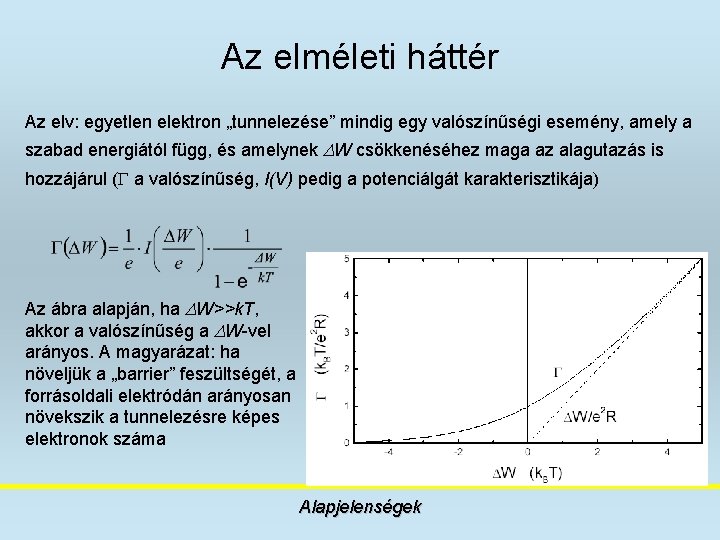

Az elméleti háttér Az elv: egyetlen elektron „tunnelezése” mindig egy valószínűségi esemény, amely a szabad energiától függ, és amelynek W csökkenéséhez maga az alagutazás is hozzájárul ( a valószínűség, I(V) pedig a potenciálgát karakterisztikája) Az ábra alapján, ha W>>k. T, akkor a valószínűség a W-vel arányos. A magyarázat: ha növeljük a „barrier” feszültségét, a forrásoldali elektródán arányosan növekszik a tunnelezésre képes elektronok száma Alapjelenségek

Az elméleti háttér Az „ortodox” elv korlátai • „Cotunneling”. Megfigyelték, hogy egy időpontban több elektron alagutazása is lehetséges, mint egyetlen egységes kvantummechanikai folyamat. Az egy-elektron alagutazásokhoz képest az arány , N az egyszerre alagutazó elektronok száma. Az R ellenállás nagyságára vonatkozó feltétel (ld. 7. dia) betartásával a jelenséget még nem tapasztalták. • Diszkrét energiaszintek. Kis szigetátmérő (1 nm) esetén előjönnek a kvantumos hatások (Ek). Ebben az esetben módosítani kell a tunnelezés valószínűségét leíró képletet : (ld. következő ábra) Alapjelenségek

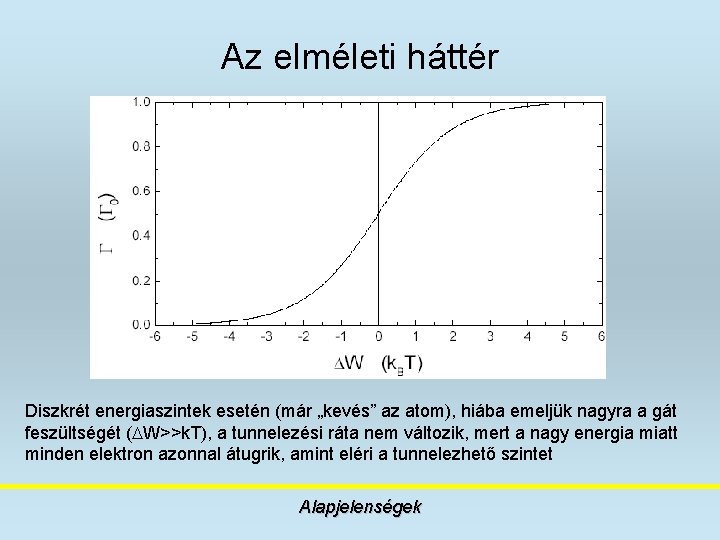

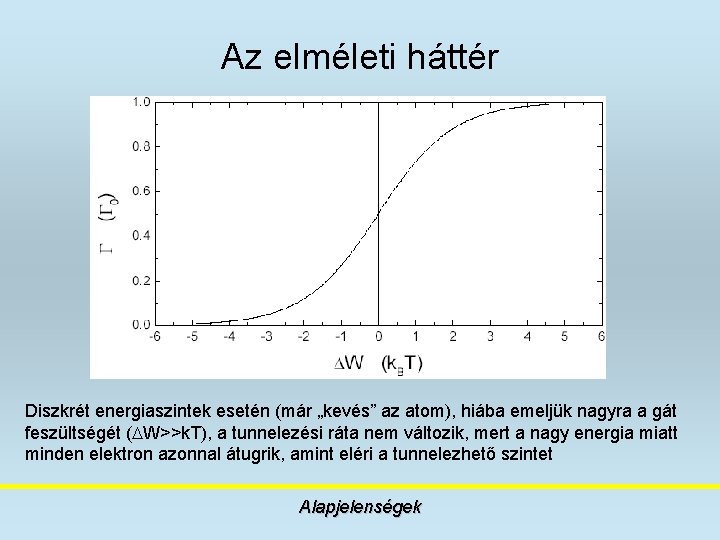

Az elméleti háttér Diszkrét energiaszintek esetén (már „kevés” az atom), hiába emeljük nagyra a gát feszültségét ( W>>k. T), a tunnelezési ráta nem változik, mert a nagy energia miatt minden elektron azonnal átugrik, amint eléri a tunnelezhető szintet Alapjelenségek

Alapeszközök • Egy-elektron doboz (Single-Electron Box) • Egy-elektron tranzisztor (Single-Electron Transistor) • Egy-elektron csapda (Single-Electron Trap) • Egy-elektron „forgóajtó” (Single-Electron Turnstile) • Egy-elektron pumpa (Single-Electron Pump) • Oszcillátor egyetlen elektron alagutazásával (SETunneling Oscillator) • Szupravezetők (Supercondutors)

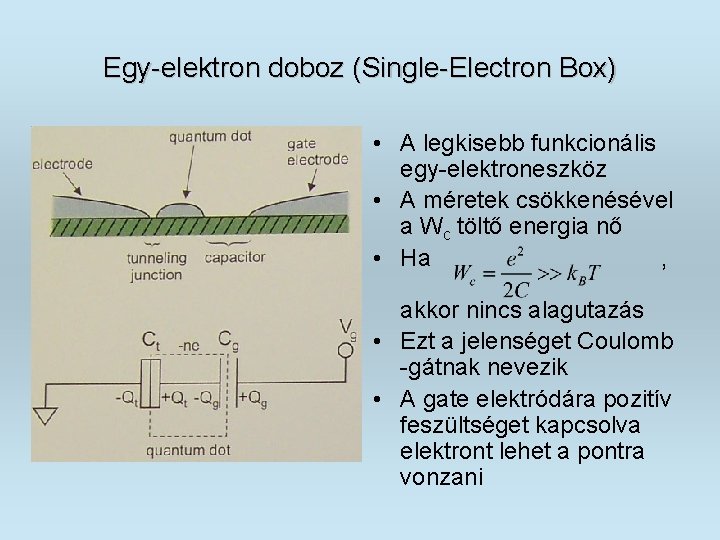

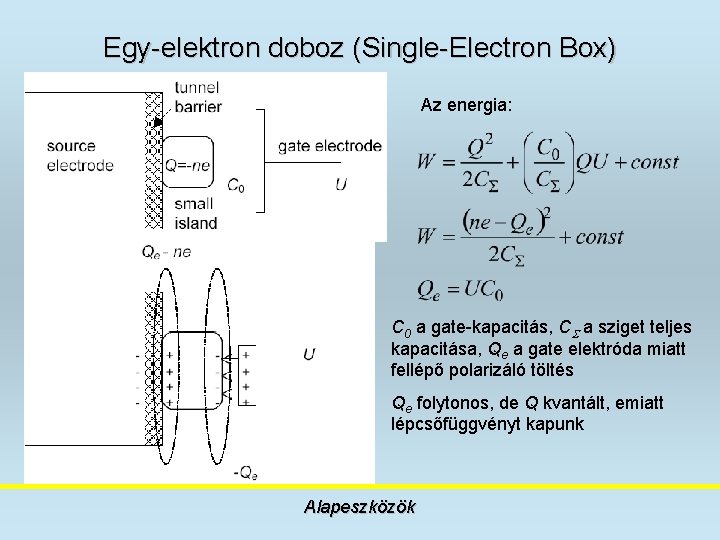

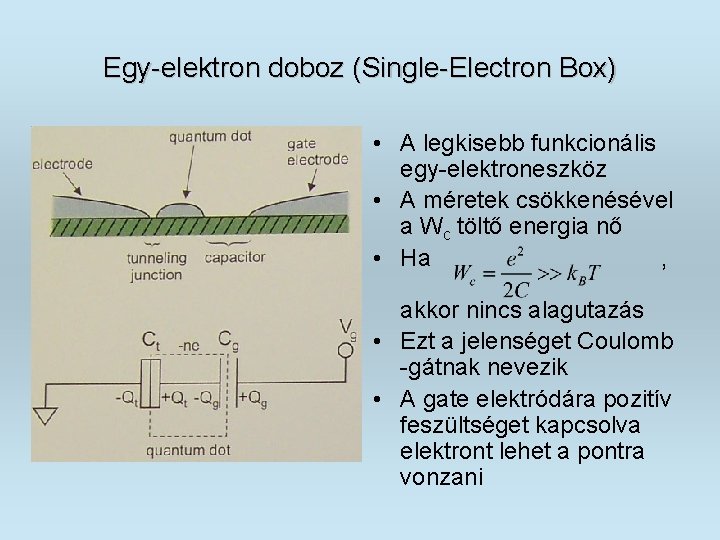

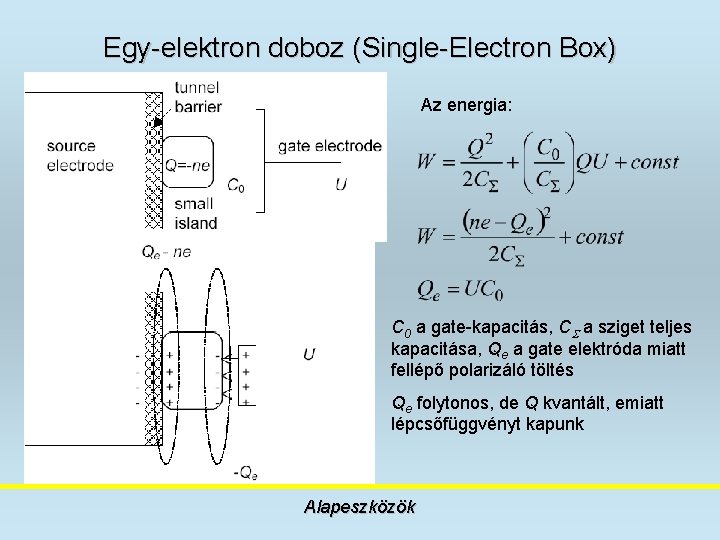

Egy-elektron doboz (Single-Electron Box) • A legkisebb funkcionális egy-elektroneszköz • A méretek csökkenésével a Wc töltő energia nő • Ha , akkor nincs alagutazás • Ezt a jelenséget Coulomb -gátnak nevezik • A gate elektródára pozitív feszültséget kapcsolva elektront lehet a pontra vonzani

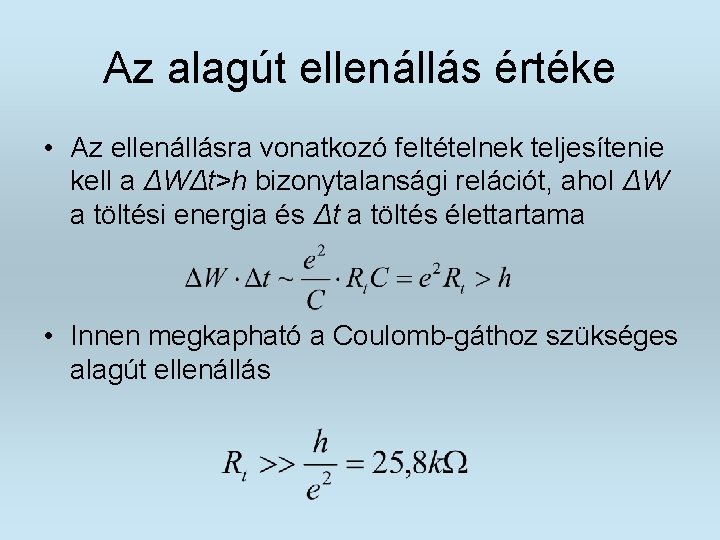

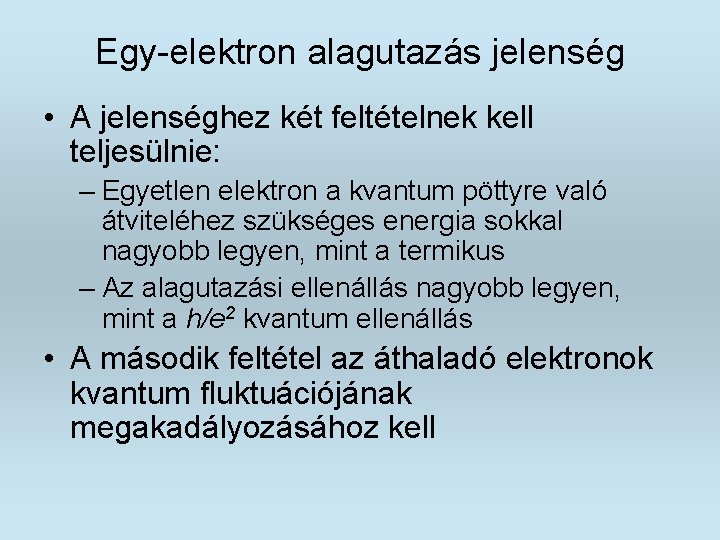

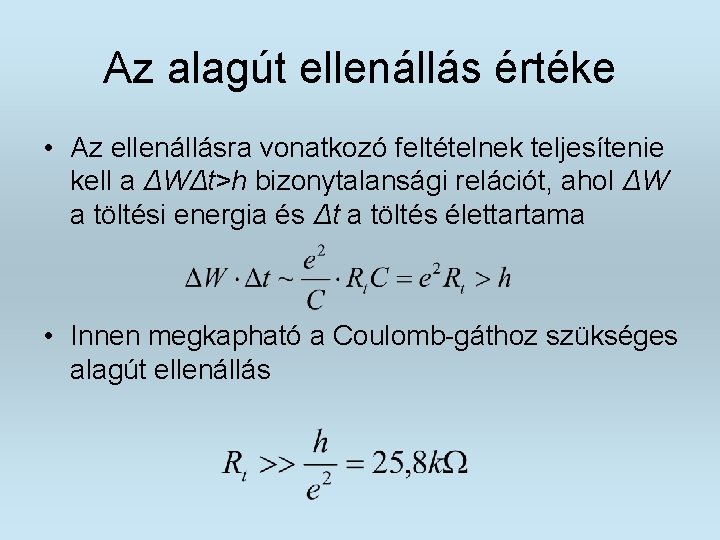

Egy-elektron alagutazás jelenség • A jelenséghez két feltételnek kell teljesülnie: – Egyetlen elektron a kvantum pöttyre való átviteléhez szükséges energia sokkal nagyobb legyen, mint a termikus – Az alagutazási ellenállás nagyobb legyen, mint a h/e 2 kvantum ellenállás • A második feltétel az áthaladó elektronok kvantum fluktuációjának megakadályozásához kell

Az alagút ellenállás értéke • Az ellenállásra vonatkozó feltételnek teljesítenie kell a ΔWΔt>h bizonytalansági relációt, ahol ΔW a töltési energia és Δt a töltés élettartama • Innen megkapható a Coulomb-gáthoz szükséges alagút ellenállás

Egy-elektron doboz (Single-Electron Box) Az energia: C 0 a gate-kapacitás, C a sziget teljes kapacitása, Qe a gate elektróda miatt fellépő polarizáló töltés Qe folytonos, de Q kvantált, emiatt lépcsőfüggvényt kapunk Alapeszközök

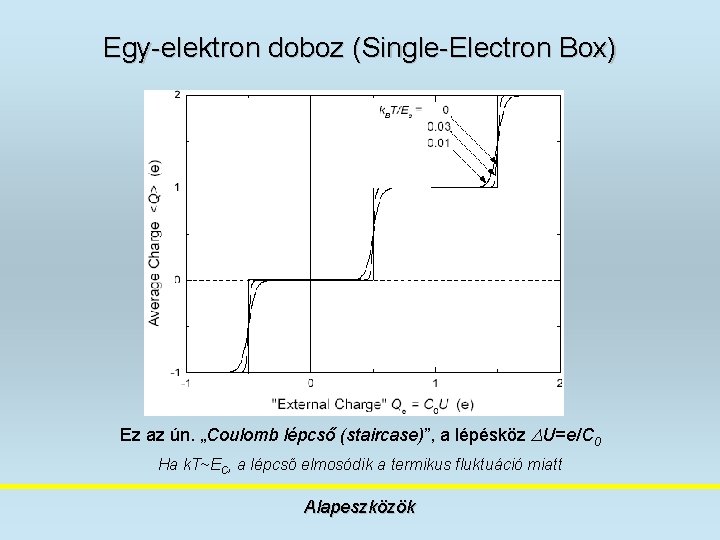

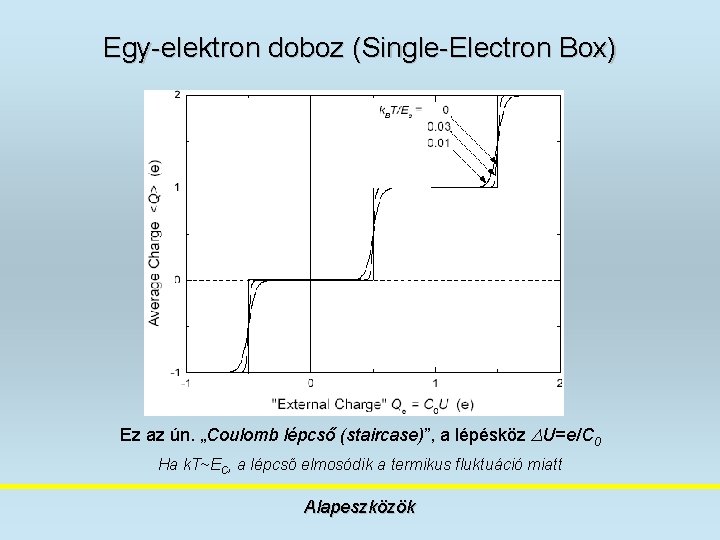

Egy-elektron doboz (Single-Electron Box) Ez az ún. „Coulomb lépcső (staircase)”, a lépésköz U=e/C 0 Ha k. T~EC, a lépcső elmosódik a termikus fluktuáció miatt Alapeszközök

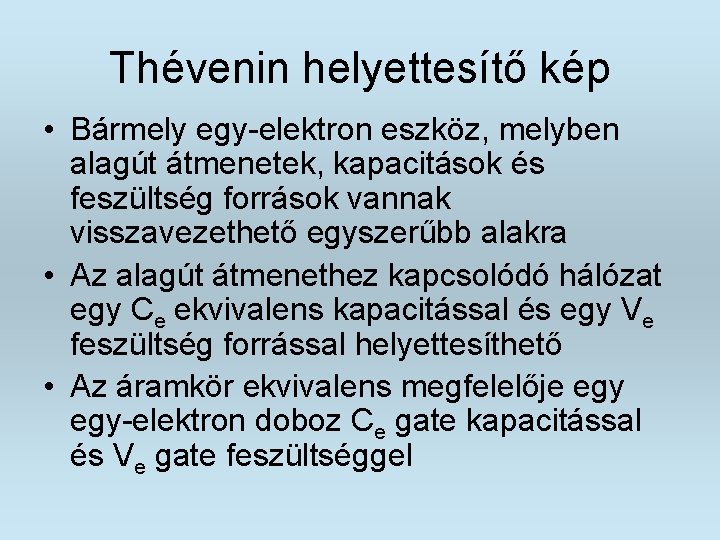

Thévenin helyettesítő kép • Bármely egy-elektron eszköz, melyben alagút átmenetek, kapacitások és feszültség források vannak visszavezethető egyszerűbb alakra • Az alagút átmenethez kapcsolódó hálózat egy Ce ekvivalens kapacitással és egy Ve feszültség forrással helyettesíthető • Az áramkör ekvivalens megfelelője egy-elektron doboz Ce gate kapacitással és Ve gate feszültséggel

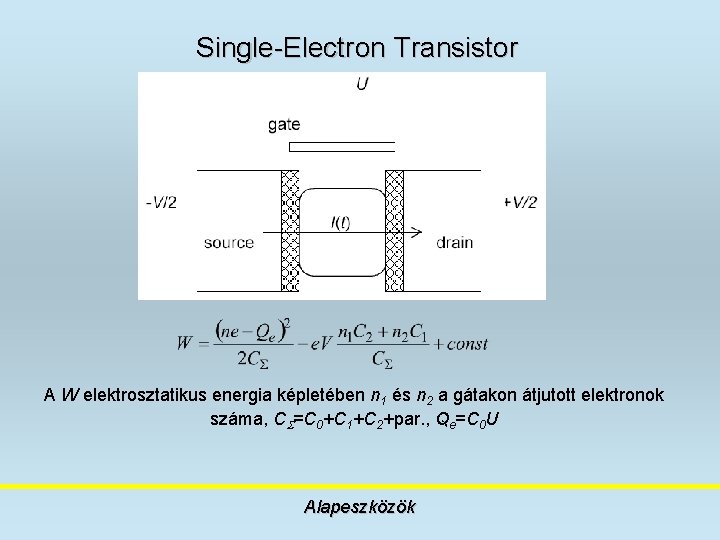

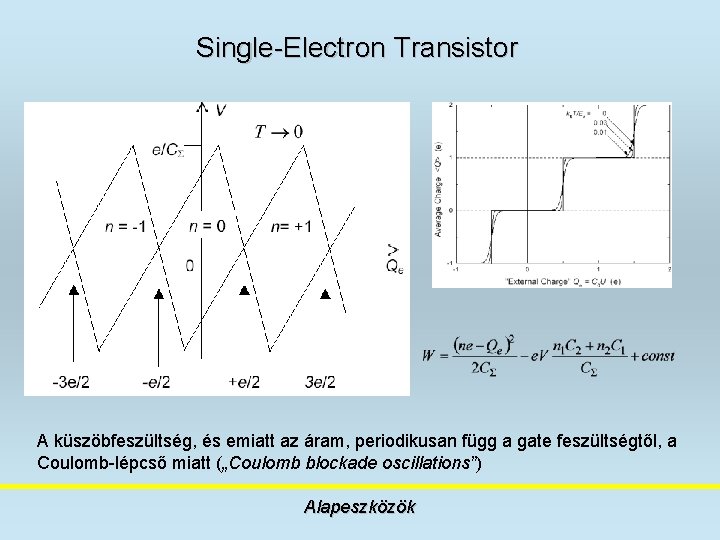

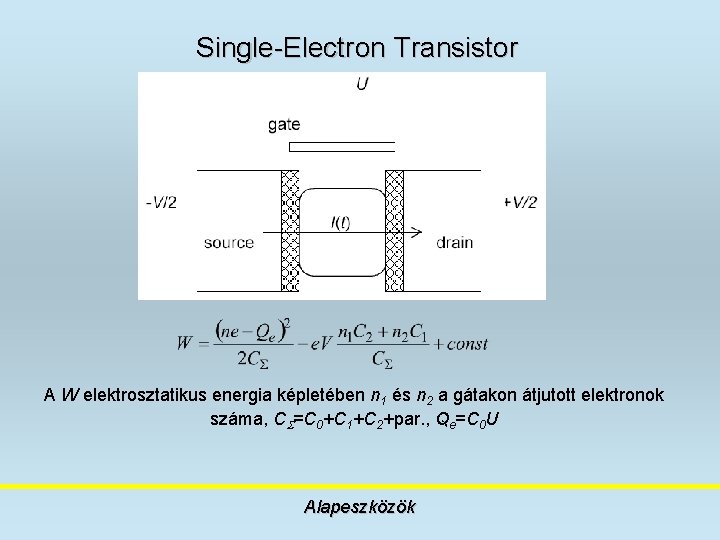

Single-Electron Transistor A W elektrosztatikus energia képletében n 1 és n 2 a gátakon átjutott elektronok száma, C =C 0+C 1+C 2+par. , Qe=C 0 U Alapeszközök

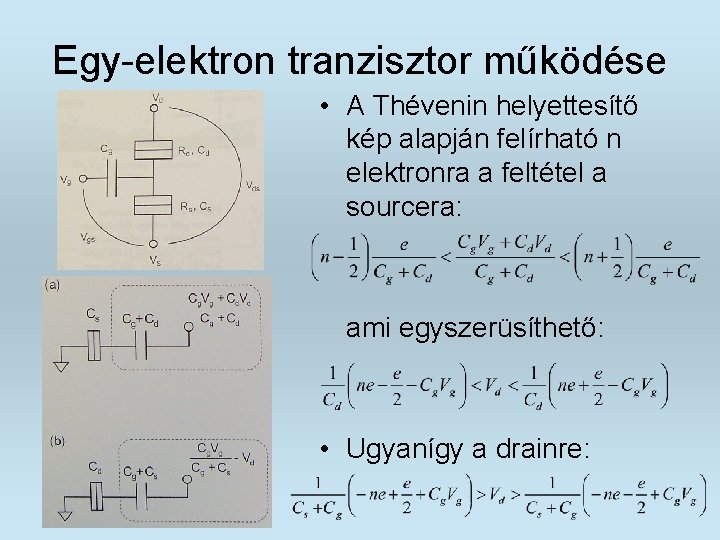

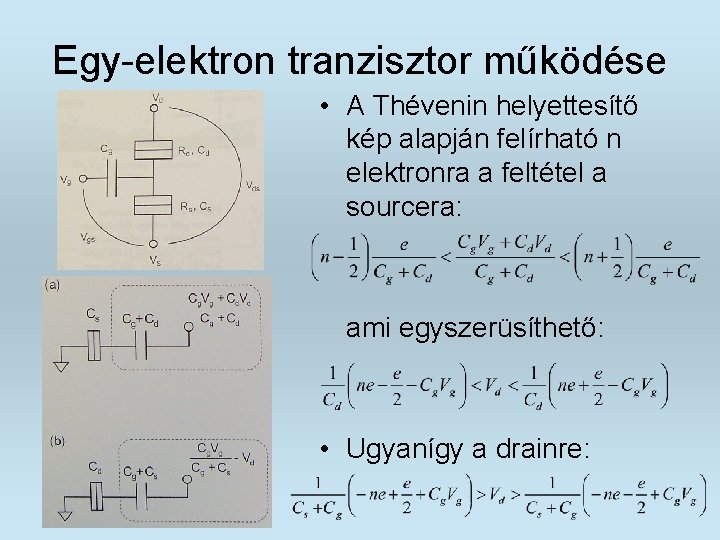

Egy-elektron tranzisztor működése • A Thévenin helyettesítő kép alapján felírható n elektronra a feltétel a sourcera: ami egyszerüsíthető: • Ugyanígy a drainre:

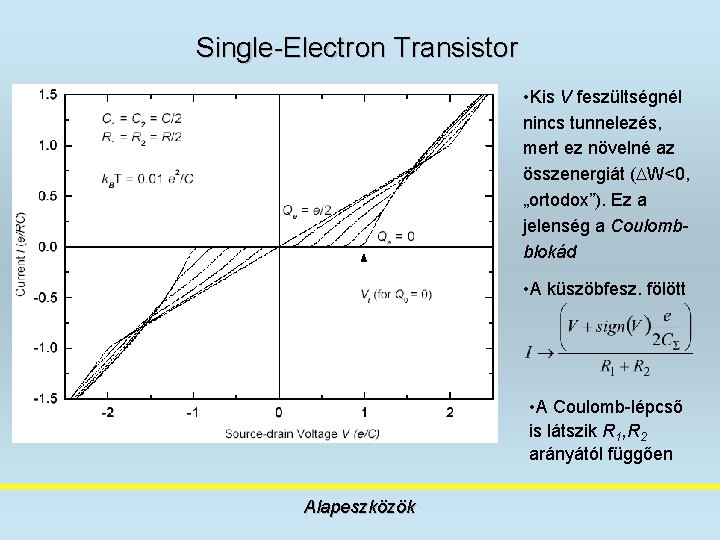

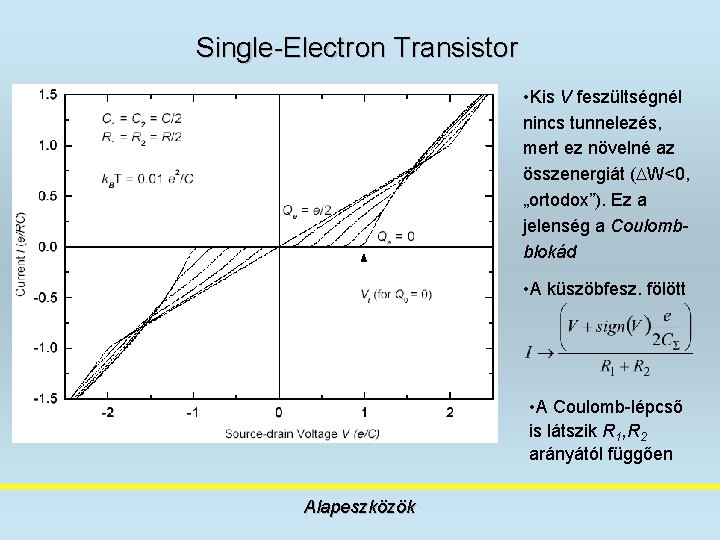

Single-Electron Transistor • Kis V feszültségnél nincs tunnelezés, mert ez növelné az összenergiát ( W<0, „ortodox”). Ez a jelenség a Coulombblokád • A küszöbfesz. fölött • A Coulomb-lépcső is látszik R 1, R 2 arányától függően Alapeszközök

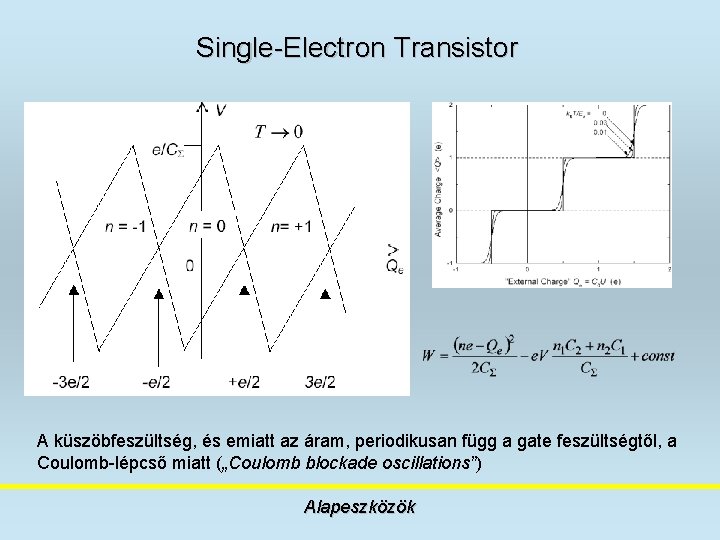

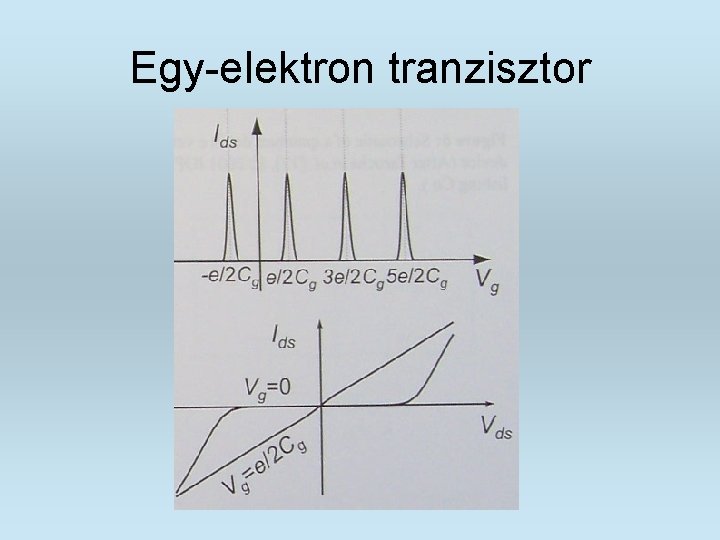

Single-Electron Transistor A küszöbfeszültség, és emiatt az áram, periodikusan függ a gate feszültségtől, a Coulomb-lépcső miatt („Coulomb blockade oscillations”) Alapeszközök

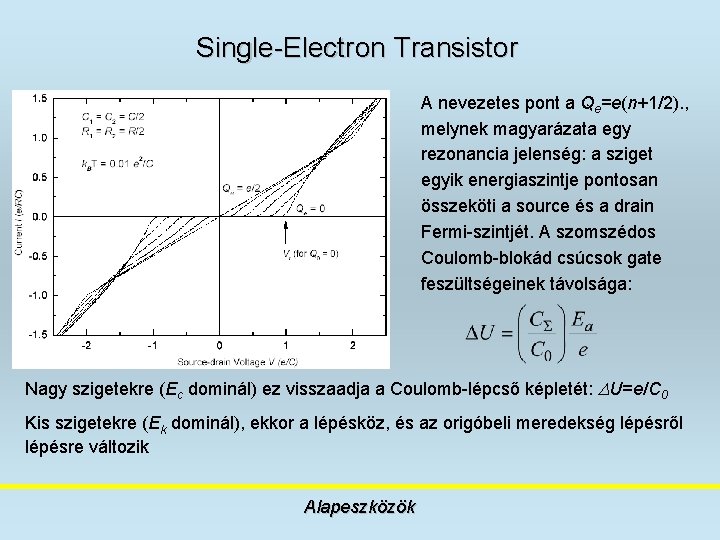

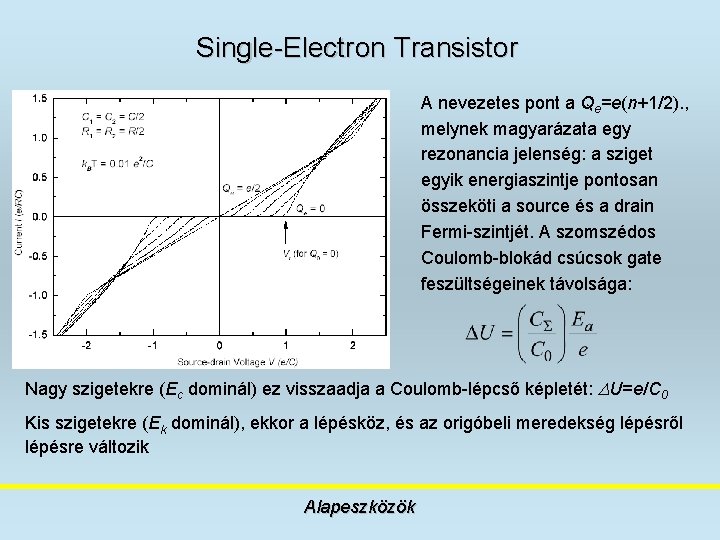

Single-Electron Transistor A nevezetes pont a Qe=e(n+1/2). , melynek magyarázata egy rezonancia jelenség: a sziget egyik energiaszintje pontosan összeköti a source és a drain Fermi-szintjét. A szomszédos Coulomb-blokád csúcsok gate feszültségeinek távolsága: Nagy szigetekre (Ec dominál) ez visszaadja a Coulomb-lépcső képletét: U=e/C 0 Kis szigetekre (Ek dominál), ekkor a lépésköz, és az origóbeli meredekség lépésről lépésre változik Alapeszközök

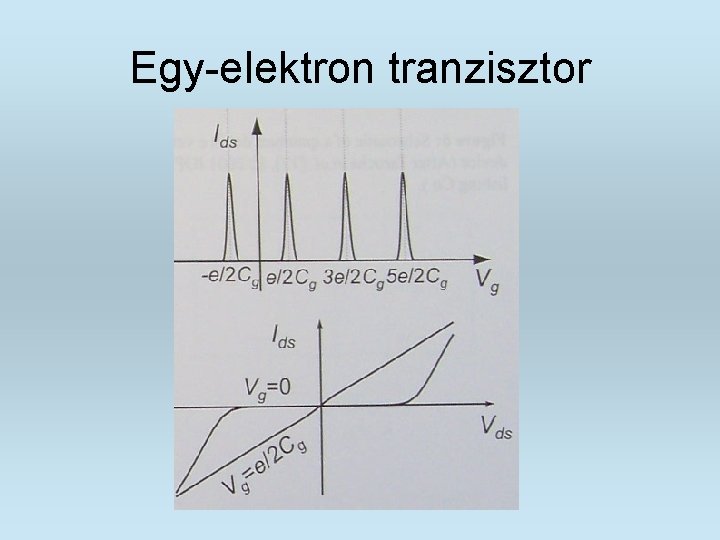

Egy-elektron tranzisztor

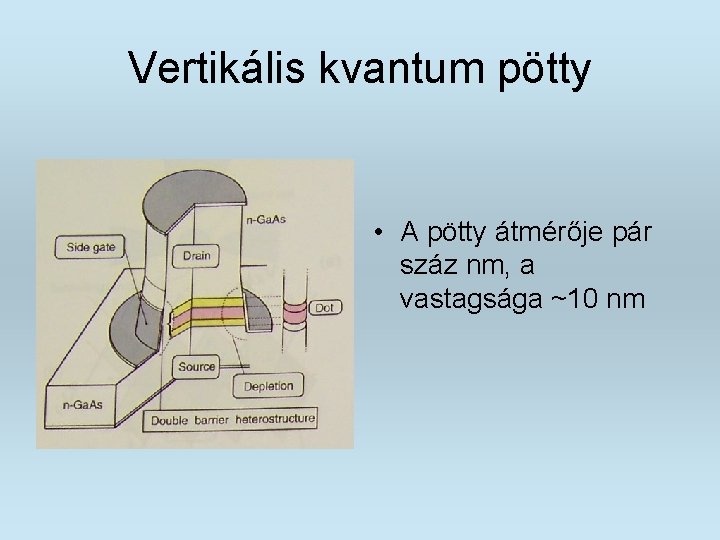

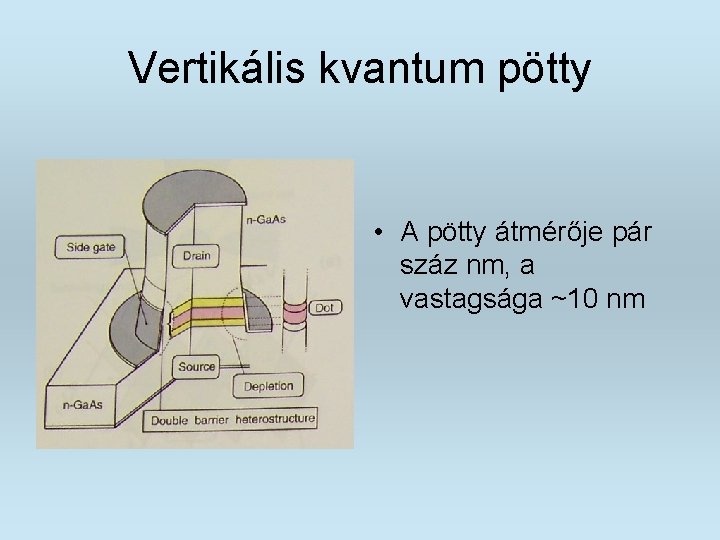

Vertikális kvantum pötty • A pötty átmérője pár száz nm, a vastagsága ~10 nm

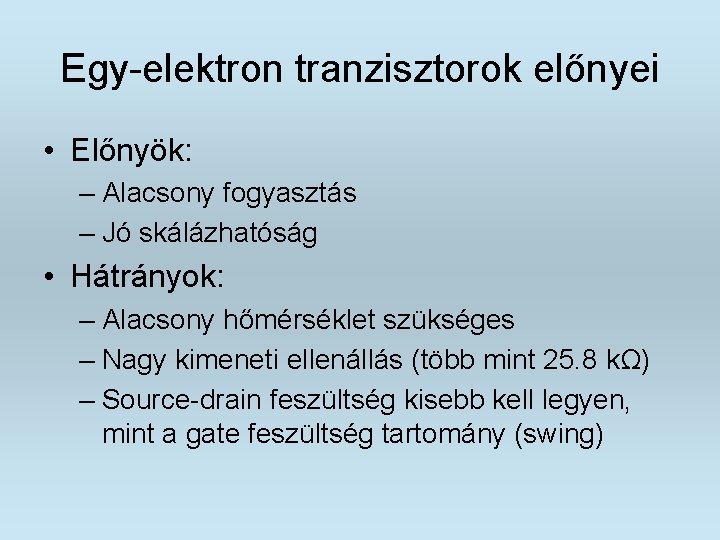

Egy-elektron tranzisztorok előnyei • Előnyök: – Alacsony fogyasztás – Jó skálázhatóság • Hátrányok: – Alacsony hőmérséklet szükséges – Nagy kimeneti ellenállás (több mint 25. 8 kΩ) – Source-drain feszültség kisebb kell legyen, mint a gate feszültség tartomány (swing)

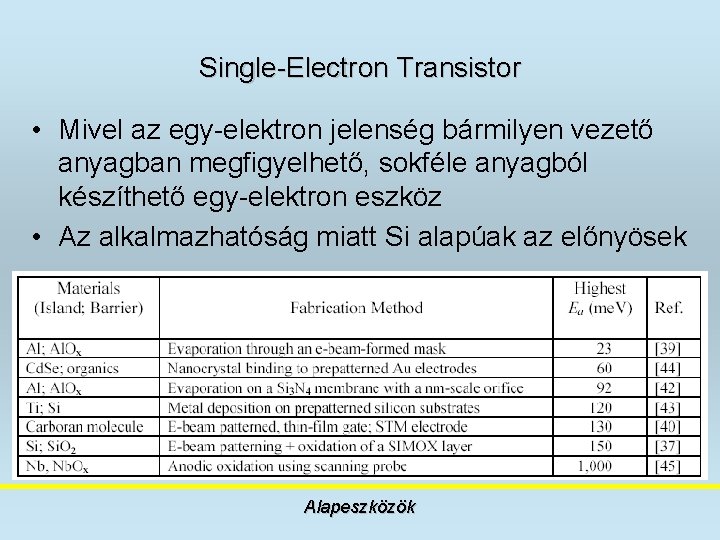

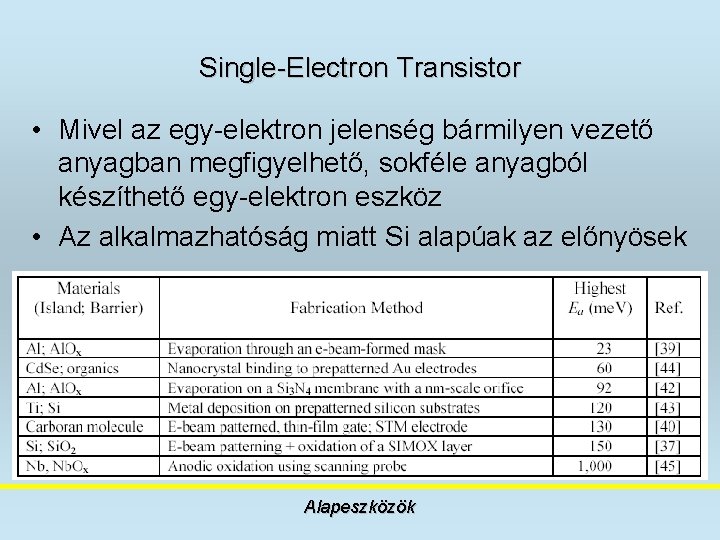

Single-Electron Transistor • Mivel az egy-elektron jelenség bármilyen vezető anyagban megfigyelhető, sokféle anyagból készíthető egy-elektron eszköz • Az alkalmazhatóság miatt Si alapúak az előnyösek Alapeszközök

Si kvantum pöttyök kialakítása • Alapvetően két tehnológia létezik: – A szilícium kvantum pöttyök kialakítása finom litográfiai módszerekkel (PADOX, V-PADOX) – Szilícium kvantum pöttyök növesztése leválasztásos technikákkal

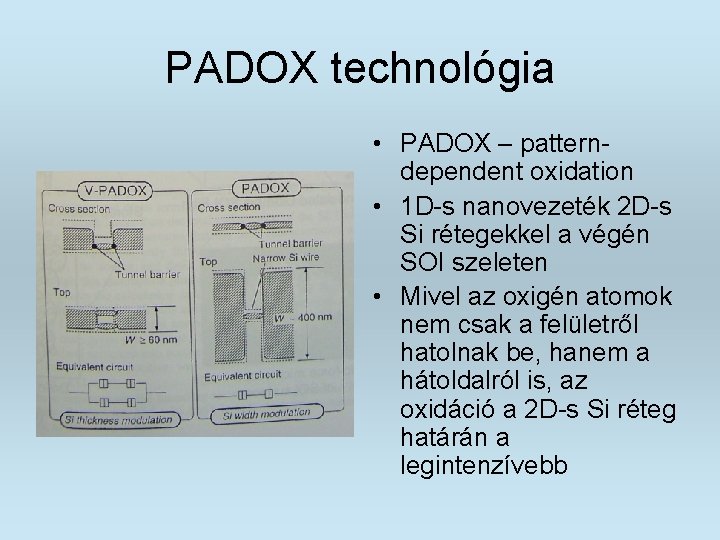

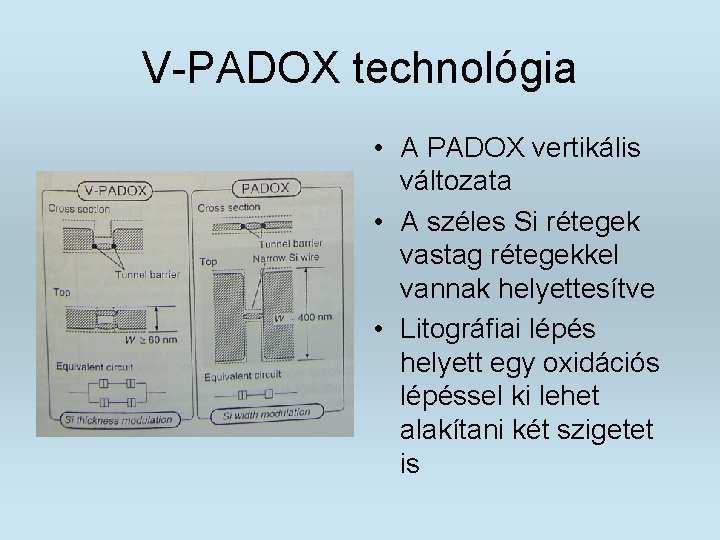

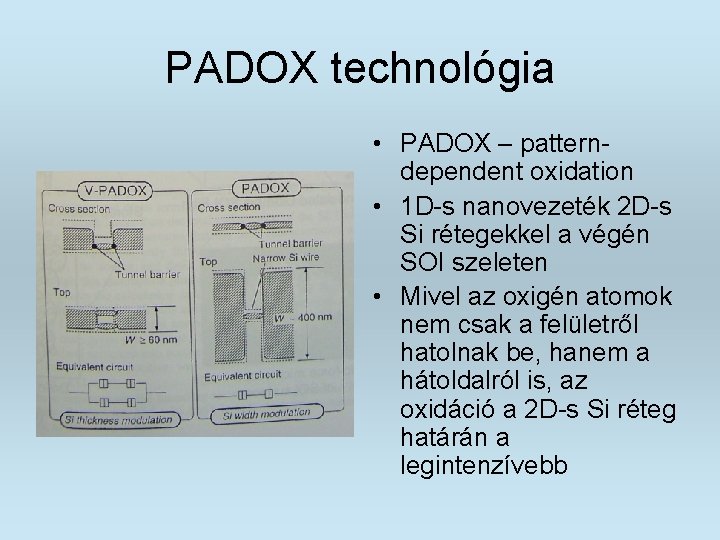

PADOX technológia • PADOX – patterndependent oxidation • 1 D-s nanovezeték 2 D-s Si rétegekkel a végén SOI szeleten • Mivel az oxigén atomok nem csak a felületről hatolnak be, hanem a hátoldalról is, az oxidáció a 2 D-s Si réteg határán a legintenzívebb

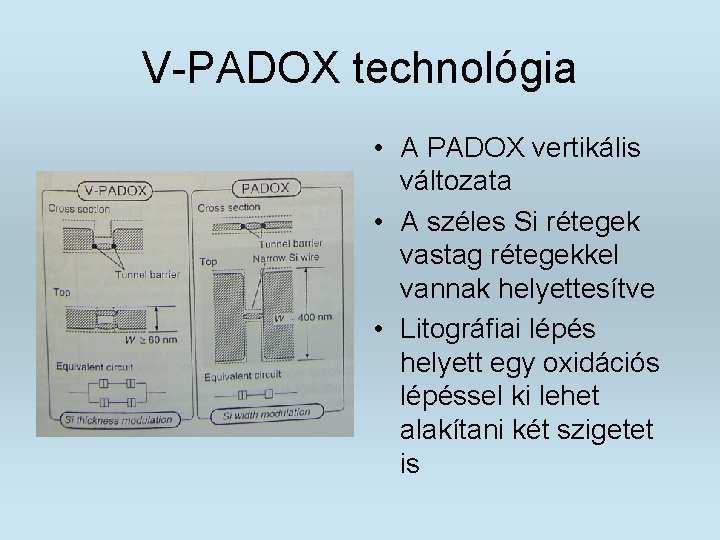

V-PADOX technológia • A PADOX vertikális változata • A széles Si rétegek vastag rétegekkel vannak helyettesítve • Litográfiai lépés helyett egy oxidációs lépéssel ki lehet alakítani két szigetet is

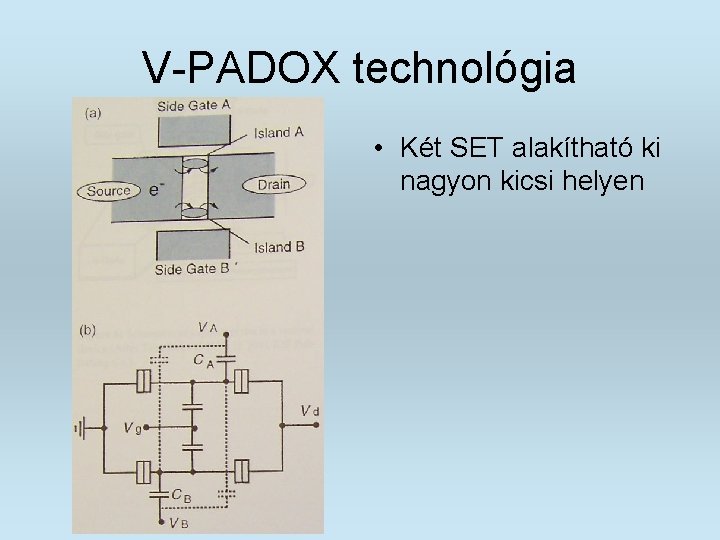

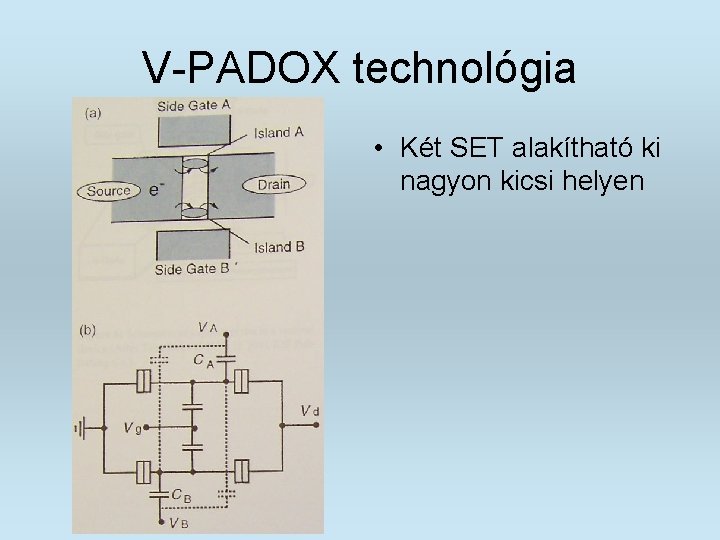

V-PADOX technológia • Két SET alakítható ki nagyon kicsi helyen

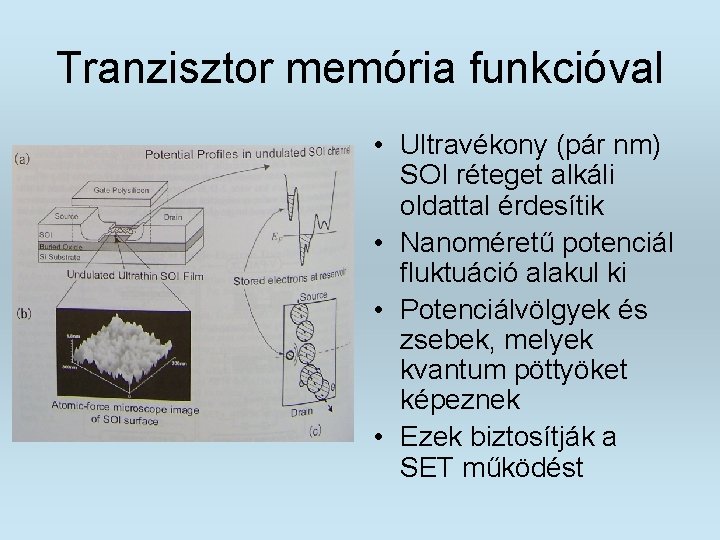

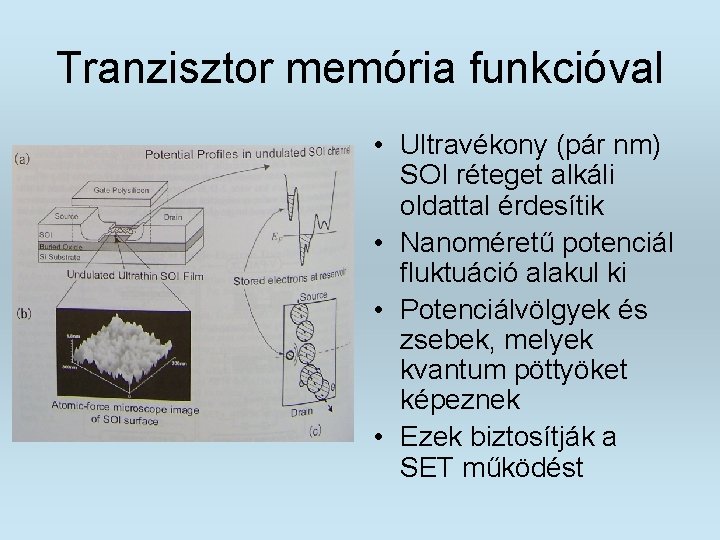

Tranzisztor memória funkcióval • Ultravékony (pár nm) SOI réteget alkáli oldattal érdesítik • Nanoméretű potenciál fluktuáció alakul ki • Potenciálvölgyek és zsebek, melyek kvantum pöttyöket képeznek • Ezek biztosítják a SET működést

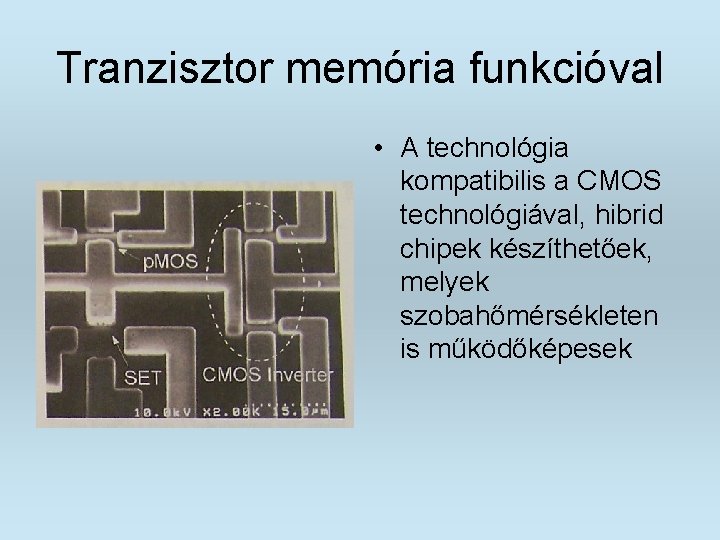

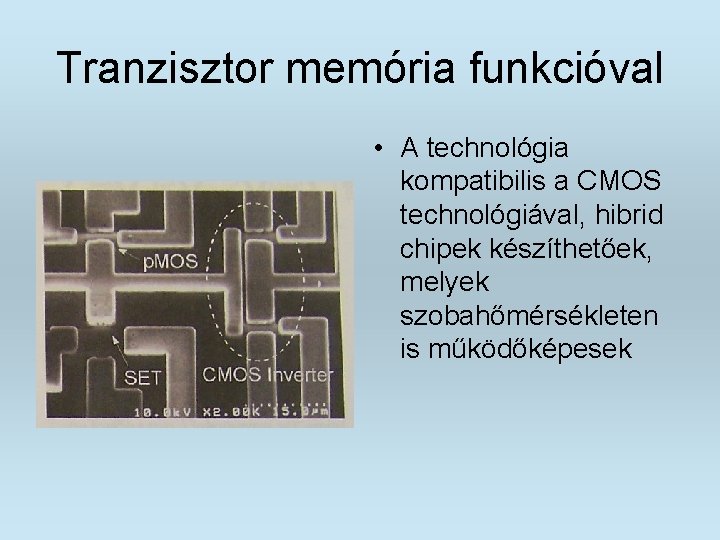

Tranzisztor memória funkcióval • A technológia kompatibilis a CMOS technológiával, hibrid chipek készíthetőek, melyek szobahőmérsékleten is működőképesek

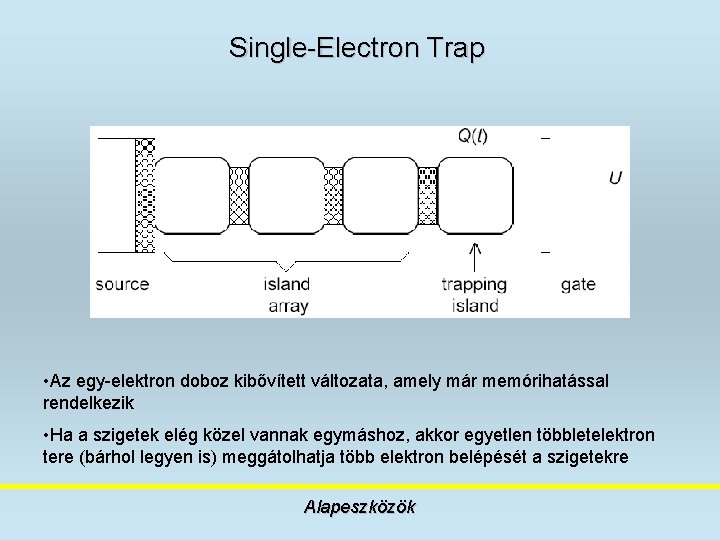

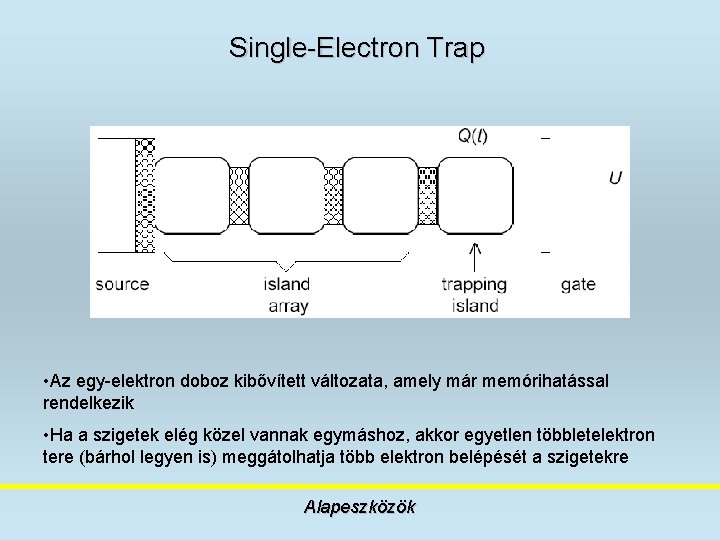

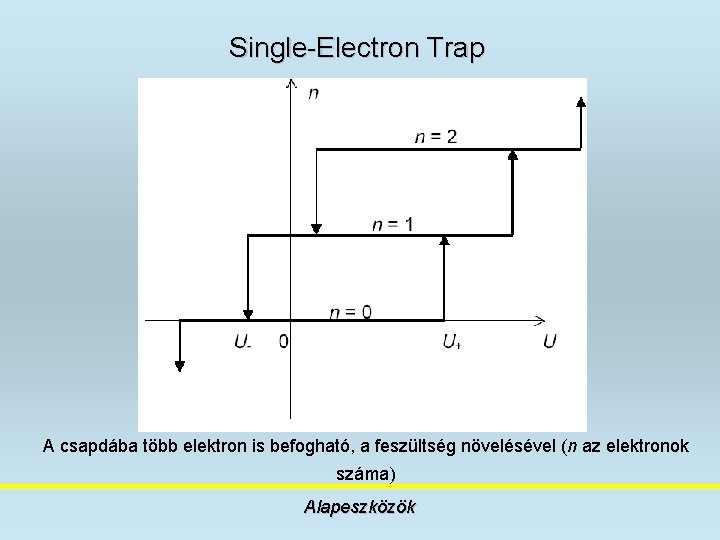

Single-Electron Trap • Az egy-elektron doboz kibővített változata, amely már memórihatással rendelkezik • Ha a szigetek elég közel vannak egymáshoz, akkor egyetlen többletelektron tere (bárhol legyen is) meggátolhatja több elektron belépését a szigetekre Alapeszközök

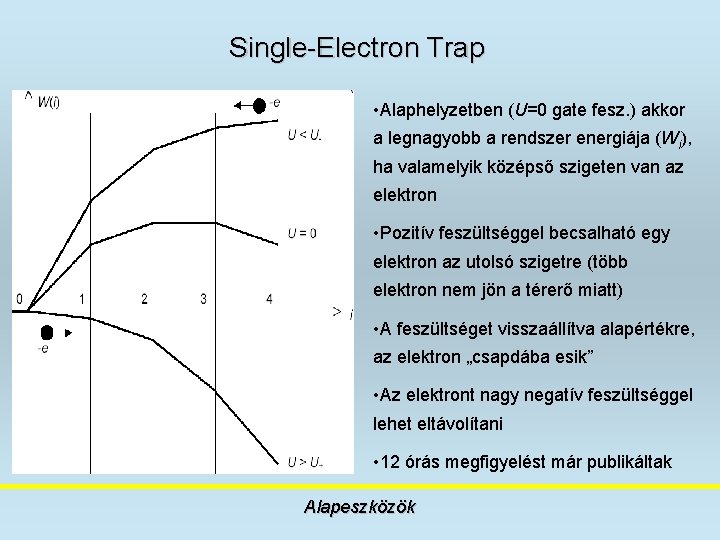

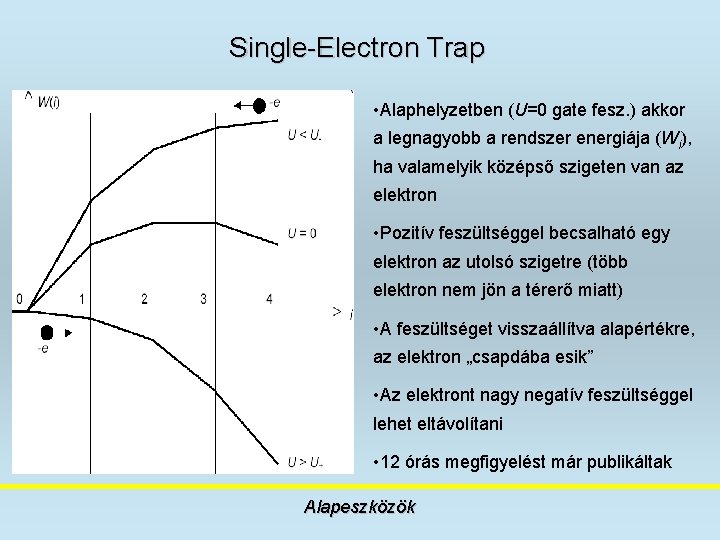

Single-Electron Trap • Alaphelyzetben (U=0 gate fesz. ) akkor a legnagyobb a rendszer energiája (Wi), ha valamelyik középső szigeten van az elektron • Pozitív feszültséggel becsalható egy elektron az utolsó szigetre (több elektron nem jön a térerő miatt) • A feszültséget visszaállítva alapértékre, az elektron „csapdába esik” • Az elektront nagy negatív feszültséggel lehet eltávolítani • 12 órás megfigyelést már publikáltak Alapeszközök

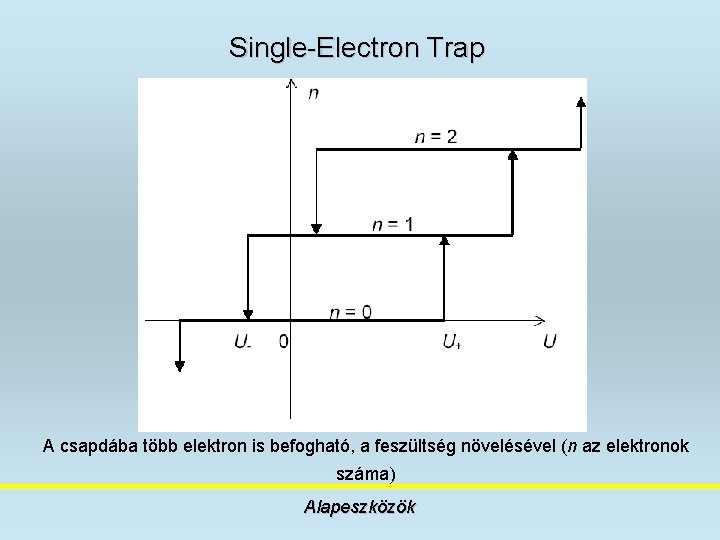

Single-Electron Trap A csapdába több elektron is befogható, a feszültség növelésével (n az elektronok száma) Alapeszközök

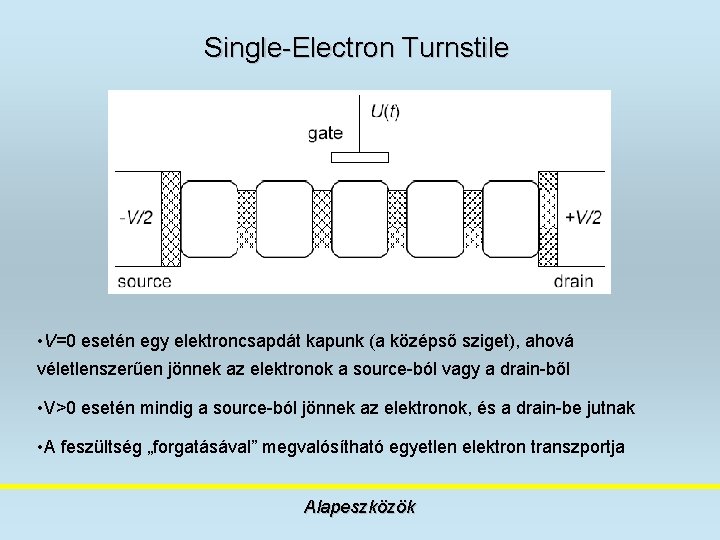

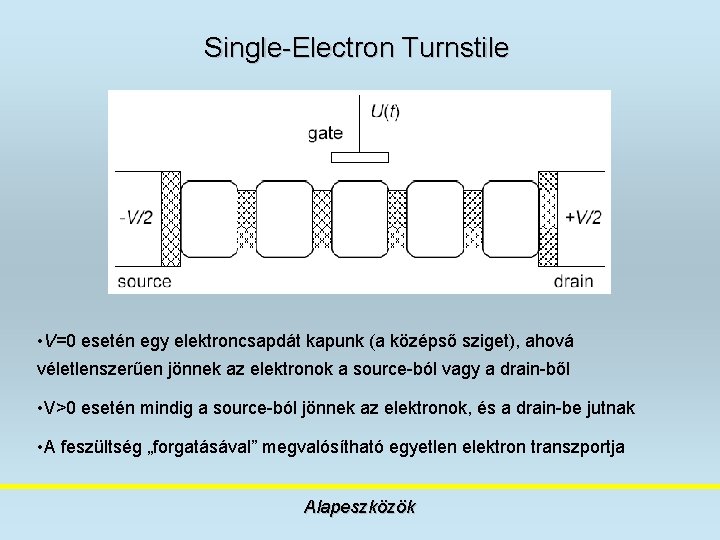

Single-Electron Turnstile • V=0 esetén egy elektroncsapdát kapunk (a középső sziget), ahová véletlenszerűen jönnek az elektronok a source-ból vagy a drain-ből • V>0 esetén mindig a source-ból jönnek az elektronok, és a drain-be jutnak • A feszültség „forgatásával” megvalósítható egyetlen elektron transzportja Alapeszközök

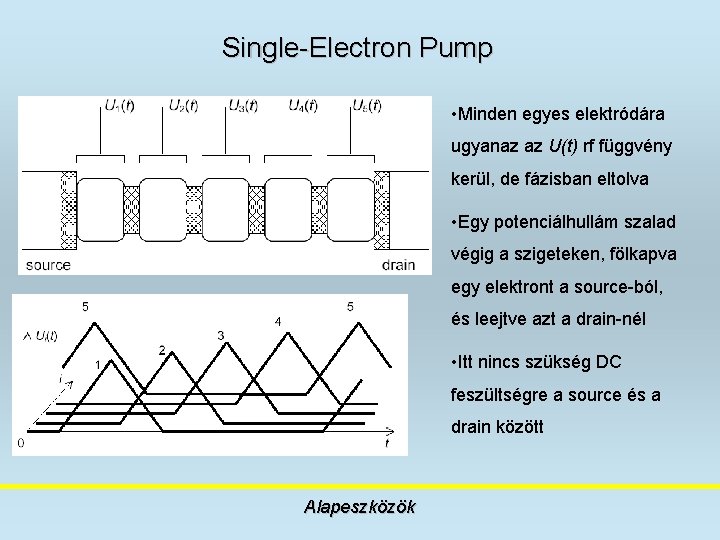

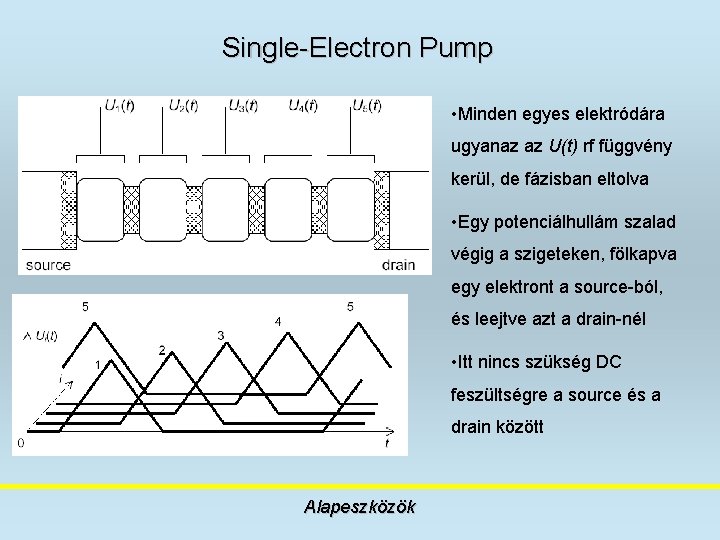

Single-Electron Pump • Minden egyes elektródára ugyanaz az U(t) rf függvény kerül, de fázisban eltolva • Egy potenciálhullám szalad végig a szigeteken, fölkapva egy elektront a source-ból, és leejtve azt a drain-nél • Itt nincs szükség DC feszültségre a source és a drain között Alapeszközök

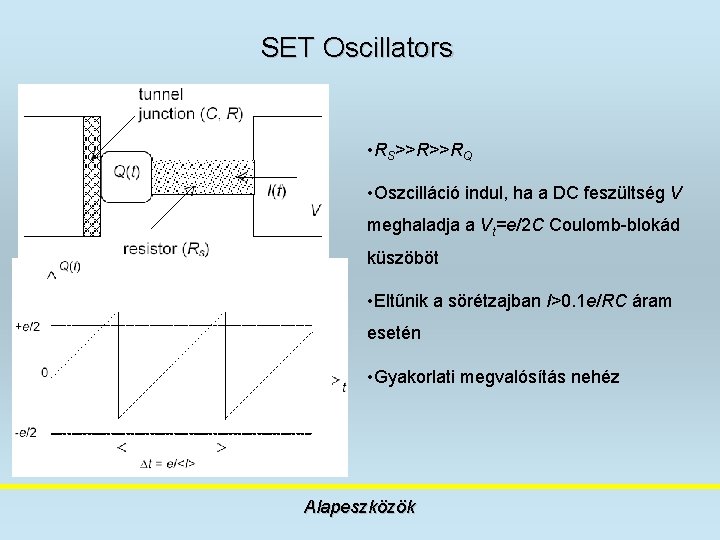

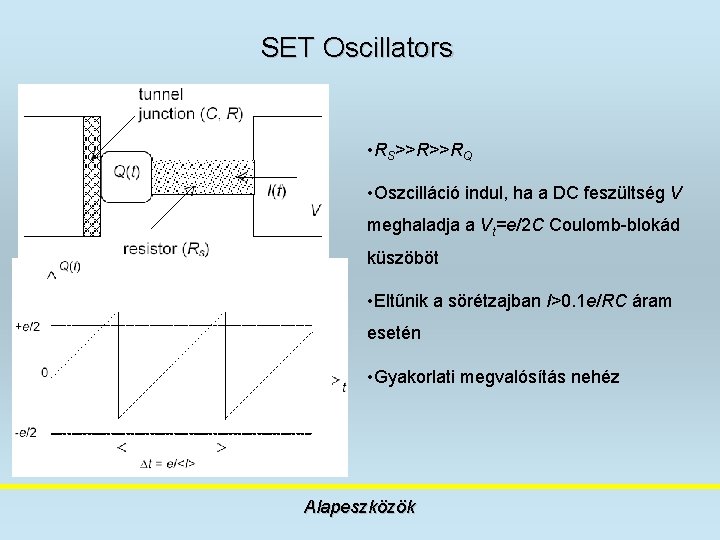

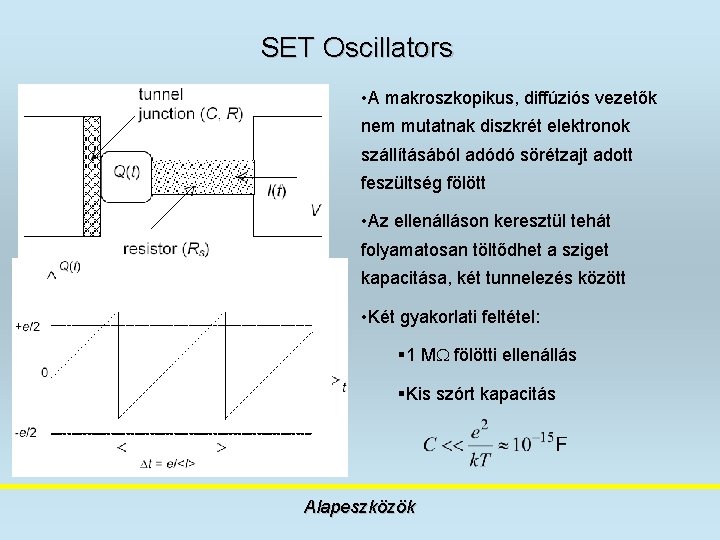

SET Oscillators • RS>>R>>RQ • Oszcilláció indul, ha a DC feszültség V meghaladja a Vt=e/2 C Coulomb-blokád küszöböt • Eltűnik a sörétzajban I>0. 1 e/RC áram esetén • Gyakorlati megvalósítás nehéz Alapeszközök

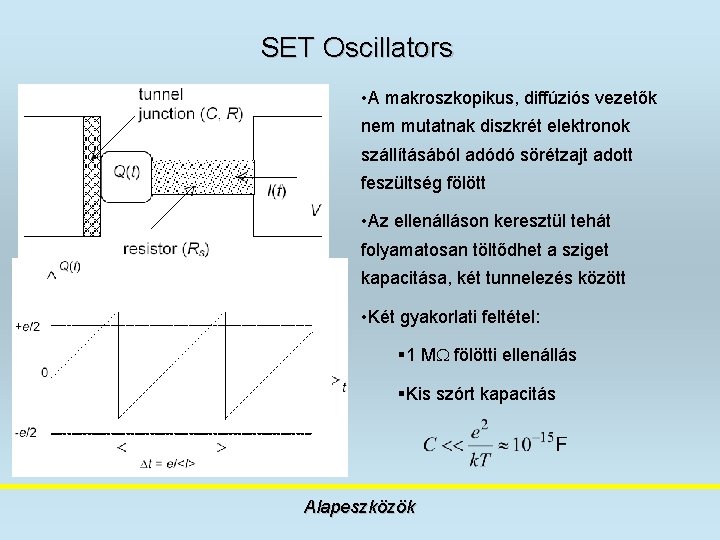

SET Oscillators • A makroszkopikus, diffúziós vezetők nem mutatnak diszkrét elektronok szállításából adódó sörétzajt adott feszültség fölött • Az ellenálláson keresztül tehát folyamatosan töltődhet a sziget kapacitása, két tunnelezés között • Két gyakorlati feltétel: § 1 M fölötti ellenállás §Kis szórt kapacitás Alapeszközök

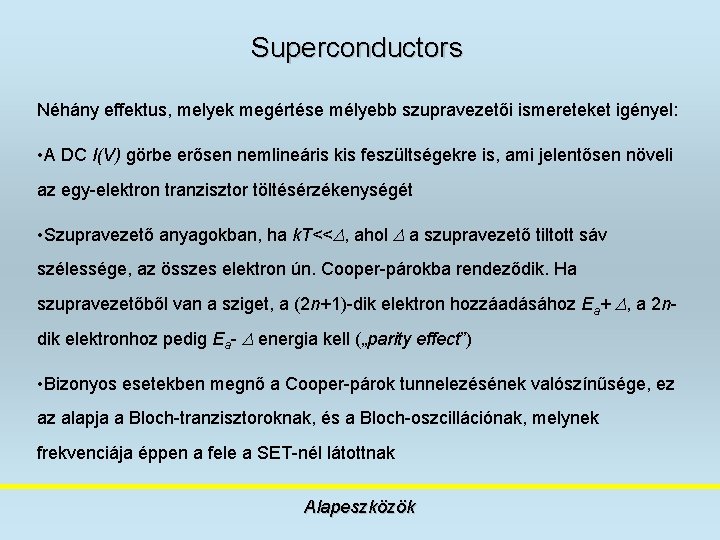

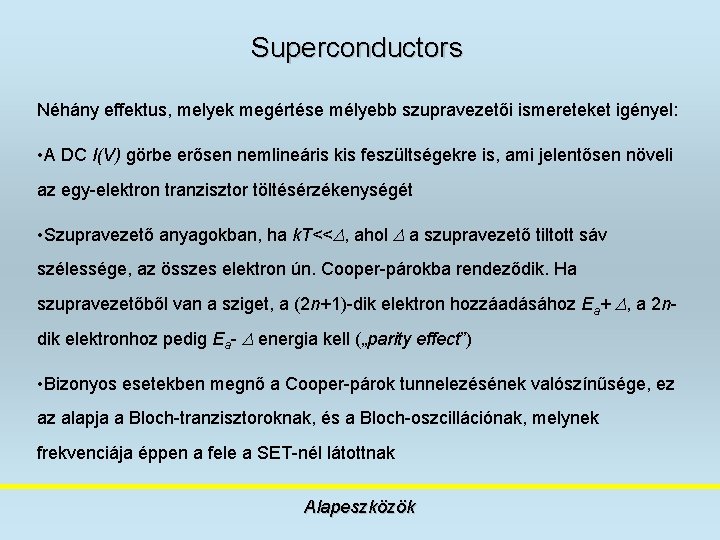

Superconductors Néhány effektus, melyek megértése mélyebb szupravezetői ismereteket igényel: • A DC I(V) görbe erősen nemlineáris kis feszültségekre is, ami jelentősen növeli az egy-elektron tranzisztor töltésérzékenységét • Szupravezető anyagokban, ha k. T<< , ahol a szupravezető tiltott sáv szélessége, az összes elektron ún. Cooper-párokba rendeződik. Ha szupravezetőből van a sziget, a (2 n+1)-dik elektron hozzáadásához Ea+ , a 2 ndik elektronhoz pedig Ea- energia kell („parity effect”) • Bizonyos esetekben megnő a Cooper-párok tunnelezésének valószínűsége, ez az alapja a Bloch-tranzisztoroknak, és a Bloch-oszcillációnak, melynek frekvenciája éppen a fele a SET-nél látottnak Alapeszközök

Analóg felhasználási területek • Szuperérzékeny elektrométer • Egy-elektron spektroszkópia • DC áramstandard • Hőmérsékleti standard • Ellenállás standard • Infravörös sugárzás érzékelése

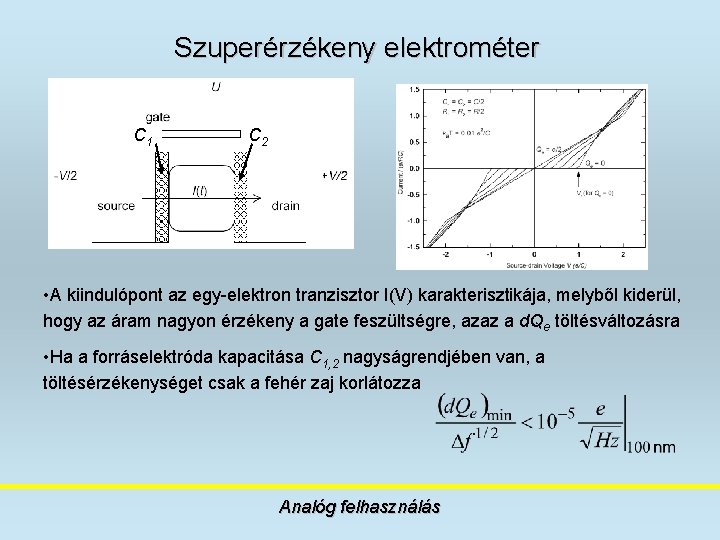

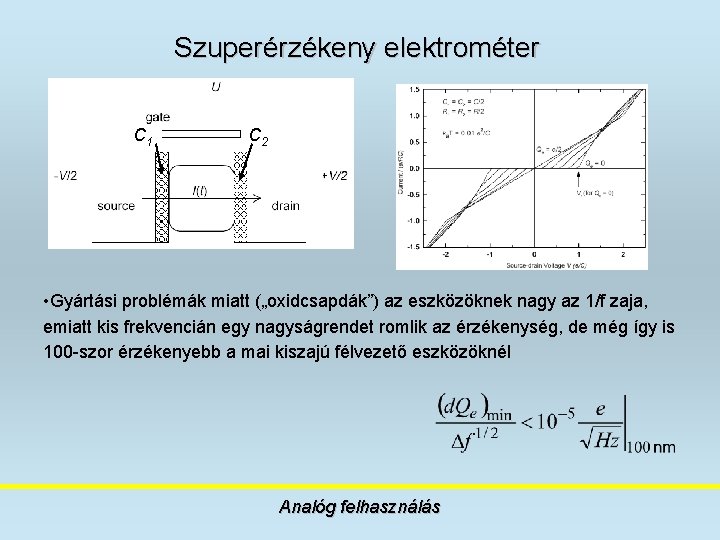

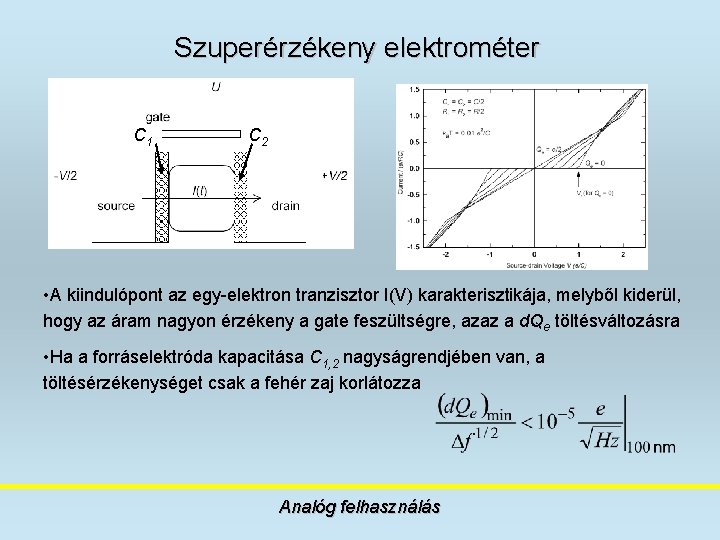

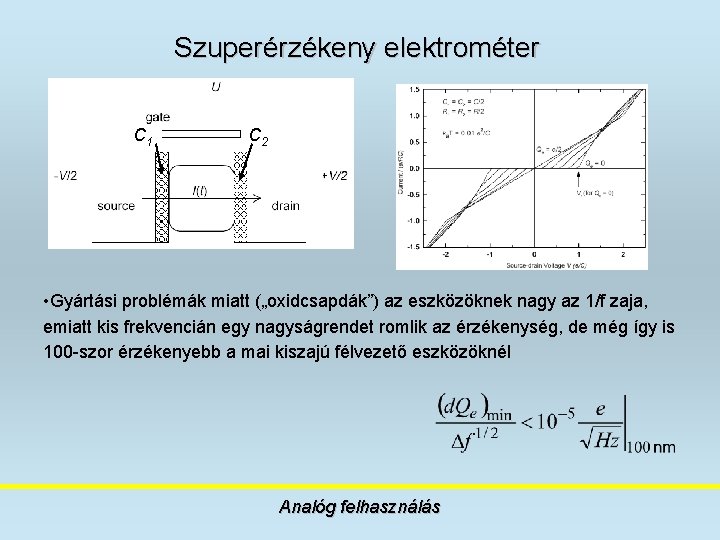

Szuperérzékeny elektrométer C 1 C 2 • A kiindulópont az egy-elektron tranzisztor I(V) karakterisztikája, melyből kiderül, hogy az áram nagyon érzékeny a gate feszültségre, azaz a d. Qe töltésváltozásra • Ha a forráselektróda kapacitása C 1, 2 nagyságrendjében van, a töltésérzékenységet csak a fehér zaj korlátozza Analóg felhasználás

Szuperérzékeny elektrométer C 1 C 2 • Gyártási problémák miatt („oxidcsapdák”) az eszközöknek nagy az 1/f zaja, emiatt kis frekvencián egy nagyságrendet romlik az érzékenység, de még így is 100 -szor érzékenyebb a mai kiszajú félvezető eszközöknél Analóg felhasználás

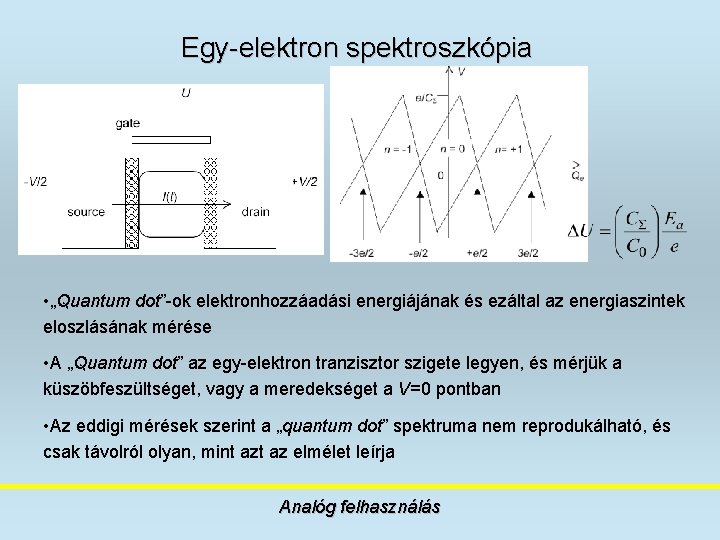

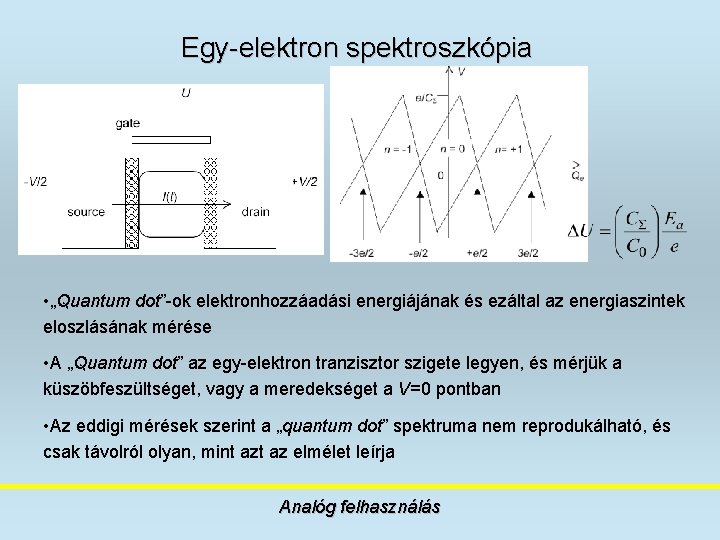

Egy-elektron spektroszkópia • „Quantum dot”-ok elektronhozzáadási energiájának és ezáltal az energiaszintek eloszlásának mérése • A „Quantum dot” az egy-elektron tranzisztor szigete legyen, és mérjük a küszöbfeszültséget, vagy a meredekséget a V=0 pontban • Az eddigi mérések szerint a „quantum dot” spektruma nem reprodukálható, és csak távolról olyan, mint az elmélet leírja Analóg felhasználás

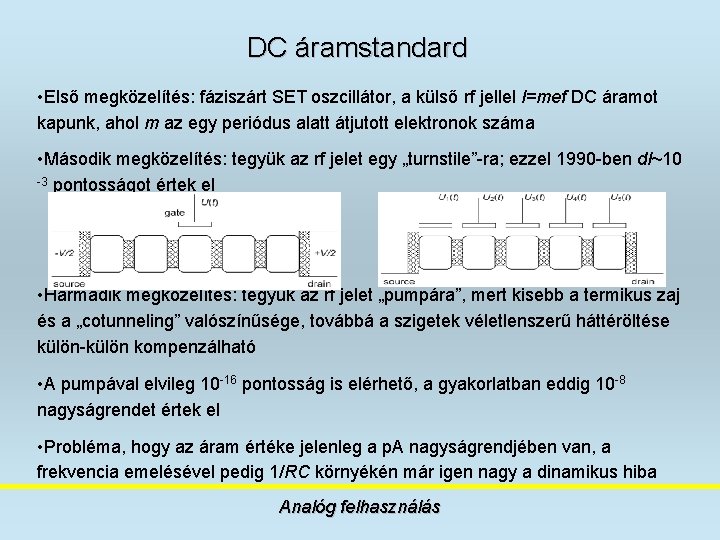

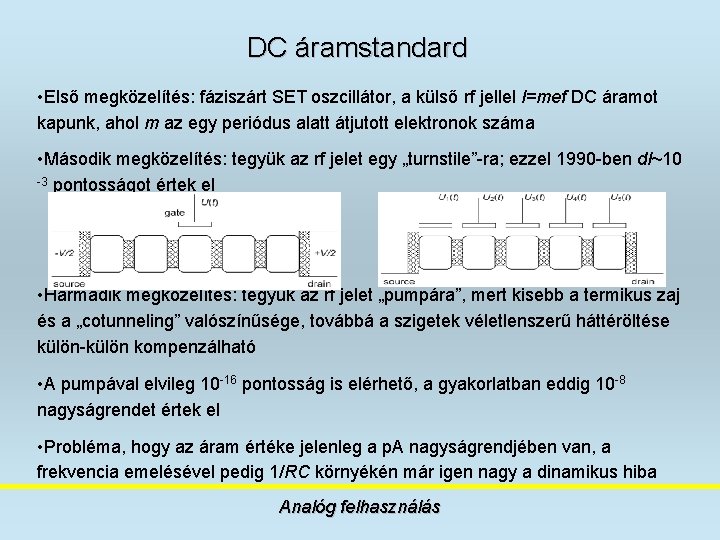

DC áramstandard • Első megközelítés: fáziszárt SET oszcillátor, a külső rf jellel I=mef DC áramot kapunk, ahol m az egy periódus alatt átjutott elektronok száma • Második megközelítés: tegyük az rf jelet egy „turnstile”-ra; ezzel 1990 -ben d. I~10 -3 pontosságot értek el • Harmadik megközelítés: tegyük az rf jelet „pumpára”, mert kisebb a termikus zaj és a „cotunneling” valószínűsége, továbbá a szigetek véletlenszerű háttéröltése külön-külön kompenzálható • A pumpával elvileg 10 -16 pontosság is elérhető, a gyakorlatban eddig 10 -8 nagyságrendet értek el • Probléma, hogy az áram értéke jelenleg a p. A nagyságrendjében van, a frekvencia emelésével pedig 1/RC környékén már igen nagy a dinamikus hiba Analóg felhasználás

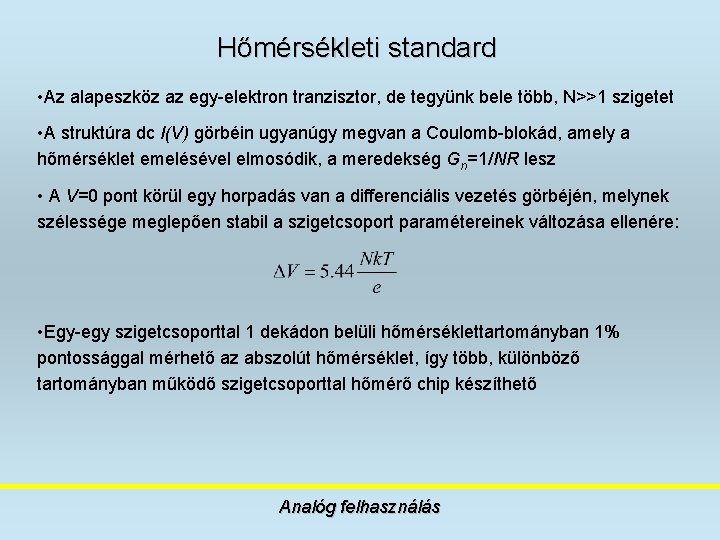

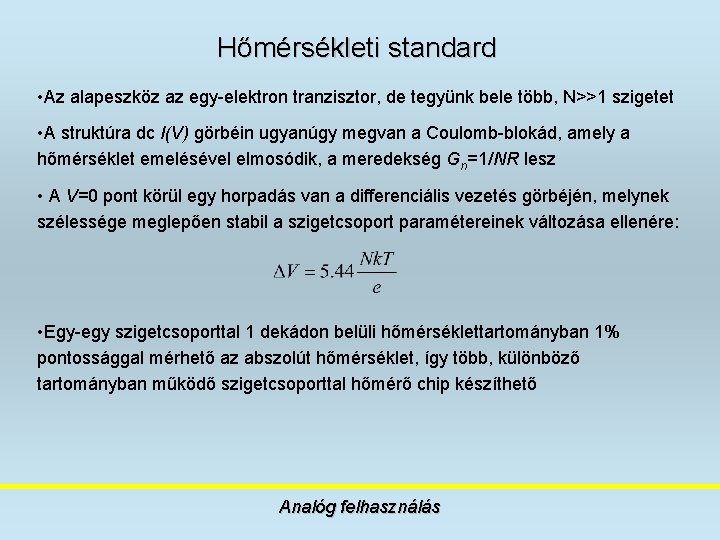

Hőmérsékleti standard • Az alapeszköz az egy-elektron tranzisztor, de tegyünk bele több, N>>1 szigetet • A struktúra dc I(V) görbéin ugyanúgy megvan a Coulomb-blokád, amely a hőmérséklet emelésével elmosódik, a meredekség Gn=1/NR lesz • A V=0 pont körül egy horpadás van a differenciális vezetés görbéjén, melynek szélessége meglepően stabil a szigetcsoport paramétereinek változása ellenére: • Egy-egy szigetcsoporttal 1 dekádon belüli hőmérséklettartományban 1% pontossággal mérhető az abszolút hőmérséklet, így több, különböző tartományban működő szigetcsoporttal hőmérő chip készíthető Analóg felhasználás

Digitális alkalmazások • Feszültségállapotos logikák • Töltésállapotos logikák • „SET Parametron” • Problémák, nehézségek • Háttértöltésre érzéketlen memória • Átmenetes szigetelő réteg („Crested” Tunnel Barrier) • Nemfelejtő RAM (NOVORAM) • Nagykapacitású elektrosztatikus adattárolás Digitális alkalmazás

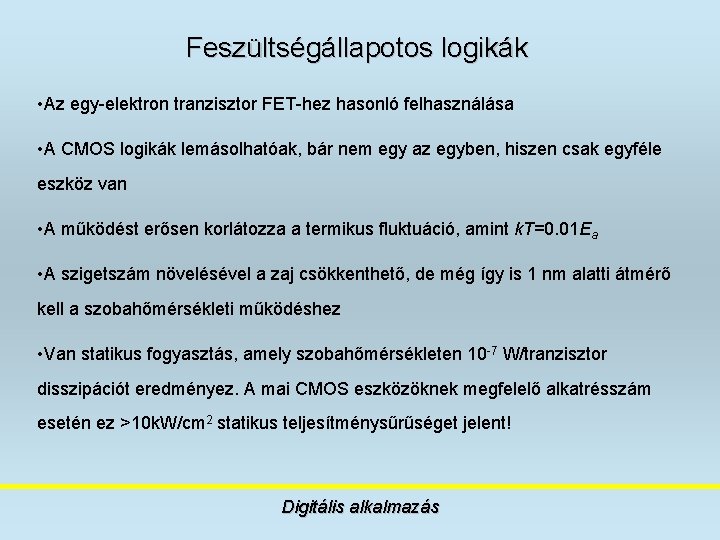

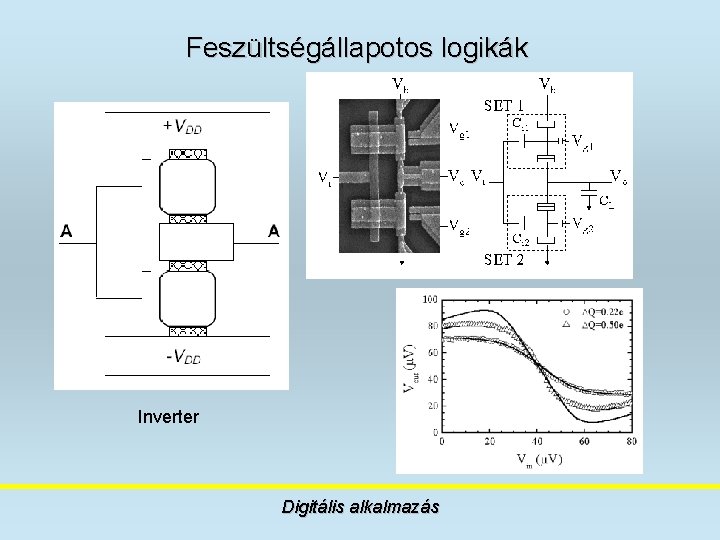

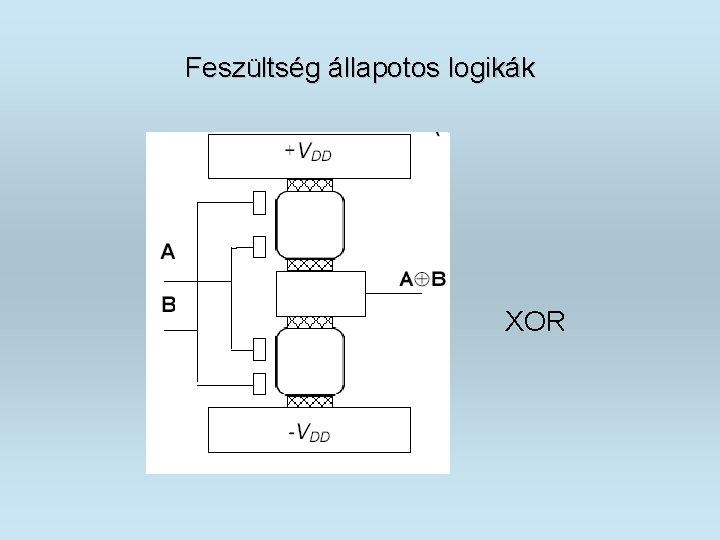

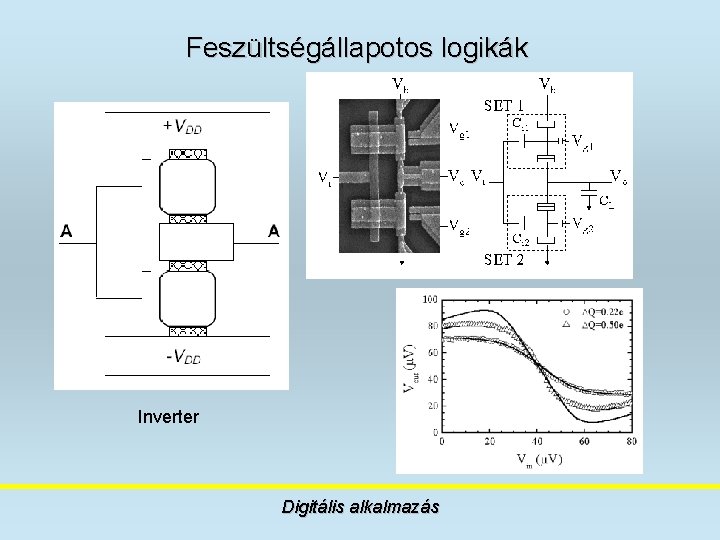

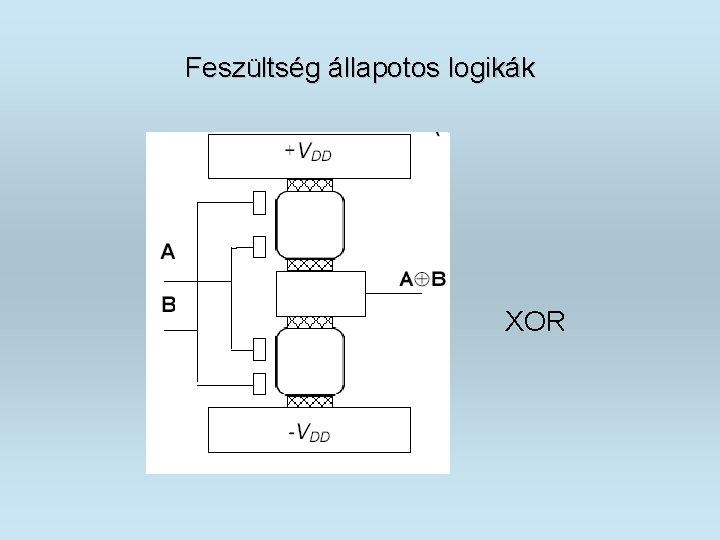

Feszültségállapotos logikák • Az egy-elektron tranzisztor FET-hez hasonló felhasználása • A CMOS logikák lemásolhatóak, bár nem egy az egyben, hiszen csak egyféle eszköz van • A működést erősen korlátozza a termikus fluktuáció, amint k. T=0. 01 Ea • A szigetszám növelésével a zaj csökkenthető, de még így is 1 nm alatti átmérő kell a szobahőmérsékleti működéshez • Van statikus fogyasztás, amely szobahőmérsékleten 10 -7 W/tranzisztor disszipációt eredményez. A mai CMOS eszközöknek megfelelő alkatrésszám esetén ez >10 k. W/cm 2 statikus teljesítménysűrűséget jelent! Digitális alkalmazás

Feszültségállapotos logikák Inverter Digitális alkalmazás

Feszültség állapotos logikák XOR

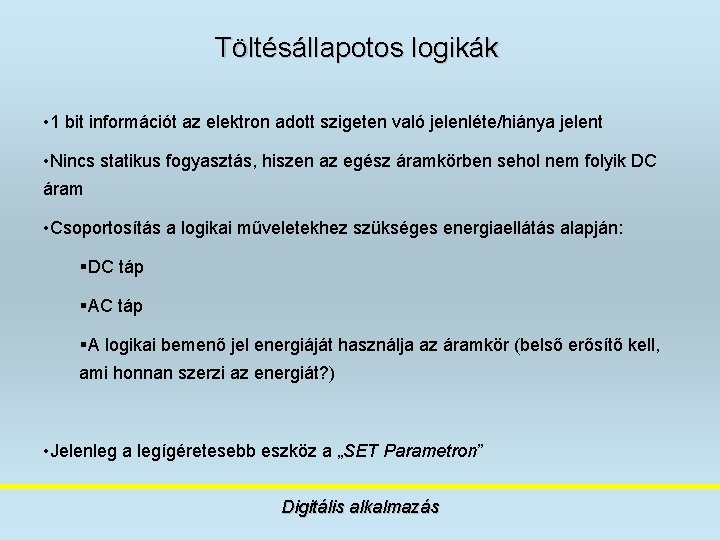

Töltésállapotos logikák • 1 bit információt az elektron adott szigeten való jelenléte/hiánya jelent • Nincs statikus fogyasztás, hiszen az egész áramkörben sehol nem folyik DC áram • Csoportosítás a logikai műveletekhez szükséges energiaellátás alapján: §DC táp §A logikai bemenő jel energiáját használja az áramkör (belső erősítő kell, ami honnan szerzi az energiát? ) • Jelenleg a legígéretesebb eszköz a „SET Parametron” Digitális alkalmazás

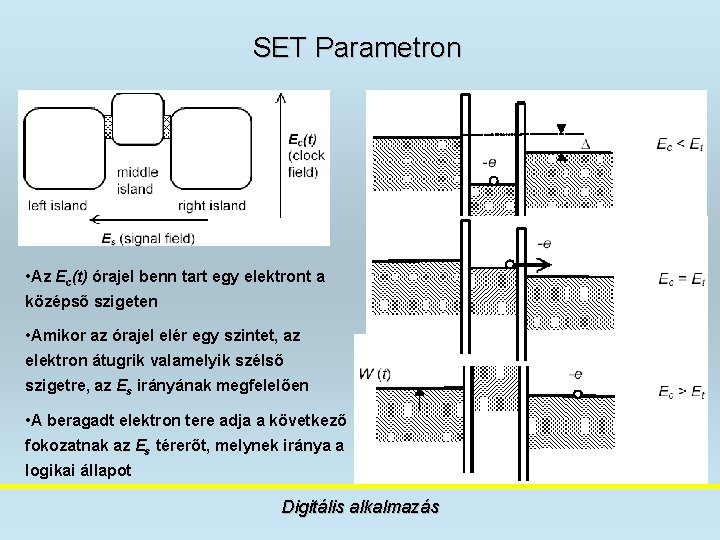

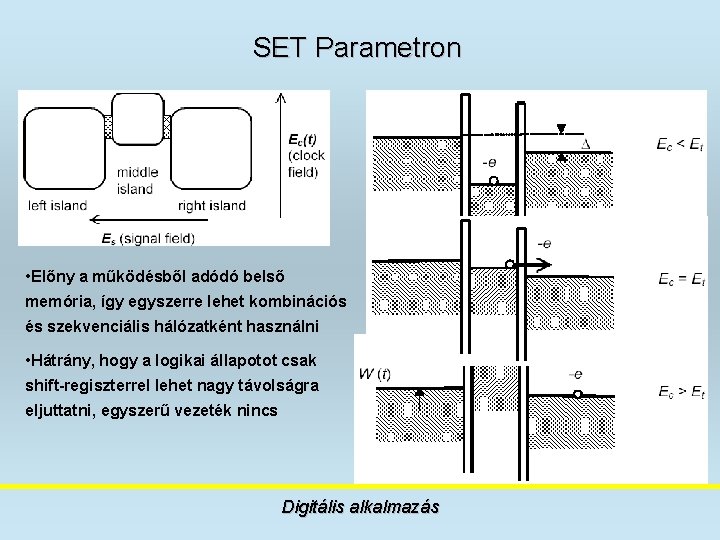

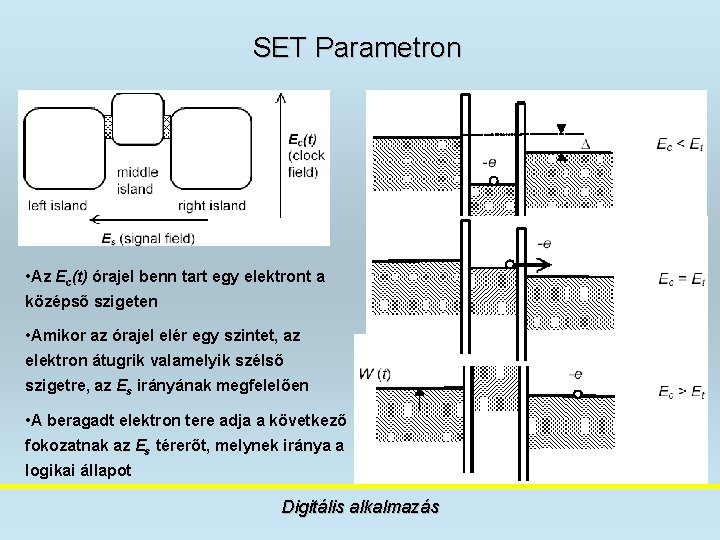

SET Parametron • Az Ec(t) órajel benn tart egy elektront a középső szigeten • Amikor az órajel elér egy szintet, az elektron átugrik valamelyik szélső szigetre, az Es irányának megfelelően • A beragadt elektron tere adja a következő fokozatnak az Es térerőt, melynek iránya a logikai állapot Digitális alkalmazás

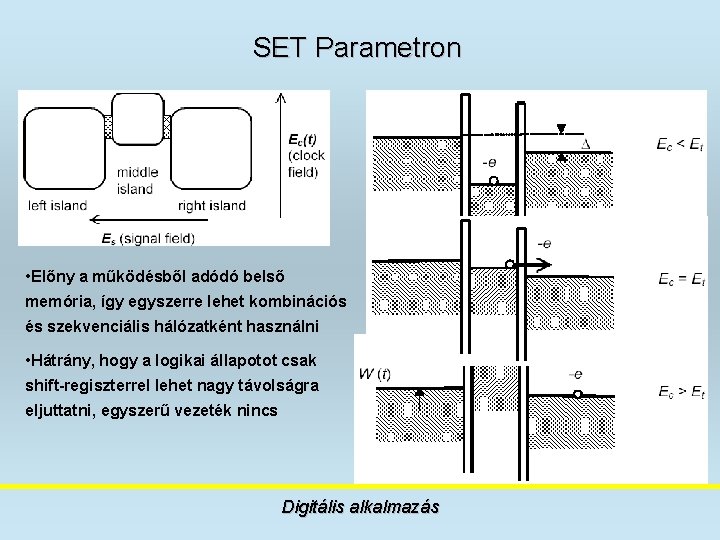

SET Parametron • Előny a működésből adódó belső memória, így egyszerre lehet kombinációs és szekvenciális hálózatként használni • Hátrány, hogy a logikai állapotot csak shift-regiszterrel lehet nagy távolságra eljuttatni, egyszerű vezeték nincs Digitális alkalmazás

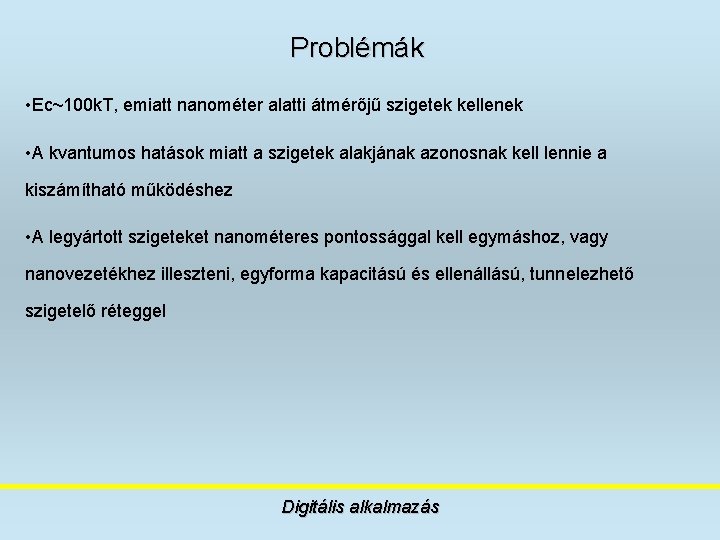

Problémák • Ec~100 k. T, emiatt nanométer alatti átmérőjű szigetek kellenek • A kvantumos hatások miatt a szigetek alakjának azonosnak kell lennie a kiszámítható működéshez • A legyártott szigeteket nanométeres pontossággal kell egymáshoz, vagy nanovezetékhez illeszteni, egyforma kapacitású és ellenállású, tunnelezhető szigetelő réteggel Digitális alkalmazás

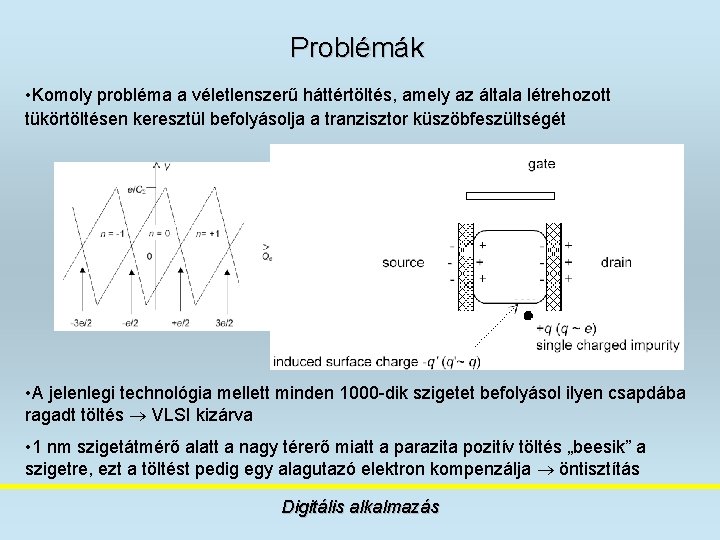

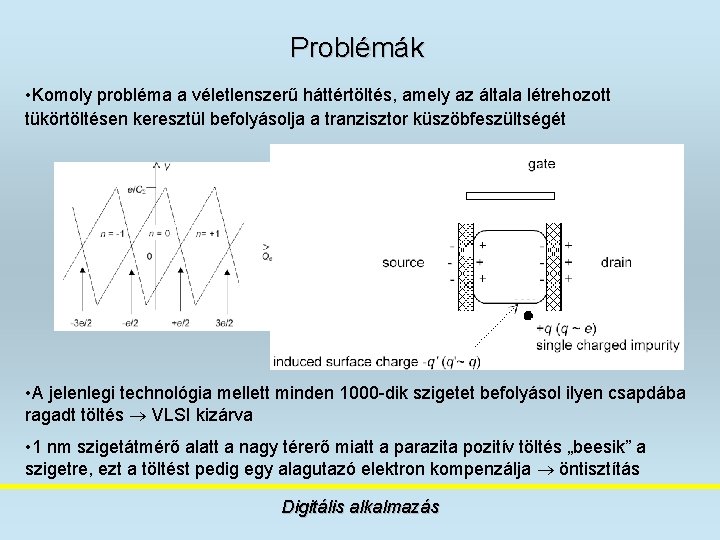

Problémák • Komoly probléma a véletlenszerű háttértöltés, amely az általa létrehozott tükörtöltésen keresztül befolyásolja a tranzisztor küszöbfeszültségét • A jelenlegi technológia mellett minden 1000 -dik szigetet befolyásol ilyen csapdába ragadt töltés VLSI kizárva • 1 nm szigetátmérő alatt a nagy térerő miatt a parazita pozitív töltés „beesik” a szigetre, ezt a töltést pedig egy alagutazó elektron kompenzálja öntisztítás Digitális alkalmazás

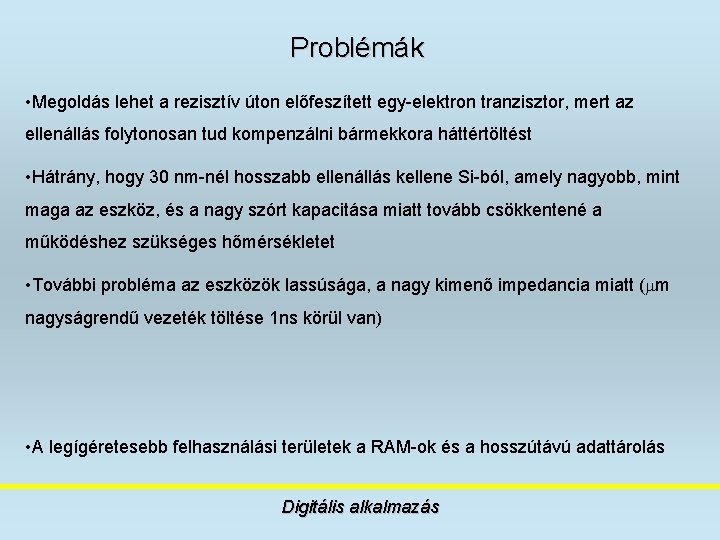

Problémák • Megoldás lehet a rezisztív úton előfeszített egy-elektron tranzisztor, mert az ellenállás folytonosan tud kompenzálni bármekkora háttértöltést • Hátrány, hogy 30 nm-nél hosszabb ellenállás kellene Si-ból, amely nagyobb, mint maga az eszköz, és a nagy szórt kapacitása miatt tovább csökkentené a működéshez szükséges hőmérsékletet • További probléma az eszközök lassúsága, a nagy kimenő impedancia miatt ( m nagyságrendű vezeték töltése 1 ns körül van) • A legígéretesebb felhasználási területek a RAM-ok és a hosszútávú adattárolás Digitális alkalmazás

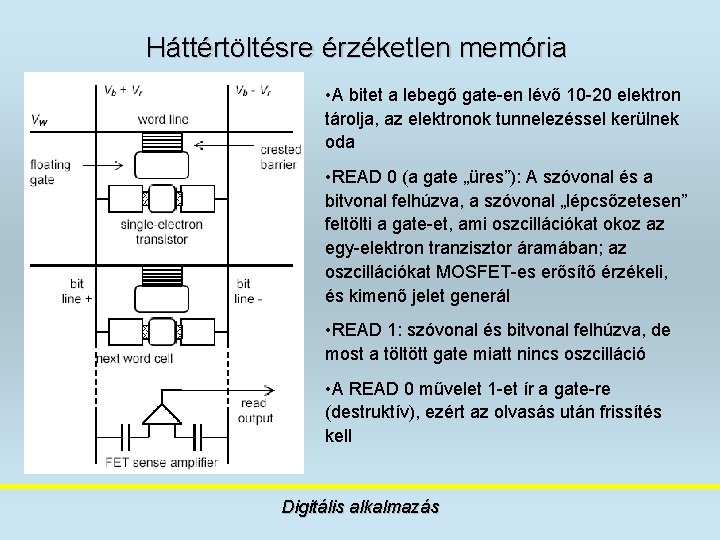

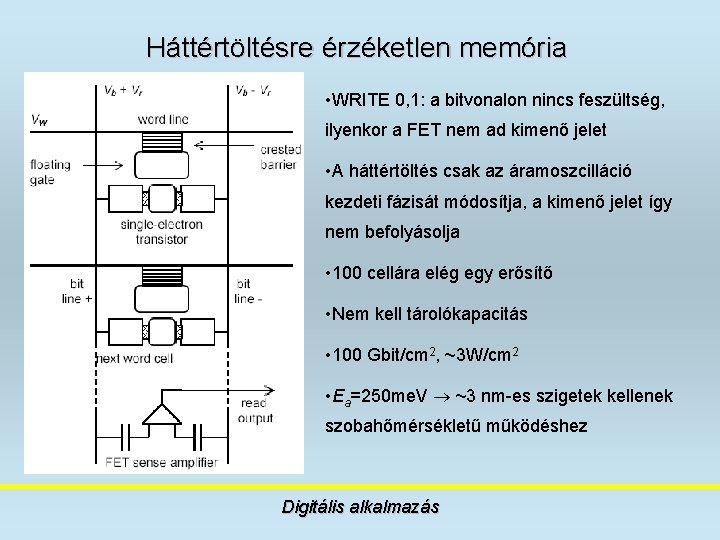

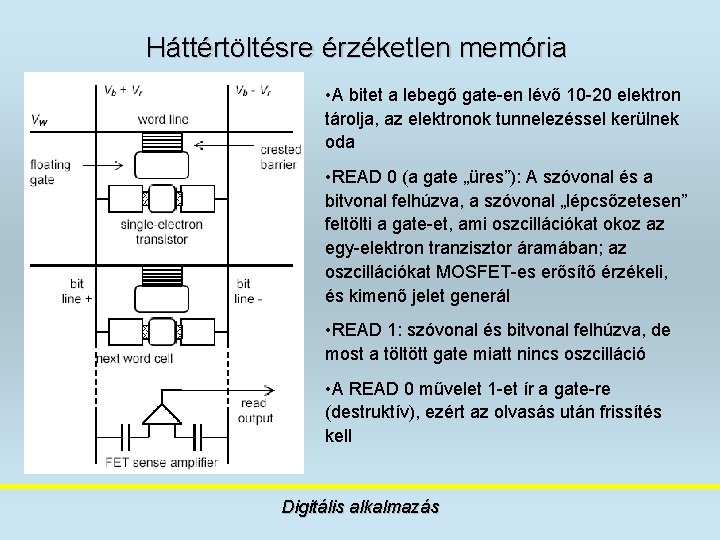

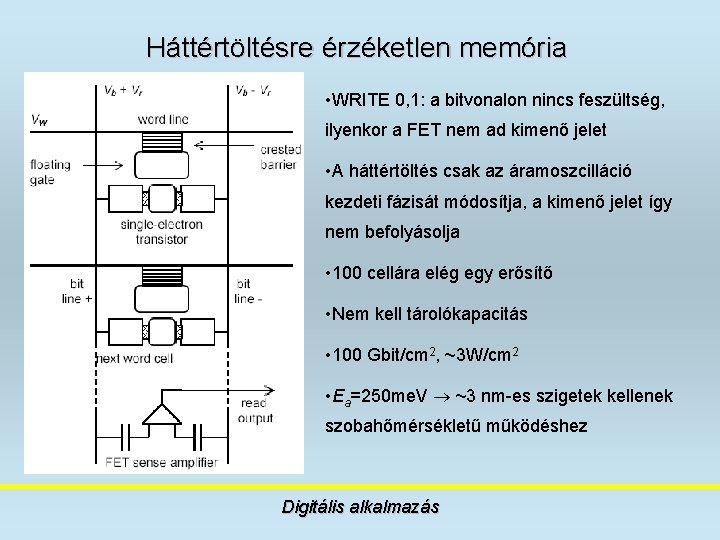

Háttértöltésre érzéketlen memória • A bitet a lebegő gate-en lévő 10 -20 elektron tárolja, az elektronok tunnelezéssel kerülnek oda • READ 0 (a gate „üres”): A szóvonal és a bitvonal felhúzva, a szóvonal „lépcsőzetesen” feltölti a gate-et, ami oszcillációkat okoz az egy-elektron tranzisztor áramában; az oszcillációkat MOSFET-es erősítő érzékeli, és kimenő jelet generál • READ 1: szóvonal és bitvonal felhúzva, de most a töltött gate miatt nincs oszcilláció • A READ 0 művelet 1 -et ír a gate-re (destruktív), ezért az olvasás után frissítés kell Digitális alkalmazás

Háttértöltésre érzéketlen memória • WRITE 0, 1: a bitvonalon nincs feszültség, ilyenkor a FET nem ad kimenő jelet • A háttértöltés csak az áramoszcilláció kezdeti fázisát módosítja, a kimenő jelet így nem befolyásolja • 100 cellára elég egy erősítő • Nem kell tárolókapacitás • 100 Gbit/cm 2, ~3 W/cm 2 • Ea=250 me. V ~3 nm-es szigetek kellenek szobahőmérsékletű működéshez Digitális alkalmazás

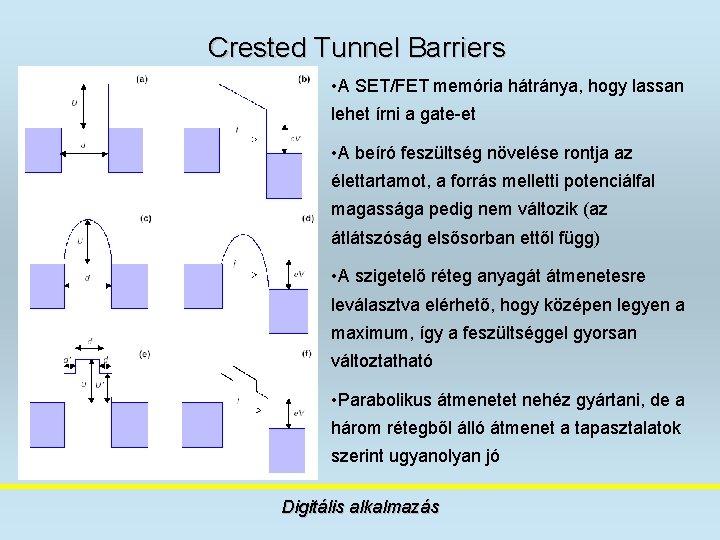

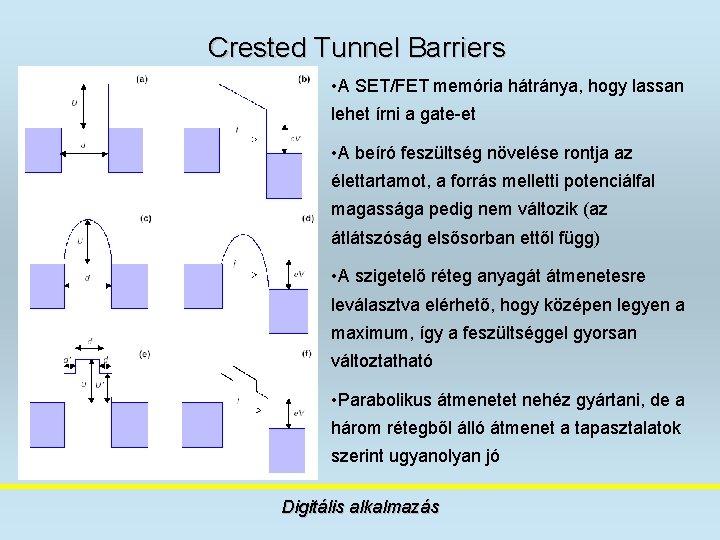

Crested Tunnel Barriers • A SET/FET memória hátránya, hogy lassan lehet írni a gate-et • A beíró feszültség növelése rontja az élettartamot, a forrás melletti potenciálfal magassága pedig nem változik (az átlátszóság elsősorban ettől függ) • A szigetelő réteg anyagát átmenetesre leválasztva elérhető, hogy középen legyen a maximum, így a feszültséggel gyorsan változtatható • Parabolikus átmenetet nehéz gyártani, de a három rétegből álló átmenet a tapasztalatok szerint ugyanolyan jó Digitális alkalmazás

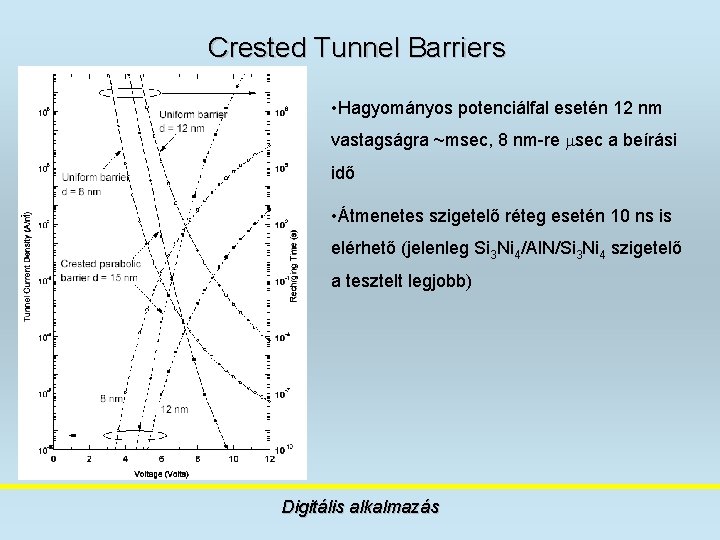

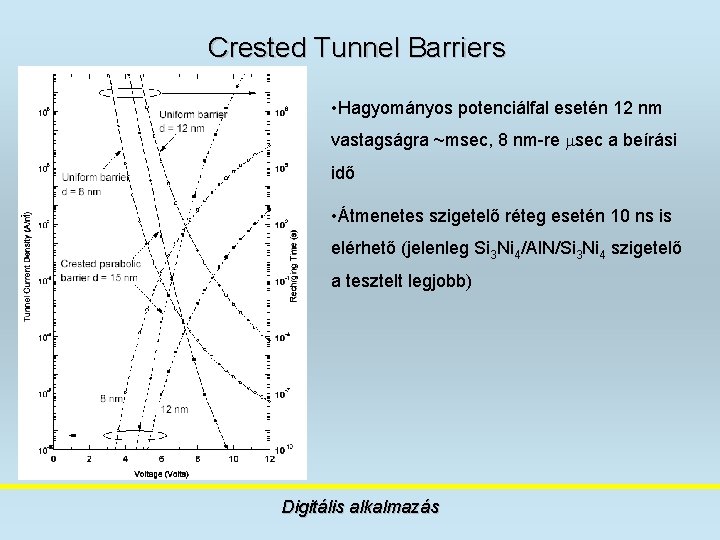

Crested Tunnel Barriers • Hagyományos potenciálfal esetén 12 nm vastagságra ~msec, 8 nm-re sec a beírási idő • Átmenetes szigetelő réteg esetén 10 ns is elérhető (jelenleg Si 3 Ni 4/Al. N/Si 3 Ni 4 szigetelő a tesztelt legjobb) Digitális alkalmazás

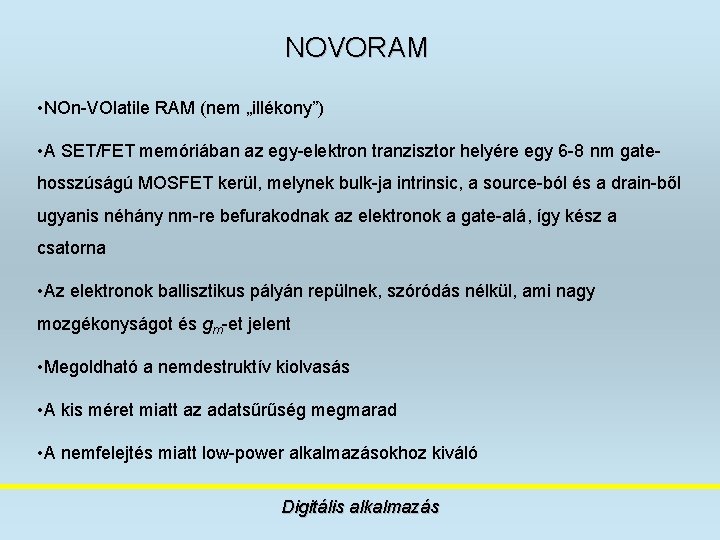

NOVORAM • NOn-VOlatile RAM (nem „illékony”) • A SET/FET memóriában az egy-elektron tranzisztor helyére egy 6 -8 nm gatehosszúságú MOSFET kerül, melynek bulk-ja intrinsic, a source-ból és a drain-ből ugyanis néhány nm-re befurakodnak az elektronok a gate-alá, így kész a csatorna • Az elektronok ballisztikus pályán repülnek, szóródás nélkül, ami nagy mozgékonyságot és gm-et jelent • Megoldható a nemdestruktív kiolvasás • A kis méret miatt az adatsűrűség megmarad • A nemfelejtés miatt low-power alkalmazásokhoz kiváló Digitális alkalmazás

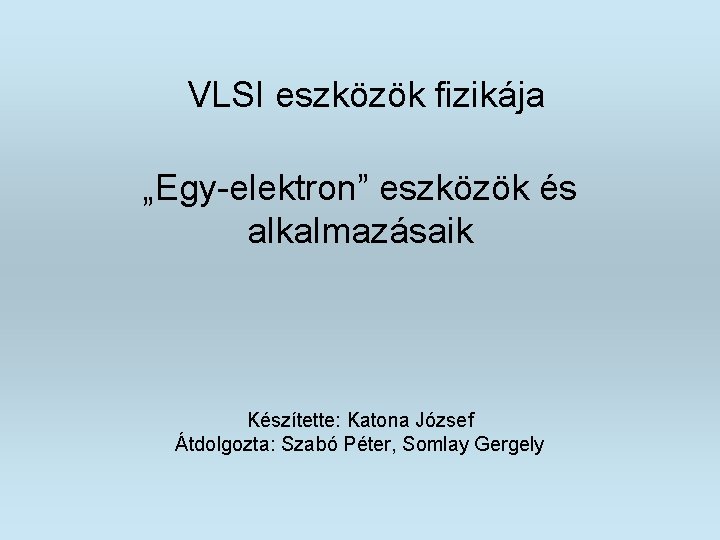

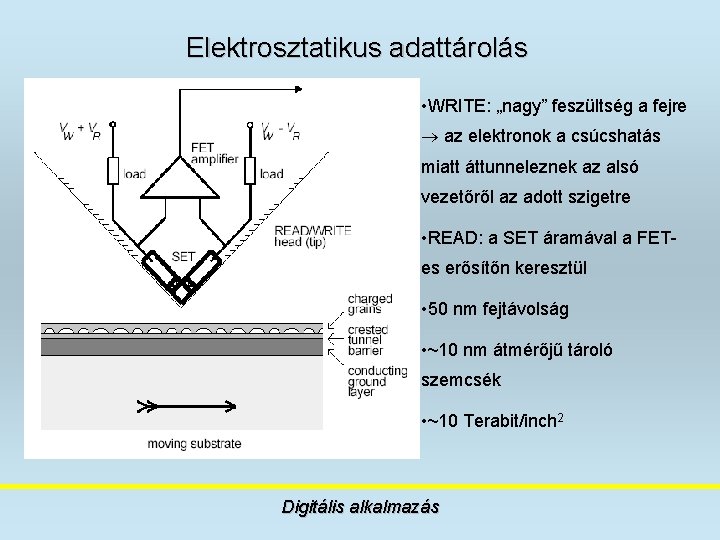

Elektrosztatikus adattárolás • WRITE: „nagy” feszültség a fejre az elektronok a csúcshatás miatt áttunneleznek az alsó vezetőről az adott szigetre • READ: a SET áramával a FETes erősítőn keresztül • 50 nm fejtávolság • ~10 nm átmérőjű tároló szemcsék • ~10 Terabit/inch 2 Digitális alkalmazás