VLSI Design Lecture 4 a Layout Extraction Mohammad

- Slides: 35

VLSI Design Lecture 4 -a: Layout Extraction Mohammad Arjomand CE Department Sharif Univ. of Tech. Adapted with modifications from Harris’s lecture notes

Topics SCMOS scalable design rules. n Reliability. n Stick diagrams. n Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

MOSIS SCMOS design rules Designed to scale across a wide range of technologies. n Designed to support multiple vendors. n Designed for educational use. n Ergo, fairly conservative. n Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

and design rules is the size of a minimum feature. n Specifying particularizes the scalable rules. n Parasitics are generally not specified in units n Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

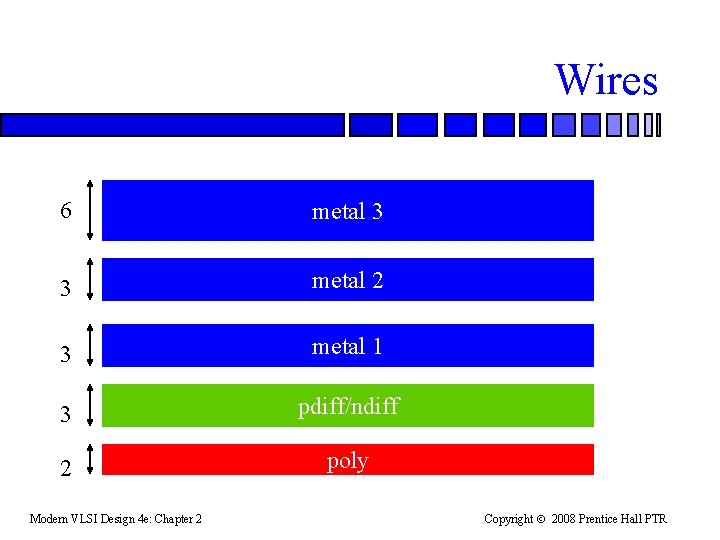

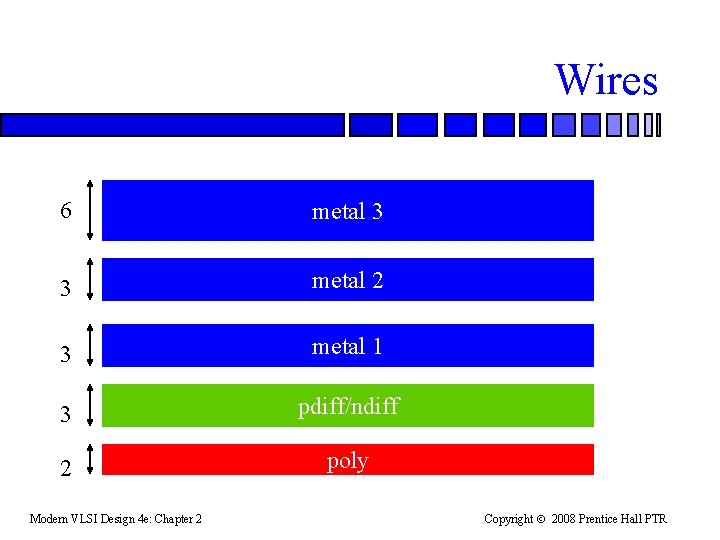

Wires 6 metal 3 3 metal 2 3 metal 1 3 pdiff/ndiff 2 poly Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

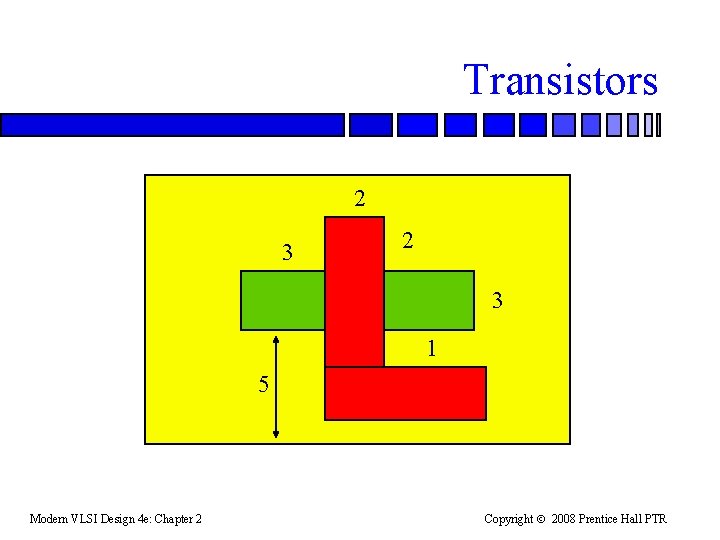

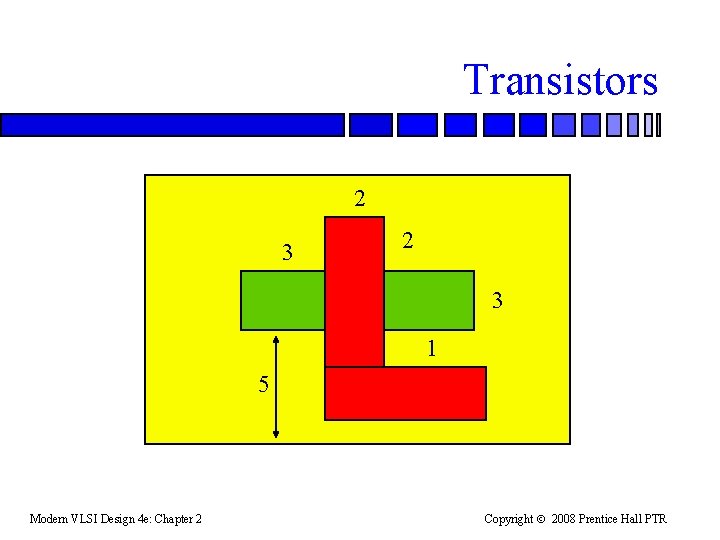

Transistors 2 3 1 5 Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

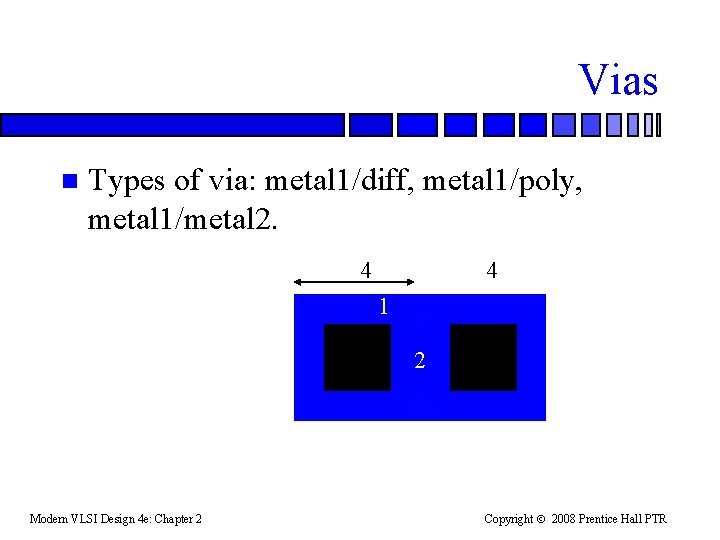

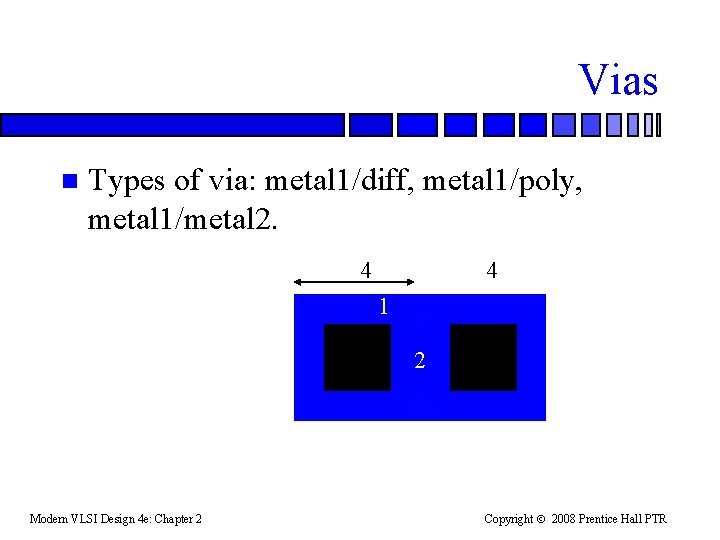

Vias n Types of via: metal 1/diff, metal 1/poly, metal 1/metal 2. 4 4 1 2 Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

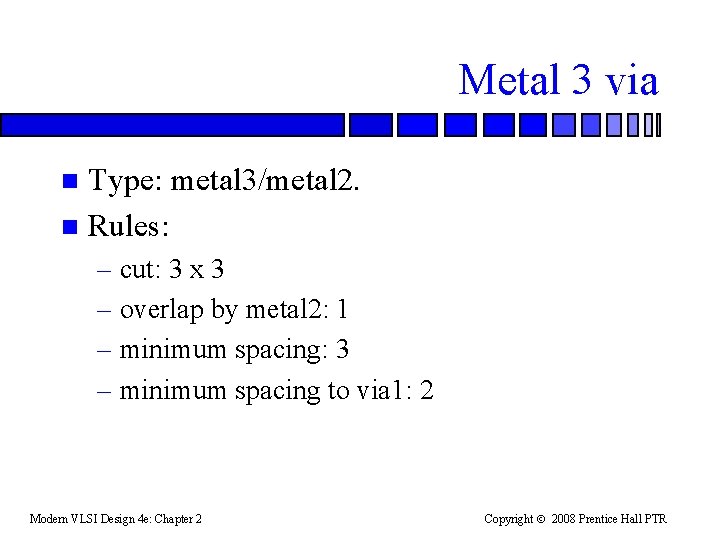

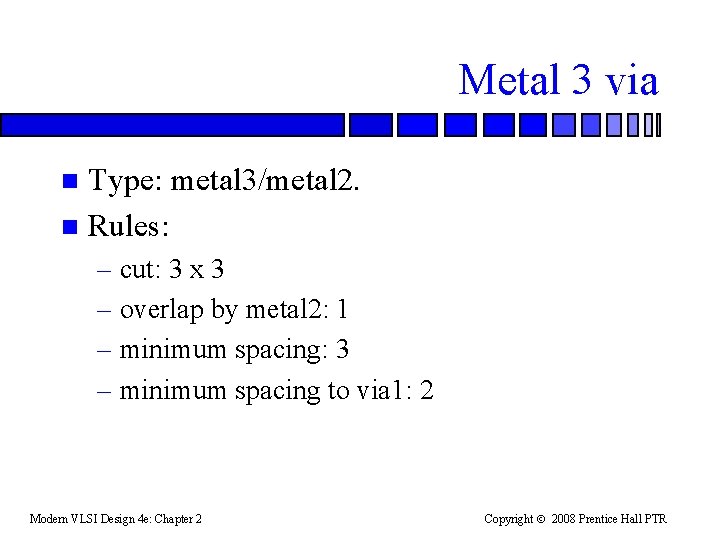

Metal 3 via Type: metal 3/metal 2. n Rules: n – cut: 3 x 3 – overlap by metal 2: 1 – minimum spacing: 3 – minimum spacing to via 1: 2 Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

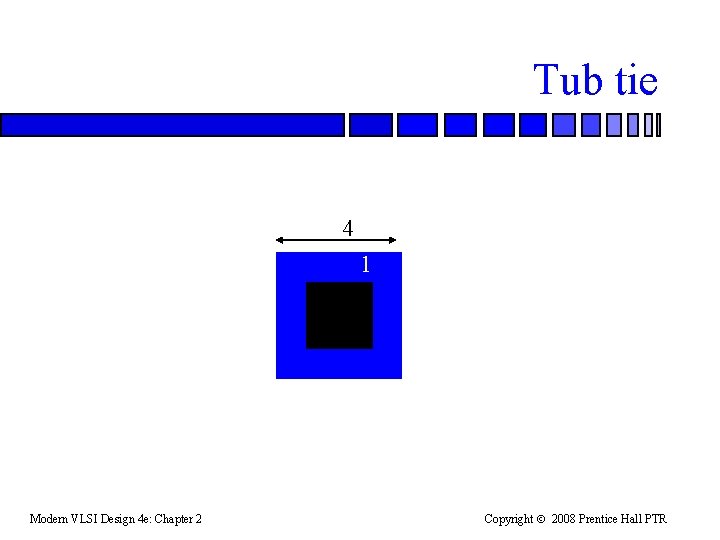

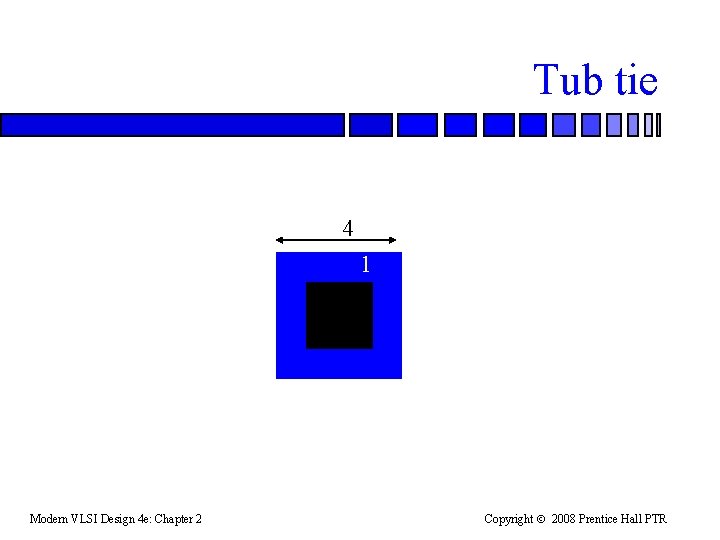

Tub tie 4 1 Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

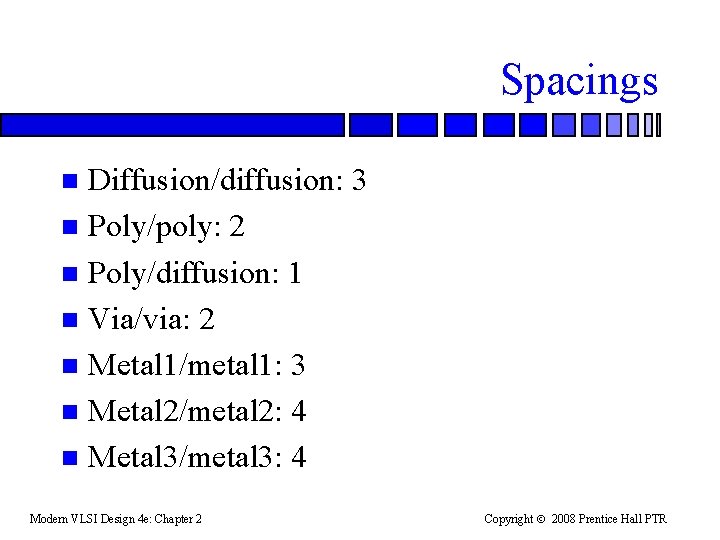

Spacings Diffusion/diffusion: 3 n Poly/poly: 2 n Poly/diffusion: 1 n Via/via: 2 n Metal 1/metal 1: 3 n Metal 2/metal 2: 4 n Metal 3/metal 3: 4 n Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

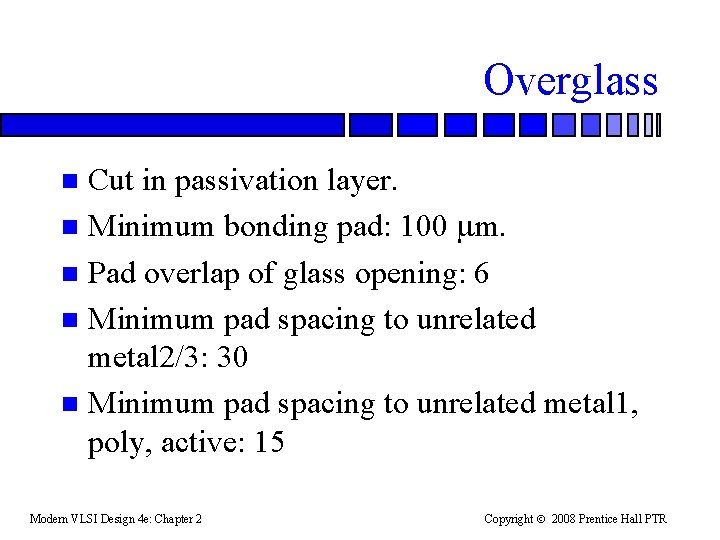

Overglass Cut in passivation layer. n Minimum bonding pad: 100 m. n Pad overlap of glass opening: 6 n Minimum pad spacing to unrelated metal 2/3: 30 n Minimum pad spacing to unrelated metal 1, poly, active: 15 n Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

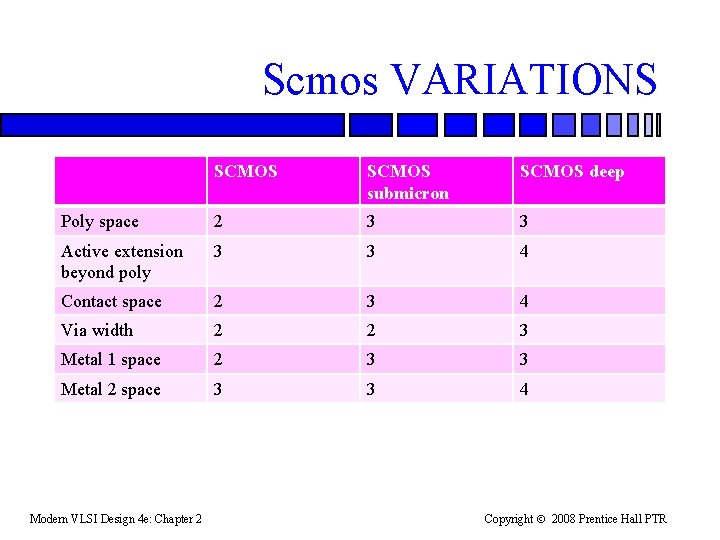

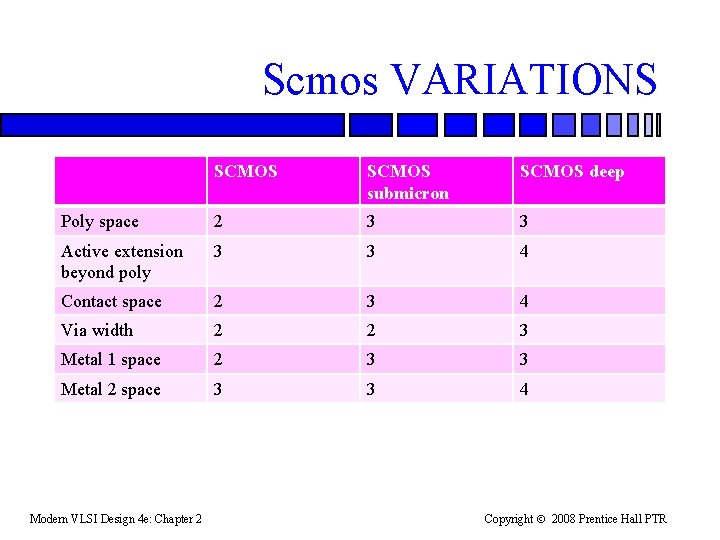

Scmos VARIATIONS SCMOS submicron SCMOS deep Poly space 2 3 3 Active extension beyond poly 3 3 4 Contact space 2 3 4 Via width 2 2 3 Metal 1 space 2 3 3 Metal 2 space 3 3 4 Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

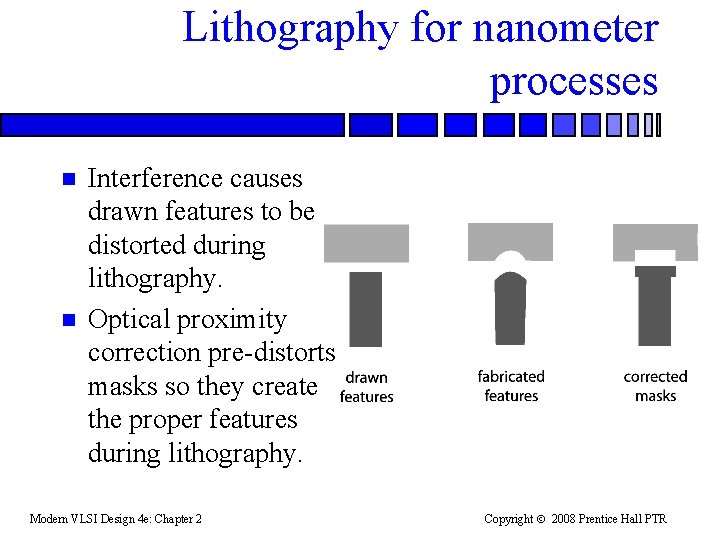

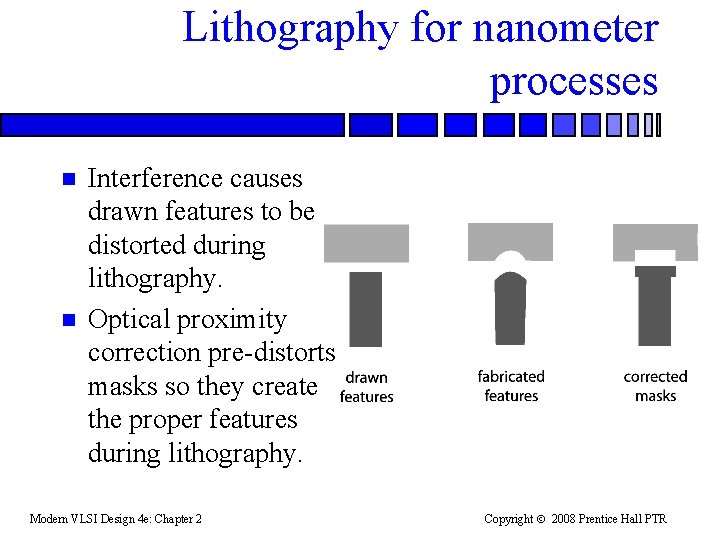

Lithography for nanometer processes n n Interference causes drawn features to be distorted during lithography. Optical proximity correction pre-distorts masks so they create the proper features during lithography. Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

3 -D integration 3 -D technology stacks multiple levels of transistors and interconnect. n Through-silicon-via (TSV) with die stacking uses special via to connect between separately fabricated chips. n Multilayer buried structures build several layers of devices on a substrate. n Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

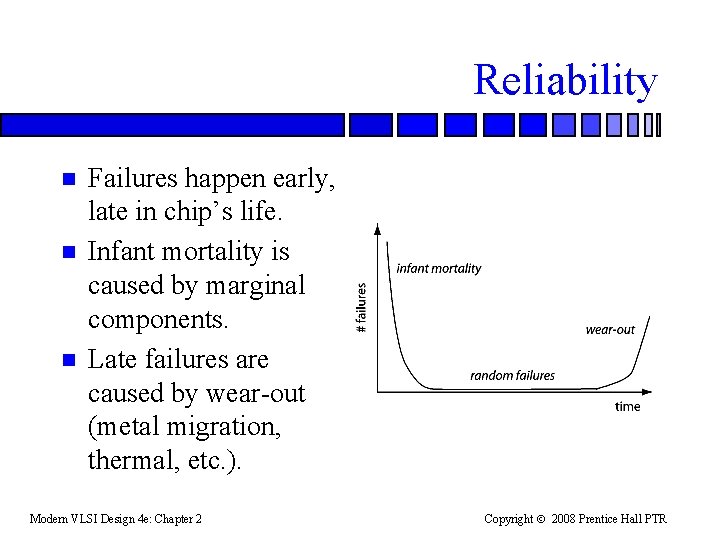

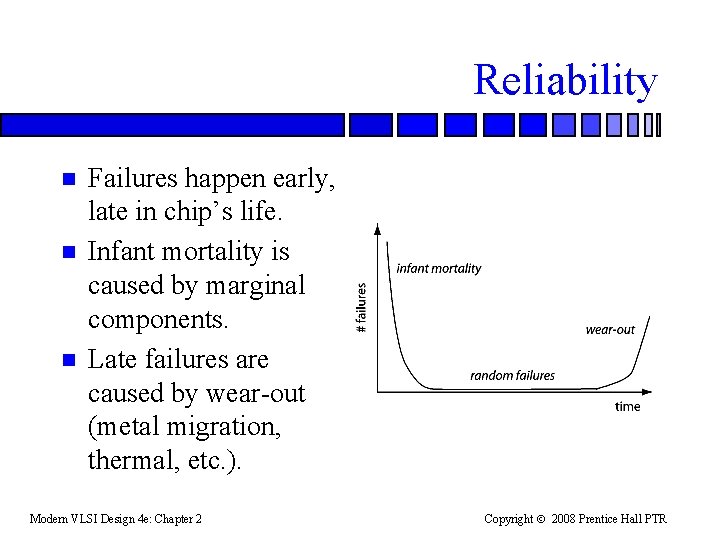

Reliability n n n Failures happen early, late in chip’s life. Infant mortality is caused by marginal components. Late failures are caused by wear-out (metal migration, thermal, etc. ). Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

Mean-time-to-failure MTF for metal wires = time required for 50% of wires to fail. n Depends on current density: n – proportional to j-n e Q/k. T – j is current density – n is constant between 1 and 3 – Q is diffusion activation energy n Can determine lifetime from MTTF. Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

Traditional sources of unreliability Diffusions and junctions: crystal defects, impurity precipitation, mask misalignment, surface contamination. n Oxides: Mobile ions, pinholes, interface states, hot carriers, time-dependent dielectric breakdown. n Metalization: scratches/voids, mechanical damage, non-ohmic contacts, step coverage. n Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

TDDB Time-dependent dielectric breakdown: gate voltages cause stress in gate oxides. n More common as oxides become thinner. n TDDB failure rate: n – MTTF = A 10 b. E e. Es/kt Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

Hot carriers Hot carrier has enough energy to jump from silicon to oxide. n Accumulated hot carriers create a space charge that affects threshold voltage. n Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

NTBI Negative bias temperature instability is particular to p. MOS devices. n Threshold voltage, transconductance change due to stresses. n Can be reversed by applying a reverse bias to the transistor. n Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

Electromigration and stress migration Degenerative failure for wires. n Grains in metal have defects at grain surface that cause electromigration. n Stress migration caused by mechanical stress. n – Can occur even with zero current. Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

Soft errors Caused by alpha particles. n Packages contain small amounts of uranium and thorium, which generate error-inducing radiation. n Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

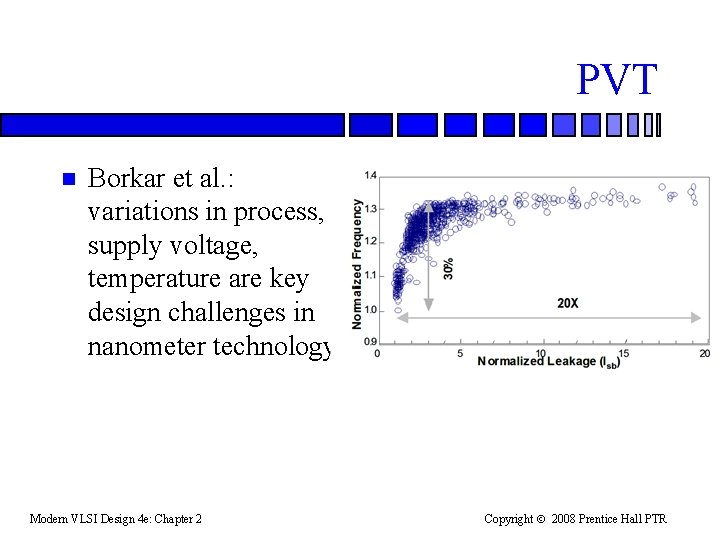

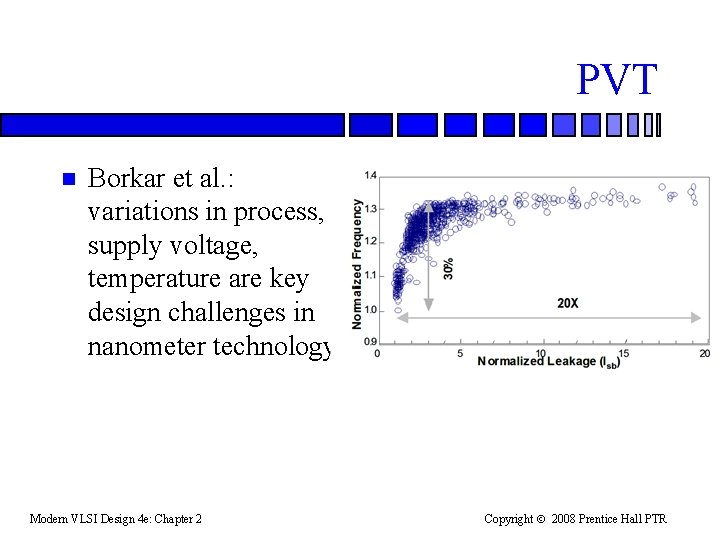

PVT n Borkar et al. : variations in process, supply voltage, temperature are key design challenges in nanometer technology. Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

PVT challenges Process variations: channel length and threshold significantly in nanometer technologies. n Supply voltage: non-ideal wires introduce variations in supply across chip. n Temperature: higher chip operating temperatures degrade both transistors and interconnect. n Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

On-chip temperature sensors Temperature sensors are used to shut off part or all of the chip to stop thermal runaway. n Use a pn junction from a parasitic bipolar transistor. n – Can also use MOS transistor. Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

Stick diagrams A stick diagram is a cartoon of a layout. n Does show all components/vias (except possibly tub ties), relative placement. n Does not show exact placement, transistor sizes, wire lengths, wire widths, tub boundaries. n Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

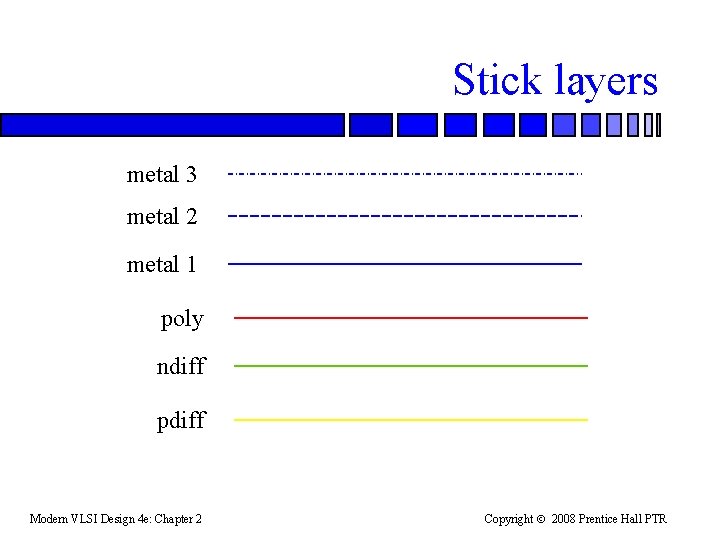

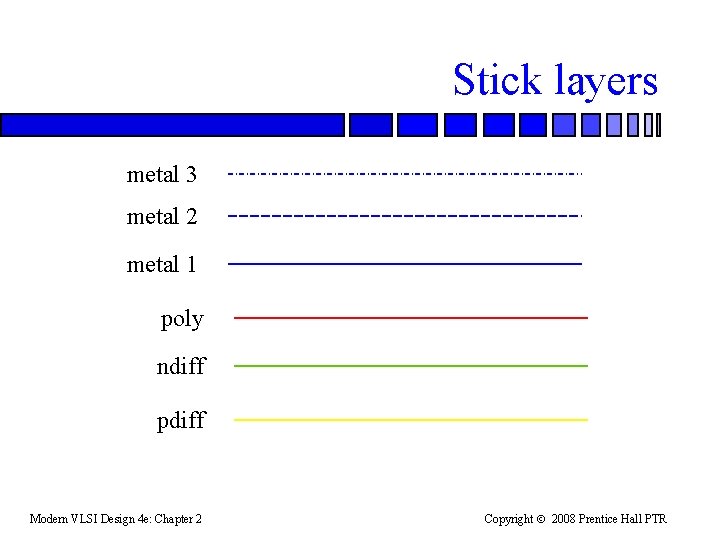

Stick layers metal 3 metal 2 metal 1 poly ndiff pdiff Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

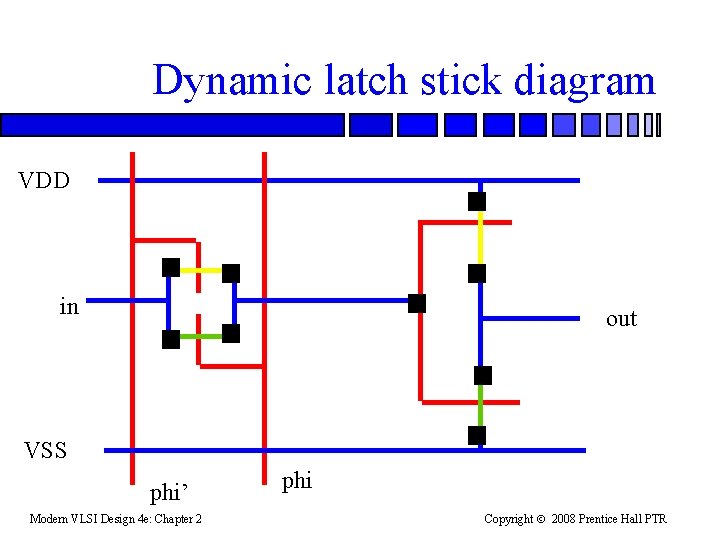

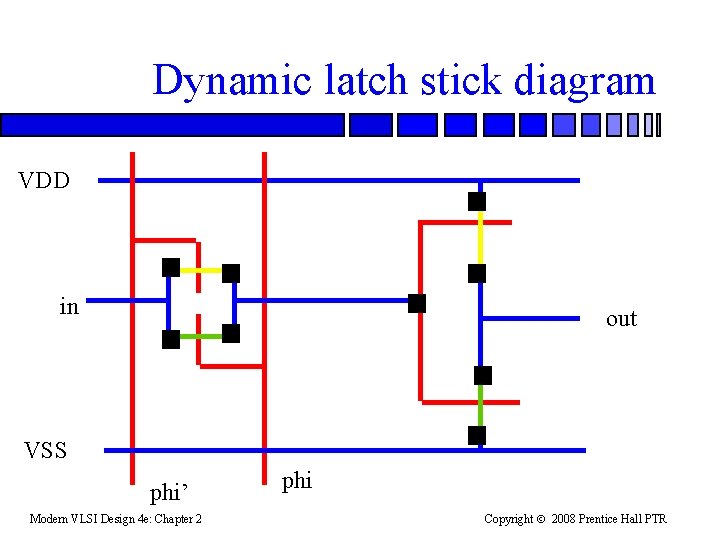

Dynamic latch stick diagram VDD in out VSS phi’ Modern VLSI Design 4 e: Chapter 2 phi Copyright 2008 Prentice Hall PTR

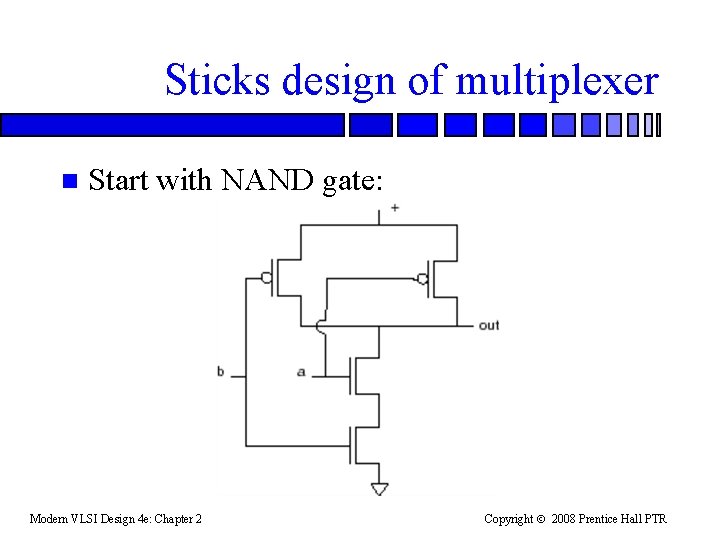

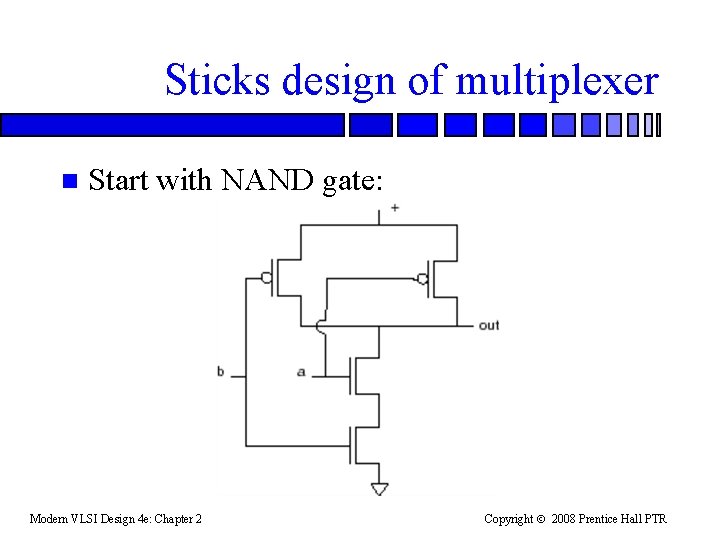

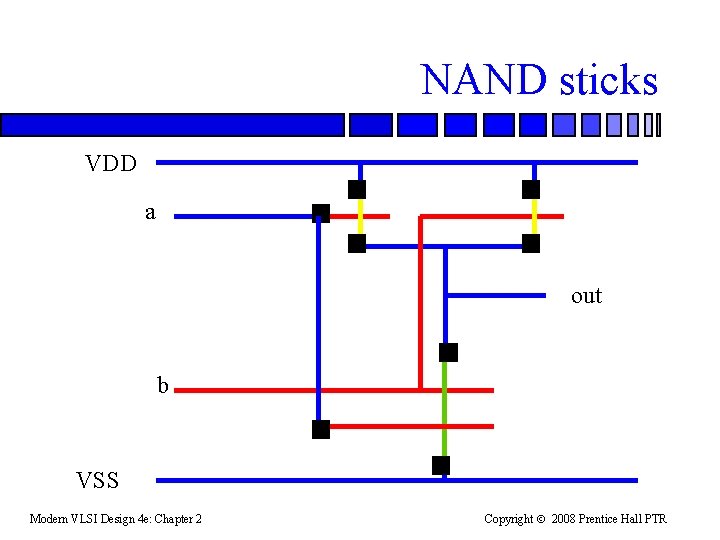

Sticks design of multiplexer n Start with NAND gate: Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

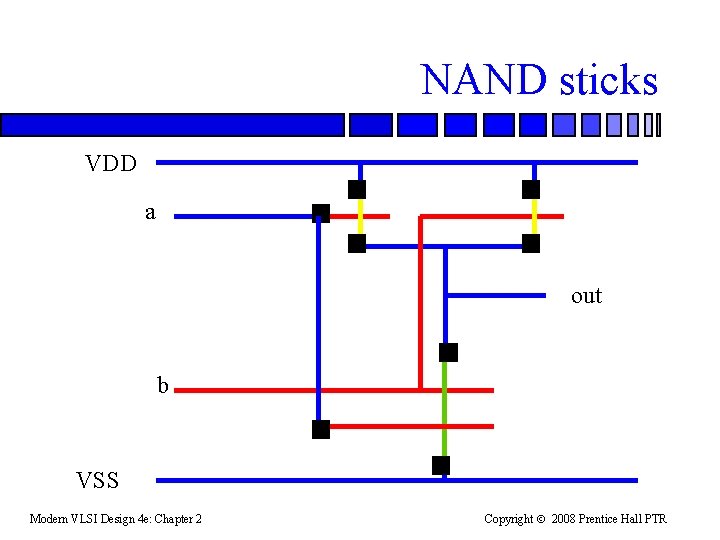

NAND sticks VDD a out b VSS Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

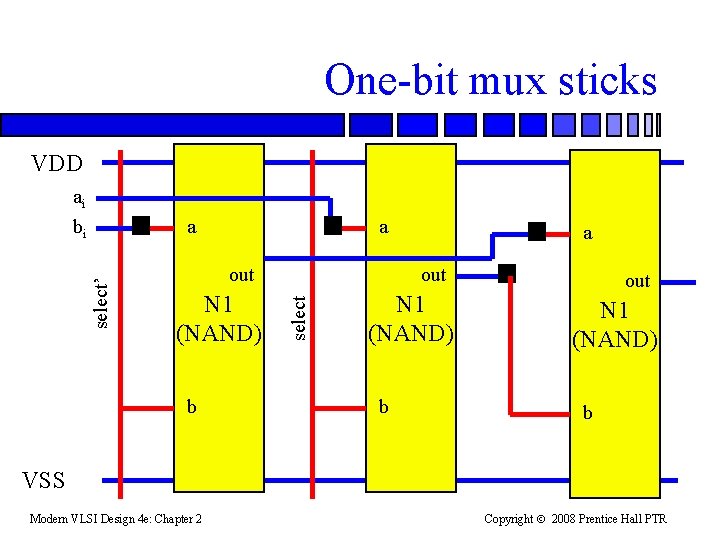

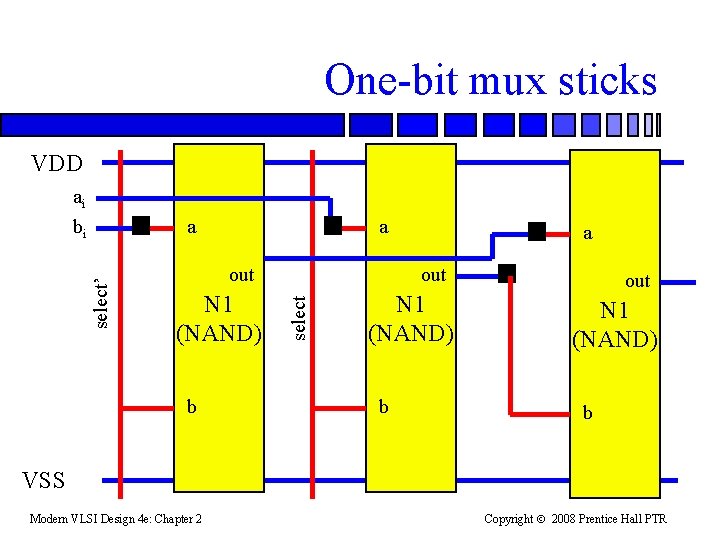

One-bit mux sticks VDD ai bi a out N 1 (NAND) b a out select’ a N 1 (NAND) b out N 1 (NAND) b VSS Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

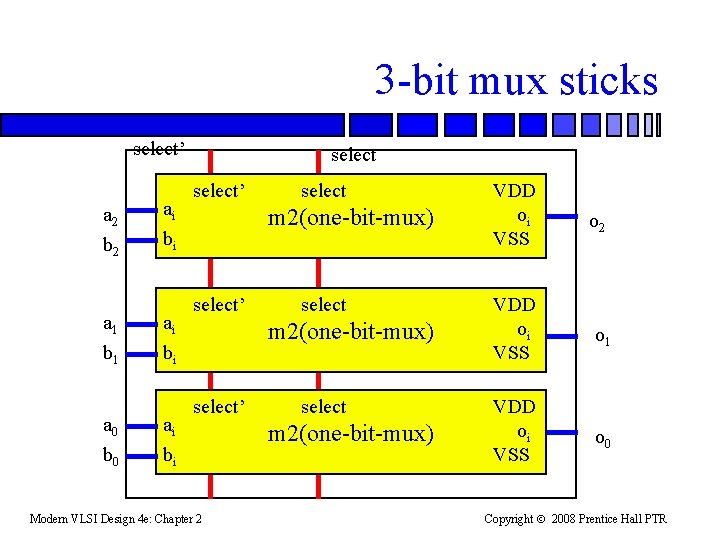

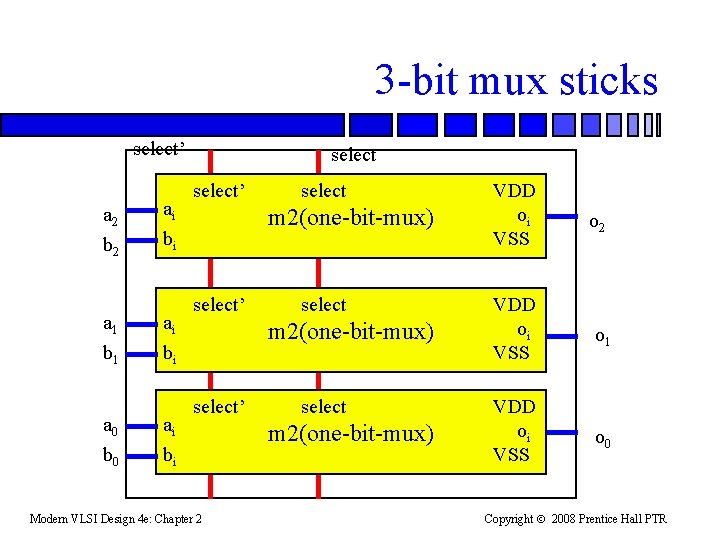

3 -bit mux sticks select’ a 2 b 2 a 1 b 1 a 0 b 0 ai bi select’ select m 2(one-bit-mux) select’ Modern VLSI Design 4 e: Chapter 2 select m 2(one-bit-mux) VDD oi VSS o 2 VDD oi VSS o 1 VDD oi VSS o 0 Copyright 2008 Prentice Hall PTR

Layout design and analysis tools Layout editors are interactive tools. n Design rule checkers are generally batch--identify DRC errors on the layout. n Circuit extractors extract the netlist from the layout. n Connectivity verification systems (CVS) compare extracted and original netlists. n Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

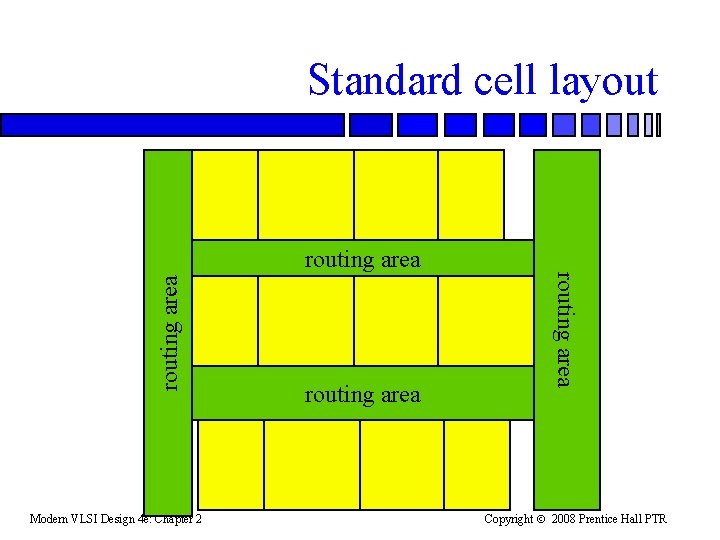

Automatic layout Cell generators (macrocell generators) create optimized layouts for ALUs, etc. n Standard cell/sea-of-gates layout creates layout from predesigned cells + custom routing. n – Sea-of-gates allows routing over the cell. Modern VLSI Design 4 e: Chapter 2 Copyright 2008 Prentice Hall PTR

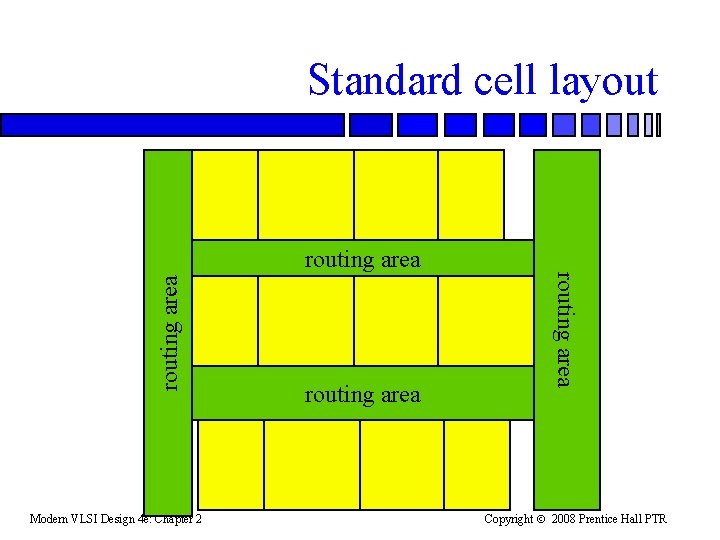

Standard cell layout Modern VLSI Design 4 e: Chapter 2 routing area Copyright 2008 Prentice Hall PTR