VLSI Circuit System Lab My CAD Layout VLSI

VLSI Circuit & System Lab. My. CAD & Layout VLSI회로 및 시스템 연구실 (양병도 교수님 연구실) 2010. 04. 30 VLSICS CBNU

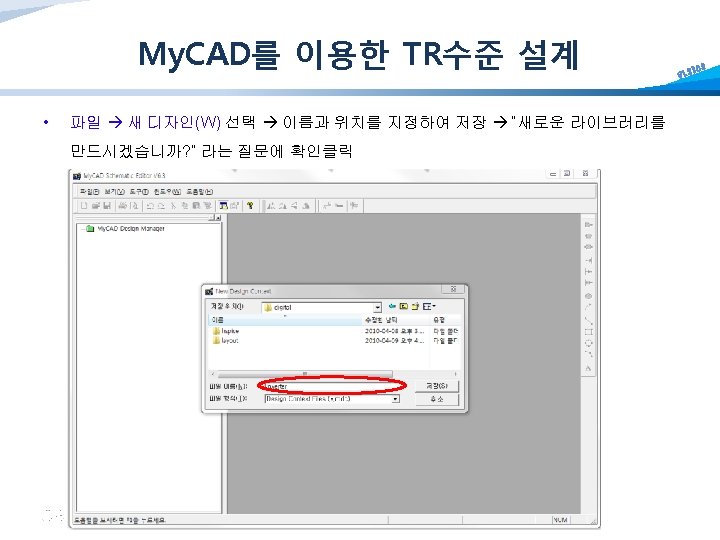

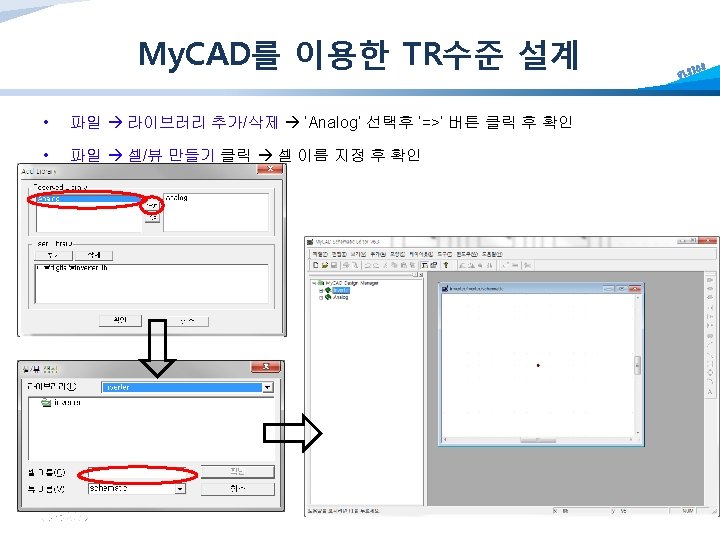

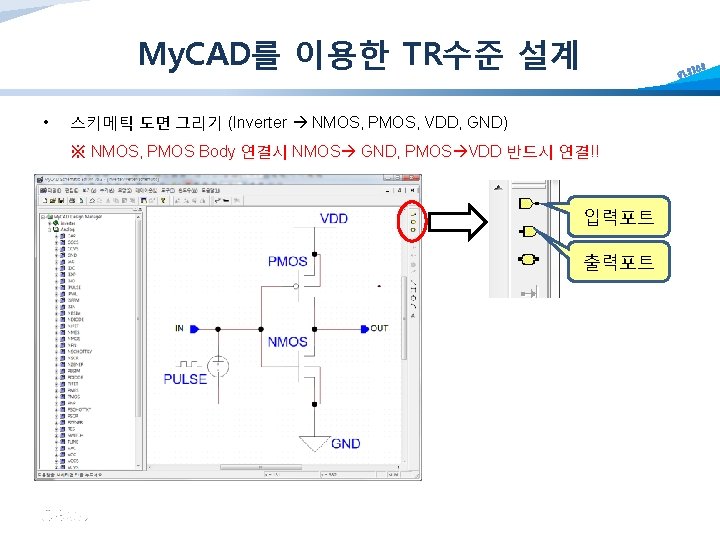

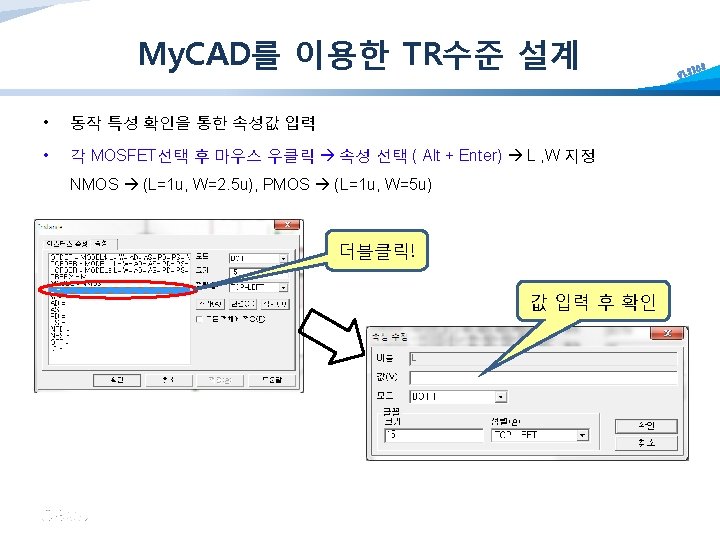

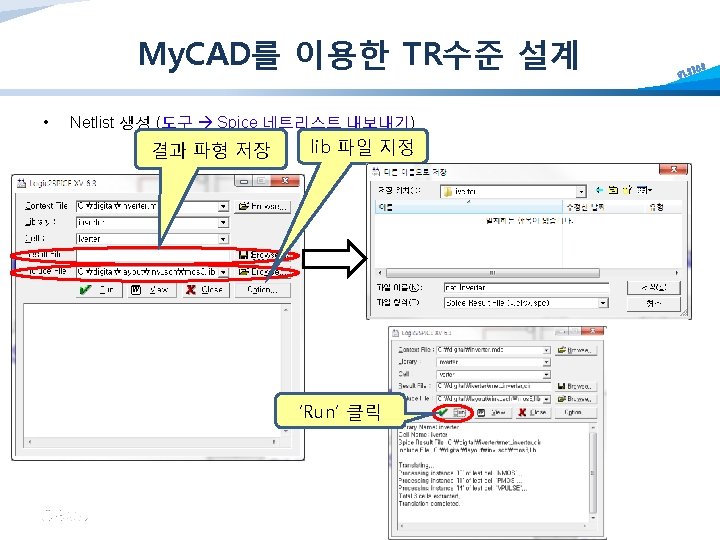

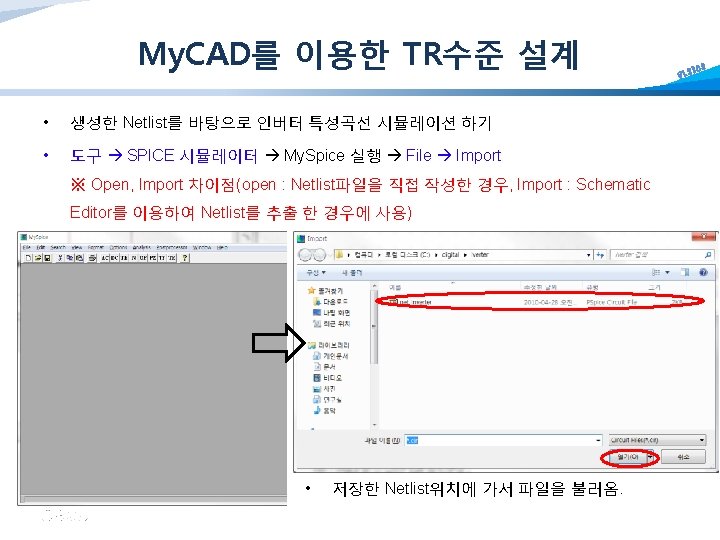

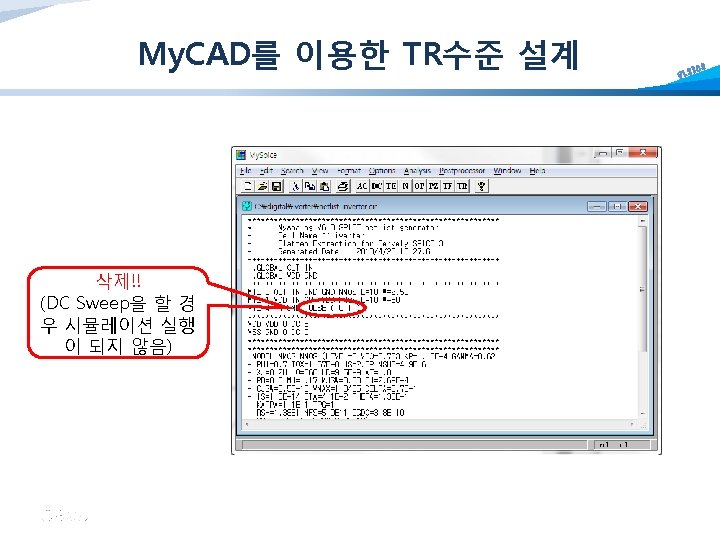

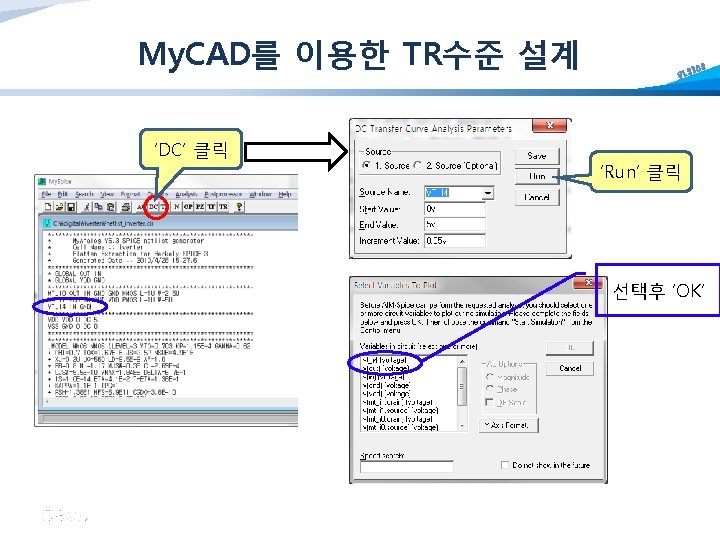

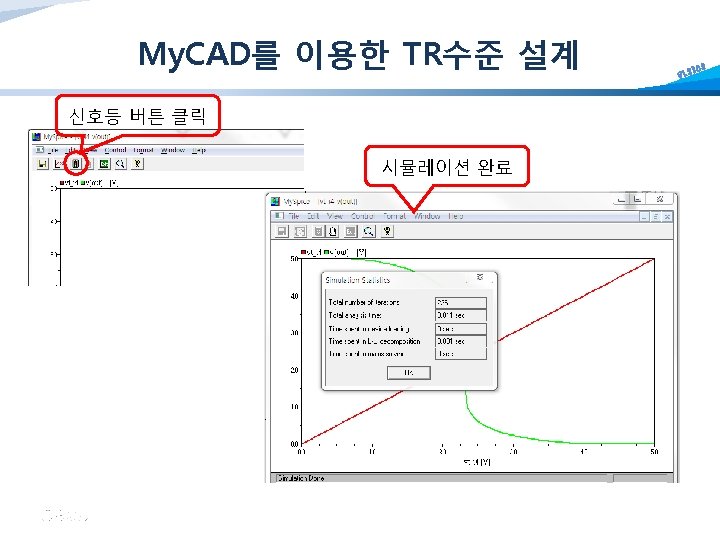

My. CAD를 이용한 TR수준 설계 • Schematic Editor For My. Analog 실행 CBNU S IC VLS

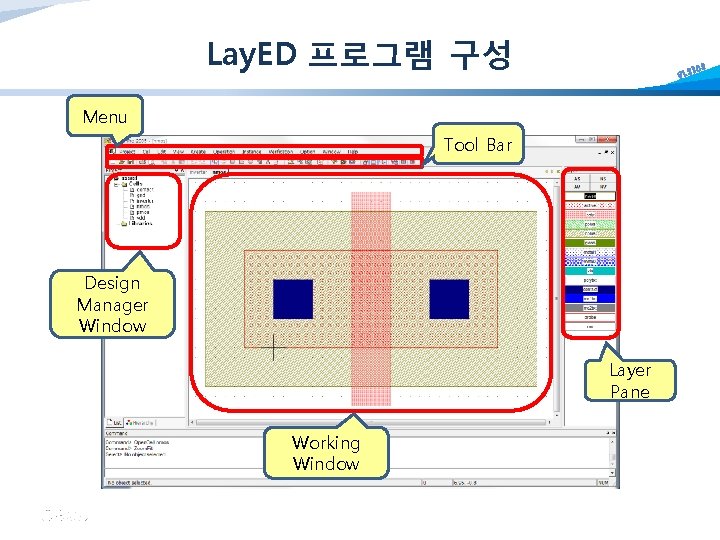

Lay. ED 프로그램 구성 S IC VLS Menu Tool Bar Design Manager Window Layer Pane Working Window CBNU

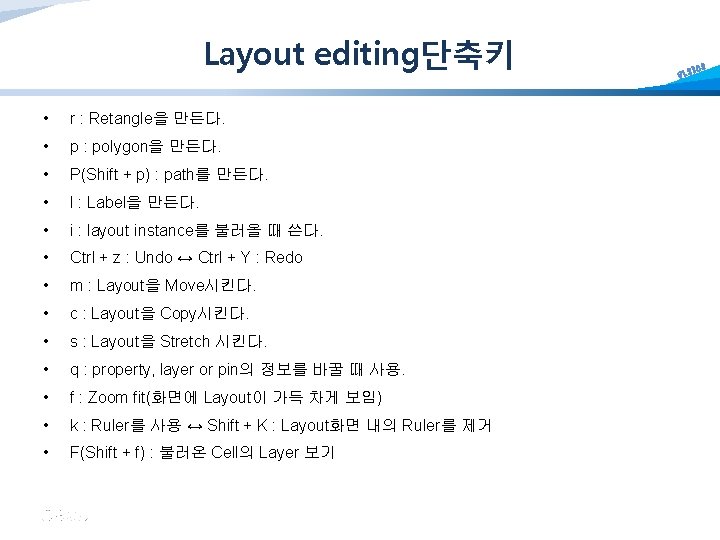

Layout editing단축키 • r : Retangle을 만든다. • p : polygon을 만든다. • P(Shift + p) : path를 만든다. • l : Label을 만든다. • i : layout instance를 불러올 때 쓴다. • Ctrl + z : Undo ↔ Ctrl + Y : Redo • m : Layout을 Move시킨다. • c : Layout을 Copy시킨다. • s : Layout을 Stretch 시킨다. • q : property, layer or pin의 정보를 바꿀 때 사용. • f : Zoom fit(화면에 Layout이 가득 차게 보임) • k : Ruler를 사용 ↔ Shift + K : Layout화면 내의 Ruler를 제거 • F(Shift + f) : 불러온 Cell의 Layer 보기 CBNU S IC VLS

Layout 실습 • MOSIS SCMOS single poly double metal (n-well 사용) Inverter Layout 단면도 CBNU S IC VLS

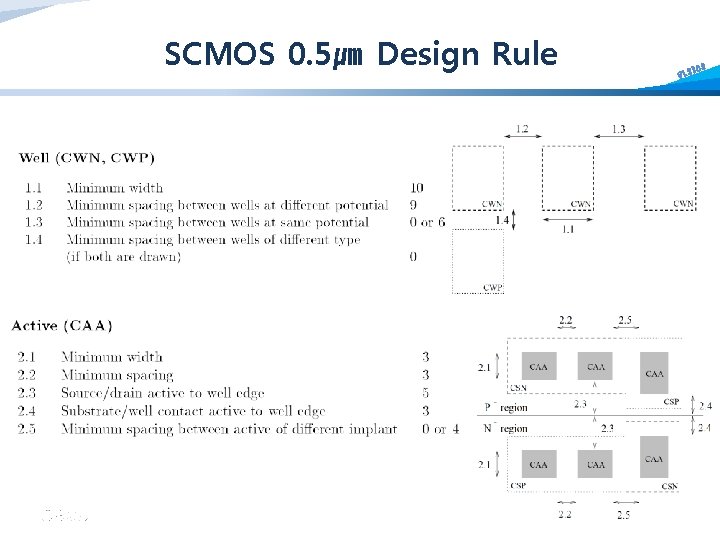

SCMOS 0. 5㎛ Design Rule CBNU S IC VLS

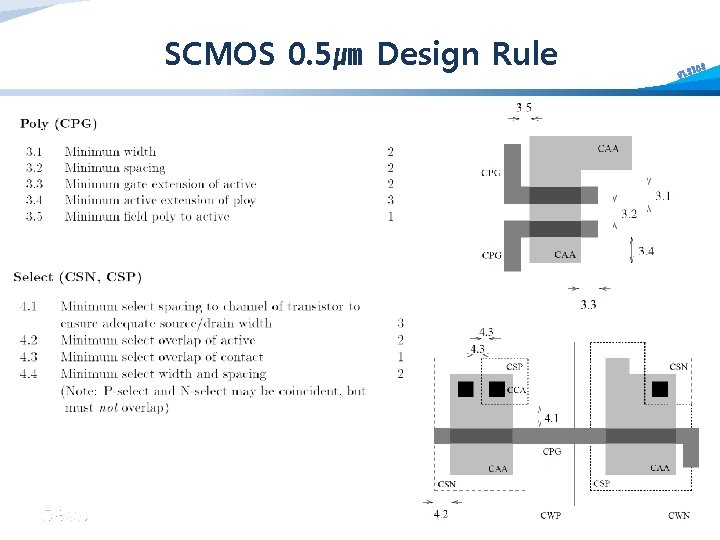

SCMOS 0. 5㎛ Design Rule CBNU S IC VLS

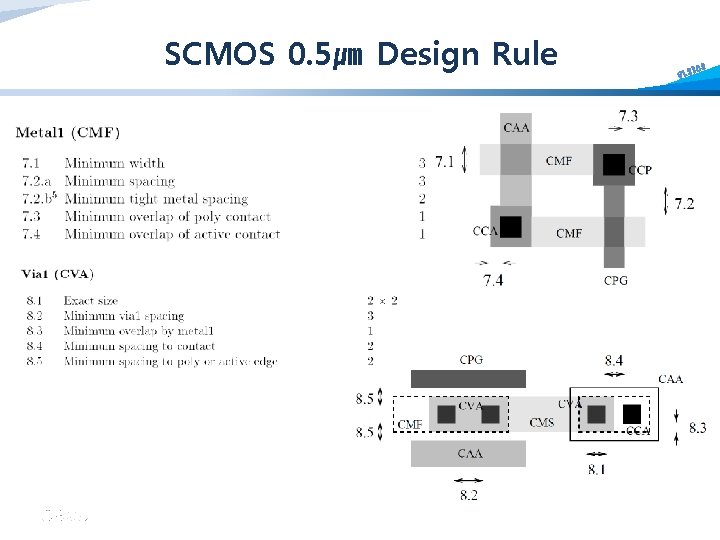

SCMOS 0. 5㎛ Design Rule CBNU S IC VLS

SCMOS 0. 5㎛ Design Rule CBNU S IC VLS

SCMOS 0. 5㎛ Design Rule CBNU S IC VLS

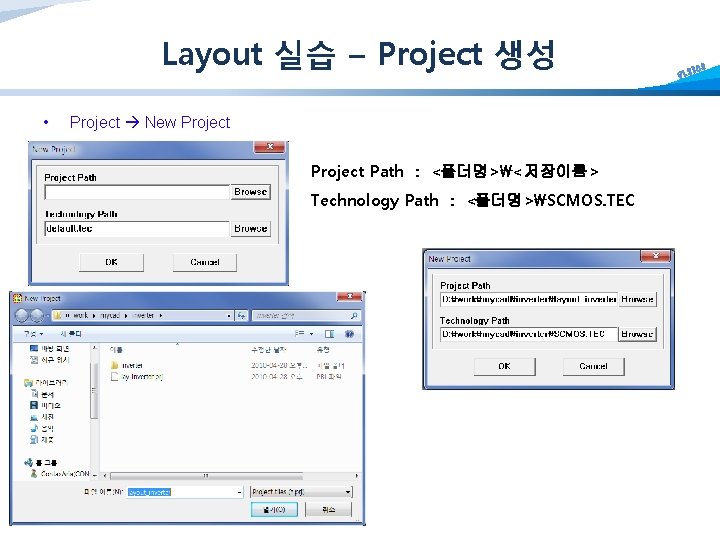

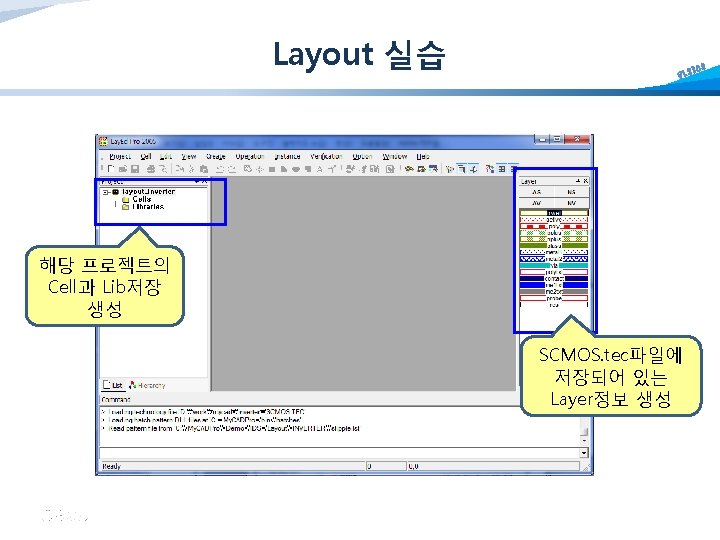

Layout 실습 – Project 생성 • Project New Project Path : <폴더명><저장이름> Technology Path : <폴더명>SCMOS. TEC CBNU S IC VLS

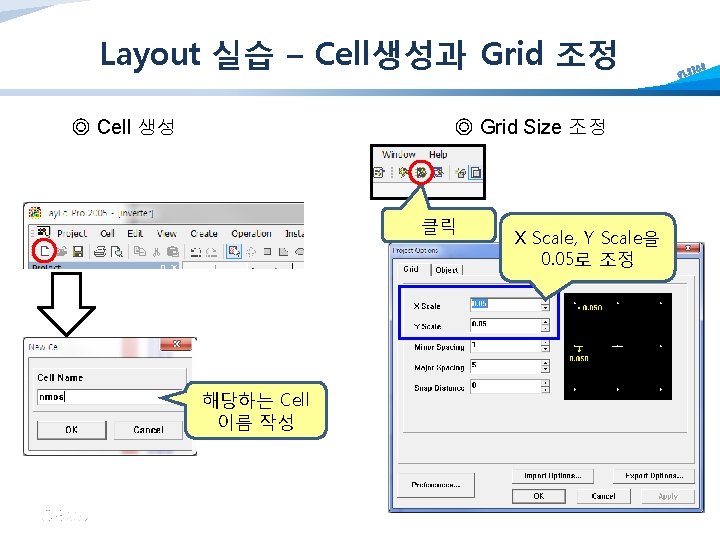

Layout 실습 – Cell생성과 Grid 조정 ◎ Cell 생성 ◎ Grid Size 조정 클릭 해당하는 Cell 이름 작성 CBNU X Scale, Y Scale을 0. 05로 조정 S IC VLS

Layout 실습 – NMOS 그리기 S IC VLS Poly 3 C Active 6 B 5 D W 4 B Contact L CBNU N+ implant (Nplus)

Layout 실습 – PMOS 그리기 S IC VLS Poly 3 C Active 6 B 5 D W 4 B 5 C L CBNU P+ implant (Pplus)

Layout 실습 – VDD, GND 그리기 NPLUS + active + Metal 1 + Contact 5 C 7 C 5 C 6 B 4 B VDD PPLUS + active + Metal 1 + Contact GND CBNU S IC VLS

Layout 실습 – Inverter 그리기 S IC VLS Layout Schematic CBNU

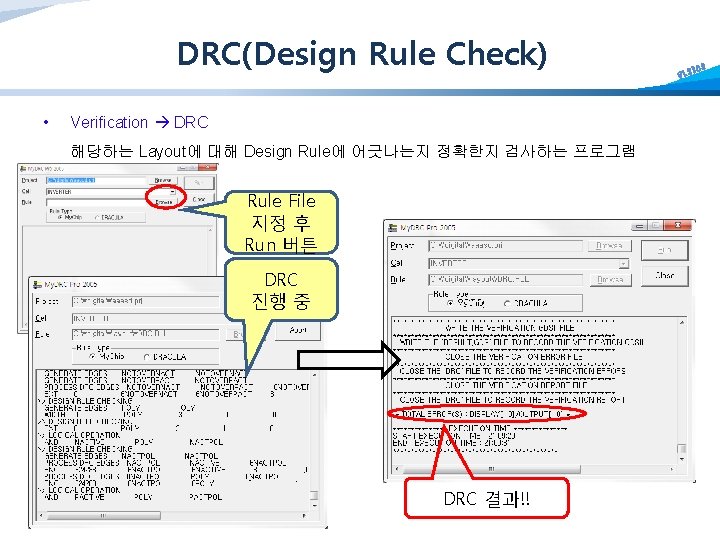

DRC(Design Rule Check) • Verification DRC 해당하는 Layout에 대해 Design Rule에 어긋나는지 정확한지 검사하는 프로그램 Rule File 지정 후 Run 버튼 DRC 진행 중 CBNU DRC 결과!! S IC VLS

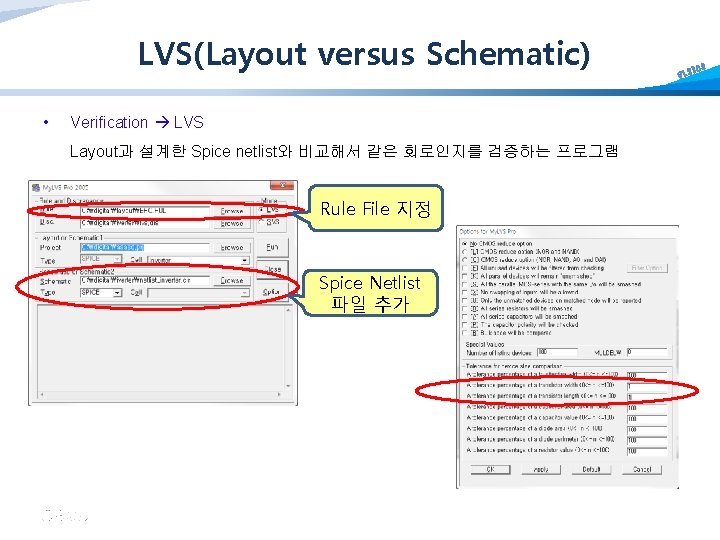

LVS(Layout versus Schematic) • Verification LVS Layout과 설계한 Spice netlist와 비교해서 같은 회로인지를 검증하는 프로그램 Rule File 지정 Spice Netlist 파일 추가 CBNU S IC VLS

LVS(Layout versus Schematic) CBNU S IC VLS

- Slides: 33