Viterbi Decoder Implementation Convolutional Codes Chip Overview Verilog

Viterbi Decoder Implementation • Convolutional Codes • Chip Overview • Verilog Code • Simulation Result 1

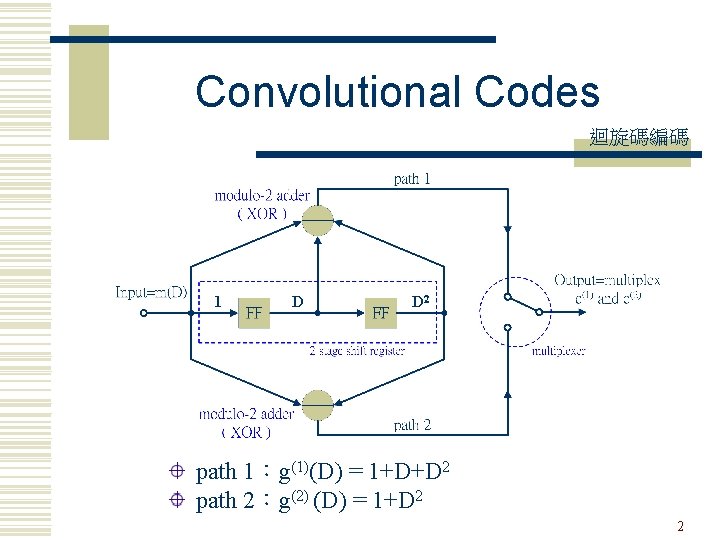

Convolutional Codes 迴旋碼編碼 1 D D 2 path 1:g(1)(D) = 1+D+D 2 path 2:g(2) (D) = 1+D 2 2

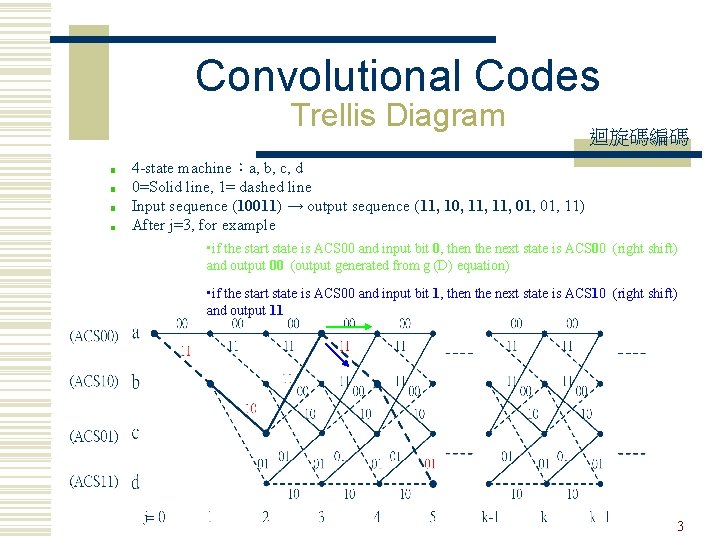

Convolutional Codes Trellis Diagram 迴旋碼編碼 4 -state machine:a, b, c, d 0=Solid line, 1= dashed line Input sequence (10011) → output sequence (11, 10, 11, 01, 11) After j=3, for example • if the start state is ACS 00 and input bit 0, then the next state is ACS 00 (right shift) and output 00 (output generated from g (D) equation) • if the start state is ACS 00 and input bit 1, then the next state is ACS 10 (right shift) and output 11 3

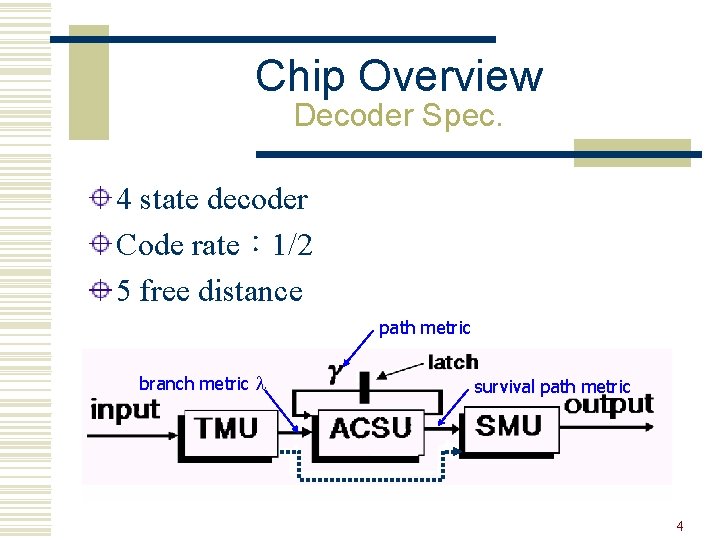

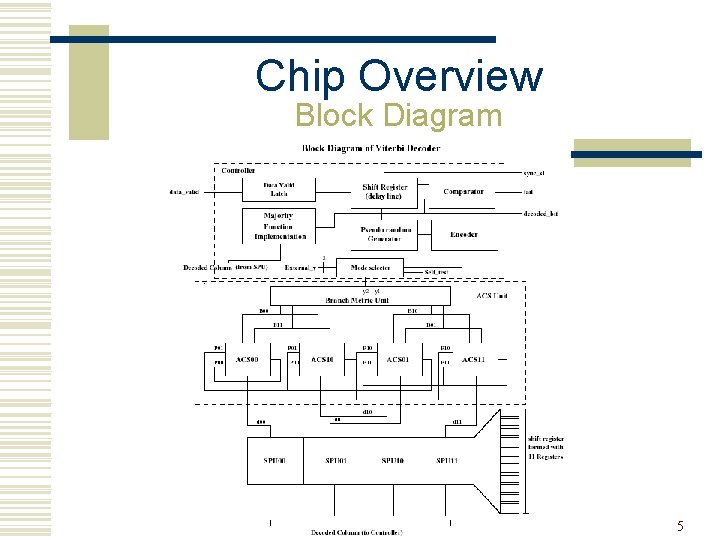

Chip Overview Decoder Spec. 4 state decoder Code rate: 1/2 5 free distance path metric branch metric survival path metric 4

Chip Overview Block Diagram 5

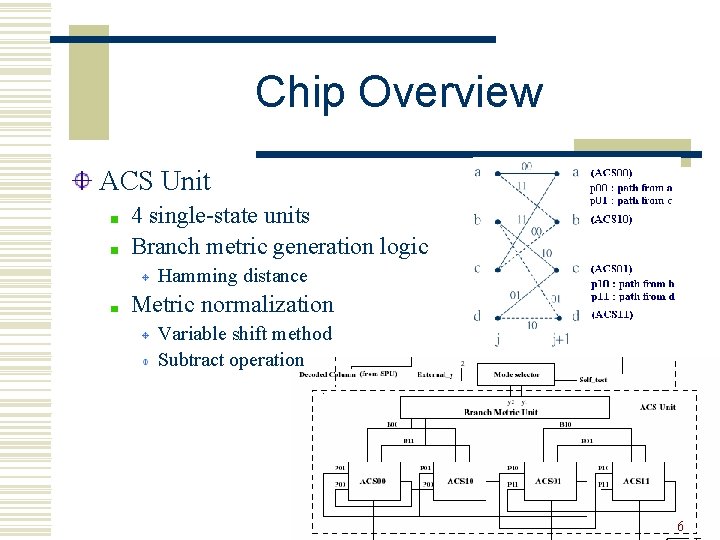

Chip Overview ACS Unit 4 single-state units Branch metric generation logic Hamming distance Metric normalization Variable shift method Subtract operation 6

![Chip Overview Survivor Path Unit A [4 x 11] matrix of cells 4: 4 Chip Overview Survivor Path Unit A [4 x 11] matrix of cells 4: 4](http://slidetodoc.com/presentation_image/41cc0972cf3dd31030246f309c95c846/image-7.jpg)

Chip Overview Survivor Path Unit A [4 x 11] matrix of cells 4: 4 state 11:survivor path length L + 1 For cord rate 1/n where N is # of state 7

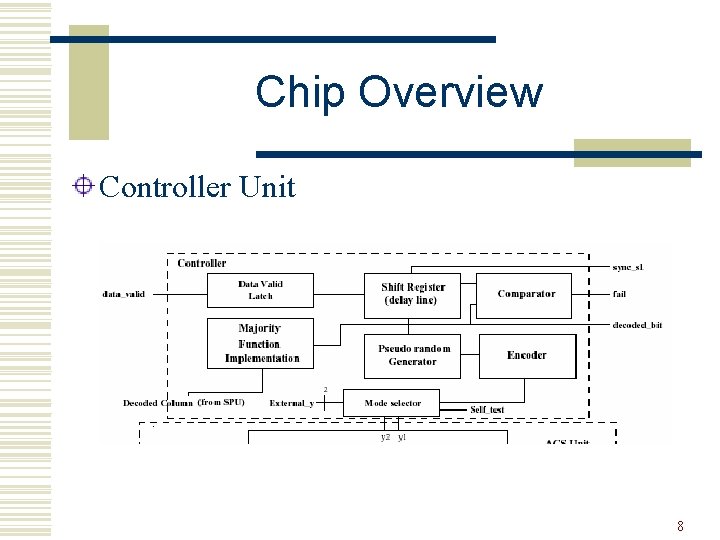

Chip Overview Controller Unit 8

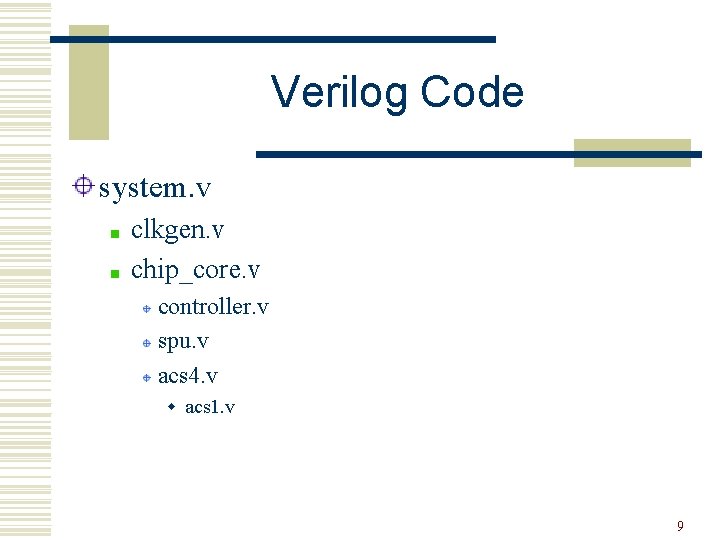

Verilog Code system. v clkgen. v chip_core. v controller. v spu. v acs 4. v w acs 1. v 9

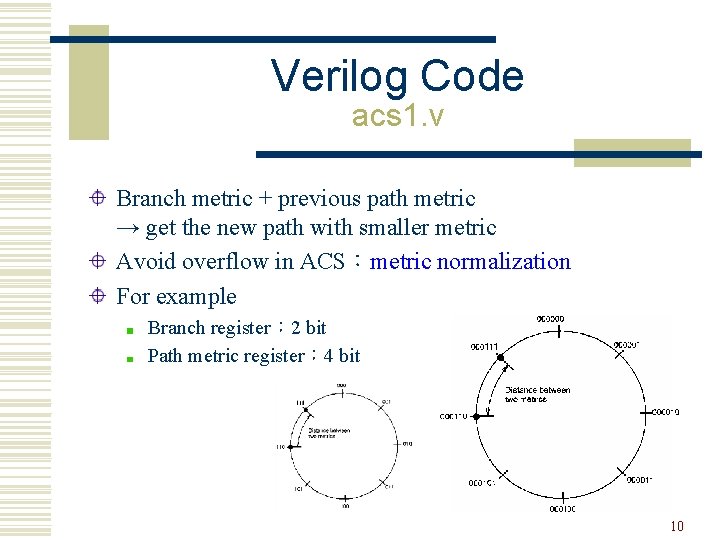

Verilog Code acs 1. v Branch metric + previous path metric → get the new path with smaller metric Avoid overflow in ACS:metric normalization For example Branch register: 2 bit Path metric register: 4 bit 10

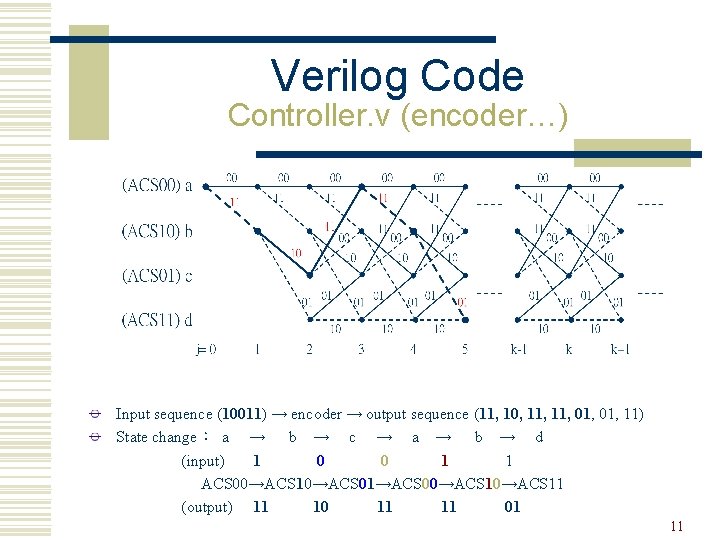

Verilog Code Controller. v (encoder…) Input sequence (10011) → encoder → output sequence (11, 10, 11, 01, 11) State change: a → b → c → a → b → d (input) 1 0 0 1 1 ACS 00→ACS 10→ACS 01→ACS 00→ACS 11 (output) 11 10 11 11 01 11

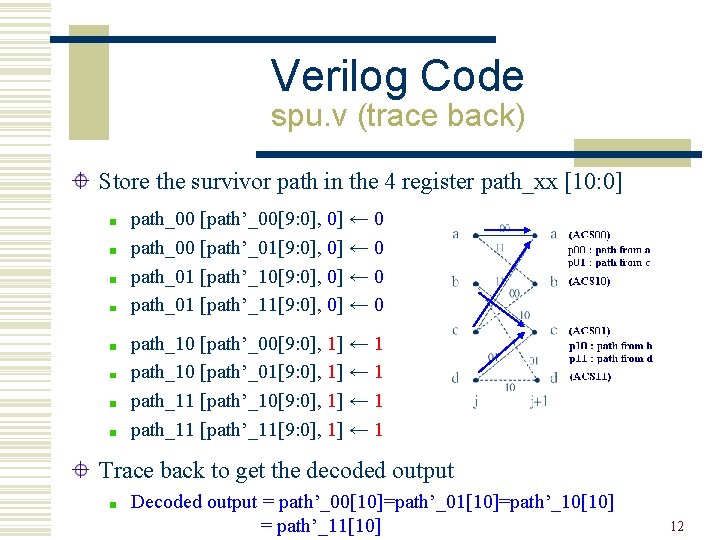

Verilog Code spu. v (trace back) Store the survivor path in the 4 register path_xx [10: 0] path_00 [path’_00[9: 0], 0] ← 0 path_00 [path’_01[9: 0], 0] ← 0 path_01 [path’_10[9: 0], 0] ← 0 path_01 [path’_11[9: 0], 0] ← 0 path_10 [path’_00[9: 0], 1] ← 1 path_10 [path’_01[9: 0], 1] ← 1 path_11 [path’_10[9: 0], 1] ← 1 path_11 [path’_11[9: 0], 1] ← 1 Trace back to get the decoded output Decoded output = path’_00[10]=path’_01[10]=path’_10[10] = path’_11[10] 12

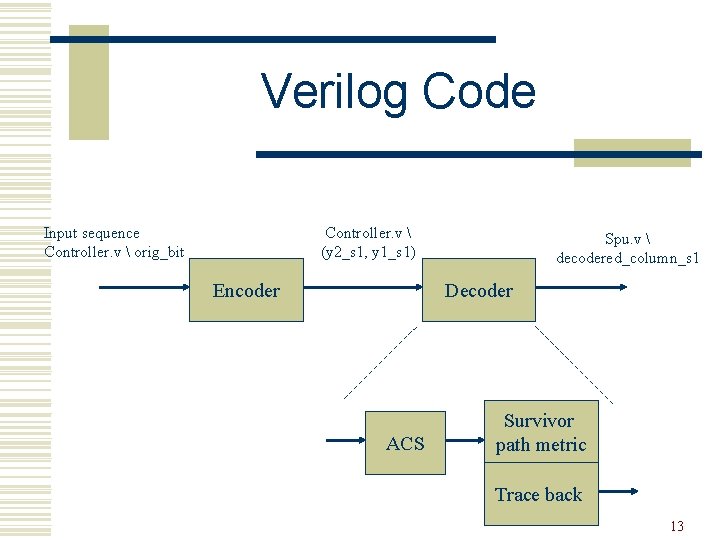

Verilog Code Input sequence Controller. v orig_bit Controller. v (y 2_s 1, y 1_s 1) Encoder Spu. v decodered_column_s 1 Decoder ACS Survivor path metric Trace back 13

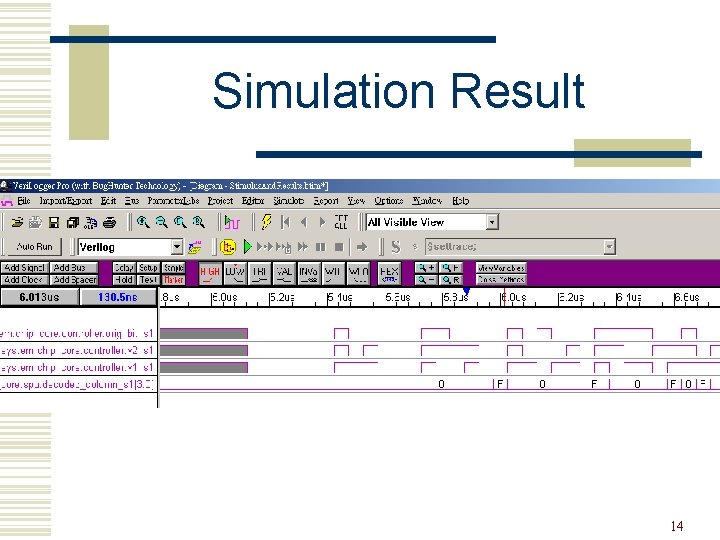

Simulation Result 14

- Slides: 14