VII GATE LEVEL MINIMIZATION A IMPLEMENTASI NAND dan

- Slides: 23

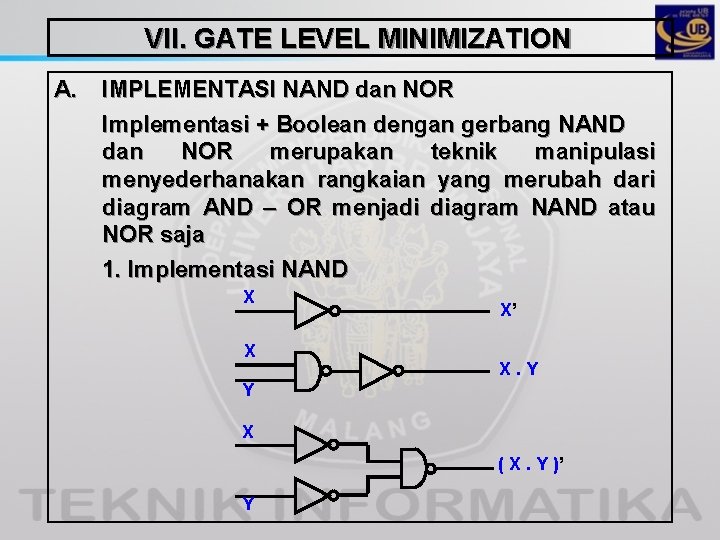

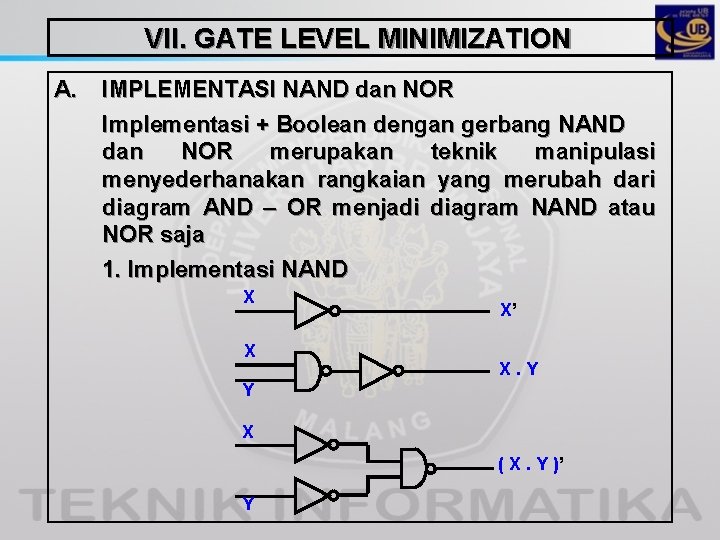

VII. GATE LEVEL MINIMIZATION A. IMPLEMENTASI NAND dan NOR Implementasi + Boolean dengan gerbang NAND dan NOR merupakan teknik manipulasi menyederhanakan rangkaian yang merubah dari diagram AND – OR menjadi diagram NAND atau NOR saja 1. Implementasi NAND X X X’ X. Y Y X ( X. Y )’ Y

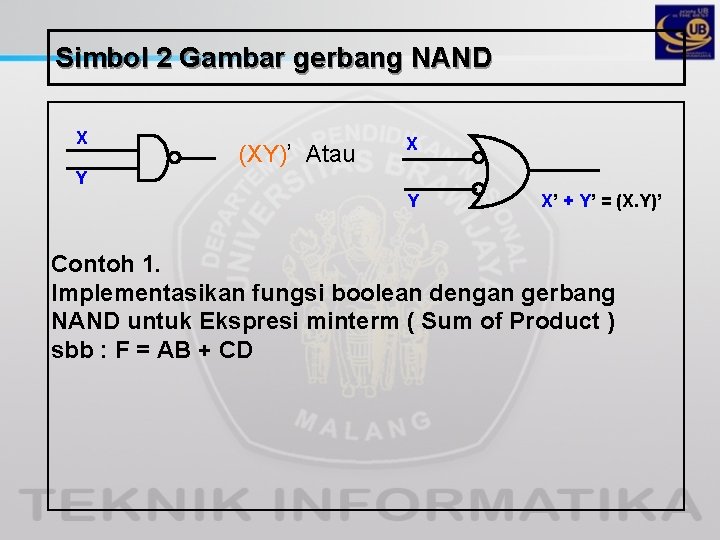

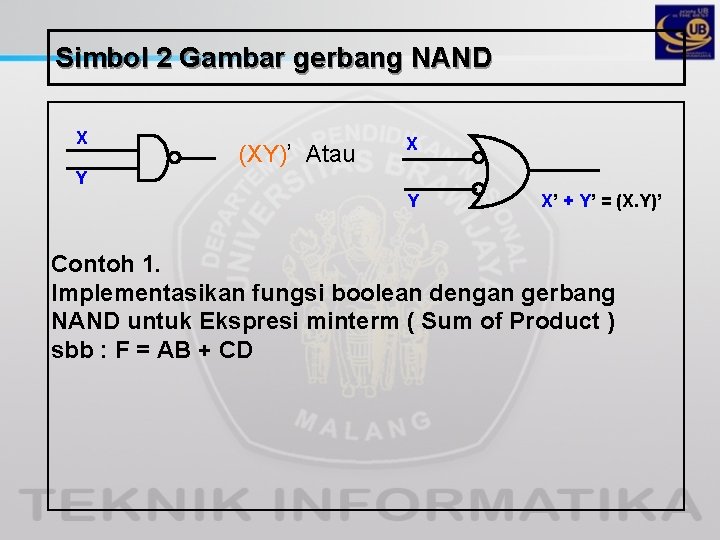

Simbol 2 Gambar gerbang NAND X (XY)’ Atau X Y Y X’ + Y’ = (X. Y)’ Contoh 1. Implementasikan fungsi boolean dengan gerbang NAND untuk Ekspresi minterm ( Sum of Product ) sbb : F = AB + CD

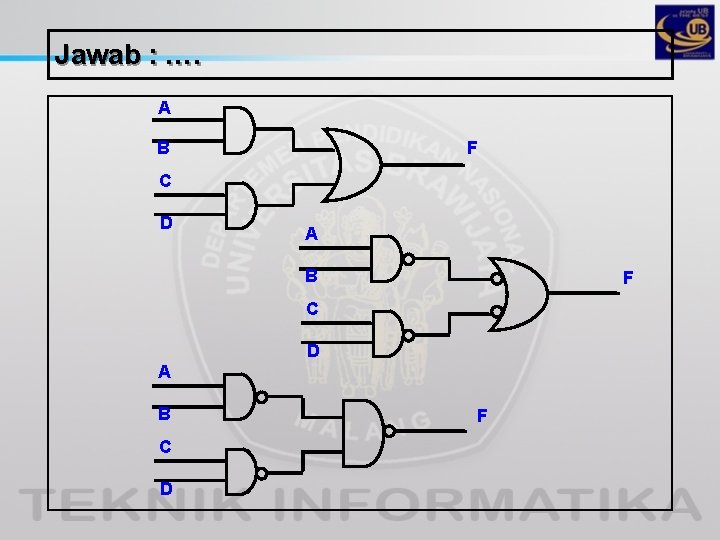

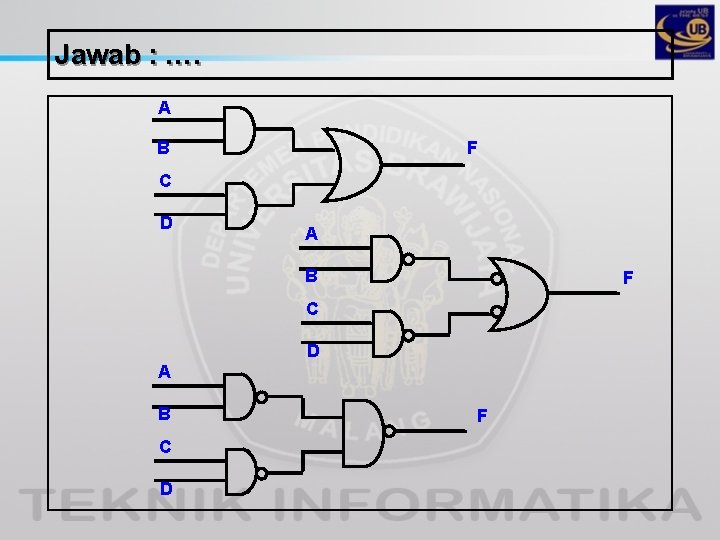

Jawab : …. A B F C D A B C D F

Contoh 2. Implementasi fungsi boolean dengan gerbang NAND untuk F(XYZ) = ∑ 1, 2, 3, 4, 5, 7 Jawab : YZ YZ X’ O 1 1 1 X 1 1 1 0 Fungsi Boolean F = XY’ + X’Y + Z X Y’ X’ Y Z F

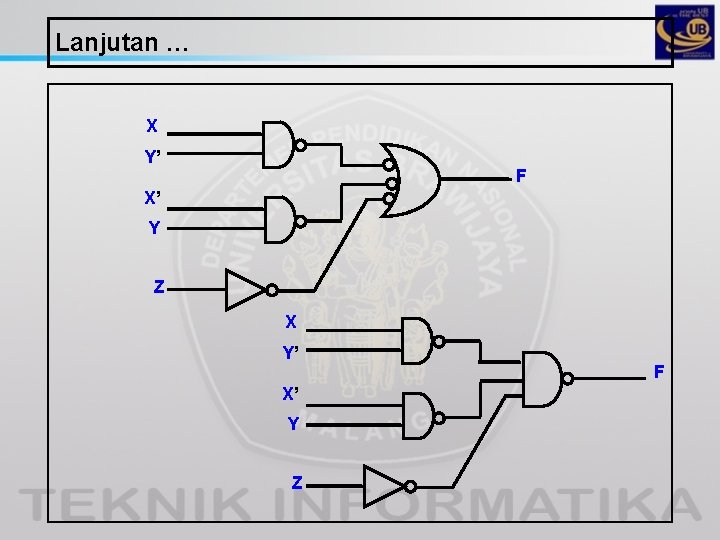

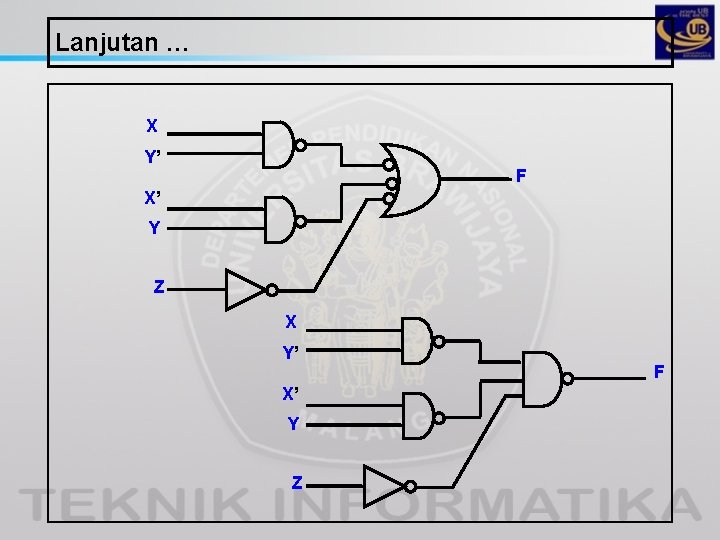

Lanjutan … X Y’ F X’ Y Z X Y’ X’ Y Z F

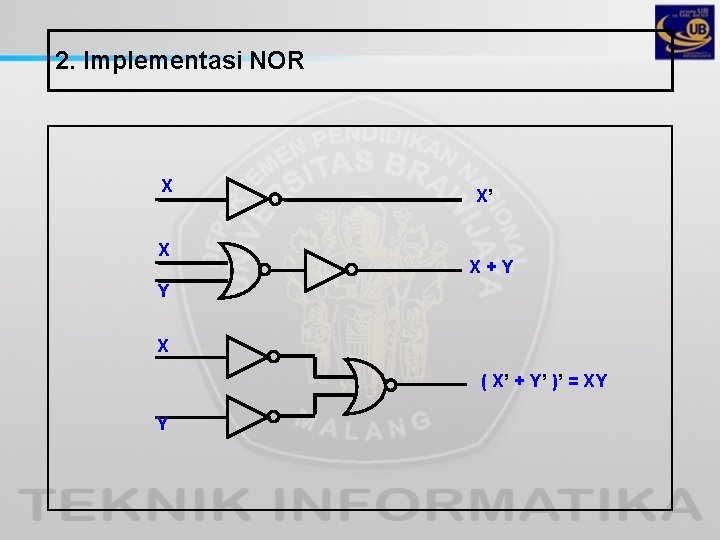

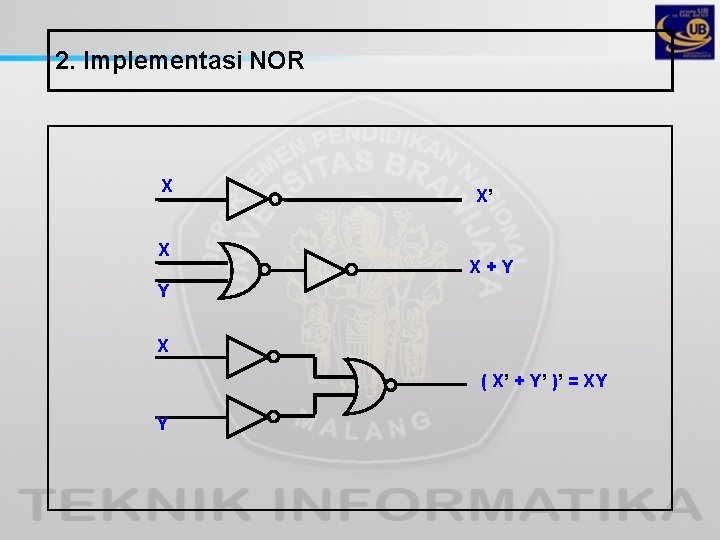

2. Implementasi NOR X X X’ X+Y Y X ( X’ + Y’ )’ = XY Y

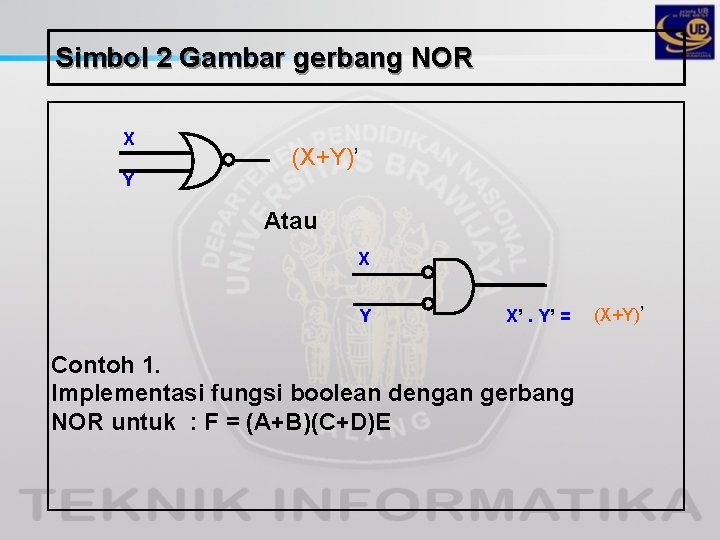

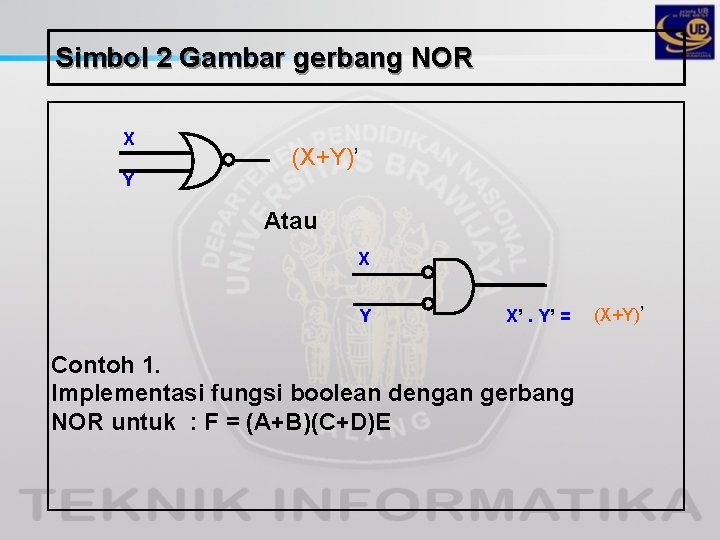

Simbol 2 Gambar gerbang NOR X Y (X+Y)’ Atau X Y X’. Y’ = Contoh 1. Implementasi fungsi boolean dengan gerbang NOR untuk : F = (A+B)(C+D)E (X+Y)’

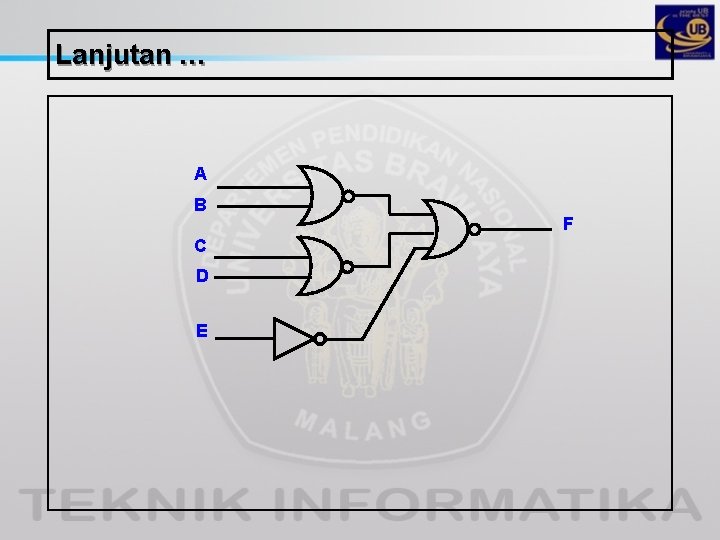

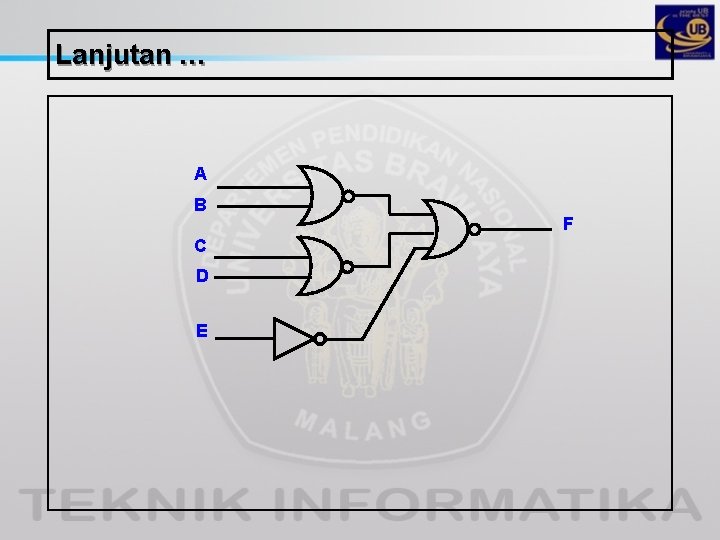

Jawab : …. A B F C D E A B C D E F

Lanjutan … A B C D E F

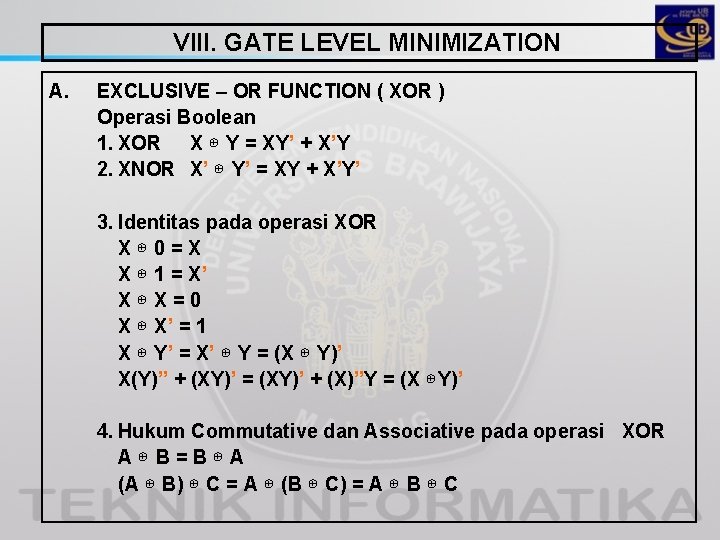

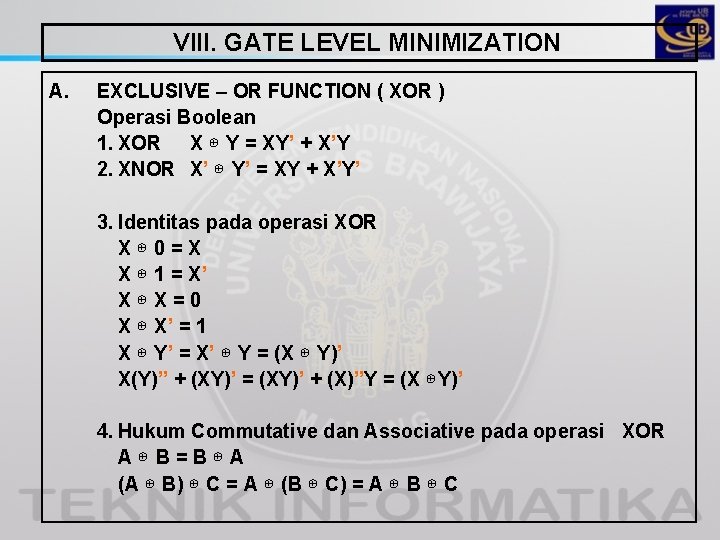

VIII. GATE LEVEL MINIMIZATION A. EXCLUSIVE – OR FUNCTION ( XOR ) Operasi Boolean 1. XOR X ⊕ Y = XY’ + X’Y 2. XNOR X’ ⊕ Y’ = XY + X’Y’ 3. Identitas pada operasi XOR X⊕ 0=X X ⊕ 1 = X’ X⊕ X=0 X ⊕ X’ = 1 X ⊕ Y’ = X’ ⊕ Y = (X ⊕ Y)’ X(Y)” + (XY)’ = (XY)’ + (X)”Y = (X ⊕ Y)’ 4. Hukum Commutative dan Associative pada operasi XOR A⊕ B=B⊕ A (A ⊕ B) ⊕ C = A ⊕ (B ⊕ C) = A ⊕ B ⊕ C

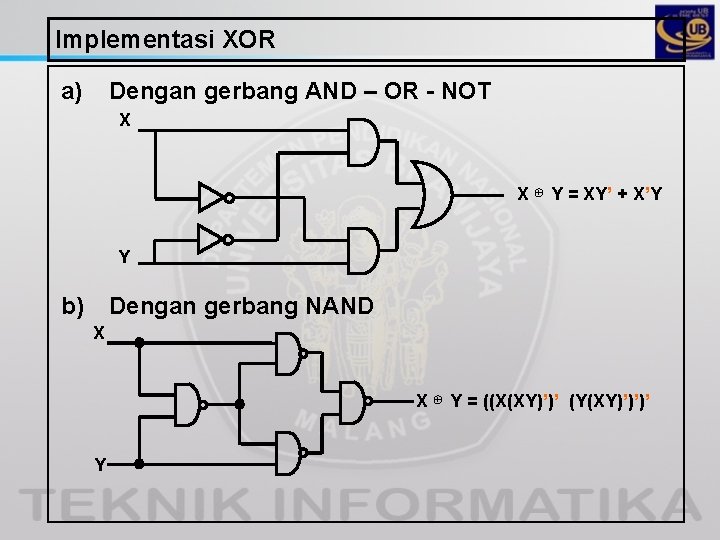

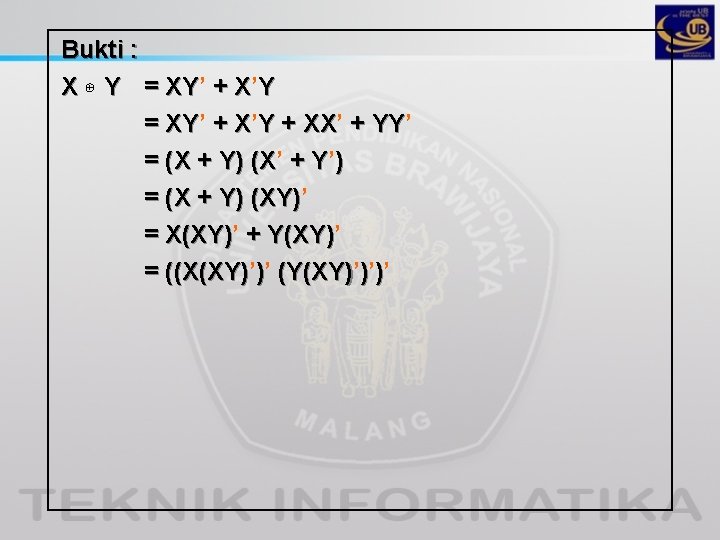

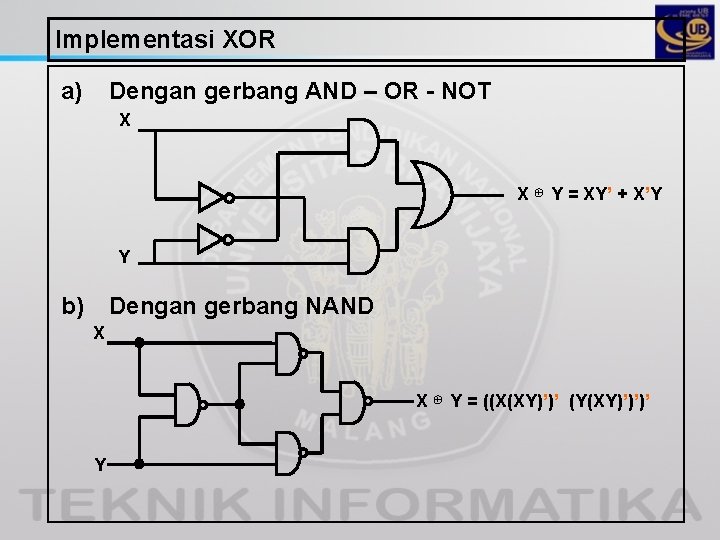

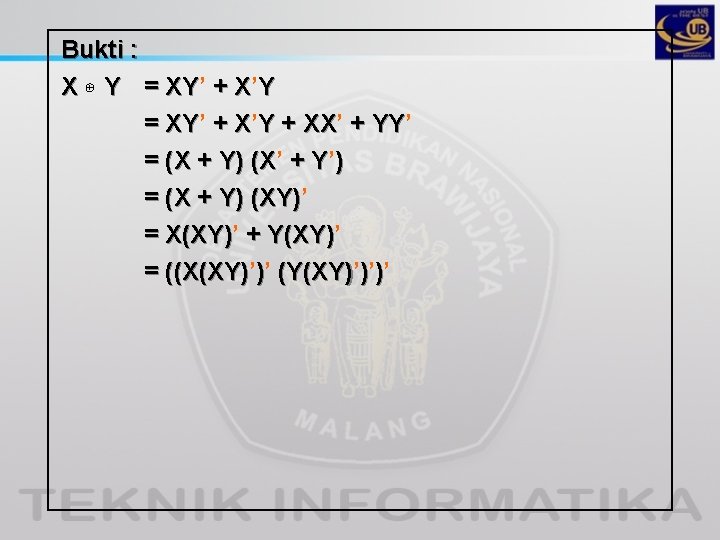

Implementasi XOR a) Dengan gerbang AND – OR - NOT X X ⊕ Y = XY’ + X’Y Y b) Dengan gerbang NAND X X ⊕ Y = ((X(XY)’)’ (Y(XY)’)’)’ Y

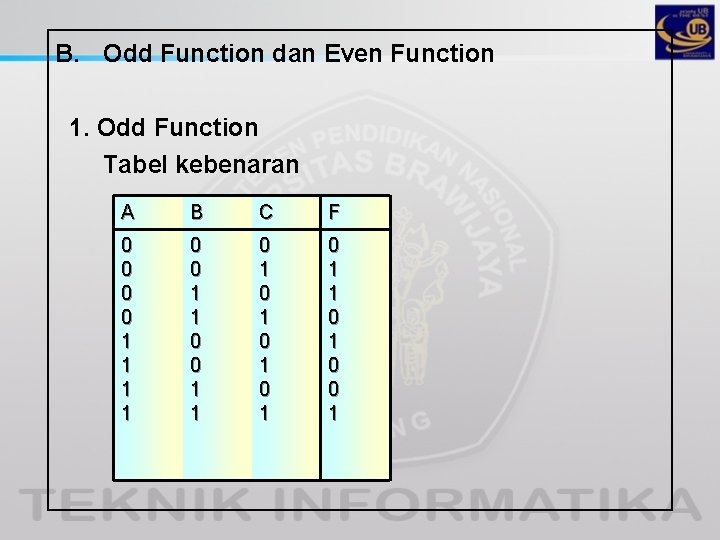

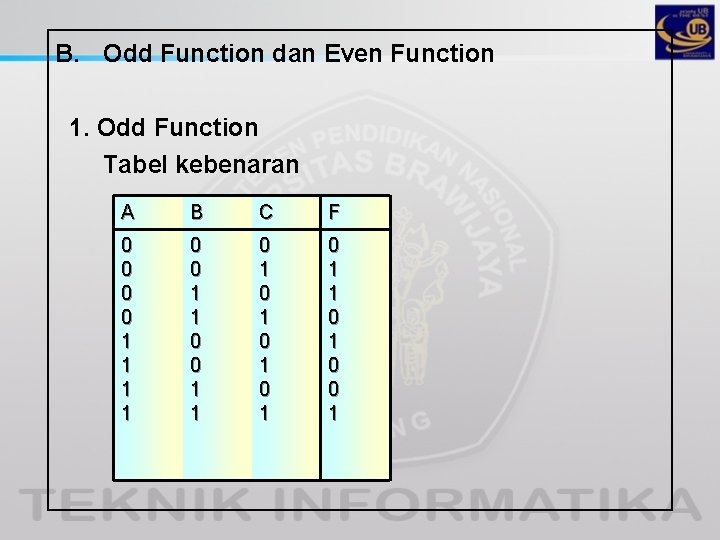

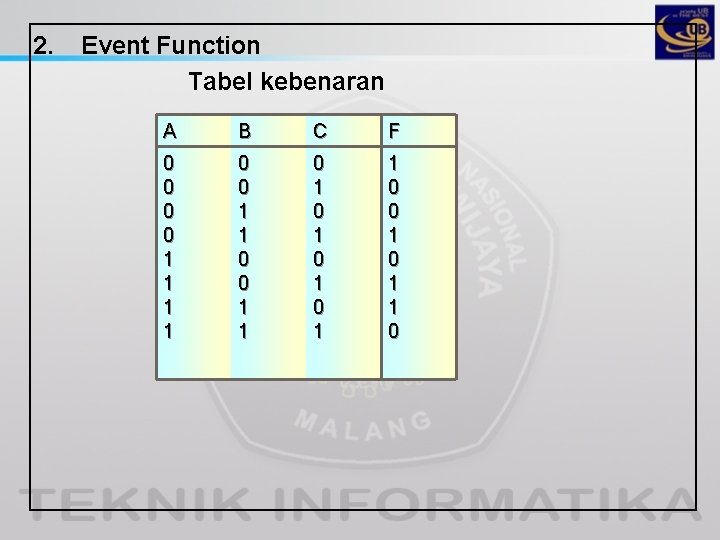

B. Odd Function dan Even Function 1. Odd Function Tabel kebenaran A B C F 0 0 1 1 0 1 0 1 0 1 1 0 0 1

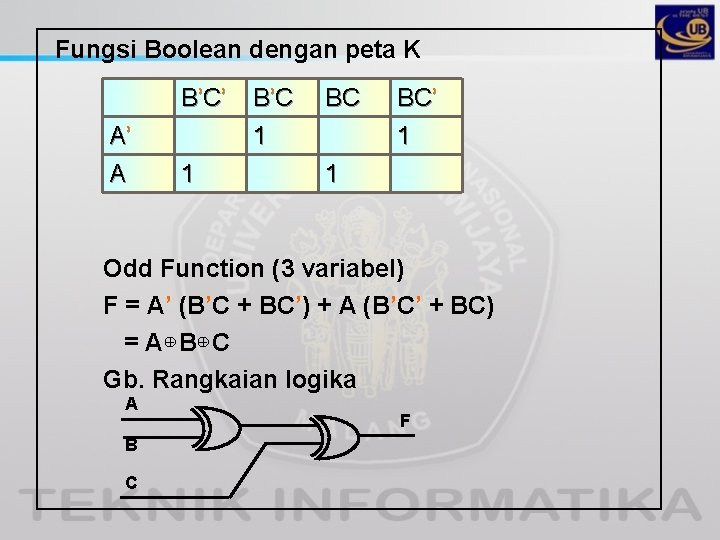

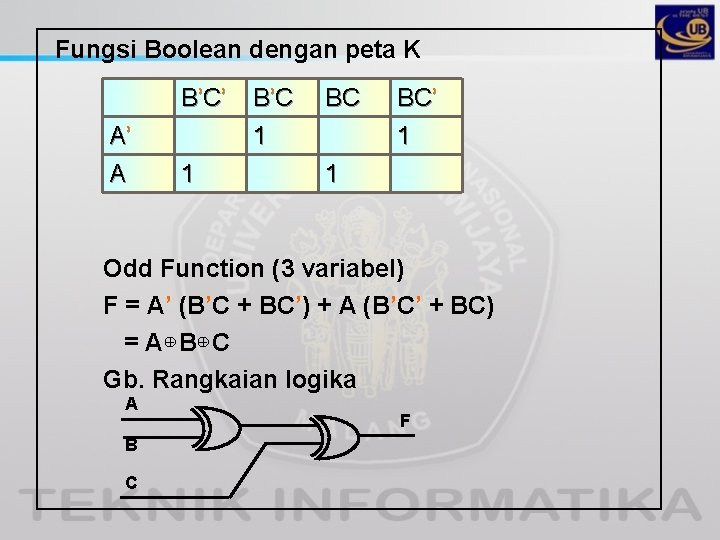

Fungsi Boolean dengan peta K B ’C’ A’ A 1 B ’C 1 BC BC’ 1 1 Odd Function (3 variabel) F = A’ (B’C + BC’) + A (B’C’ + BC) = A⊕ B⊕ C Gb. Rangkaian logika A B C F

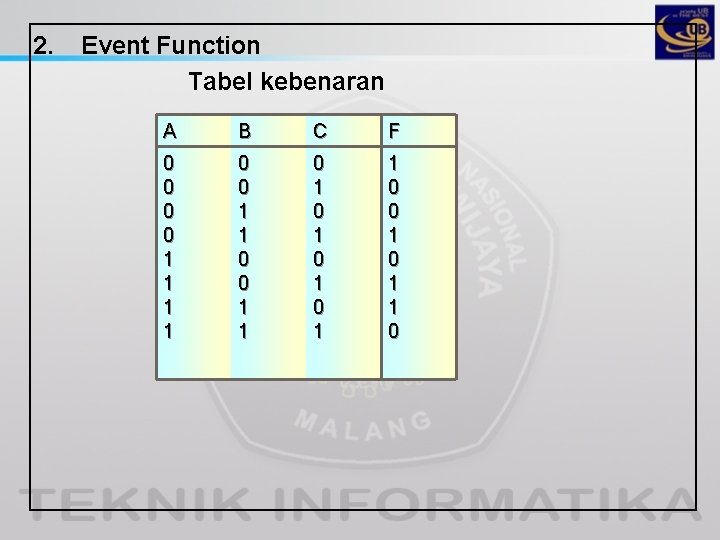

2. Event Function Tabel kebenaran A B C F 0 0 1 1 0 1 0 1 1 0

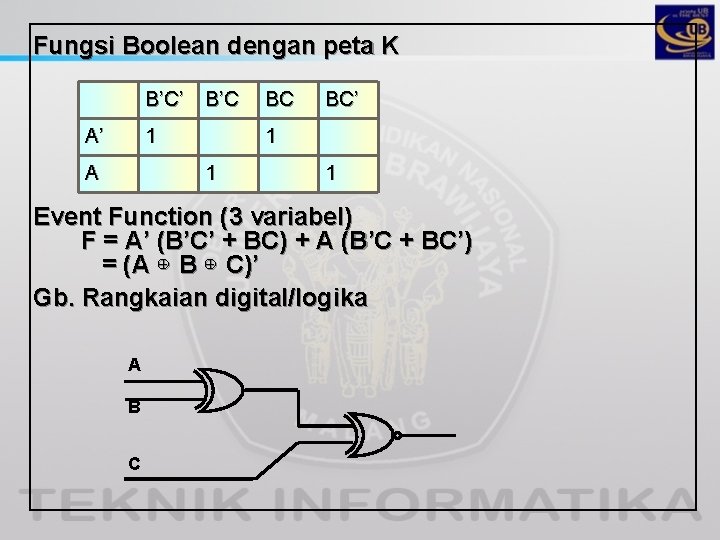

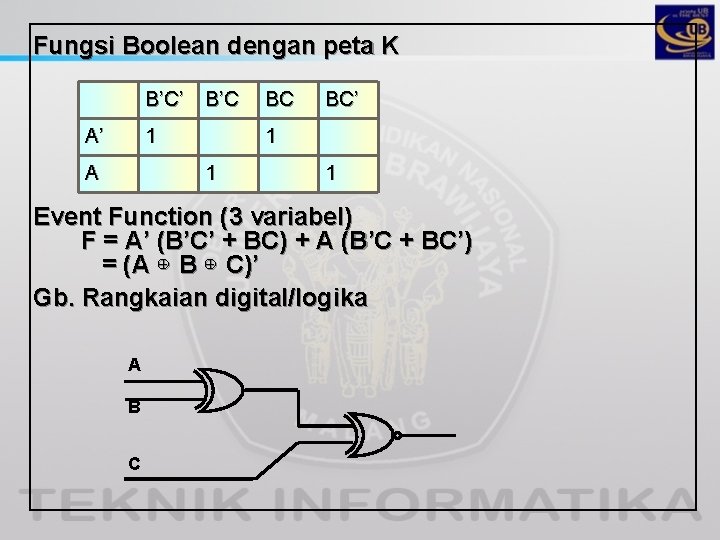

Fungsi Boolean dengan peta K A’ A B’C’ B’C BC 1 1 1 BC’ 1 Event Function (3 variabel) F = A’ (B’C’ + BC) + A (B’C + BC’) = (A ⊕ B ⊕ C)’ Gb. Rangkaian digital/logika A B C

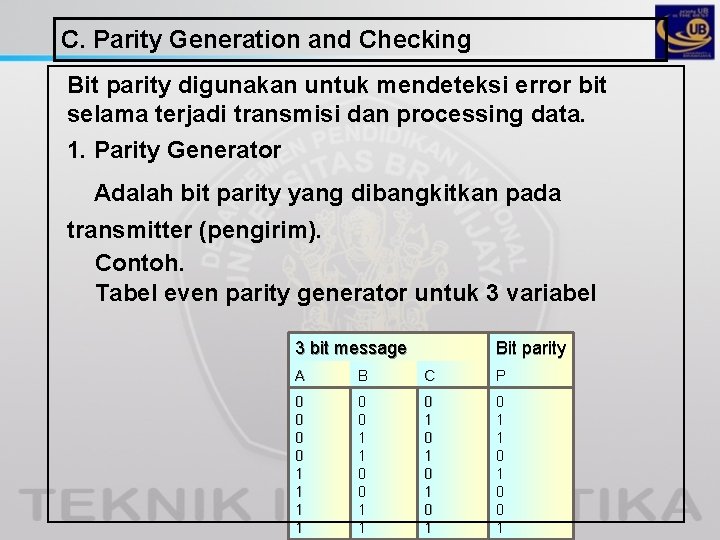

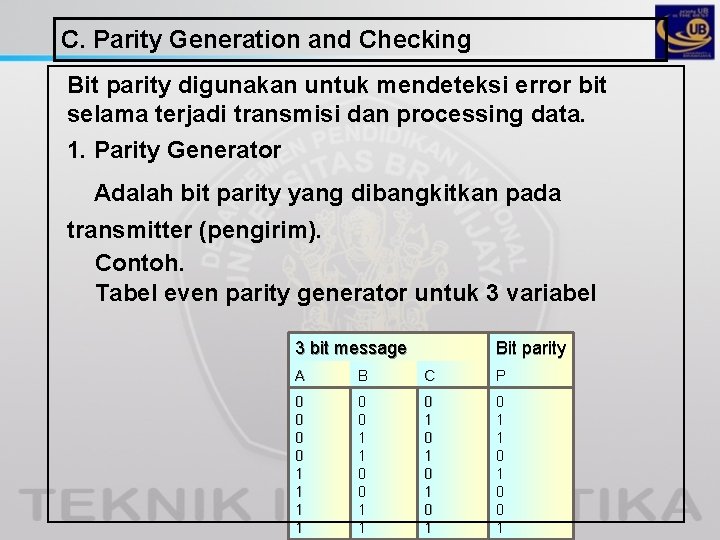

C. Parity Generation and Checking Bit parity digunakan untuk mendeteksi error bit selama terjadi transmisi dan processing data. 1. Parity Generator Adalah bit parity yang dibangkitkan pada transmitter (pengirim). Contoh. Tabel even parity generator untuk 3 variabel 3 bit message Bit parity A B C P 0 0 1 1 0 1 0 1 0 1 1 0 0 1

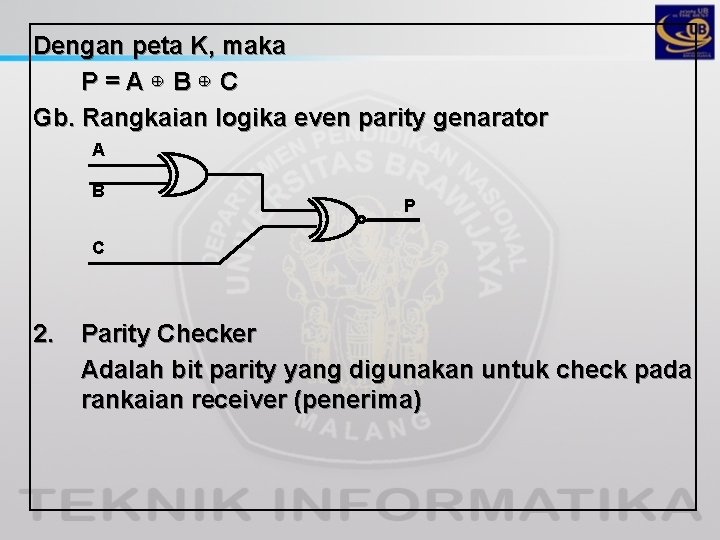

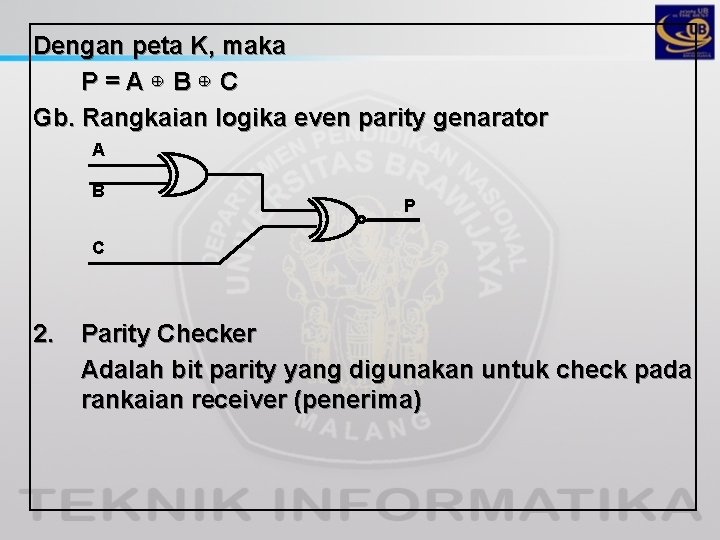

Dengan peta K, maka P=A⊕ B⊕ C Gb. Rangkaian logika even parity genarator A B P C 2. Parity Checker Adalah bit parity yang digunakan untuk check pada rankaian receiver (penerima)

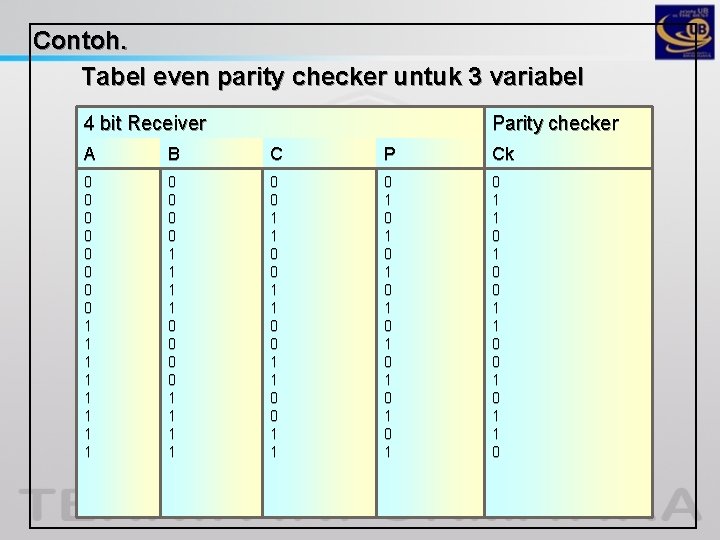

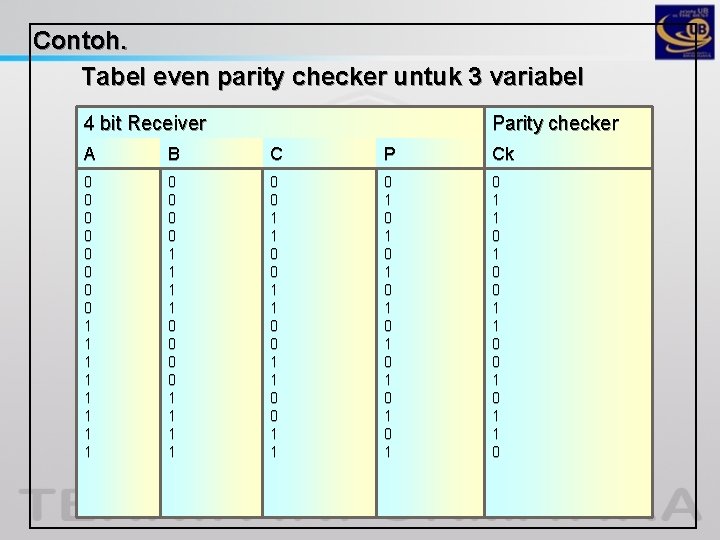

Contoh. Tabel even parity checker untuk 3 variabel 4 bit Receiver Parity checker A B C P Ck 0 0 0 0 1 1 1 1 0 0 1 1 0 1 0 1 0 1 1 0 0 1 1 0

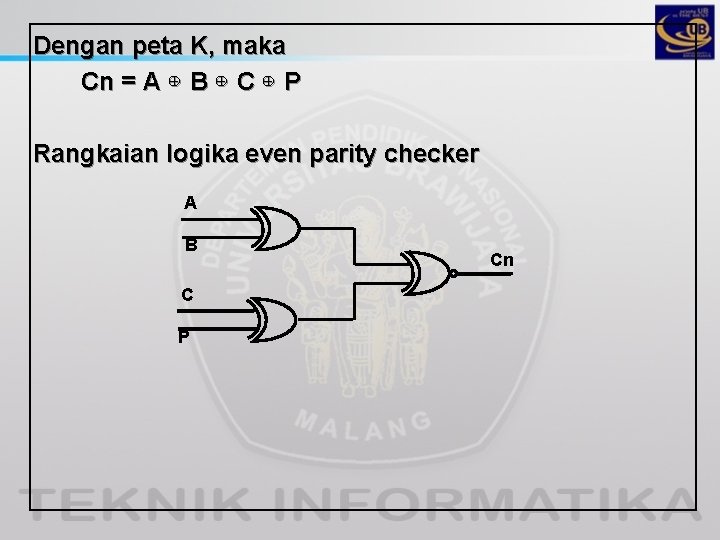

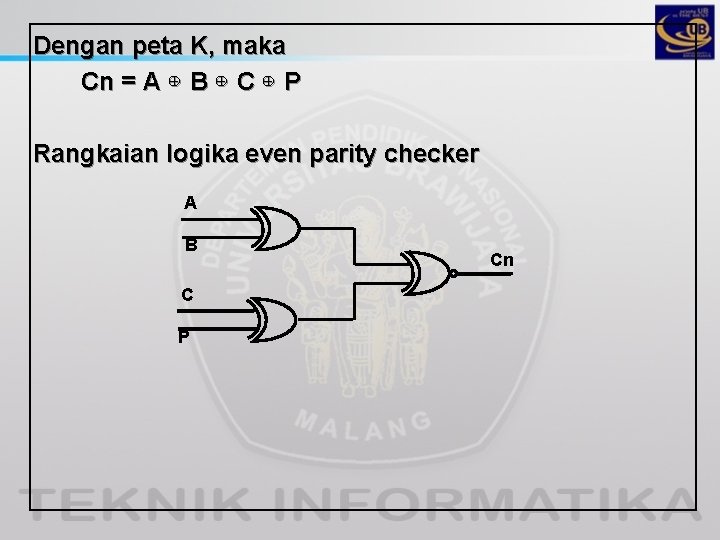

Dengan peta K, maka Cn = A ⊕ B ⊕ C ⊕ P Rangkaian logika even parity checker A B C P Cn

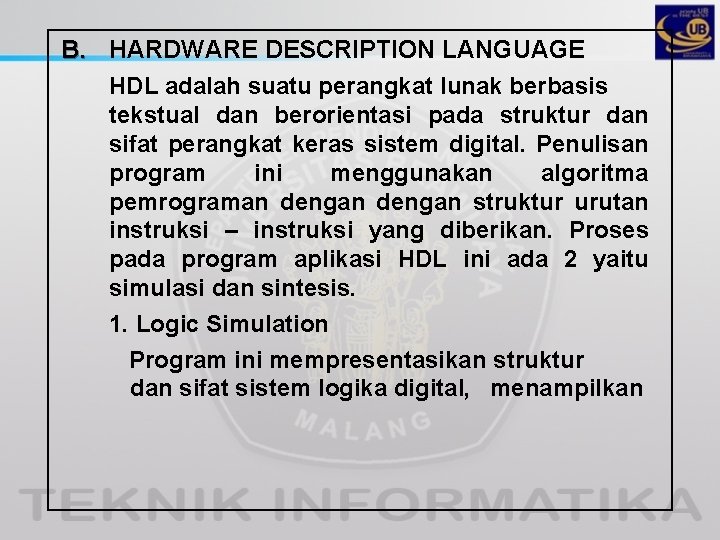

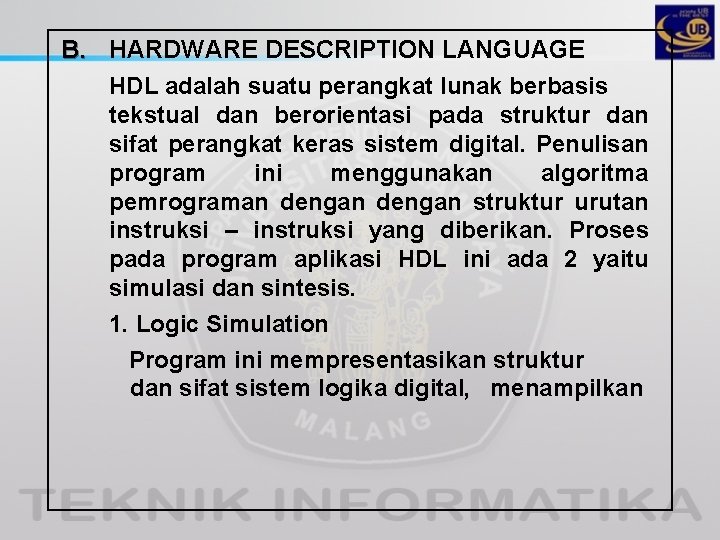

B. HARDWARE DESCRIPTION LANGUAGE HDL adalah suatu perangkat lunak berbasis tekstual dan berorientasi pada struktur dan sifat perangkat keras sistem digital. Penulisan program ini menggunakan algoritma pemrograman dengan struktur urutan instruksi – instruksi yang diberikan. Proses pada program aplikasi HDL ini ada 2 yaitu simulasi dan sintesis. 1. Logic Simulation Program ini mempresentasikan struktur dan sifat sistem logika digital, menampilkan

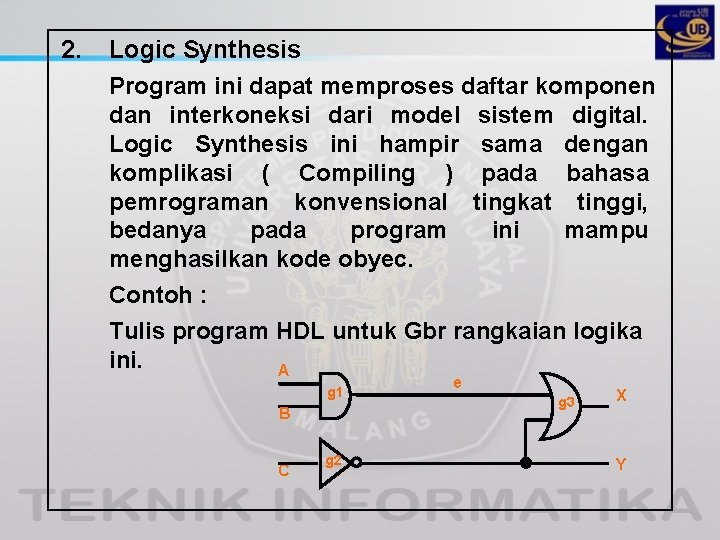

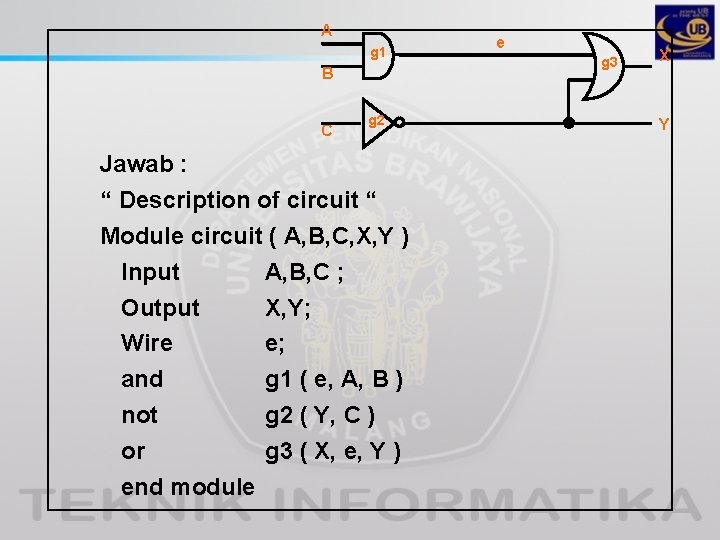

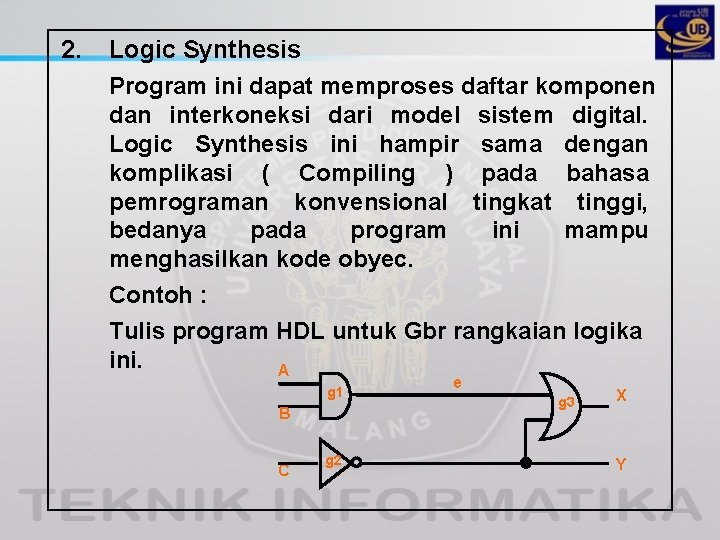

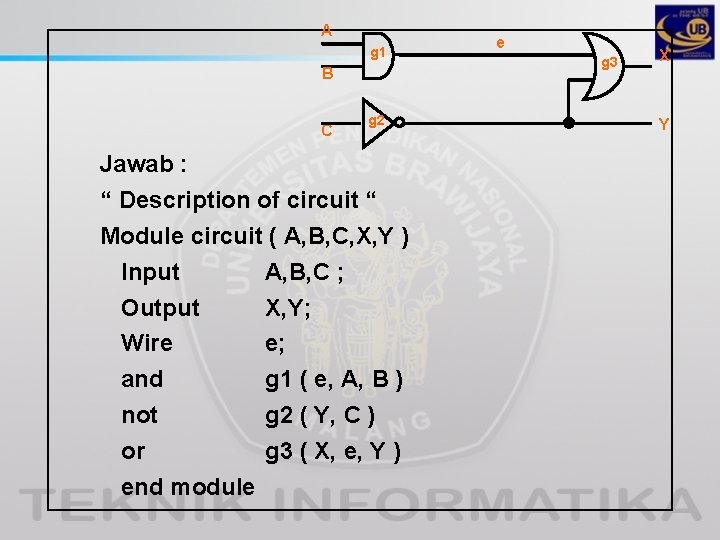

2. Logic Synthesis Program ini dapat memproses daftar komponen dan interkoneksi dari model sistem digital. Logic Synthesis ini hampir sama dengan komplikasi ( Compiling ) pada bahasa pemrograman konvensional tingkat tinggi, bedanya pada program ini mampu menghasilkan kode obyec. Contoh : Tulis program HDL untuk Gbr rangkaian logika ini. A g 1 B C g 2 e g 3 X Y

A g 1 B C g 2 Jawab : “ Description of circuit “ Module circuit ( A, B, C, X, Y ) Input A, B, C ; Output X, Y; Wire e; and g 1 ( e, A, B ) not g 2 ( Y, C ) or g 3 ( X, e, Y ) end module e g 3 X Y