VHDL VER NESNELER Abdurrahman BAYRAK ANKARA EMO FPGA

VHDL VERİ NESNELERİ Abdurrahman BAYRAK ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 1

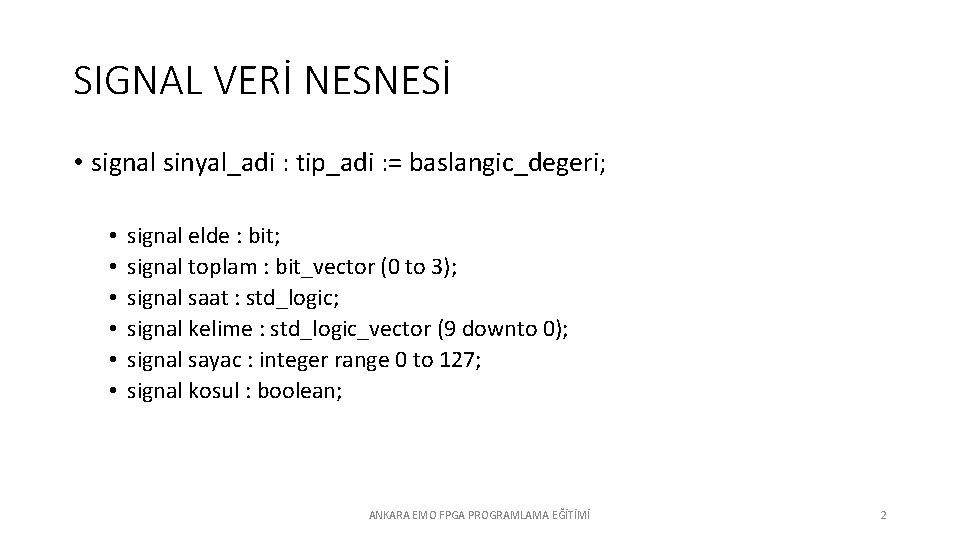

SIGNAL VERİ NESNESİ • signal sinyal_adi : tip_adi : = baslangic_degeri; • • • signal elde : bit; signal toplam : bit_vector (0 to 3); signal saat : std_logic; signal kelime : std_logic_vector (9 downto 0); signal sayac : integer range 0 to 127; signal kosul : boolean; ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 2

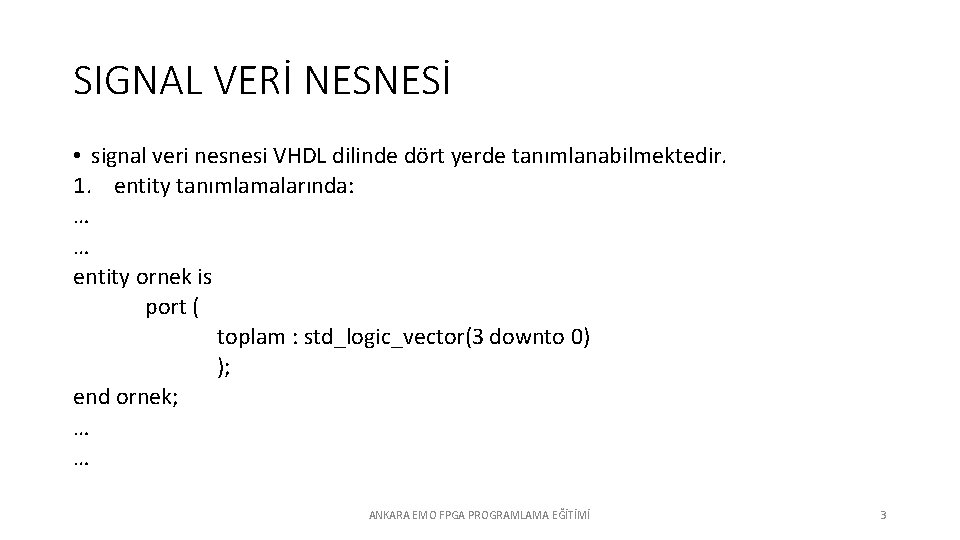

SIGNAL VERİ NESNESİ • signal veri nesnesi VHDL dilinde dört yerde tanımlanabilmektedir. 1. entity tanımlamalarında: … … entity ornek is port ( toplam : std_logic_vector(3 downto 0) ); end ornek; … … ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 3

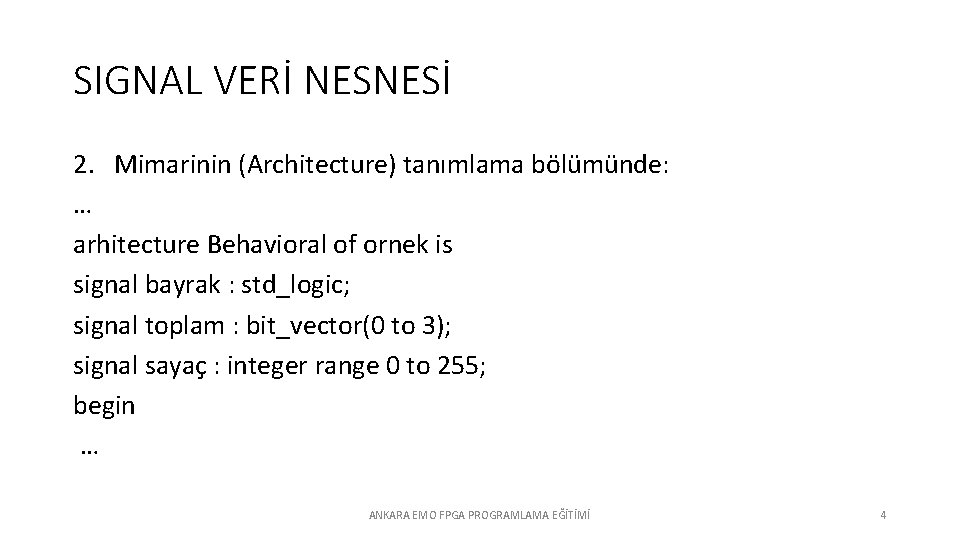

SIGNAL VERİ NESNESİ 2. Mimarinin (Architecture) tanımlama bölümünde: … arhitecture Behavioral of ornek is signal bayrak : std_logic; signal toplam : bit_vector(0 to 3); signal sayaç : integer range 0 to 255; begin … ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 4

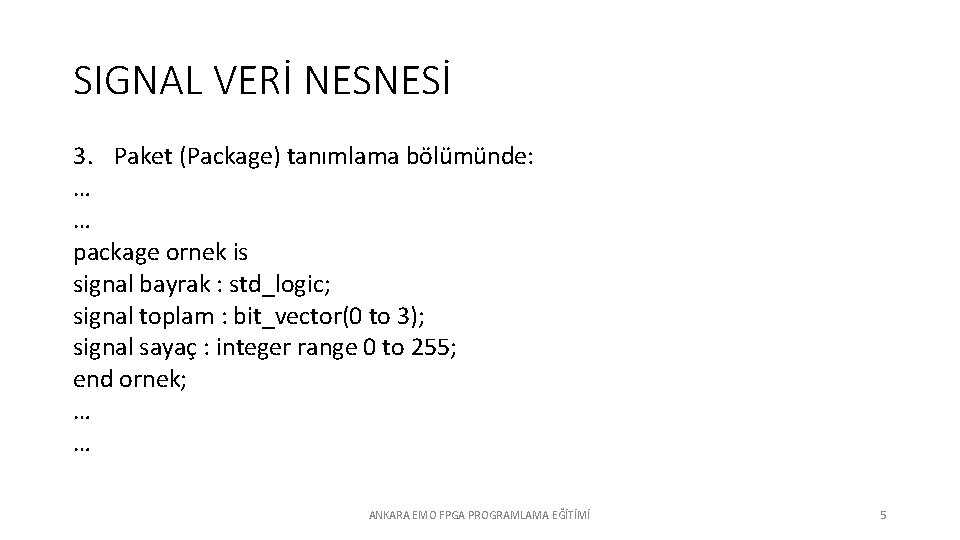

SIGNAL VERİ NESNESİ 3. Paket (Package) tanımlama bölümünde: … … package ornek is signal bayrak : std_logic; signal toplam : bit_vector(0 to 3); signal sayaç : integer range 0 to 255; end ornek; … … ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 5

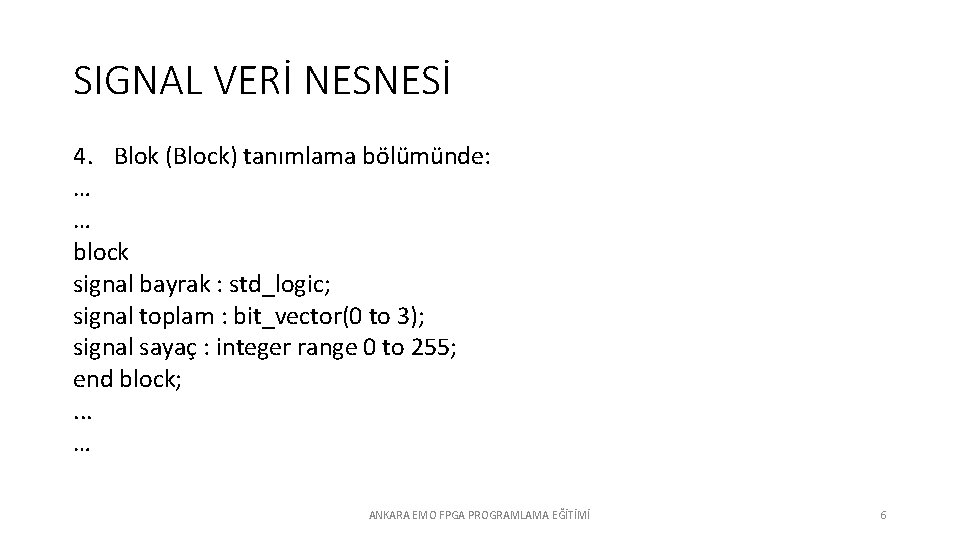

SIGNAL VERİ NESNESİ 4. Blok (Block) tanımlama bölümünde: … … block signal bayrak : std_logic; signal toplam : bit_vector(0 to 3); signal sayaç : integer range 0 to 255; end block; . . . … ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 6

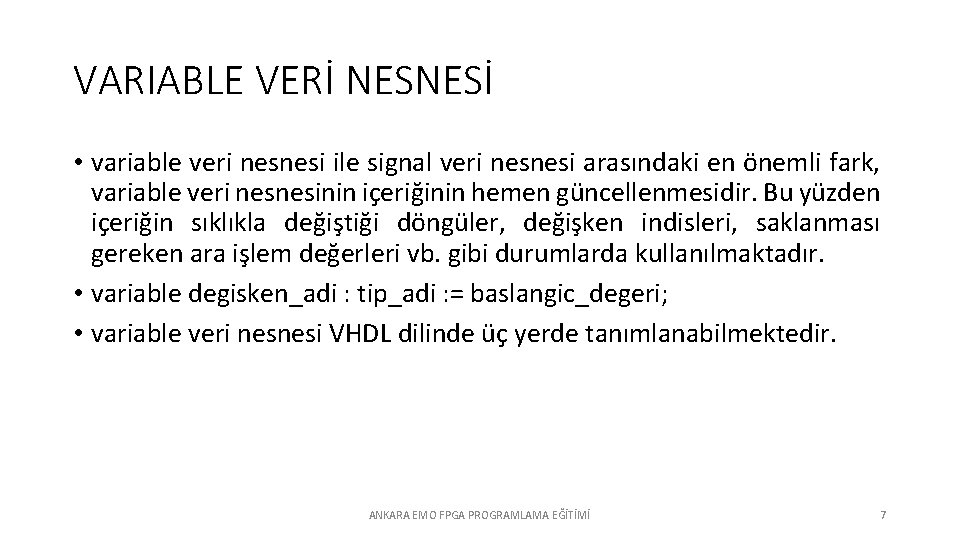

VARIABLE VERİ NESNESİ • variable veri nesnesi ile signal veri nesnesi arasındaki en önemli fark, variable veri nesnesinin içeriğinin hemen güncellenmesidir. Bu yüzden içeriğin sıklıkla değiştiği döngüler, değişken indisleri, saklanması gereken ara işlem değerleri vb. gibi durumlarda kullanılmaktadır. • variable degisken_adi : tip_adi : = baslangic_degeri; • variable veri nesnesi VHDL dilinde üç yerde tanımlanabilmektedir. ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 7

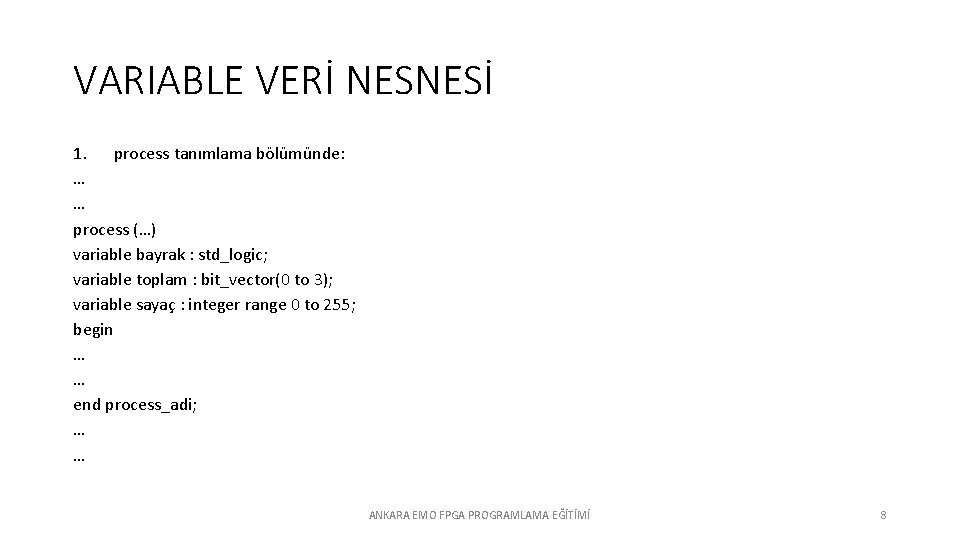

VARIABLE VERİ NESNESİ 1. process tanımlama bölümünde: … … process (…) variable bayrak : std_logic; variable toplam : bit_vector(0 to 3); variable sayaç : integer range 0 to 255; begin … … end process_adi; … … ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 8

VARIABLE VERİ NESNESİ 2. function tanımlama bölümünde: … … function fonksiyon_adi (parametreler listesi) return donus_tipi is variable bayrak : std_logic; variable toplam : bit_vector(0 to 3); variable sayaç : integer range 0 to 255; begin … … end fonksiyon_adi; … … ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 9

VARIABLE VERİ NESNESİ 3. procedure tanımlama bölümünde: … … procedure_adi (parametreler listesi) is variable bayrak : std_logic; variable toplam : bit_vector(0 to 3); variable sayaç : integer range 0 to 255; begin … … end procedure_adi; … … ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 10

CONSTANT VERİ NESNESİ • constant sabit_adi : tip_adi : = sabit_deger; constant bir : bit_vector(7 downto 0) : ="00000001"; constant bir : std_logic_vector(7 downto 0) : ="00000001"; constant bir : integer : =1; • constant veri nesnesi VHDL dilinde sekiz yerde tanımlanabilmektedir. • • package body block entity architecture process procedure function ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 11

VERİ NESNELERİNİN ADLANDIRILMASI 1. Adlandırılacak isim VHDL anahtar sözcüklerinden olmamalıdır. 2. Harf ile başlamaldır. 3. Alt çizgi ile bitmemelidir. 4. Aynı anda 2 alt çizgi karakteri kullanılmamalıdır. 5. Türkçe’ye has karakterler kullanılmamalıdır. (ç, ğ, ş , ı, ö, ü) • entity VHDL anahtar sözcüğü olduğu için tanımlanamaz. VHDL’de büyük veya küçük karakter kullanımı önemli değildir. ‘y’ ile ‘Y’, ‘if’ ile ‘IF’ aynıdır. ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 12

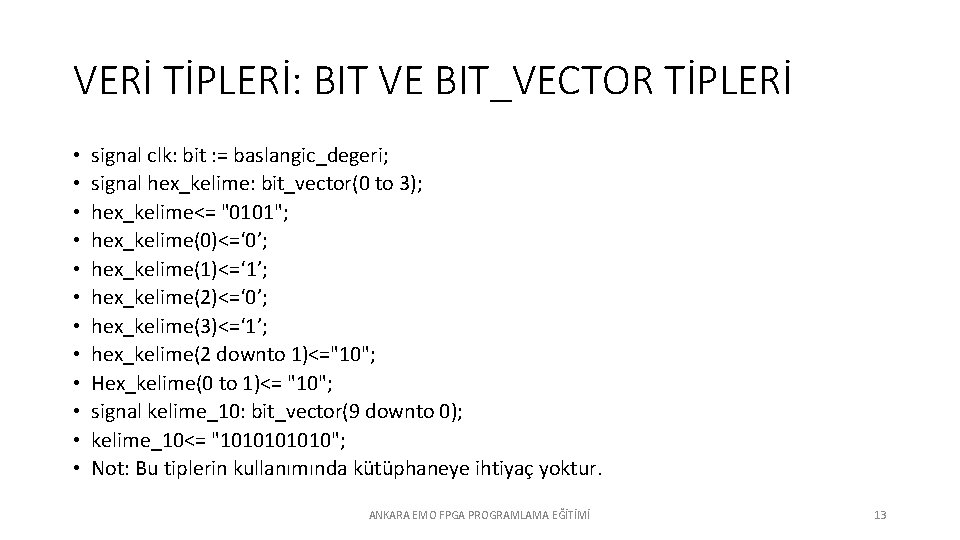

VERİ TİPLERİ: BIT VE BIT_VECTOR TİPLERİ • • • signal clk: bit : = baslangic_degeri; signal hex_kelime: bit_vector(0 to 3); hex_kelime<= "0101"; hex_kelime(0)<=‘ 0’; hex_kelime(1)<=‘ 1’; hex_kelime(2)<=‘ 0’; hex_kelime(3)<=‘ 1’; hex_kelime(2 downto 1)<="10"; Hex_kelime(0 to 1)<= "10"; signal kelime_10: bit_vector(9 downto 0); kelime_10<= "101010"; Not: Bu tiplerin kullanımında kütüphaneye ihtiyaç yoktur. ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 13

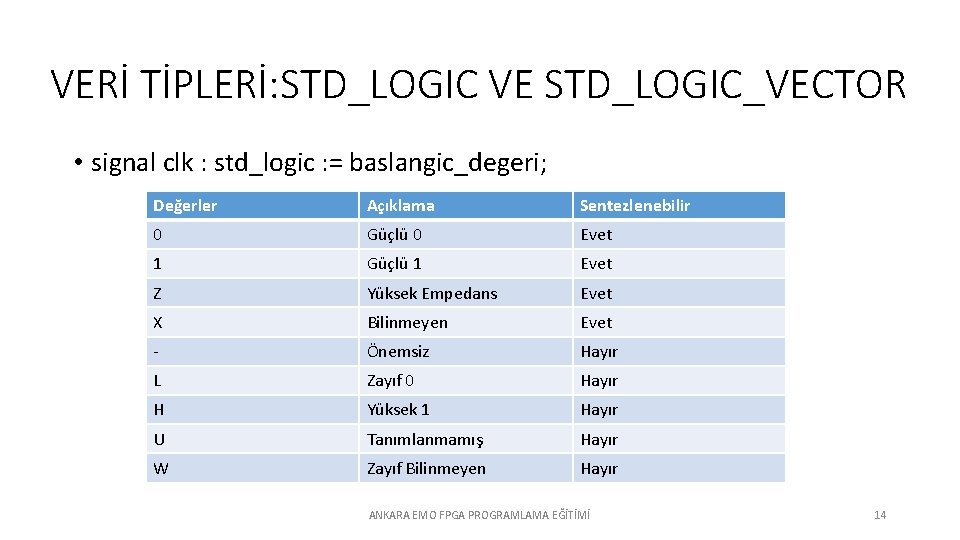

VERİ TİPLERİ: STD_LOGIC VE STD_LOGIC_VECTOR • signal clk : std_logic : = baslangic_degeri; Değerler Açıklama Sentezlenebilir 0 Güçlü 0 Evet 1 Güçlü 1 Evet Z Yüksek Empedans Evet X Bilinmeyen Evet - Önemsiz Hayır L Zayıf 0 Hayır H Yüksek 1 Hayır U Tanımlanmamış Hayır W Zayıf Bilinmeyen Hayır ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 14

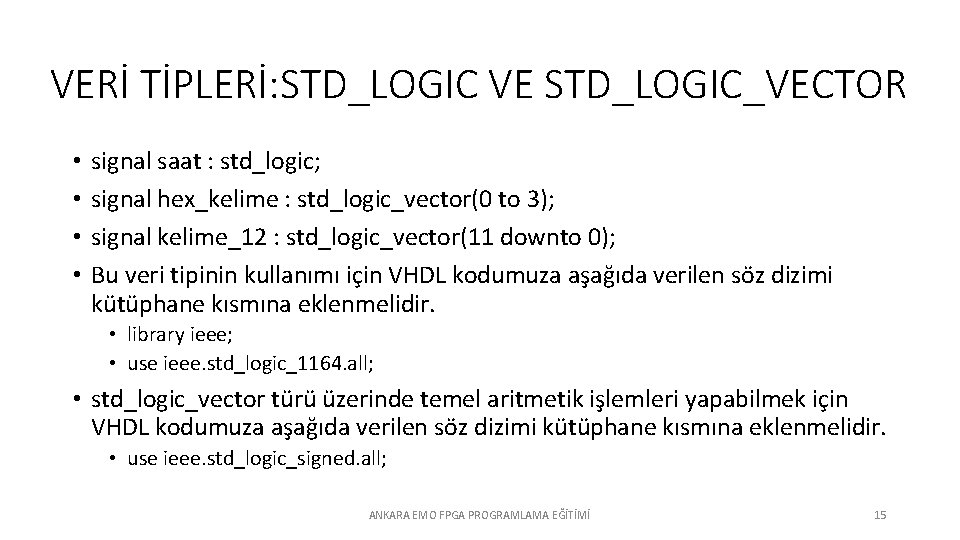

VERİ TİPLERİ: STD_LOGIC VE STD_LOGIC_VECTOR • • signal saat : std_logic; signal hex_kelime : std_logic_vector(0 to 3); signal kelime_12 : std_logic_vector(11 downto 0); Bu veri tipinin kullanımı için VHDL kodumuza aşağıda verilen söz dizimi kütüphane kısmına eklenmelidir. • library ieee; • use ieee. std_logic_1164. all; • std_logic_vector türü üzerinde temel aritmetik işlemleri yapabilmek için VHDL kodumuza aşağıda verilen söz dizimi kütüphane kısmına eklenmelidir. • use ieee. std_logic_signed. all; ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 15

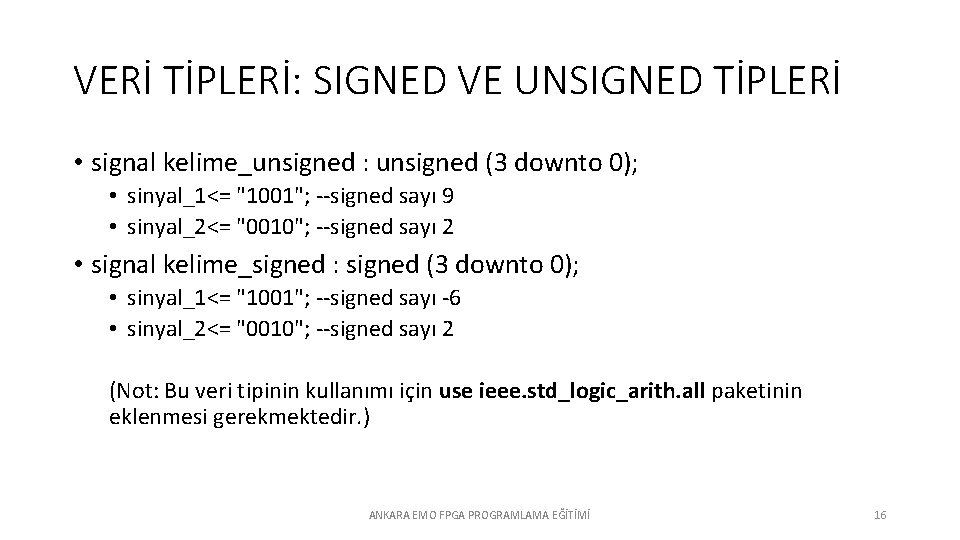

VERİ TİPLERİ: SIGNED VE UNSIGNED TİPLERİ • signal kelime_unsigned : unsigned (3 downto 0); • sinyal_1<= "1001"; --signed sayı 9 • sinyal_2<= "0010"; --signed sayı 2 • signal kelime_signed : signed (3 downto 0); • sinyal_1<= "1001"; --signed sayı -6 • sinyal_2<= "0010"; --signed sayı 2 (Not: Bu veri tipinin kullanımı için use ieee. std_logic_arith. all paketinin eklenmesi gerekmektedir. ) ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 16

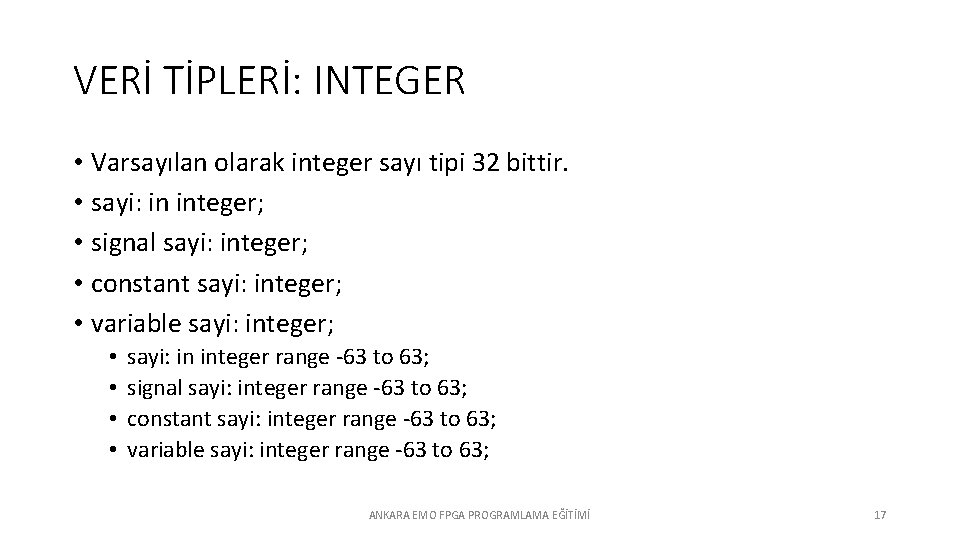

VERİ TİPLERİ: INTEGER • Varsayılan olarak integer sayı tipi 32 bittir. • sayi: in integer; • signal sayi: integer; • constant sayi: integer; • variable sayi: integer; • • sayi: in integer range -63 to 63; signal sayi: integer range -63 to 63; constant sayi: integer range -63 to 63; variable sayi: integer range -63 to 63; ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 17

VERİ TİPLERİ: BOOLEAN • TRUE • FALSE • signal bayrak : boolean; ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 18

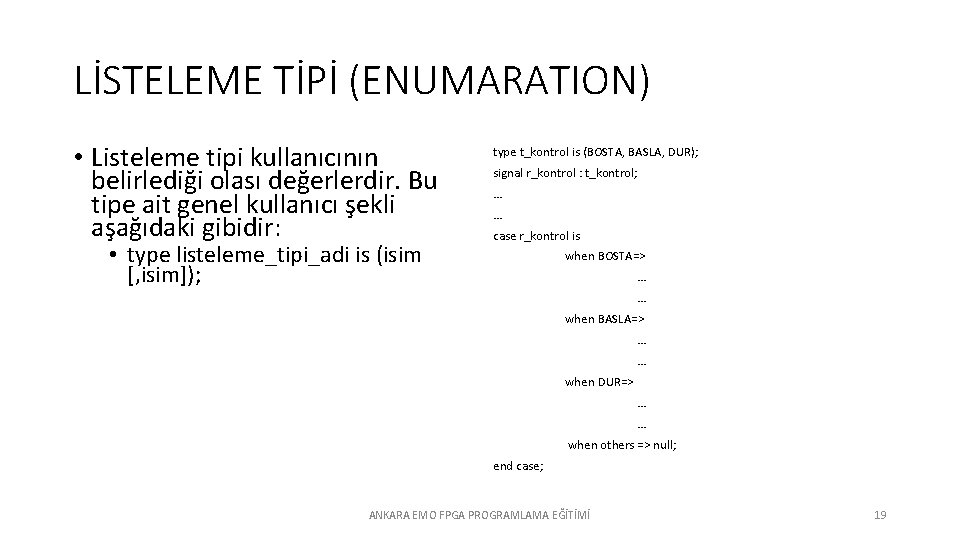

LİSTELEME TİPİ (ENUMARATION) • Listeleme tipi kullanıcının belirlediği olası değerlerdir. Bu tipe ait genel kullanıcı şekli aşağıdaki gibidir: • type listeleme_tipi_adi is (isim [, isim]); type t_kontrol is (BOSTA, BASLA, DUR); signal r_kontrol : t_kontrol; … … case r_kontrol is when BOSTA=> … … when BASLA=> … … when DUR=> … … when others => null; end case; ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 19

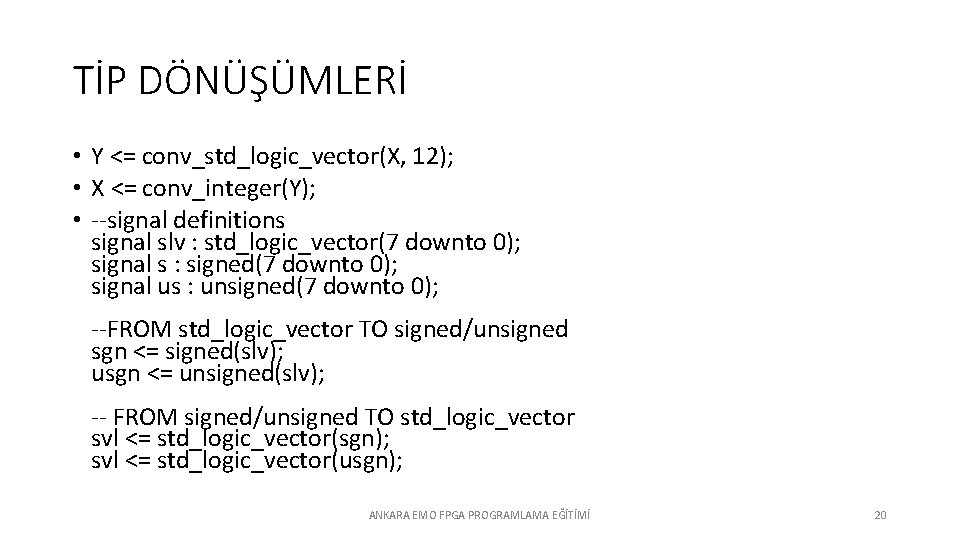

TİP DÖNÜŞÜMLERİ • Y <= conv_std_logic_vector(X, 12); • X <= conv_integer(Y); • --signal definitions signal slv : std_logic_vector(7 downto 0); signal s : signed(7 downto 0); signal us : unsigned(7 downto 0); --FROM std_logic_vector TO signed/unsigned sgn <= signed(slv); usgn <= unsigned(slv); -- FROM signed/unsigned TO std_logic_vector svl <= std_logic_vector(sgn); svl <= std_logic_vector(usgn); ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 20

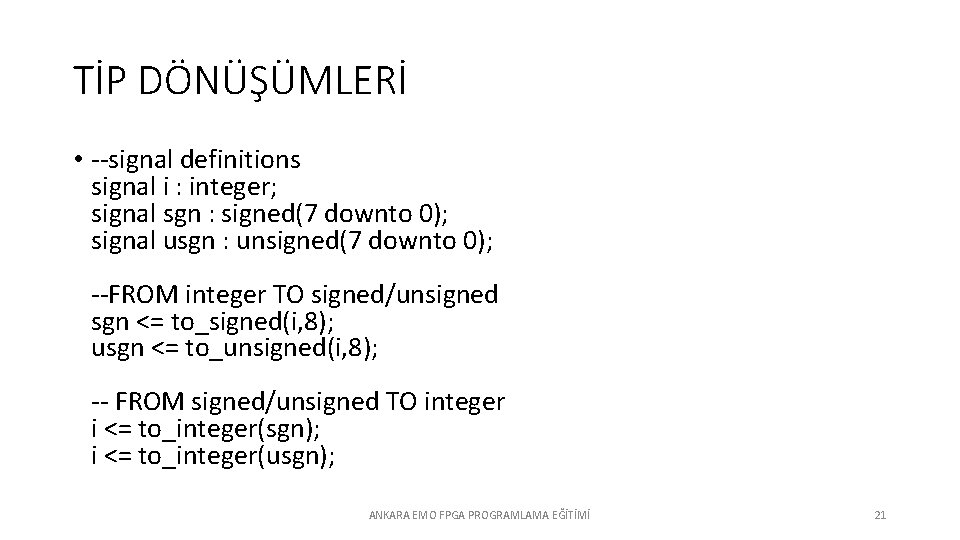

TİP DÖNÜŞÜMLERİ • --signal definitions signal i : integer; signal sgn : signed(7 downto 0); signal usgn : unsigned(7 downto 0); --FROM integer TO signed/unsigned sgn <= to_signed(i, 8); usgn <= to_unsigned(i, 8); -- FROM signed/unsigned TO integer i <= to_integer(sgn); i <= to_integer(usgn); ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 21

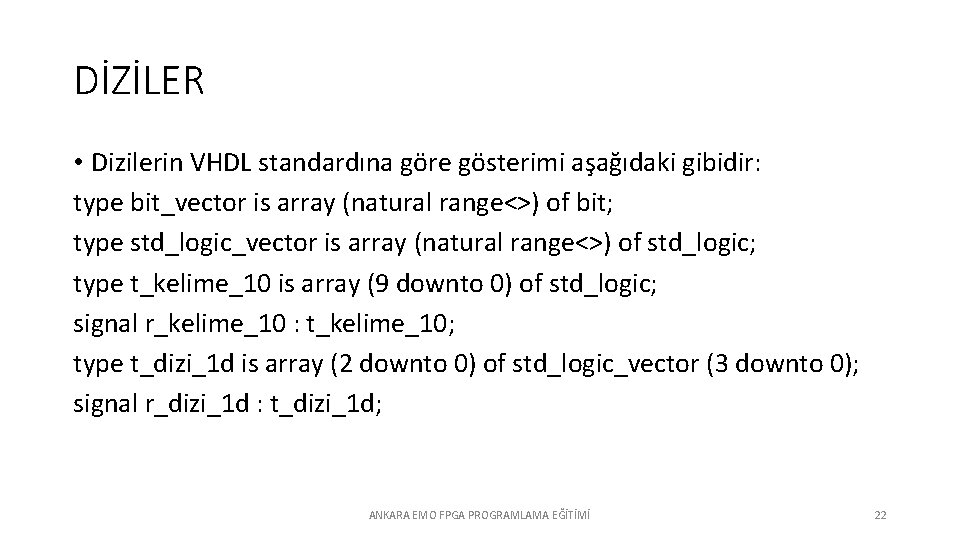

DİZİLER • Dizilerin VHDL standardına göre gösterimi aşağıdaki gibidir: type bit_vector is array (natural range<>) of bit; type std_logic_vector is array (natural range<>) of std_logic; type t_kelime_10 is array (9 downto 0) of std_logic; signal r_kelime_10 : t_kelime_10; type t_dizi_1 d is array (2 downto 0) of std_logic_vector (3 downto 0); signal r_dizi_1 d : t_dizi_1 d; ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 22

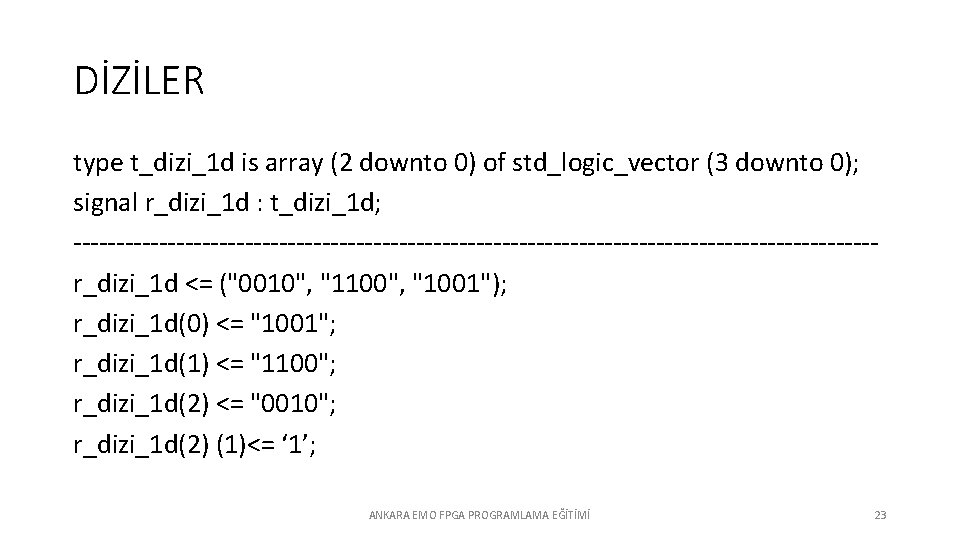

DİZİLER type t_dizi_1 d is array (2 downto 0) of std_logic_vector (3 downto 0); signal r_dizi_1 d : t_dizi_1 d; -----------------------------------------------r_dizi_1 d <= ("0010", "1100", "1001"); r_dizi_1 d(0) <= "1001"; r_dizi_1 d(1) <= "1100"; r_dizi_1 d(2) <= "0010"; r_dizi_1 d(2) (1)<= ‘ 1’; ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 23

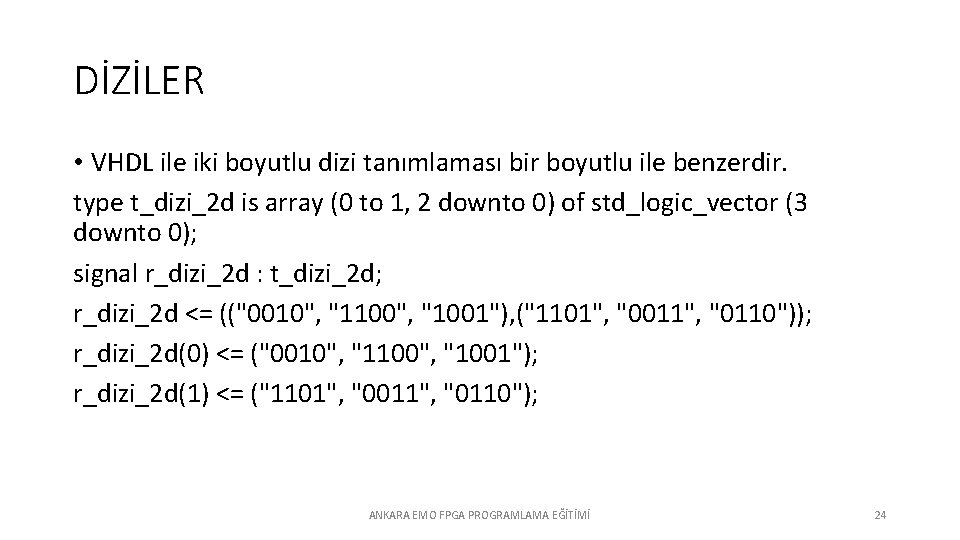

DİZİLER • VHDL ile iki boyutlu dizi tanımlaması bir boyutlu ile benzerdir. type t_dizi_2 d is array (0 to 1, 2 downto 0) of std_logic_vector (3 downto 0); signal r_dizi_2 d : t_dizi_2 d; r_dizi_2 d <= (("0010", "1100", "1001"), ("1101", "0011", "0110")); r_dizi_2 d(0) <= ("0010", "1100", "1001"); r_dizi_2 d(1) <= ("1101", "0011", "0110"); ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 24

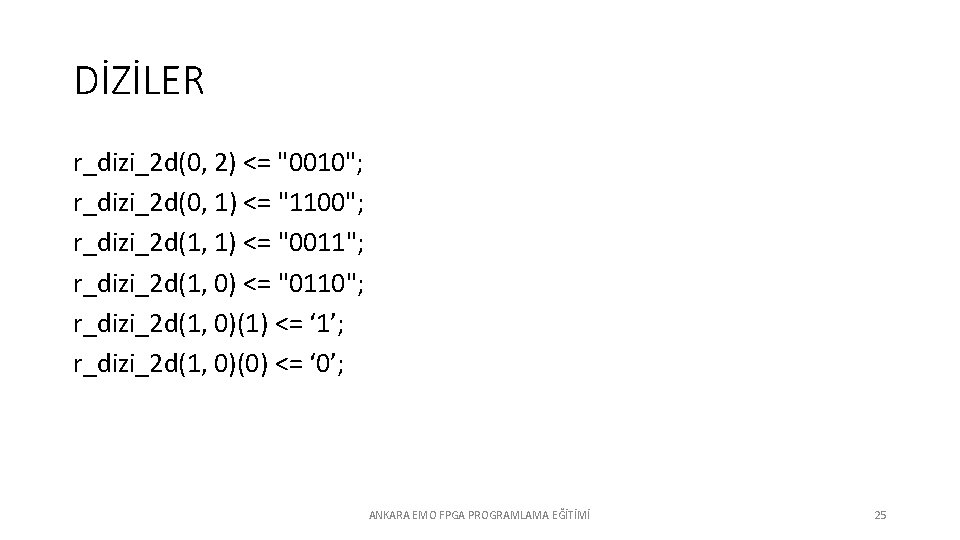

DİZİLER r_dizi_2 d(0, 2) <= "0010"; r_dizi_2 d(0, 1) <= "1100"; r_dizi_2 d(1, 1) <= "0011"; r_dizi_2 d(1, 0) <= "0110"; r_dizi_2 d(1, 0)(1) <= ‘ 1’; r_dizi_2 d(1, 0)(0) <= ‘ 0’; ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 25

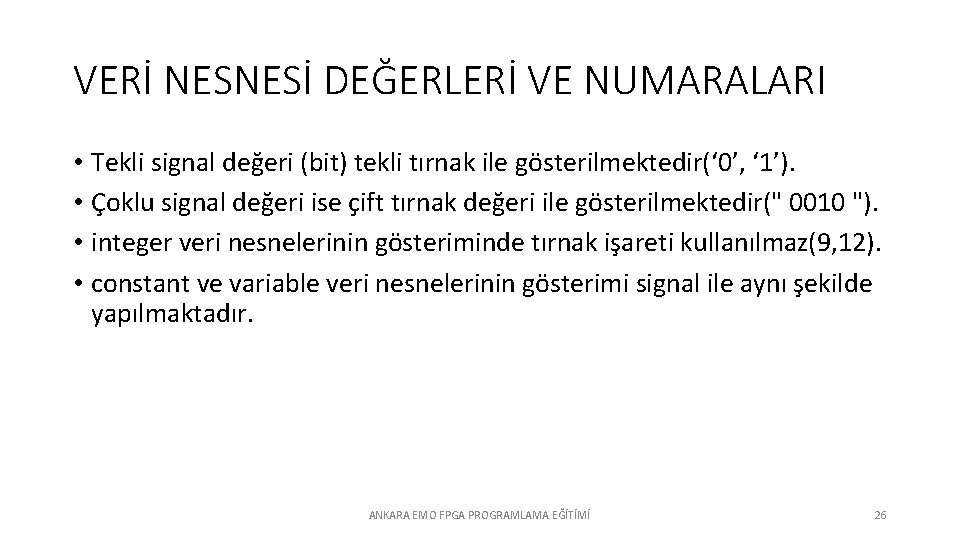

VERİ NESNESİ DEĞERLERİ VE NUMARALARI • Tekli signal değeri (bit) tekli tırnak ile gösterilmektedir(‘ 0’, ‘ 1’). • Çoklu signal değeri ise çift tırnak değeri ile gösterilmektedir(" 0010 "). • integer veri nesnelerinin gösteriminde tırnak işareti kullanılmaz(9, 12). • constant ve variable veri nesnelerinin gösterimi signal ile aynı şekilde yapılmaktadır. ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 26

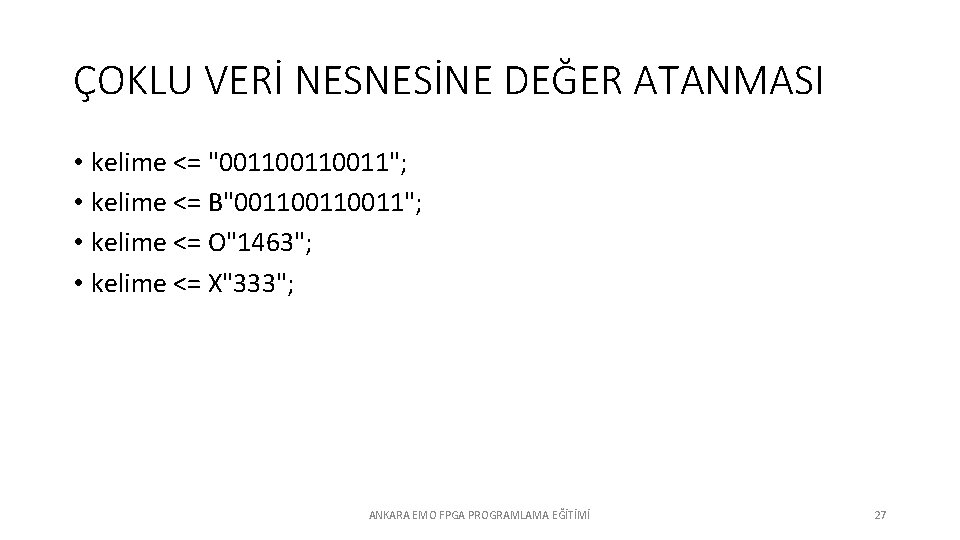

ÇOKLU VERİ NESNESİNE DEĞER ATANMASI • kelime <= "00110011"; • kelime <= B"00110011"; • kelime <= O"1463"; • kelime <= X"333"; ANKARA EMO FPGA PROGRAMLAMA EĞİTİMİ 27

- Slides: 27