VHDL Structured Logic Design School of Electrical Engineering

- Slides: 29

VHDL Structured Logic Design School of Electrical Engineering University of Belgrade Department of Computer Engineering Ivan Dugic idugic@verat. net Veljko Milutinovic vm@etf. bg. ac. yu

Table of contents § HDL Introduction § Structured Design Concepts § Basic Features of VHDL § Design Process Highlights Ivan Dugic idugic@verat. net 2

HDL Introduction Ivan Dugic idugic@verat. net 3

HDL Introduction Modern chip design aspects § Modern chips became too complex § The number of transistors in a modern chip is over a 100 M § Transistor count per chip and chip speed rise up to 50% per year § Estimated time needed for manual implementation (100 M transistor, 10 sec/transistor) – 135. 5 years!!! Ivan Dugic idugic@verat. net 4

HDL Introduction Modern ASIC design approach § ASIC – Application Specific Integrated Circuit § Modeling system should be designed and described in the highest abstraction level possible § Simulation and testing at high abstraction level § Conversion of the modeled system into the low abstraction level model (gate, circuit, silicon level) using sophisticated synthesis tools § Key point – CAD (Computer Aided Design) Ivan Dugic idugic@verat. net 5

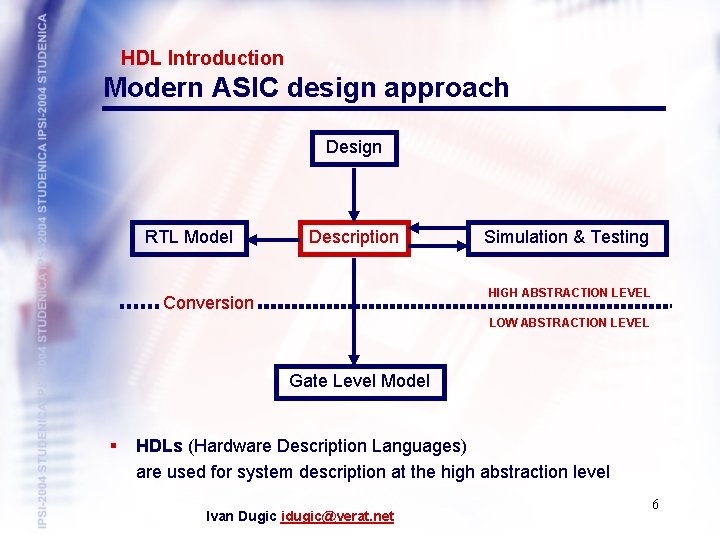

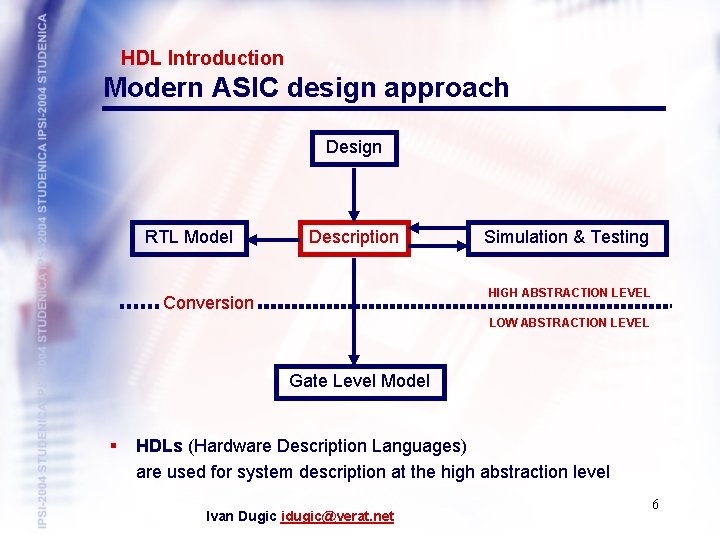

HDL Introduction Modern ASIC design approach Design RTL Model Description Simulation & Testing HIGH ABSTRACTION LEVEL Conversion LOW ABSTRACTION LEVEL Gate Level Model § HDLs (Hardware Description Languages) are used for system description at the high abstraction level Ivan Dugic idugic@verat. net 6

HDL Introduction VHDL § VHDL - VHSIC Hardware Description Language § VHSIC - Very High Speed Integrated Circuit § Development of VHDL began in 1983, sponsored by Department of defense, further developed by the IEEE and released as IEEE Standard 1076 in 1987 § Today it is De facto industry standard for hardware description languages Ivan Dugic idugic@verat. net 7

Structural Design Concepts Ivan Dugic idugic@verat. net 8

Structural Design Concepts The abstraction hierarchy § The abstraction hierarchy can be expressed in two domains: structural domain, behavioral domain § Structural domain – component model is described in terms of an interconnection of more primitive components § Behavioral domain – component model is described by defining its input/output response § VHDL is used for both structural and behavioral description § Six abstraction hierarchy levels of detail commonly used in design: silicon, circuit, gate, register, chip and system Ivan Dugic idugic@verat. net 9

Structural Design Concepts Design process § The design cycle consists of a series of transformations, synthesis steps: (1) Transformation from English to an algorithmic representation, natural language synthesis (2) Translation from an algorithmic representation to a data flow representation, algorithmic synthesis (3) Translation from data flow representation to a structural logic gate representation, logic synthesis (4) Translation from logic gate to layout and circuit representation, layout synthesis Ivan Dugic idugic@verat. net 10

Structural Design Concepts Design process § The design cycle steps can be carried out automatically in all stages except the first that is currently an active area of research § VHDL tools are used for algorithmic synthesis Ivan Dugic idugic@verat. net 11

Structural Design Concepts Design tools § Editors – textual (circuit level – SPICE gate, register, chip – VHDL) or graphic (used at all levels) § Simulators – stochastic (system level) or deterministic (all levels above the silicon level) § Checkers and Analyzers – employed at all levels, used for example (1) to insure that the circuit layout can be fabricated reliably (rule checkers), (2) to check for the longest path through a logic circuit or system (timing analyzers) § Synthesizers and Optimizers – improving a form of the design representation Ivan Dugic idugic@verat. net 12

Basic Features of VHDL Ivan Dugic idugic@verat. net 13

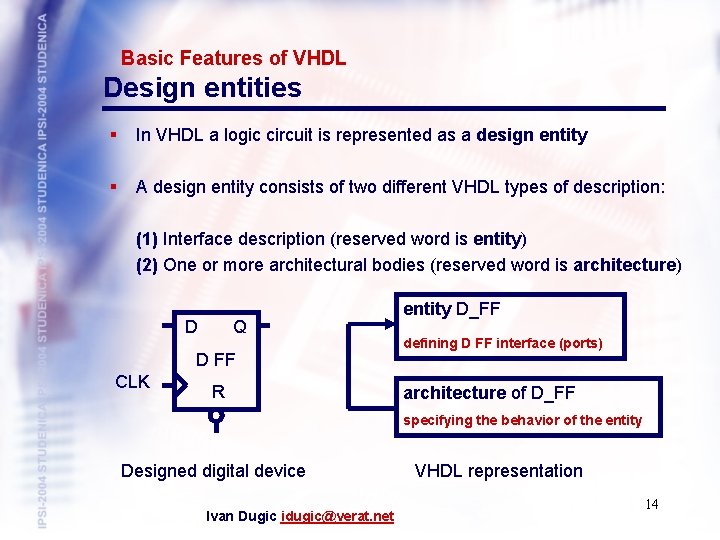

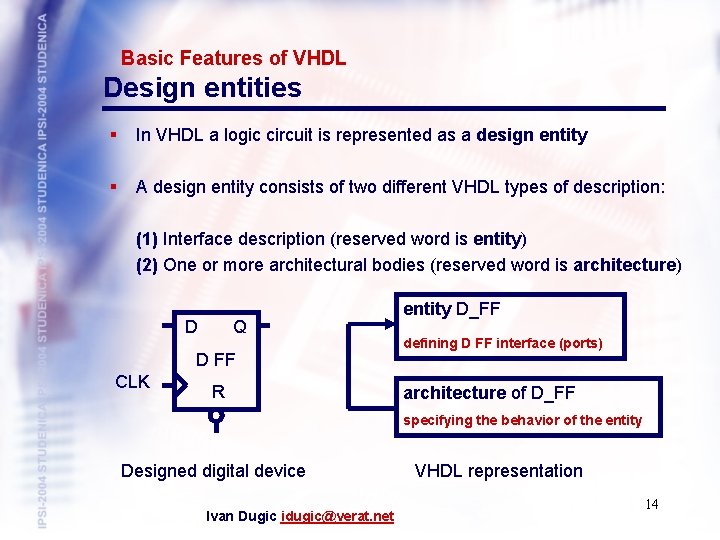

Basic Features of VHDL Design entities § In VHDL a logic circuit is represented as a design entity § A design entity consists of two different VHDL types of description: (1) Interface description (reserved word is entity) (2) One or more architectural bodies (reserved word is architecture) D Q D FF CLK R entity D_FF defining D FF interface (ports) architecture of D_FF specifying the behavior of the entity Designed digital device Ivan Dugic idugic@verat. net VHDL representation 14

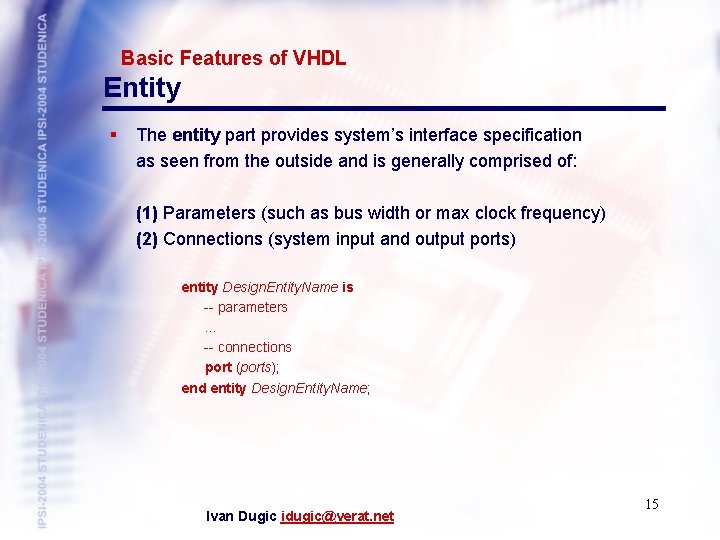

Basic Features of VHDL Entity § The entity part provides system’s interface specification as seen from the outside and is generally comprised of: (1) Parameters (such as bus width or max clock frequency) (2) Connections (system input and output ports) entity Design. Entity. Name is -- parameters … -- connections port (ports); end entity Design. Entity. Name; Ivan Dugic idugic@verat. net 15

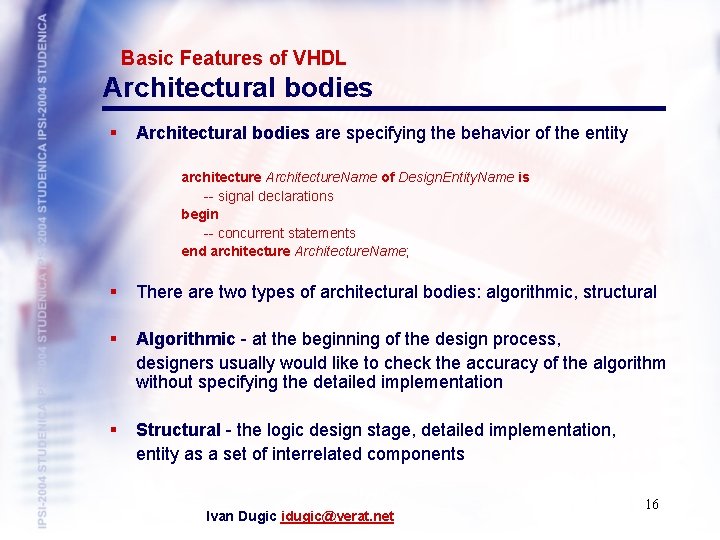

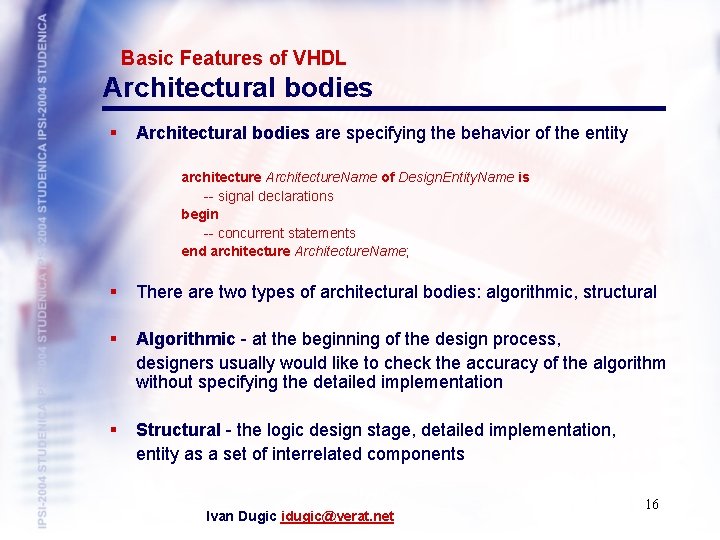

Basic Features of VHDL Architectural bodies § Architectural bodies are specifying the behavior of the entity architecture Architecture. Name of Design. Entity. Name is -- signal declarations begin -- concurrent statements end architecture Architecture. Name; § There are two types of architectural bodies: algorithmic, structural § Algorithmic - at the beginning of the design process, designers usually would like to check the accuracy of the algorithm without specifying the detailed implementation § Structural - the logic design stage, detailed implementation, entity as a set of interrelated components Ivan Dugic idugic@verat. net 16

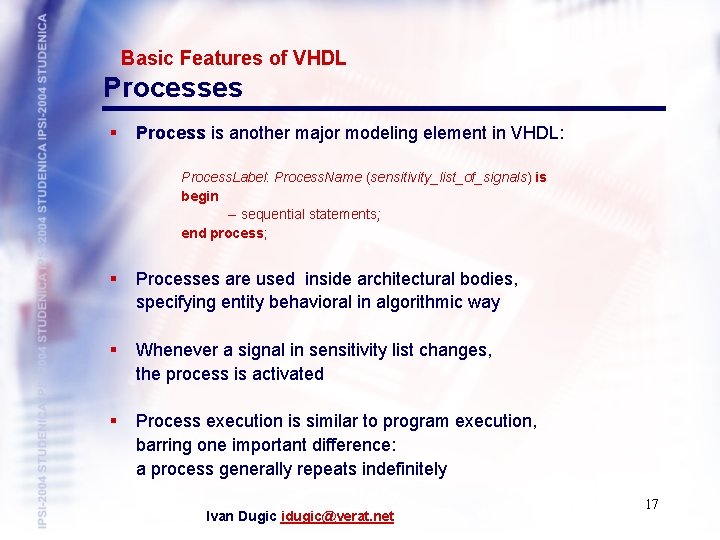

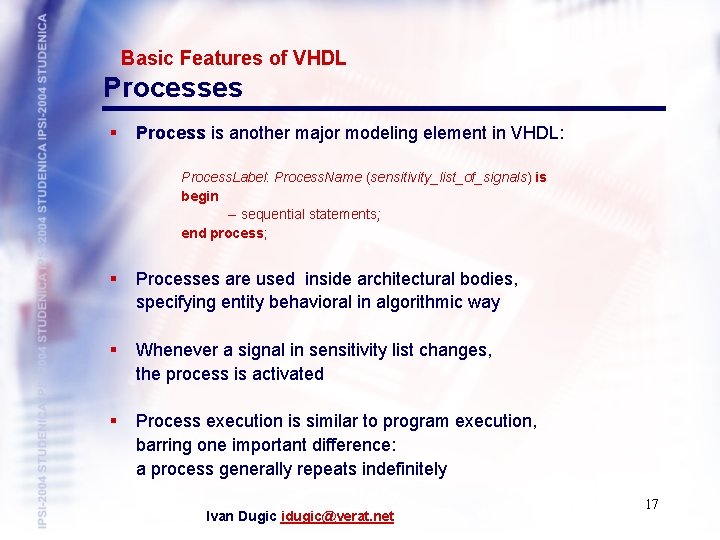

Basic Features of VHDL Processes § Process is another major modeling element in VHDL: Process. Label: Process. Name (sensitivity_list_of_signals) is begin -- sequential statements; end process; § Processes are used inside architectural bodies, specifying entity behavioral in algorithmic way § Whenever a signal in sensitivity list changes, the process is activated § Process execution is similar to program execution, barring one important difference: a process generally repeats indefinitely Ivan Dugic idugic@verat. net 17

Basic Features of VHDL Sequential and parallel processing § The statements within process are performed sequentially § The statements within architectural body are performed concurrent § Sequential and concurrent combination is called VHDL duality and it presents powerful mechanism for description of complex systems Ivan Dugic idugic@verat. net 18

Basic Features of VHDL Variables and signals § VHDL variable concept in many ways correspondents to a variable inherited from traditional sequential programming § Signals are the basic vehicle for information transmission in electronic systems § Signals model real devices’ wires and buses § Variable assignment is different from signal assignment § Main difference between variables and signals is that signal changes are visible only after process termination Ivan Dugic idugic@verat. net 19

Design Process Highlights Ivan Dugic idugic@verat. net 20

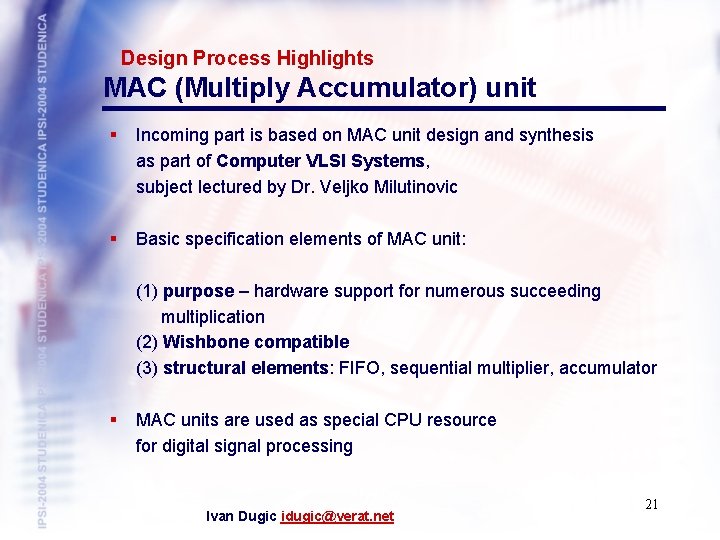

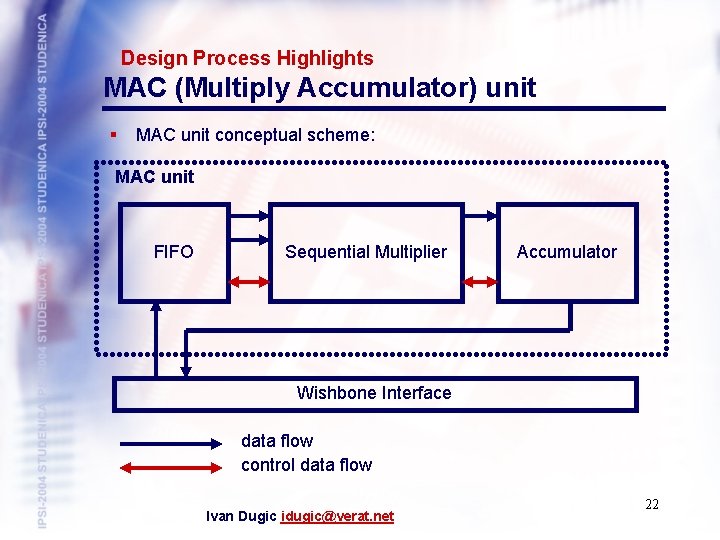

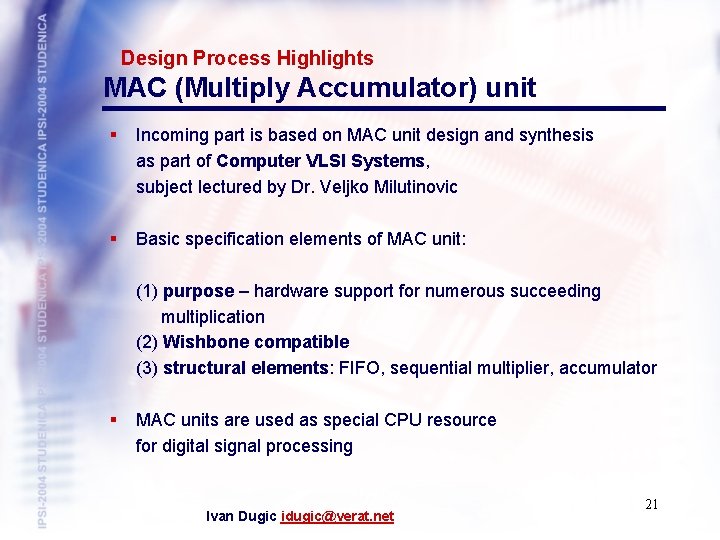

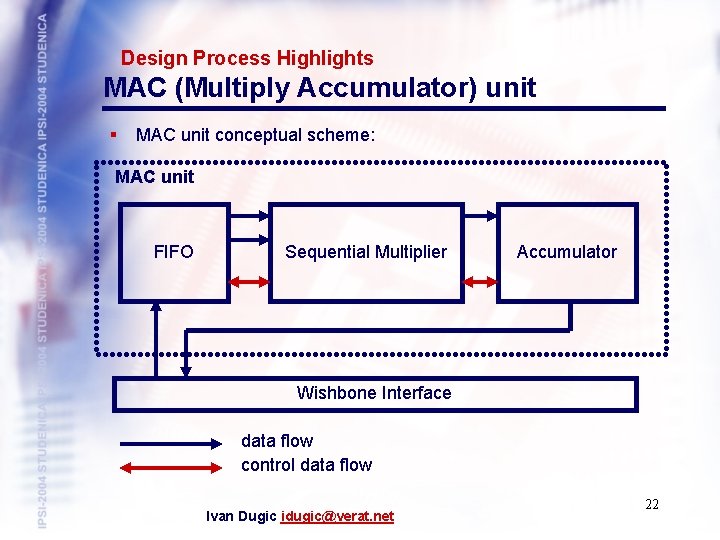

Design Process Highlights MAC (Multiply Accumulator) unit § Incoming part is based on MAC unit design and synthesis as part of Computer VLSI Systems, subject lectured by Dr. Veljko Milutinovic § Basic specification elements of MAC unit: (1) purpose – hardware support for numerous succeeding multiplication (2) Wishbone compatible (3) structural elements: FIFO, sequential multiplier, accumulator § MAC units are used as special CPU resource for digital signal processing Ivan Dugic idugic@verat. net 21

Design Process Highlights MAC (Multiply Accumulator) unit § MAC unit conceptual scheme: MAC unit FIFO Sequential Multiplier Accumulator Wishbone Interface data flow control data flow Ivan Dugic idugic@verat. net 22

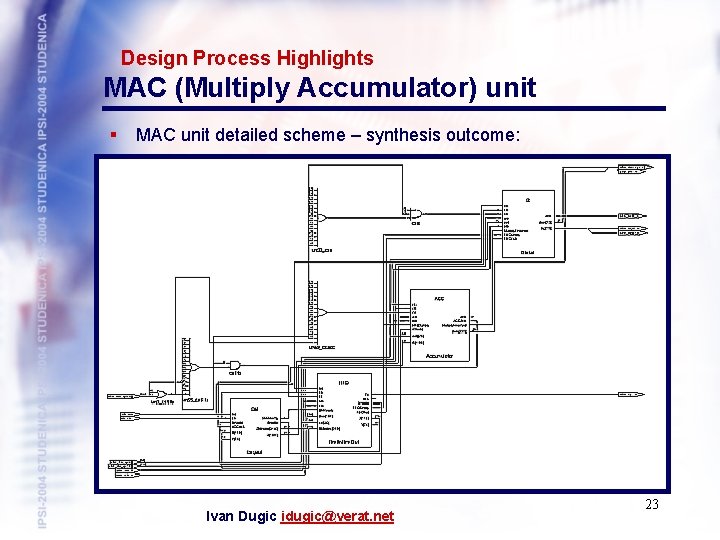

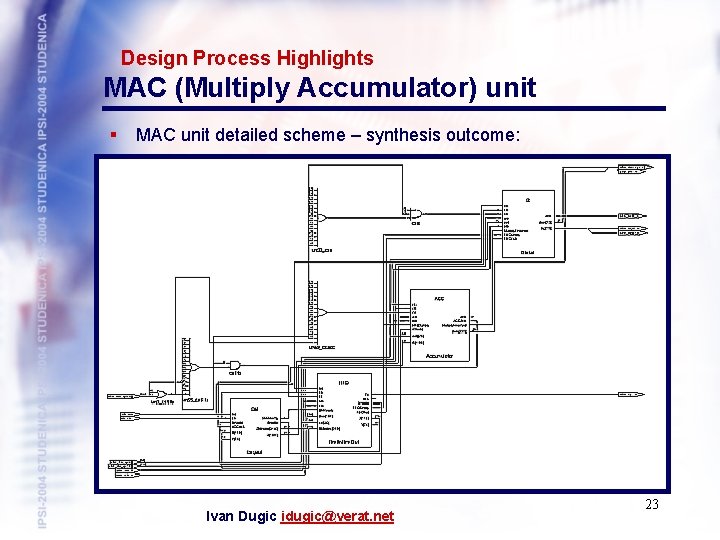

Design Process Highlights MAC (Multiply Accumulator) unit § MAC unit detailed scheme – synthesis outcome: Ivan Dugic idugic@verat. net 23

Design Process Highlights MAC: Lessons Learned § Testing is extremely important aspect of device design § In the component design process it is essential to test all structure components of top-level entity separately, and after that top-level entity itself § While projecting MAC unit so called Regression Testing is used § Regression Testing includes testing both structural and behavioral architecture of every entity simultaneously Ivan Dugic idugic@verat. net 24

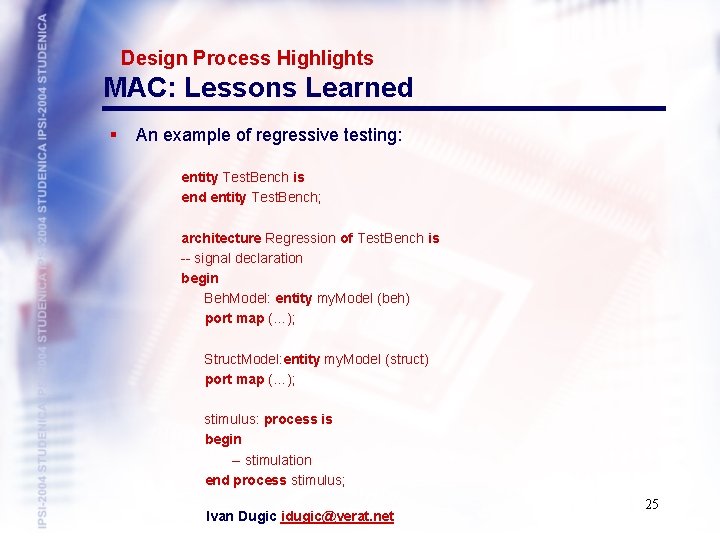

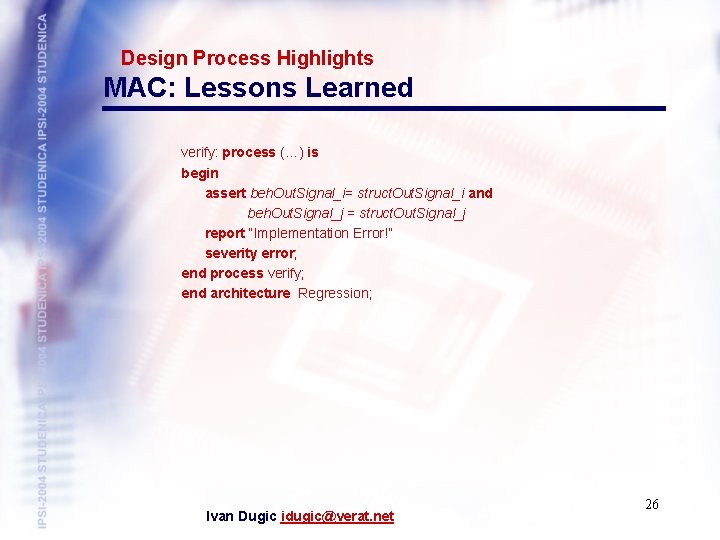

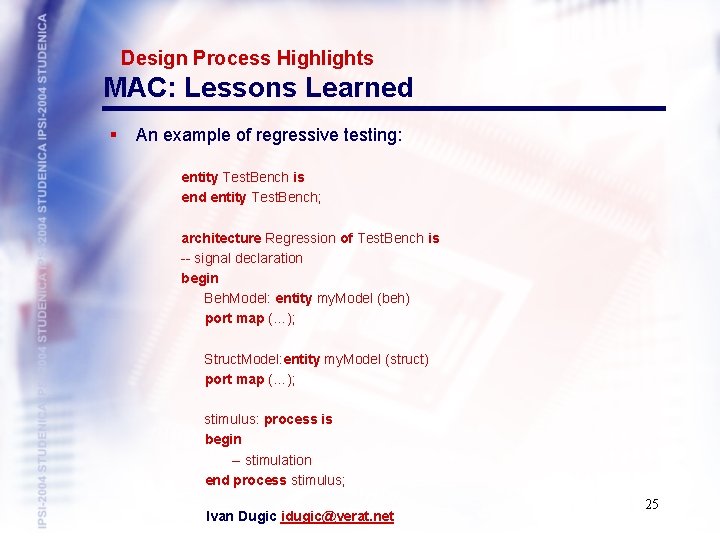

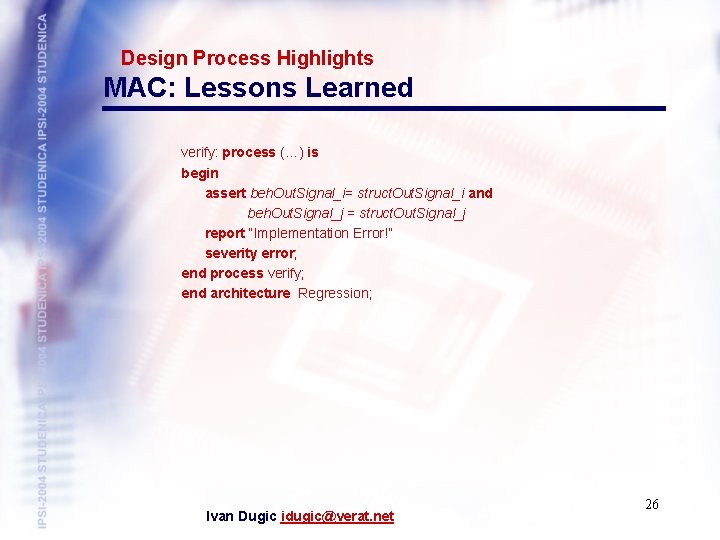

Design Process Highlights MAC: Lessons Learned § An example of regressive testing: entity Test. Bench is end entity Test. Bench; architecture Regression of Test. Bench is -- signal declaration begin Beh. Model: entity my. Model (beh) port map (…); Struct. Model: entity my. Model (struct) port map (…); stimulus: process is begin -- stimulation end process stimulus; Ivan Dugic idugic@verat. net 25

Design Process Highlights MAC: Lessons Learned verify: process (…) is begin assert beh. Out. Signal_i= struct. Out. Signal_i and beh. Out. Signal_j = struct. Out. Signal_j report “Implementation Error!” severity error; end process verify; end architecture Regression; Ivan Dugic idugic@verat. net 26

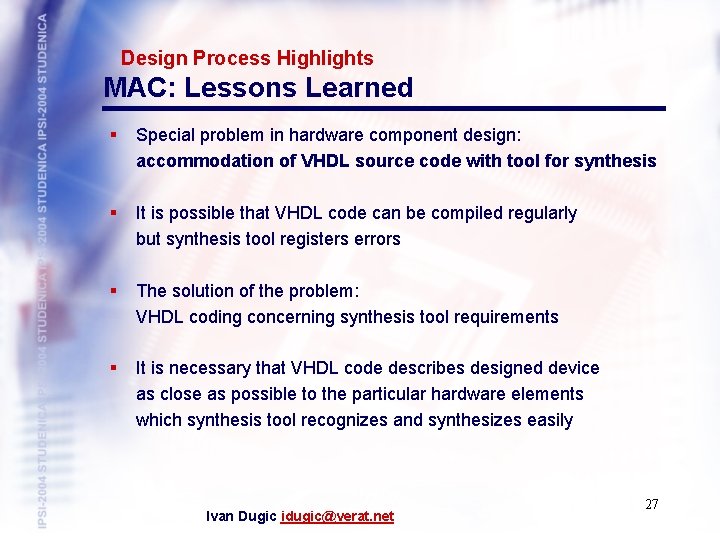

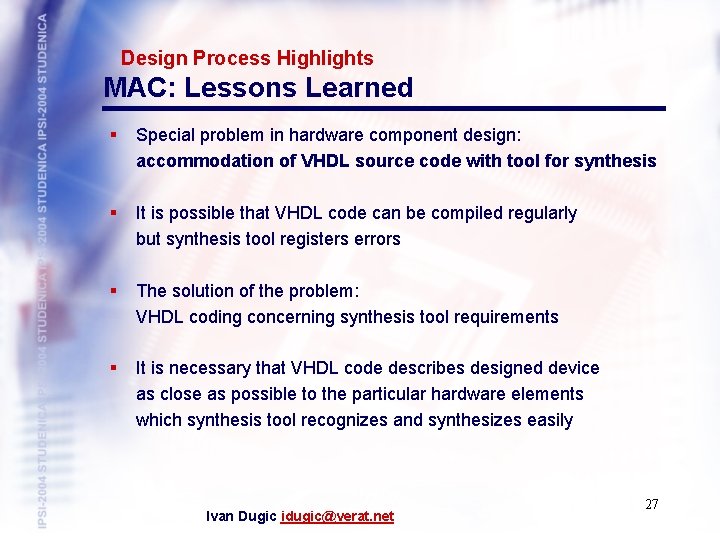

Design Process Highlights MAC: Lessons Learned § Special problem in hardware component design: accommodation of VHDL source code with tool for synthesis § It is possible that VHDL code can be compiled regularly but synthesis tool registers errors § The solution of the problem: VHDL coding concerning synthesis tool requirements § It is necessary that VHDL code describes designed device as close as possible to the particular hardware elements which synthesis tool recognizes and synthesizes easily Ivan Dugic idugic@verat. net 27

References § James R. Armstrong, F. Gail Gray, Structured Logic Design with VHDL § Peter J. Ashenden, The Designer’s Guide to VHDL § Milutinovic Veljko, Surviving the Design of a 200 MHz RISC Microprocessor: Lessons Learned Ivan Dugic idugic@verat. net 28

Authors § Ivan Dugic, idugic@verat. net § Dr. Veljko Milutinovic, vm@galeb. etf. bg. ac. yu Ivan Dugic idugic@verat. net 29