VHDL RECENT TRENDS UNIT V RTL REGISTER TRANSFER

- Slides: 55

VHDL & RECENT TRENDS UNIT V

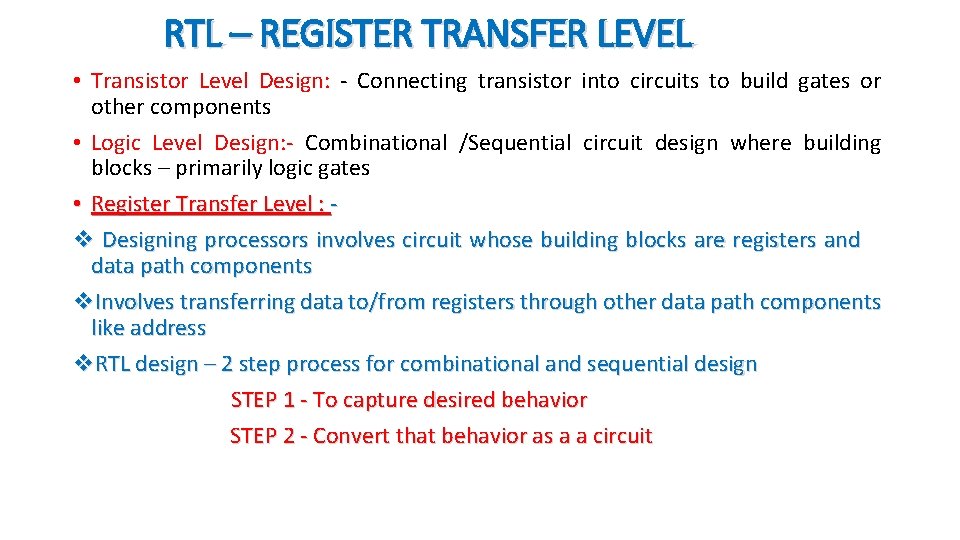

RTL – REGISTER TRANSFER LEVEL • Transistor Level Design: - Connecting transistor into circuits to build gates or other components • Logic Level Design: - Combinational /Sequential circuit design where building blocks – primarily logic gates • Register Transfer Level : v Designing processors involves circuit whose building blocks are registers and data path components v. Involves transferring data to/from registers through other data path components like address v. RTL design – 2 step process for combinational and sequential design STEP 1 - To capture desired behavior STEP 2 - Convert that behavior as a a circuit

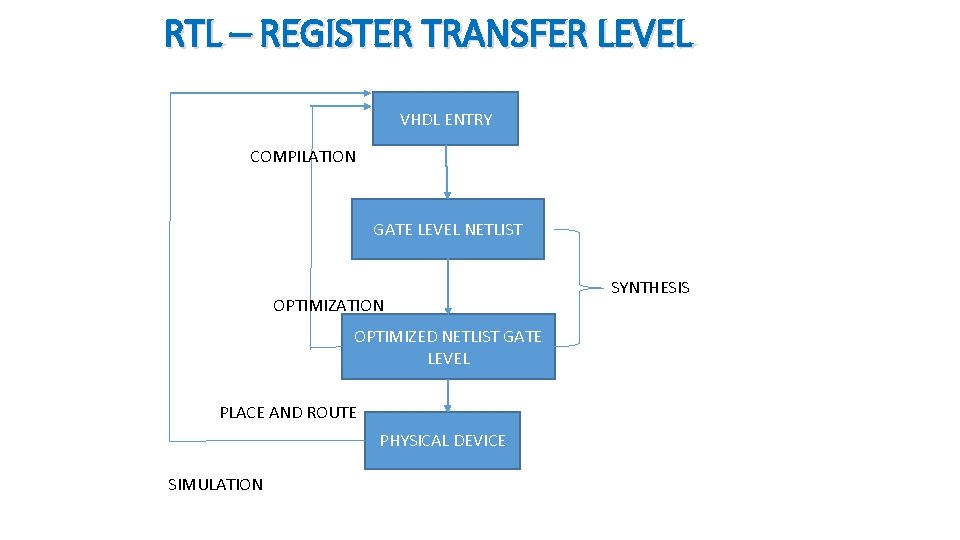

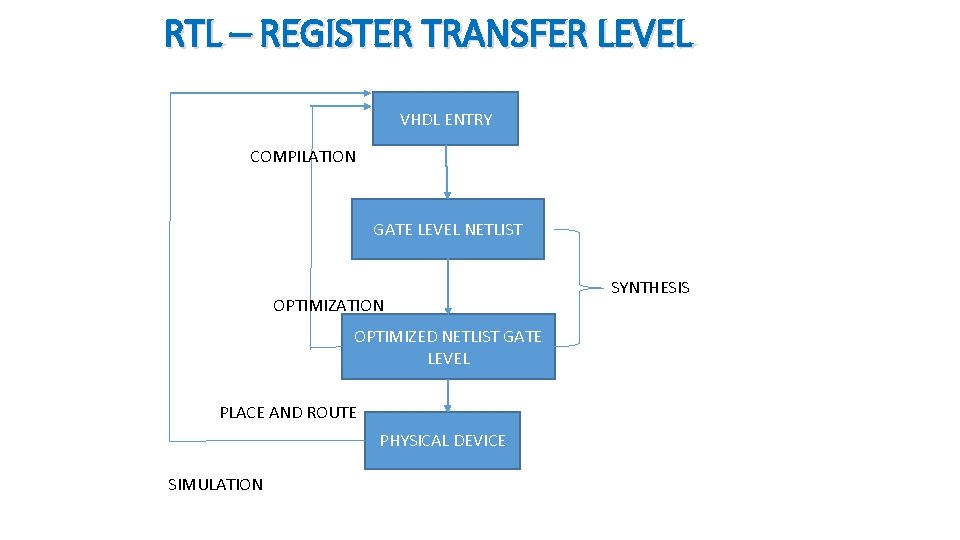

RTL – REGISTER TRANSFER LEVEL Design Procedure: • VHDL Entry – Writing code. It is saved in file name. vhd. The same name is given to entity • Compilation process – High level HDL to netlist at the gate level • Optimization – Optimized netlist • Simulation • Place and Route software generate physical layout for FPGA chip

RTL – REGISTER TRANSFER LEVEL VHDL ENTRY COMPILATION GATE LEVEL NETLIST OPTIMIZATION OPTIMIZED NETLIST GATE LEVEL PLACE AND ROUTE PHYSICAL DEVICE SIMULATION SYNTHESIS

TEST BENCHES • A test bench is a stimulus that tests the functionality of the design • It is a test program written in HDL • For digital system design , design is first described in HDL –verified by simulation – then using a test bench written in HDL, it is tested and its response observed

VHDL/VHSIC HDL • Very high speed integrated circuits hardware description language • Language describing hardware as Schematic describes hardware • Same VHDL code being used for documentation, verification and synthesis of large digital designs • Three different approaches for VHDL : 1. Data flow 2. Structural 3. Behavioral Methods/Models

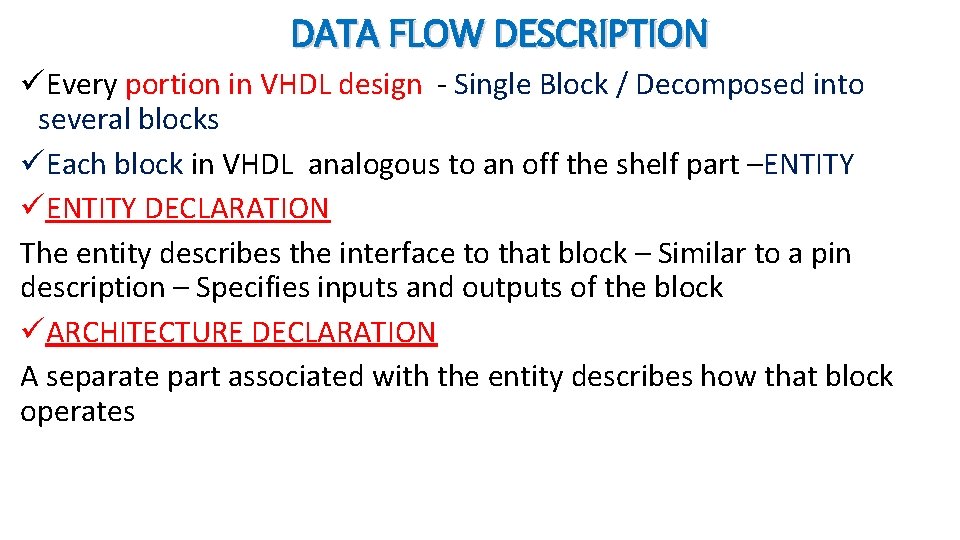

DATA FLOW DESCRIPTION üEvery portion in VHDL design - Single Block / Decomposed into several blocks üEach block in VHDL analogous to an off the shelf part –ENTITY üENTITY DECLARATION The entity describes the interface to that block – Similar to a pin description – Specifies inputs and outputs of the block üARCHITECTURE DECLARATION A separate part associated with the entity describes how that block operates

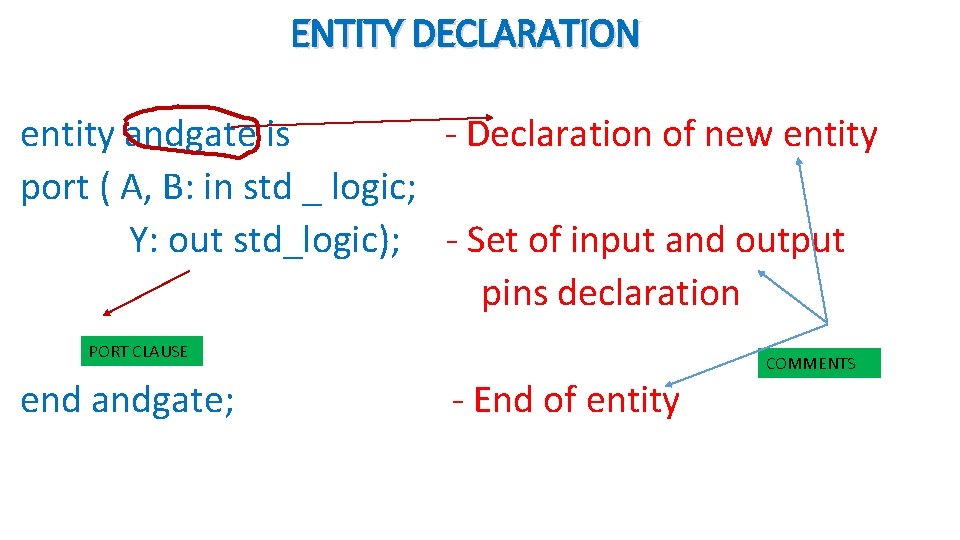

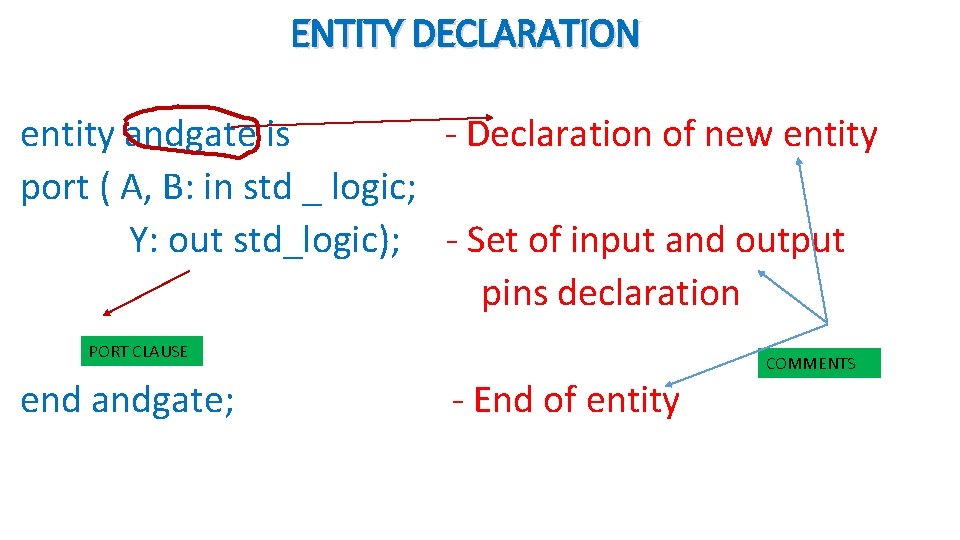

ENTITY DECLARATION entity andgate is - Declaration of new entity port ( A, B: in std _ logic; Y: out std_logic); - Set of input and output pins declaration PORT CLAUSE end andgate; - End of entity COMMENTS

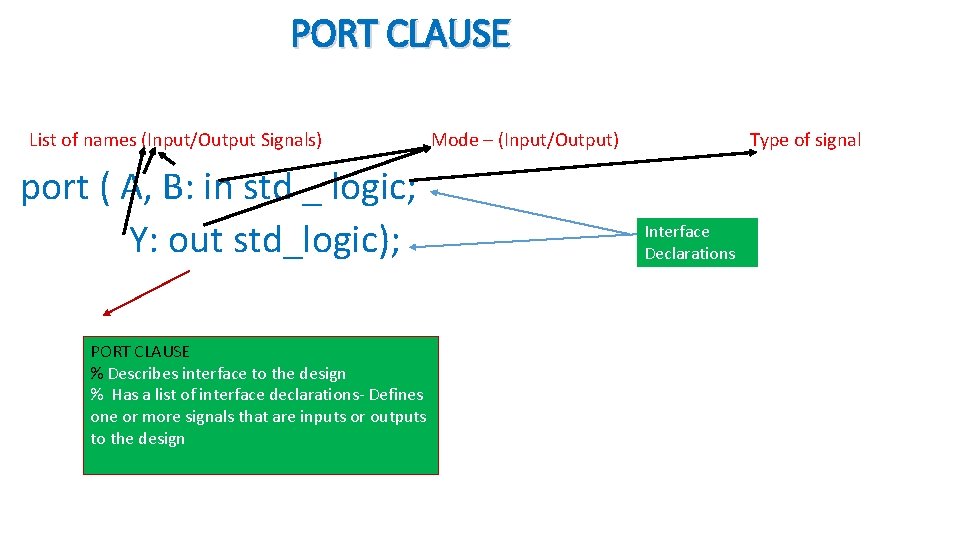

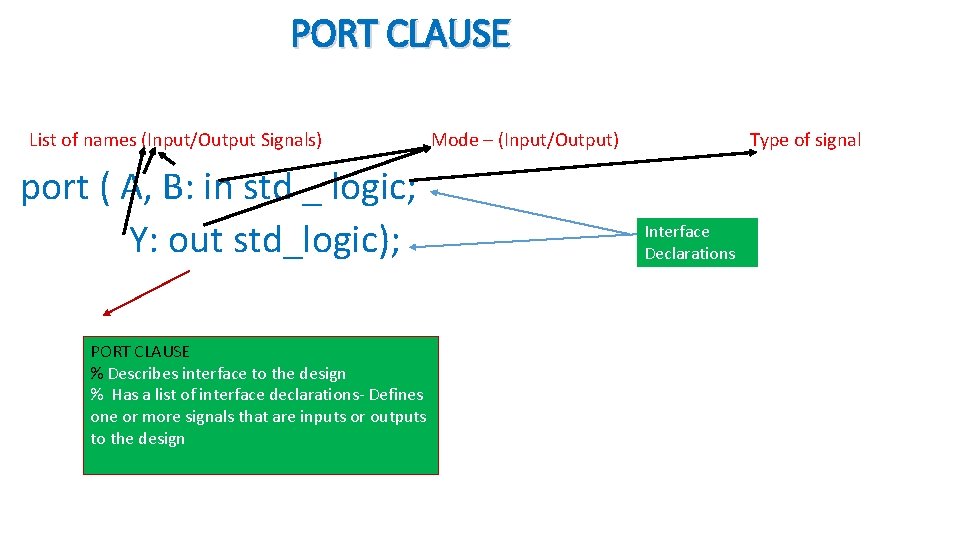

PORT CLAUSE List of names (Input/Output Signals) port ( A, B: in std _ logic; Y: out std_logic); PORT CLAUSE % Describes interface to the design % Has a list of interface declarations- Defines one or more signals that are inputs or outputs to the design Mode – (Input/Output) Type of signal Interface Declarations

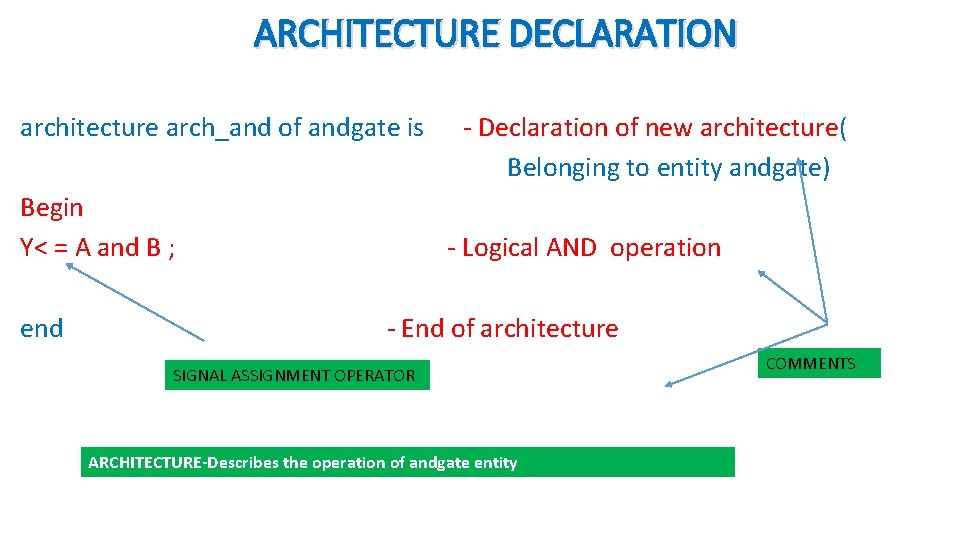

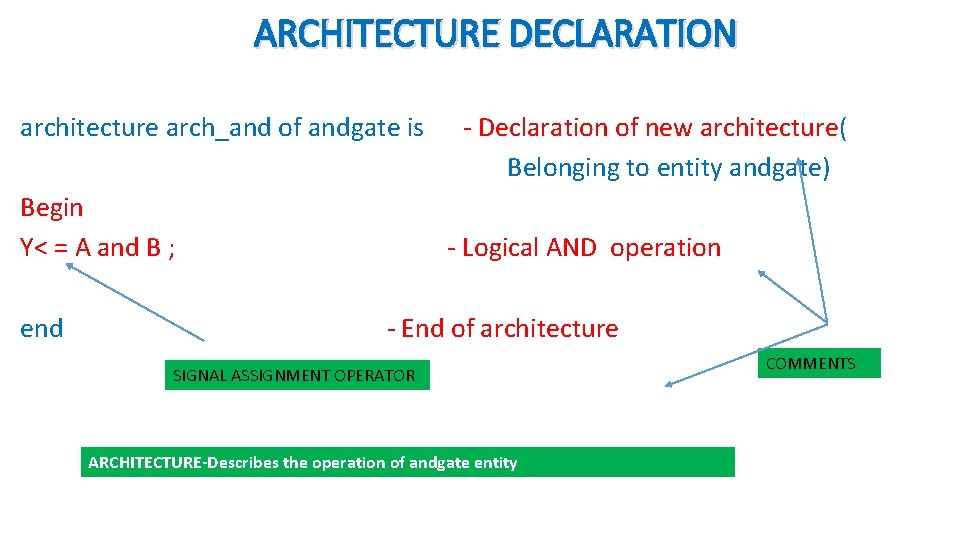

ARCHITECTURE DECLARATION architecture arch_and of andgate is Begin Y< = A and B ; end - Declaration of new architecture( Belonging to entity andgate) - Logical AND operation - End of architecture SIGNAL ASSIGNMENT OPERATOR ARCHITECTURE-Describes the operation of andgate entity COMMENTS

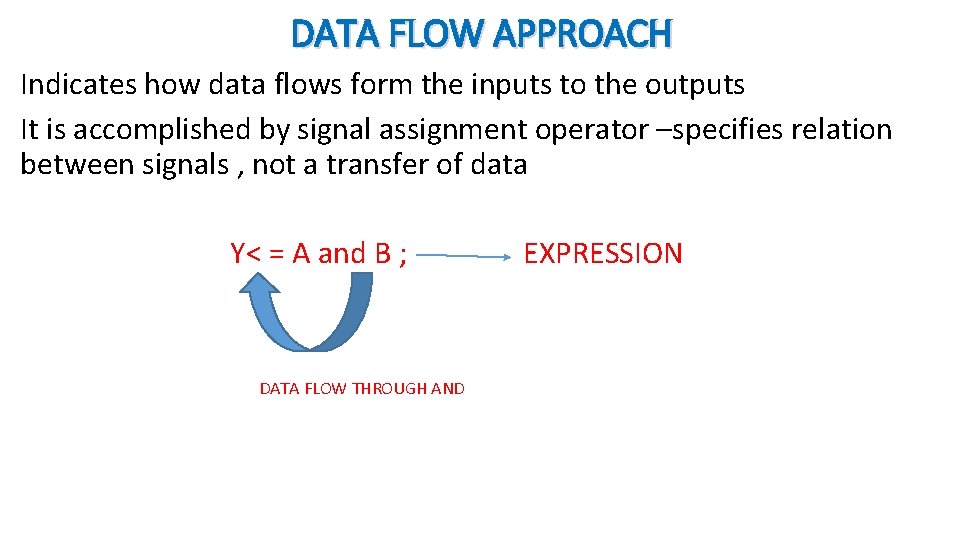

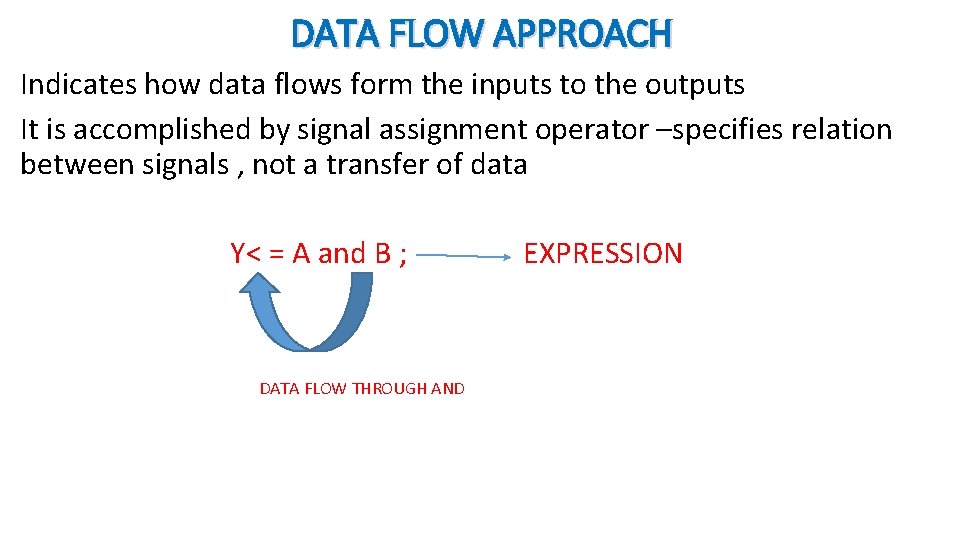

DATA FLOW APPROACH Indicates how data flows form the inputs to the outputs It is accomplished by signal assignment operator –specifies relation between signals , not a transfer of data Y< = A and B ; DATA FLOW THROUGH AND EXPRESSION

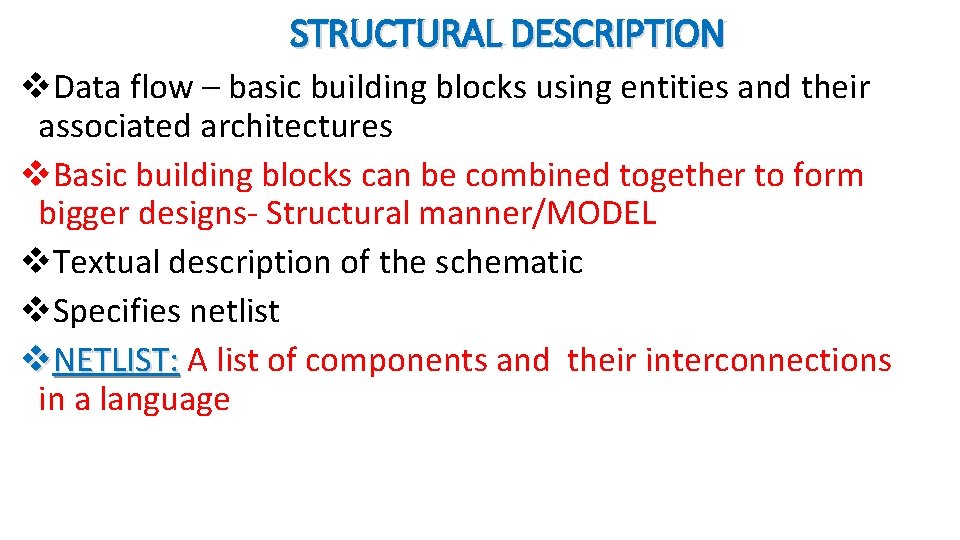

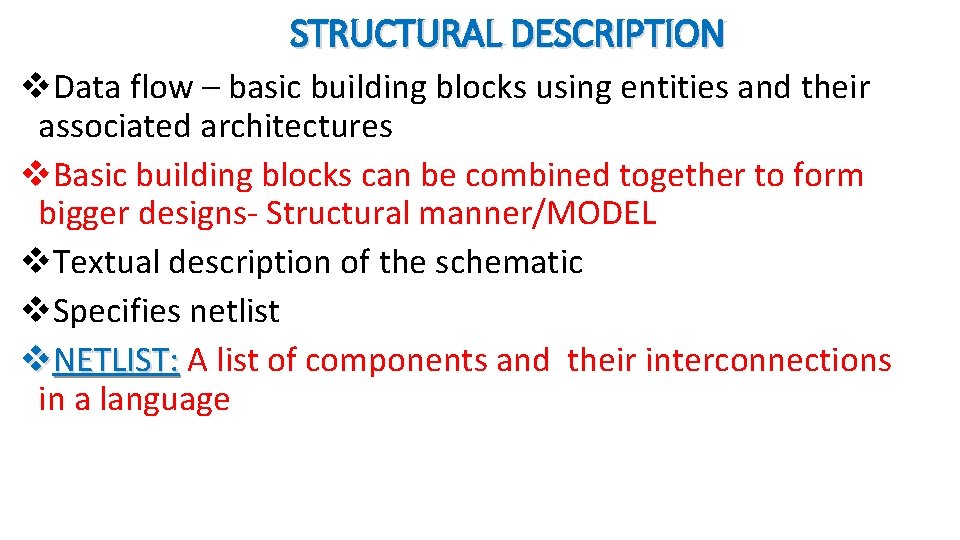

STRUCTURAL DESCRIPTION v. Data flow – basic building blocks using entities and their associated architectures v. Basic building blocks can be combined together to form bigger designs- Structural manner/MODEL v. Textual description of the schematic v. Specifies netlist v. NETLIST: A list of components and their interconnections in a language

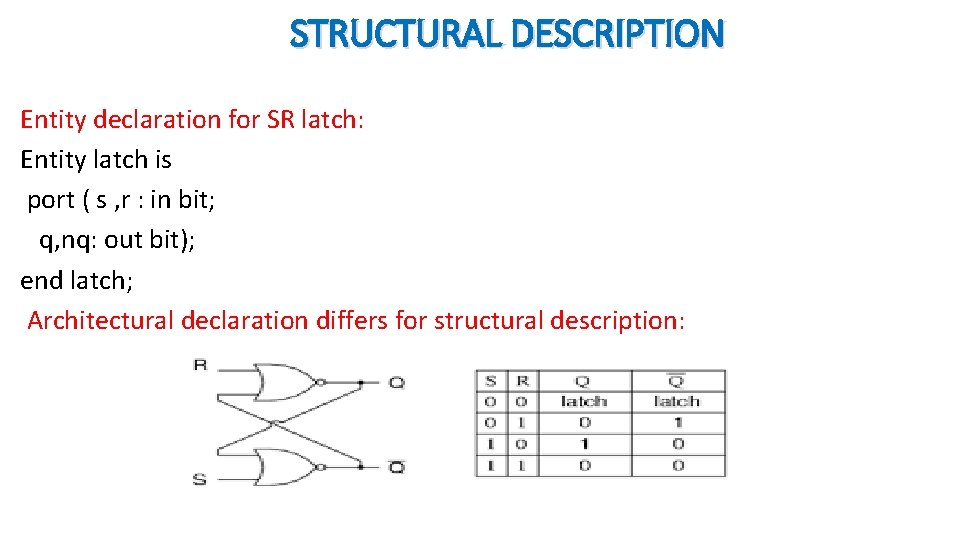

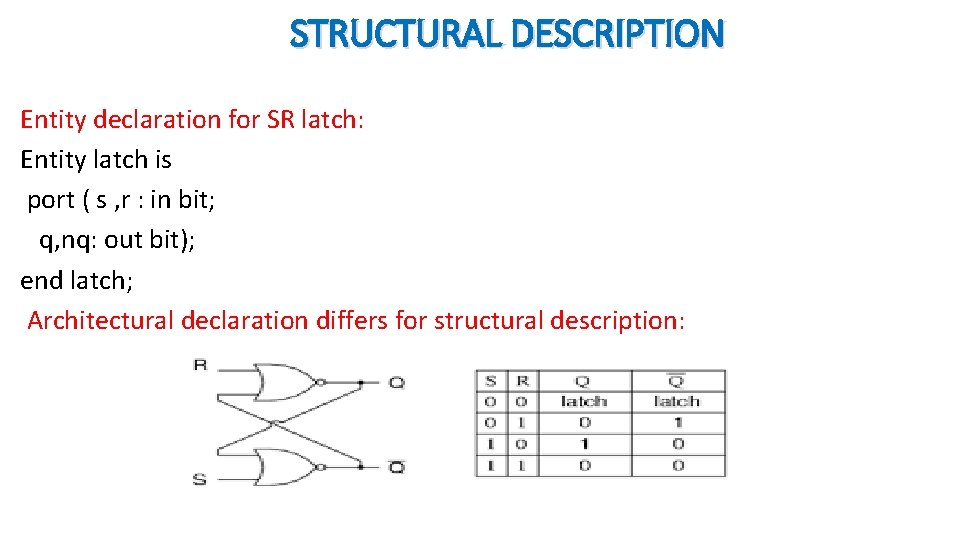

STRUCTURAL DESCRIPTION Entity declaration for SR latch: Entity latch is port ( s , r : in bit; q, nq: out bit); end latch; Architectural declaration differs for structural description:

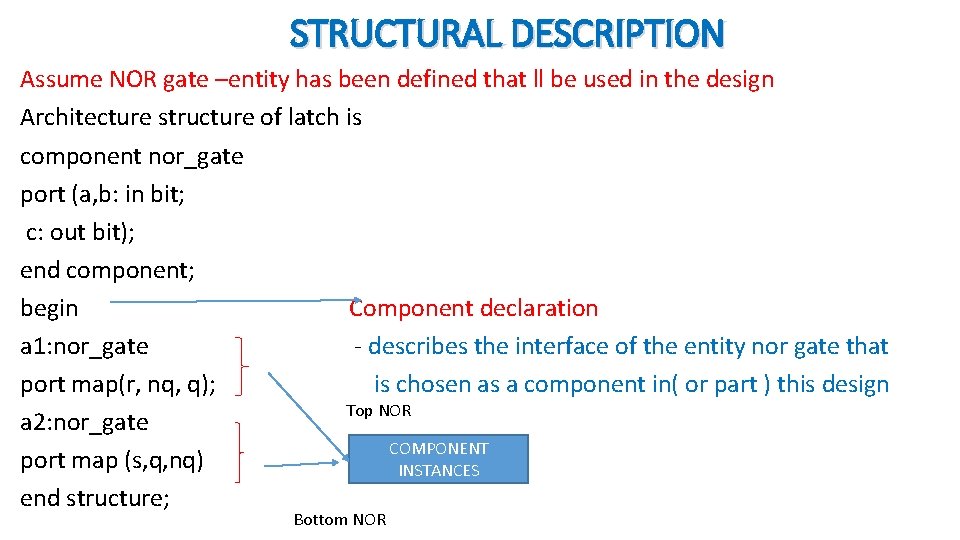

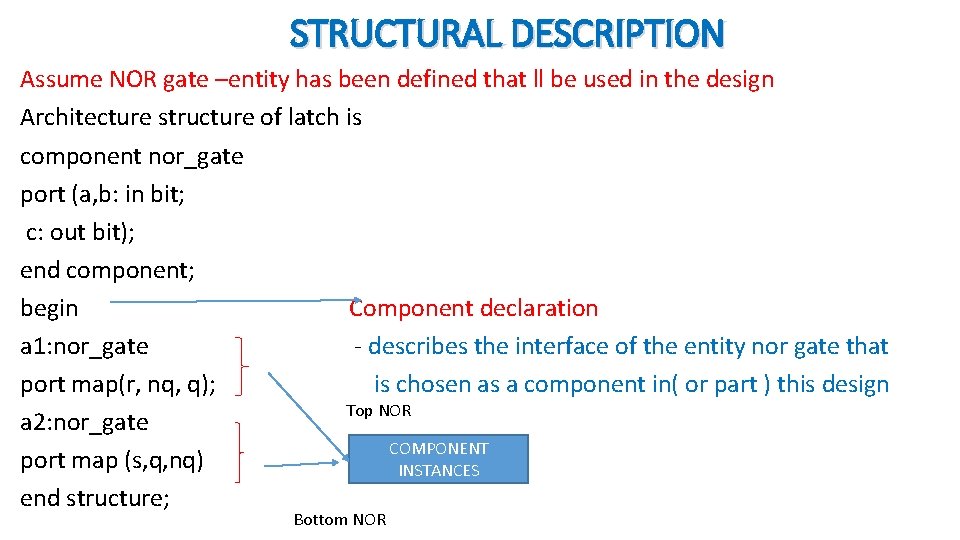

STRUCTURAL DESCRIPTION Assume NOR gate –entity has been defined that ll be used in the design Architecture structure of latch is component nor_gate port (a, b: in bit; c: out bit); end component; begin Component declaration a 1: nor_gate - describes the interface of the entity nor gate that port map(r, nq, q); is chosen as a component in( or part ) this design Top NOR a 2: nor_gate COMPONENT port map (s, q, nq) INSTANCES end structure; Bottom NOR

STRUCTURAL DESCRIPTION Entity – design interface Component – Interface of an entity that ll be used as an entity(sub block) Component instance – Distinct copy of the component connected to other parts and signals

BEHAVIORAL DESCRIPTION üBLACK BOX APPROACH: Does not reflect how the design is implemented üIt accurately models what happens on the inputs and the way it is guided towards outputs of the black box üIt does not deal with what is inside or how it works üUsed in two ways in VHDL üIt can be used to model complex components that would be tedious üEx- If it is required to simulate the operation of the custom design connected to a commercial part like microprocessor – complex- internal operation irrelevant – external behavior important – modeled using behavioral üMore powerful and convenient for designs- behavioral description imply some structure of the implementation

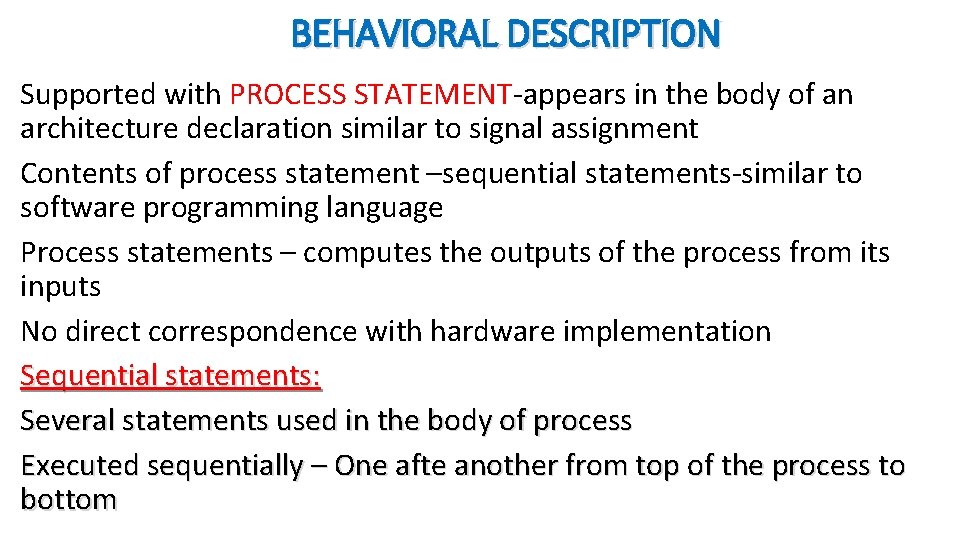

BEHAVIORAL DESCRIPTION Supported with PROCESS STATEMENT-appears in the body of an architecture declaration similar to signal assignment Contents of process statement –sequential statements-similar to software programming language Process statements – computes the outputs of the process from its inputs No direct correspondence with hardware implementation Sequential statements: Several statements used in the body of process Executed sequentially – One afte another from top of the process to bottom

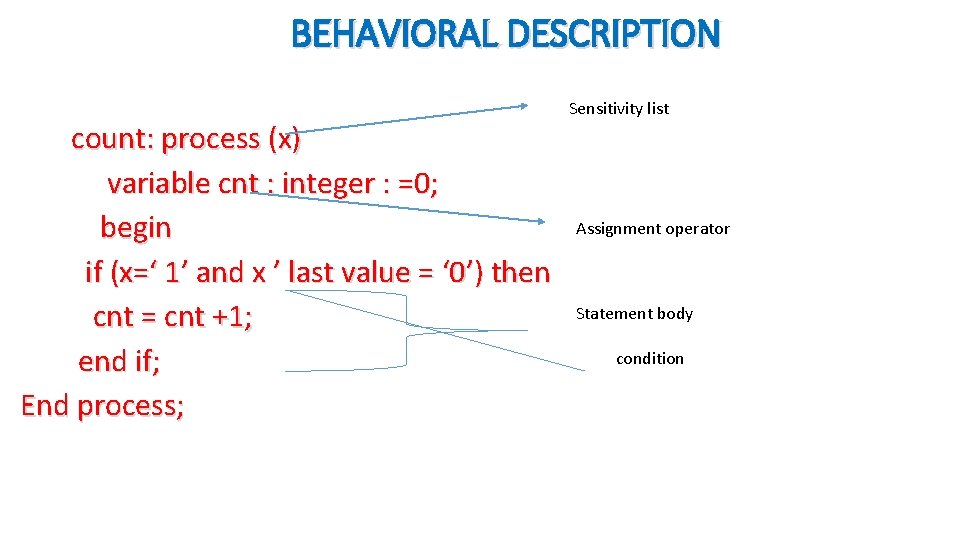

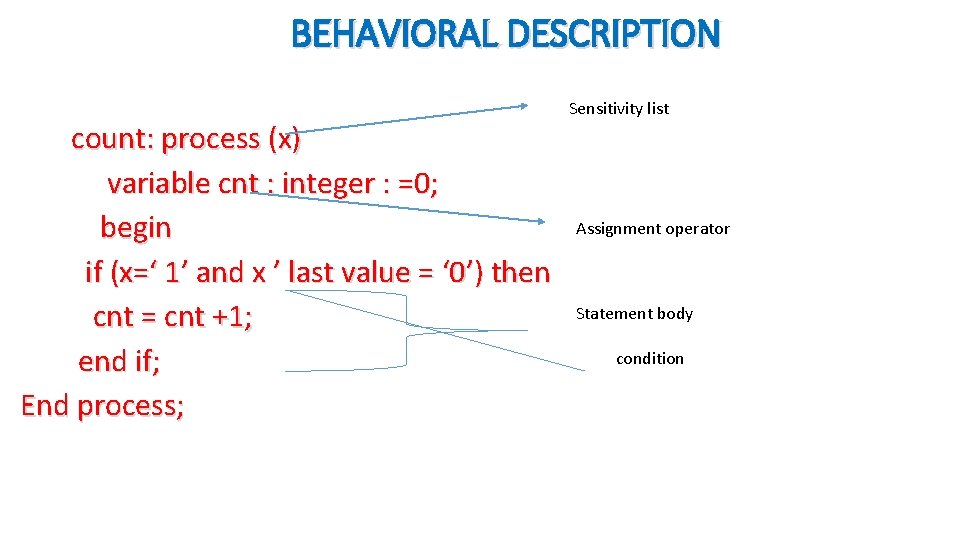

BEHAVIORAL DESCRIPTION count: process (x) variable cnt : integer : =0; begin if (x=‘ 1’ and x ’ last value = ‘ 0’) then cnt = cnt +1; end if; End process; Sensitivity list Assignment operator Statement body condition

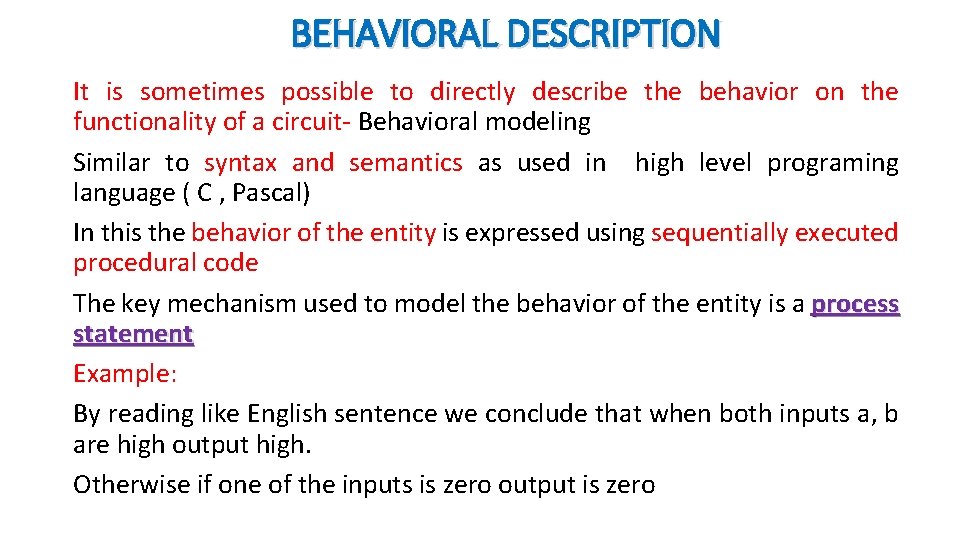

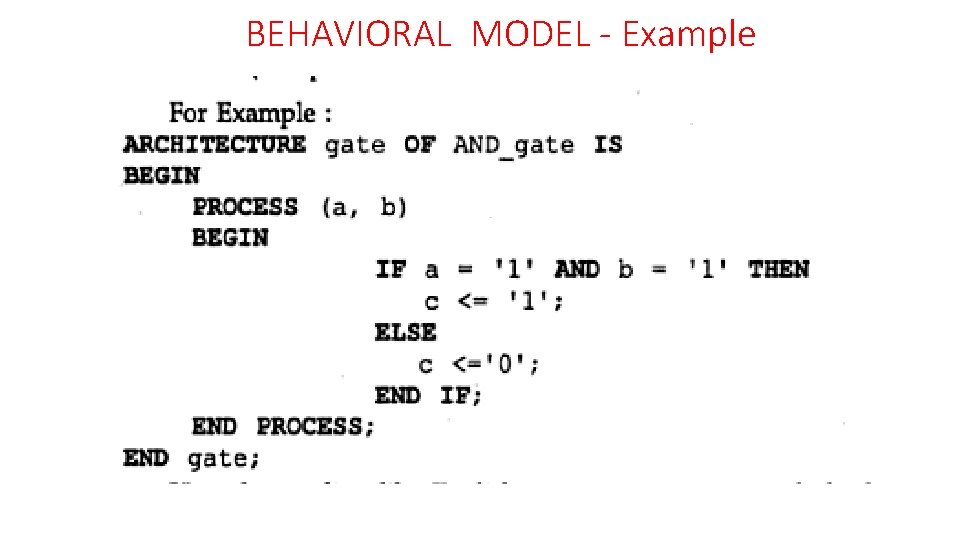

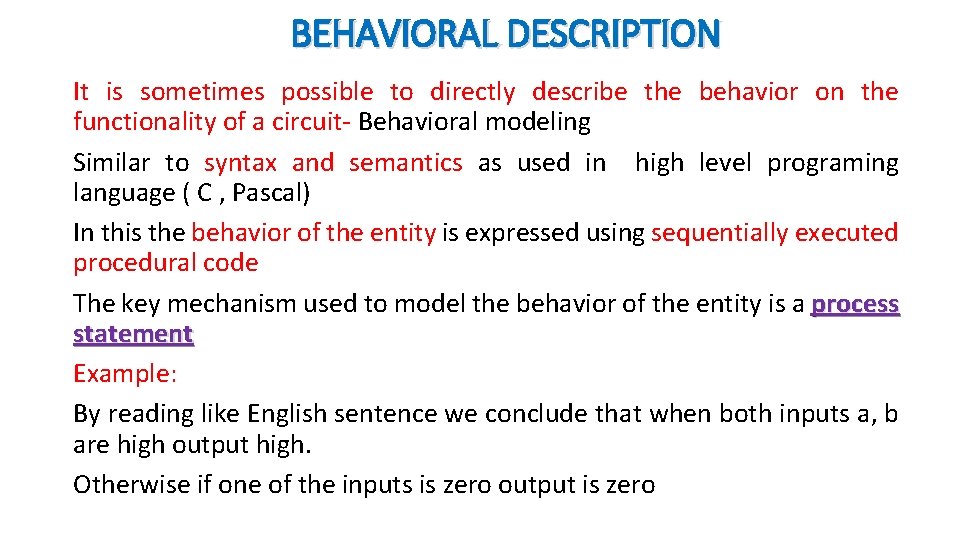

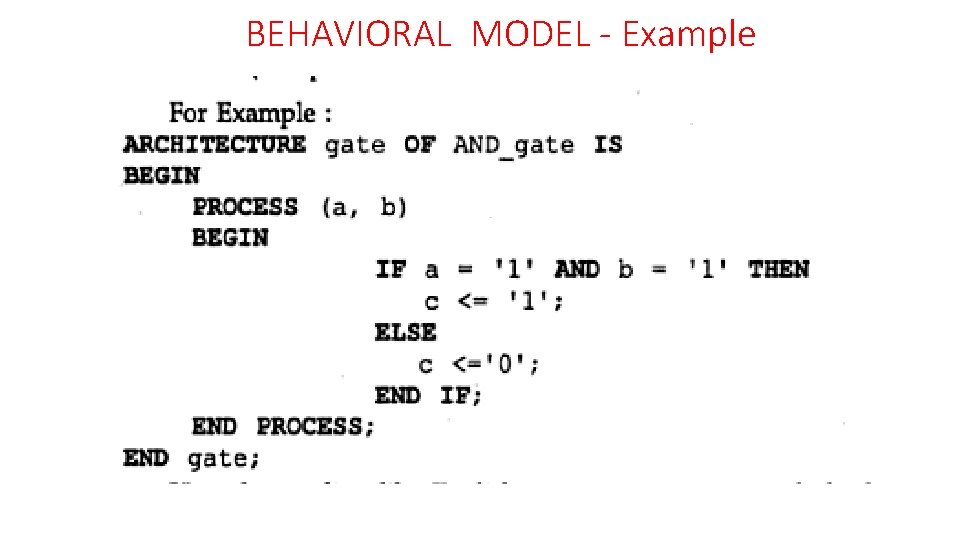

BEHAVIORAL DESCRIPTION It is sometimes possible to directly describe the behavior on the functionality of a circuit- Behavioral modeling Similar to syntax and semantics as used in high level programing language ( C , Pascal) In this the behavior of the entity is expressed using sequentially executed procedural code The key mechanism used to model the behavior of the entity is a process statement Example: By reading like English sentence we conclude that when both inputs a, b are high output high. Otherwise if one of the inputs is zero output is zero

BEHAVIORAL MODEL - Example

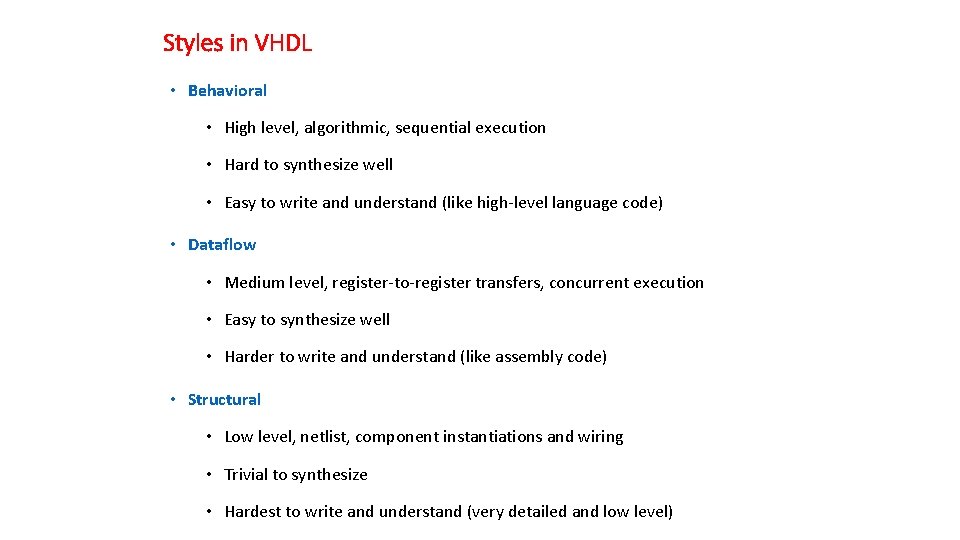

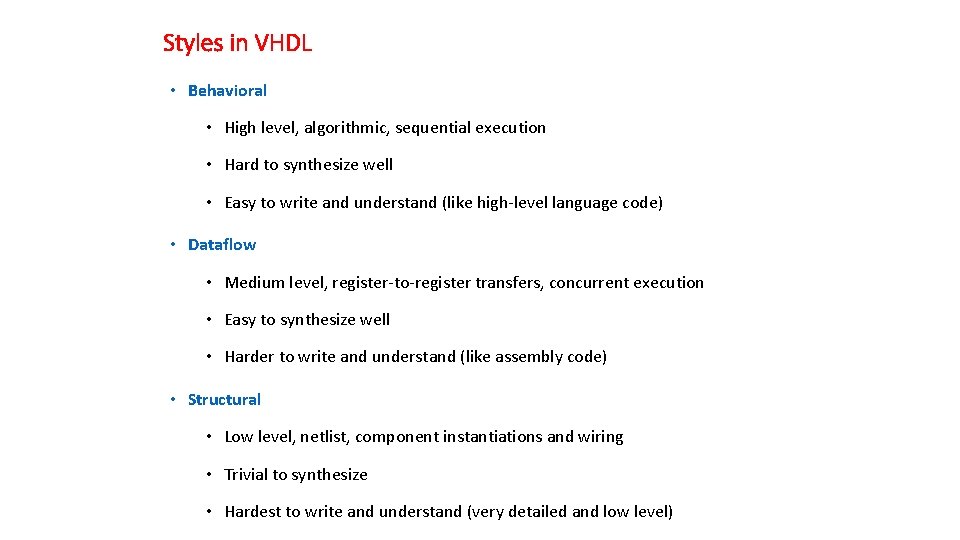

Styles in VHDL • Behavioral • High level, algorithmic, sequential execution • Hard to synthesize well • Easy to write and understand (like high-level language code) • Dataflow • Medium level, register-to-register transfers, concurrent execution • Easy to synthesize well • Harder to write and understand (like assembly code) • Structural • Low level, netlist, component instantiations and wiring • Trivial to synthesize • Hardest to write and understand (very detailed and low level)

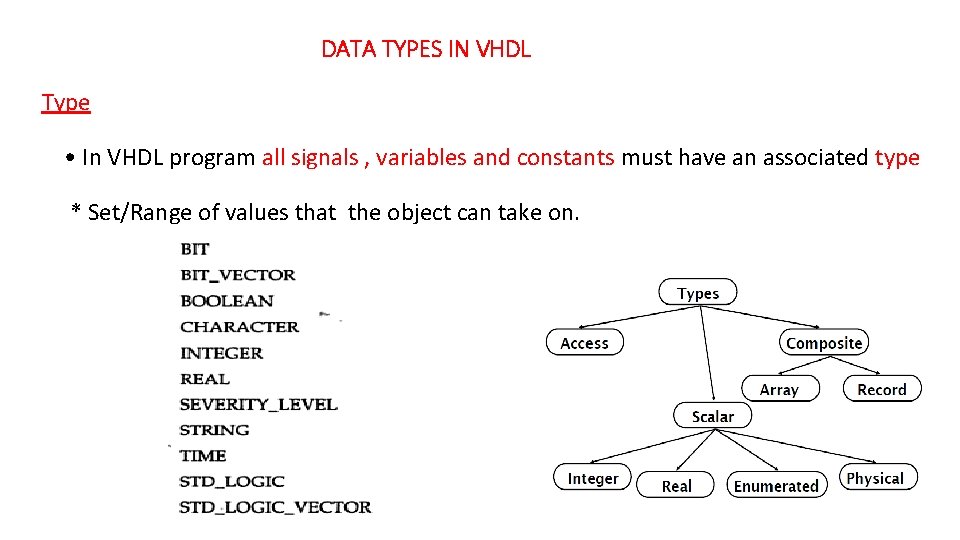

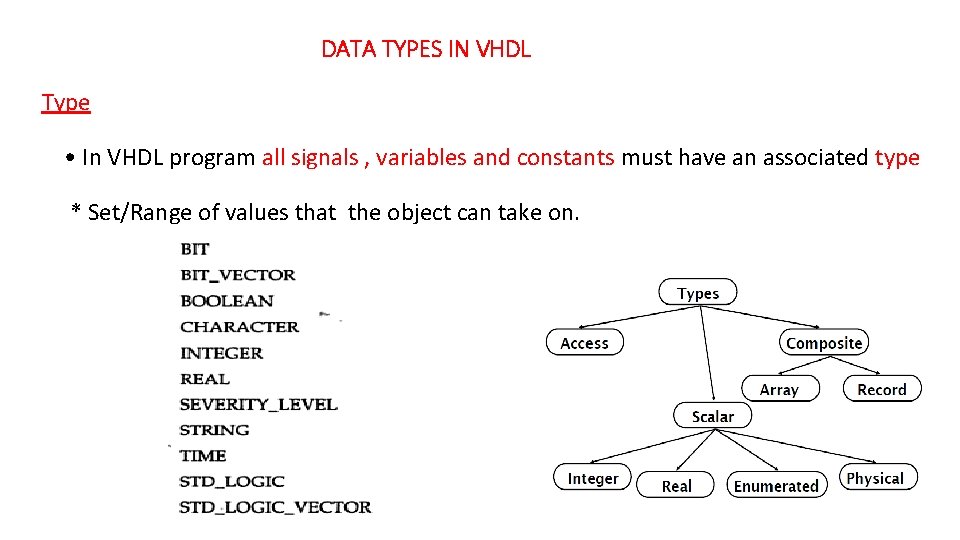

DATA TYPES IN VHDL Type • In VHDL program all signals , variables and constants must have an associated type * Set/Range of values that the object can take on.

TYPES • Most of the signals – BIT • Collection of several data items of the same type –Array • Bit Vector- Predefined array type – Several bit signals together to represent a binary number – Collection of bits • Time –Represents values of time • Integers • Real Numbers • Mostly used – Boolean (True /False), Character, Integer • STD_LOGIC – Standard user defined logic type – 7 other values in addition to 0 and 1 for simulating a logic signal (bit) in a real logic circuit

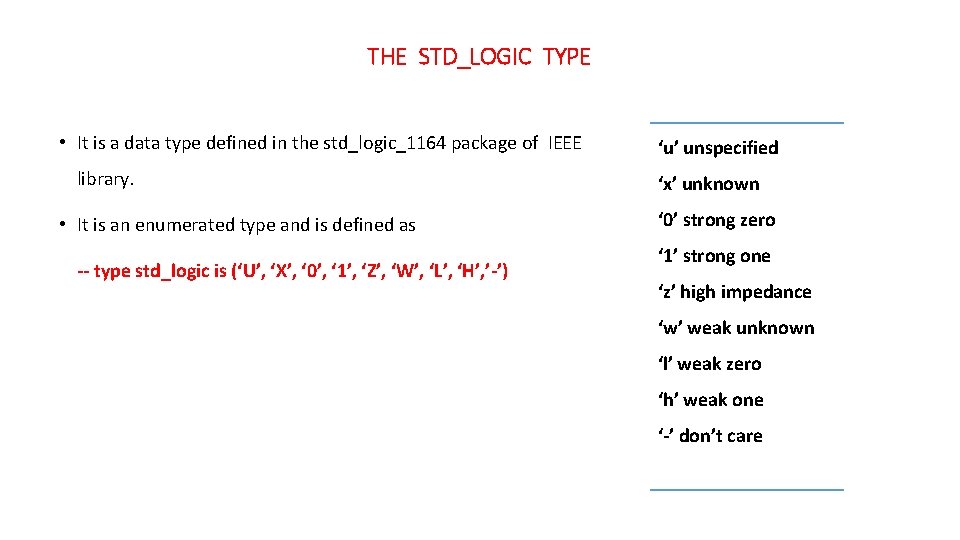

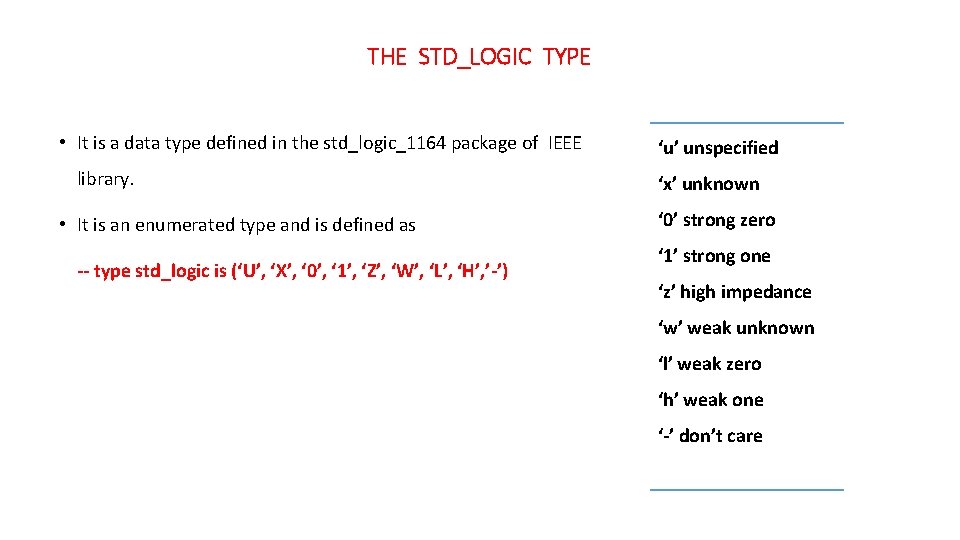

THE STD_LOGIC TYPE • It is a data type defined in the std_logic_1164 package of IEEE library. • It is an enumerated type and is defined as -- type std_logic is (‘U’, ‘X’, ‘ 0’, ‘ 1’, ‘Z’, ‘W’, ‘L’, ‘H’, ’-’) ‘u’ unspecified ‘x’ unknown ‘ 0’ strong zero ‘ 1’ strong one ‘z’ high impedance ‘w’ weak unknown ‘l’ weak zero ‘h’ weak one ‘-’ don’t care

SCALAR TYPES • Integer • Floating point Can be either positive or negative. - • exponents have to be integer. -type real is range implementation defined • Physical Predefined type “Time” used to specify delays. Example : --type TIME is range -2147483647 to 2147483647 • Enumeration Values are defined in ascending order. -

COMPOSITE TYPES There are two composite types ARRAY: • Contain many elements of the same type. • Array can be either single or multidimensional. • Single dimensional array are synthesizable. • The synthesis of multidimensional array depends upon the synthesizer being used. RECORD: Contain elements of different types.

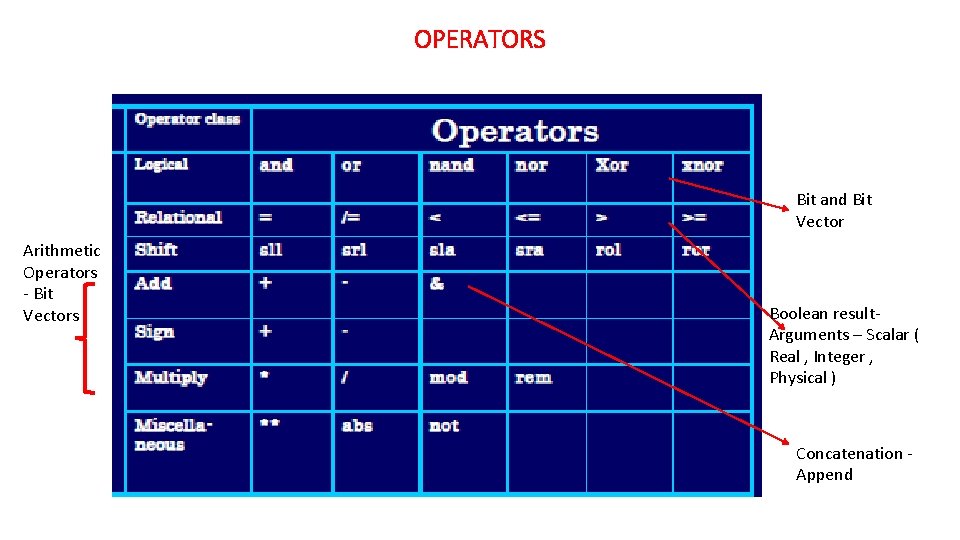

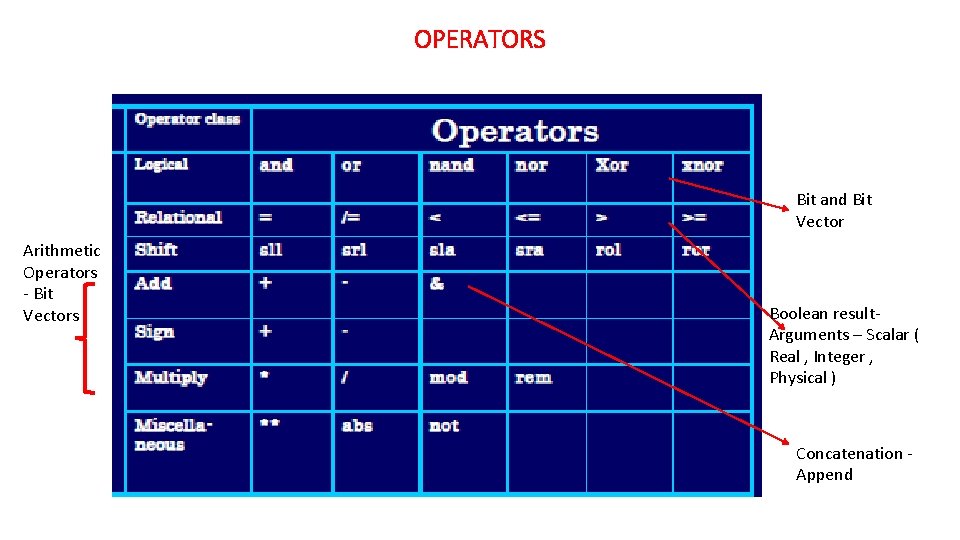

OPERATORS Bit and Bit Vector Arithmetic Operators - Bit Vectors Boolean result. Arguments – Scalar ( Real , Integer , Physical ) Concatenation Append

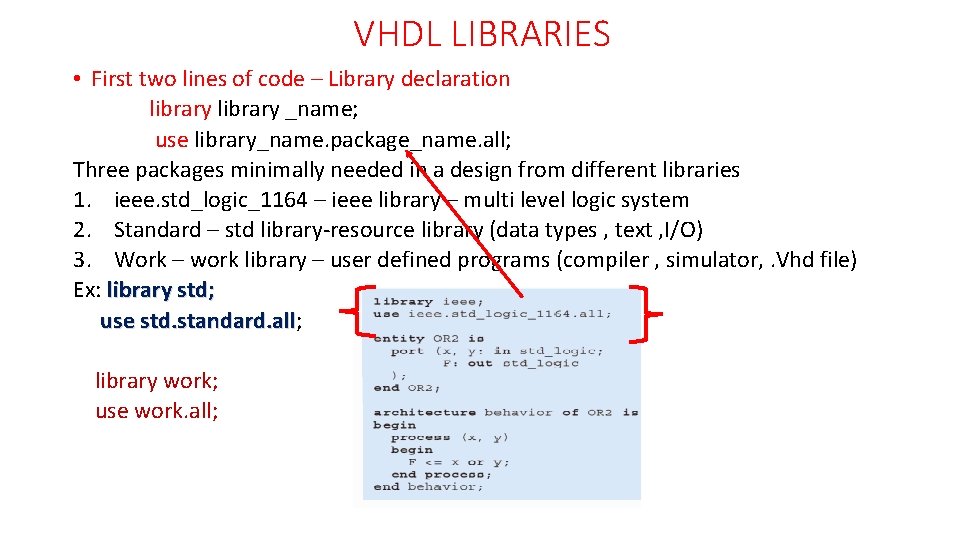

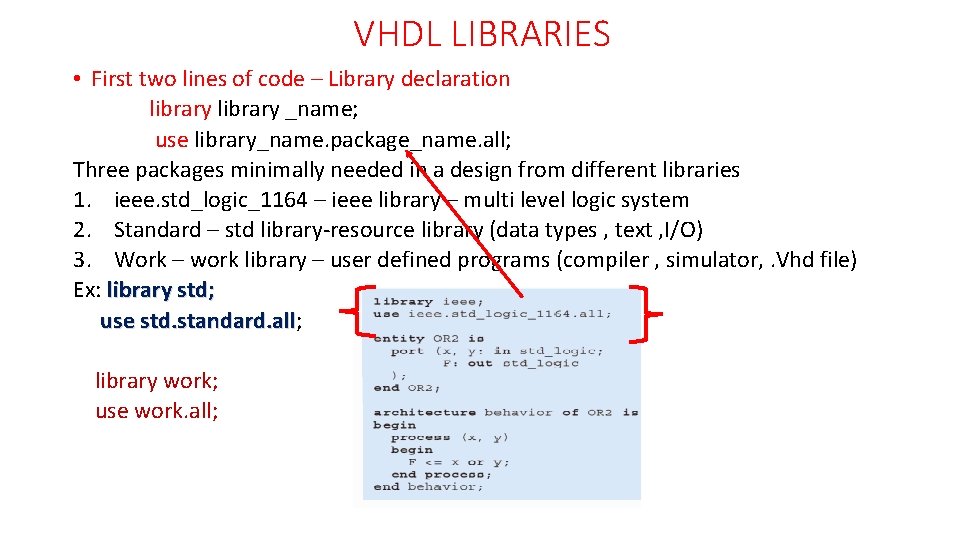

VHDL LIBRARIES • First two lines of code – Library declaration library _name; use library_name. package_name. all; Three packages minimally needed in a design from different libraries 1. ieee. std_logic_1164 – ieee library – multi level logic system 2. Standard – std library-resource library (data types , text , I/O) 3. Work – work library – user defined programs (compiler , simulator, . Vhd file) Ex: library std; use std. standard. all; std. standard. all library work; use work. all;

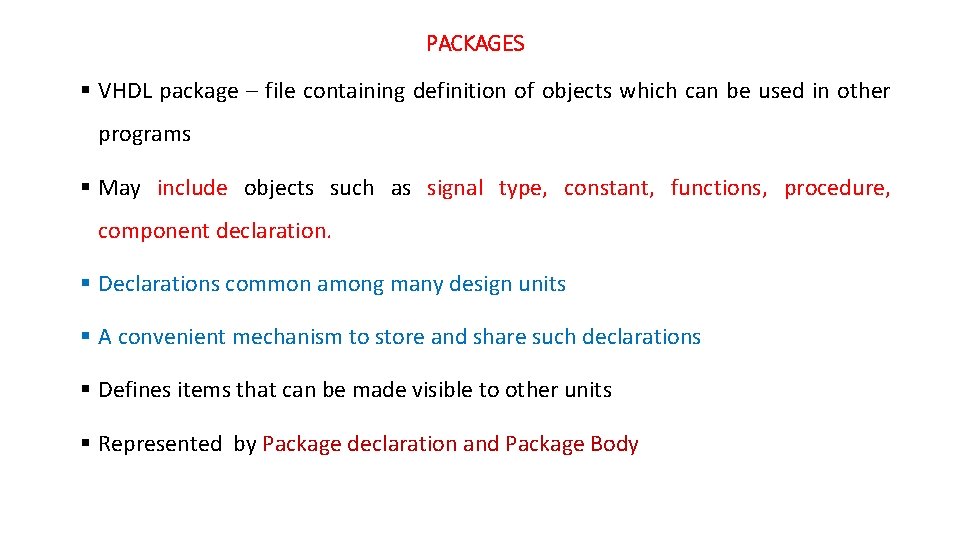

PACKAGES § VHDL package – file containing definition of objects which can be used in other programs § May include objects such as signal type, constant, functions, procedure, component declaration. § Declarations common among many design units § A convenient mechanism to store and share such declarations § Defines items that can be made visible to other units § Represented by Package declaration and Package Body

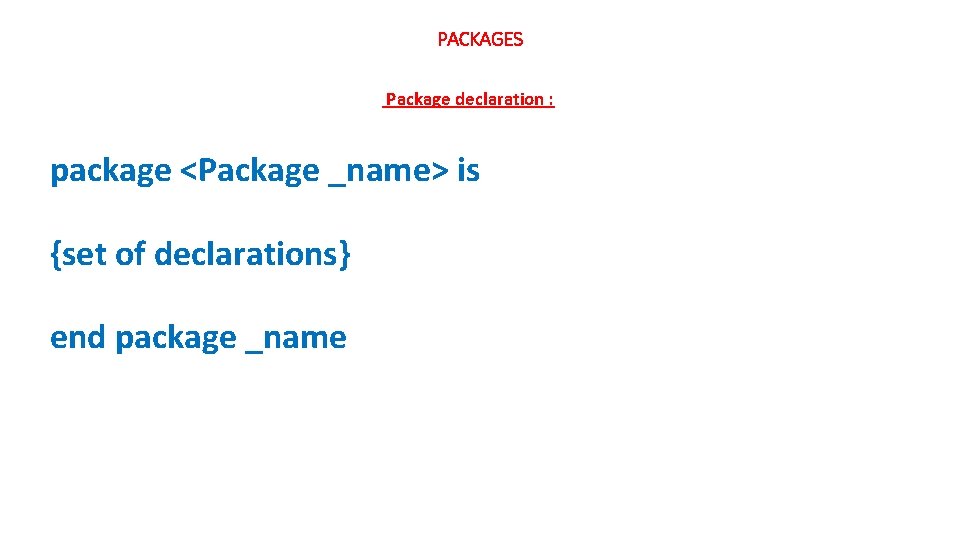

PACKAGES Package declaration : package <Package _name> is {set of declarations} end package _name

Packages Package body: package body package_name is <declarations>; <sub program body>; end package_name; • Specifies the actual behavior of the package (Similar as architecture). • A Package Declaration can have only one Package body, both having the same names. (Contrast to entity architecture)

PACKAGES Examples : library IEEE; - std_logic_1164 ---Std_logic (8 levels) , std_ulogic (9 levels) , std_logic_arith. Sttd_logic_signed, std_logic_unsigned • Library design_lib; • Use design_Lib. Ex_pack. D_FF;

SUB PROGRAM • There are two types of subprograms in VHDL * FUNCTION -- Returns a single value * PROCEDURE --Can return multiple values • Although subprograms can be defined either in a package, architecture or process it is usually defined in a package so that they can be reused. • VHDL code is sequential inside subprograms.

SUB PROGRAM • Subprograms are termed impure if they modify or depend on parameters not defined in their formal parameter list. ONLY VHDL’ 93 SUPPORTS IMPURE FUNCTION. • Subprograms can be called sequentially within a process or concurrently in the architecture • A function has to be on the right hand size of a signal assignment whereas a procedure can be called independently.

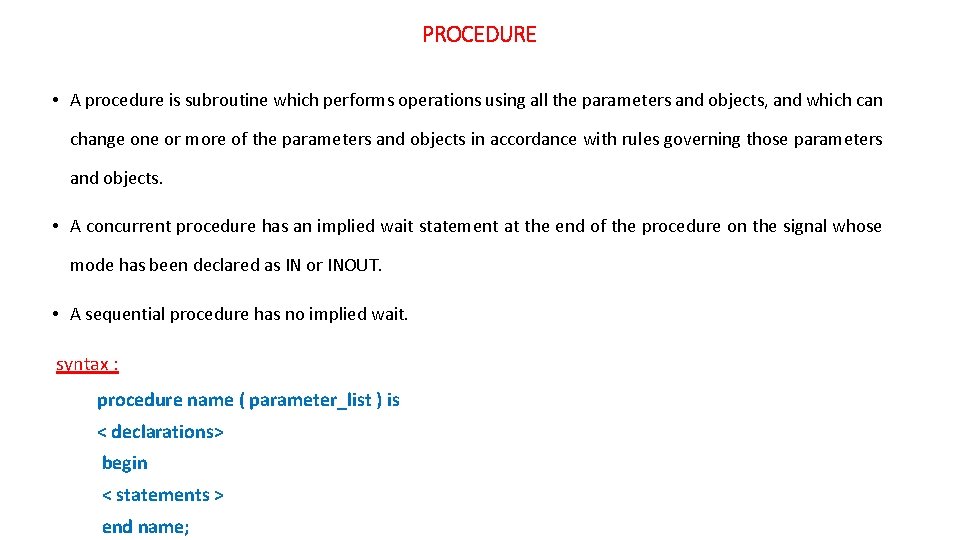

PROCEDURE • A procedure is subroutine which performs operations using all the parameters and objects, and which can change one or more of the parameters and objects in accordance with rules governing those parameters and objects. • A concurrent procedure has an implied wait statement at the end of the procedure on the signal whose mode has been declared as IN or INOUT. • A sequential procedure has no implied wait. syntax : procedure name ( parameter_list ) is < declarations> begin < statements > end name;

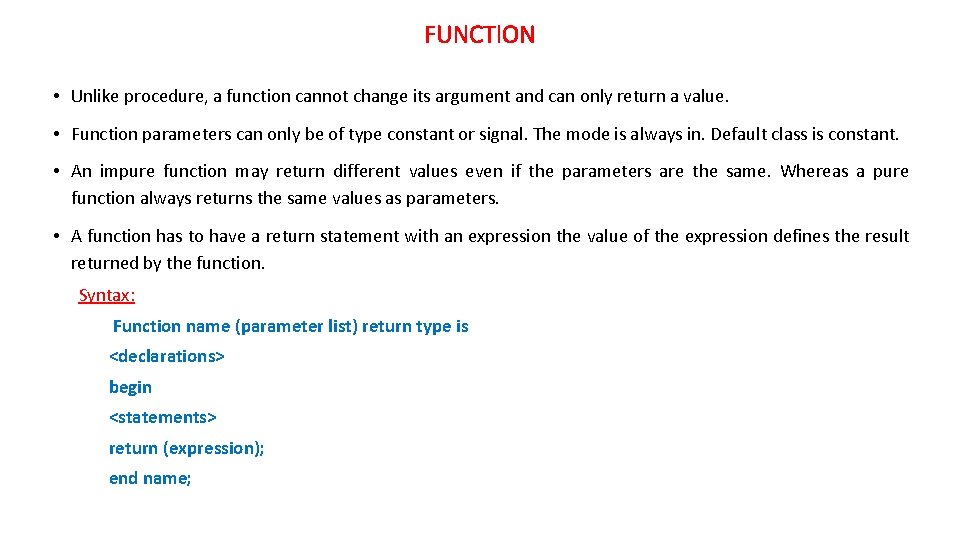

FUNCTION • Unlike procedure, a function cannot change its argument and can only return a value. • Function parameters can only be of type constant or signal. The mode is always in. Default class is constant. • An impure function may return different values even if the parameters are the same. Whereas a pure function always returns the same values as parameters. • A function has to have a return statement with an expression the value of the expression defines the result returned by the function. Syntax: Function name (parameter list) return type is <declarations> begin <statements> return (expression); end name;

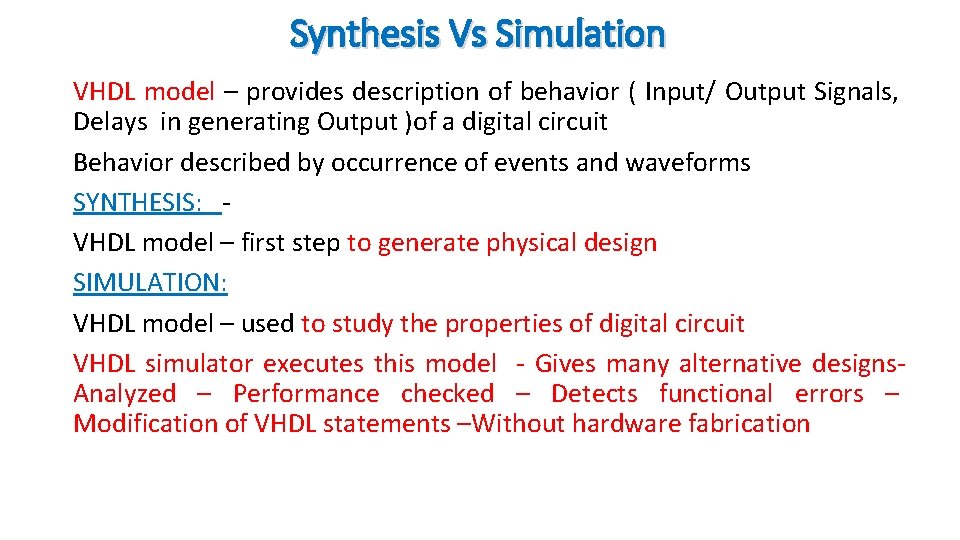

Synthesis Vs Simulation VHDL model – provides description of behavior ( Input/ Output Signals, Delays in generating Output )of a digital circuit Behavior described by occurrence of events and waveforms SYNTHESIS: VHDL model – first step to generate physical design SIMULATION: VHDL model – used to study the properties of digital circuit VHDL simulator executes this model - Gives many alternative designs. Analyzed – Performance checked – Detects functional errors – Modification of VHDL statements –Without hardware fabrication

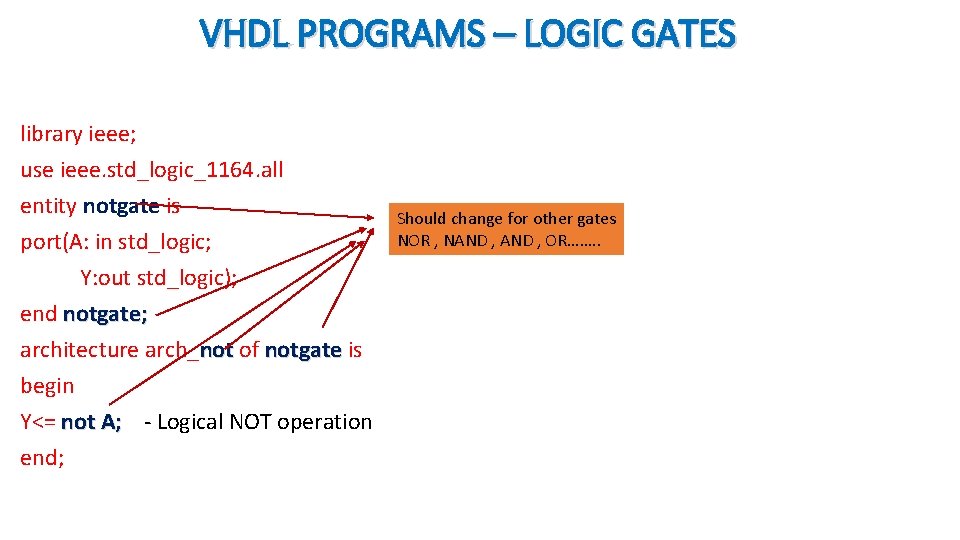

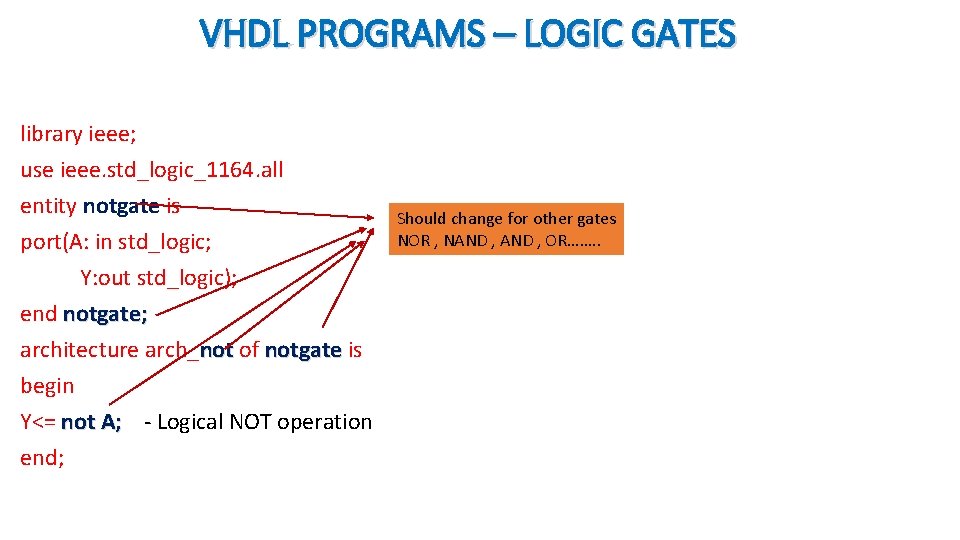

VHDL PROGRAMS – LOGIC GATES library ieee; use ieee. std_logic_1164. all entity notgate is port(A: in std_logic; Y: out std_logic); end notgate; architecture arch_not of notgate is begin Y<= not A; - Logical NOT operation end; Should change for other gates NOR , NAND , OR……. .

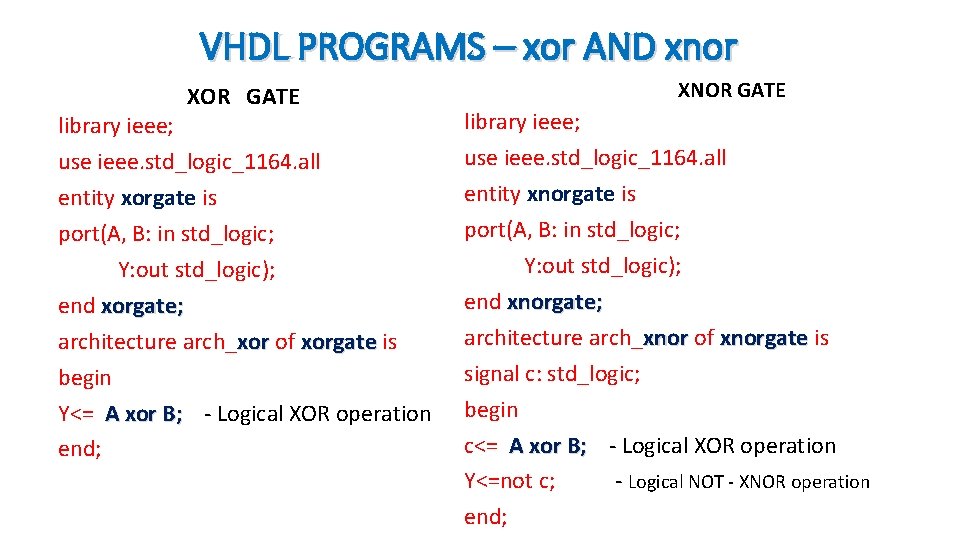

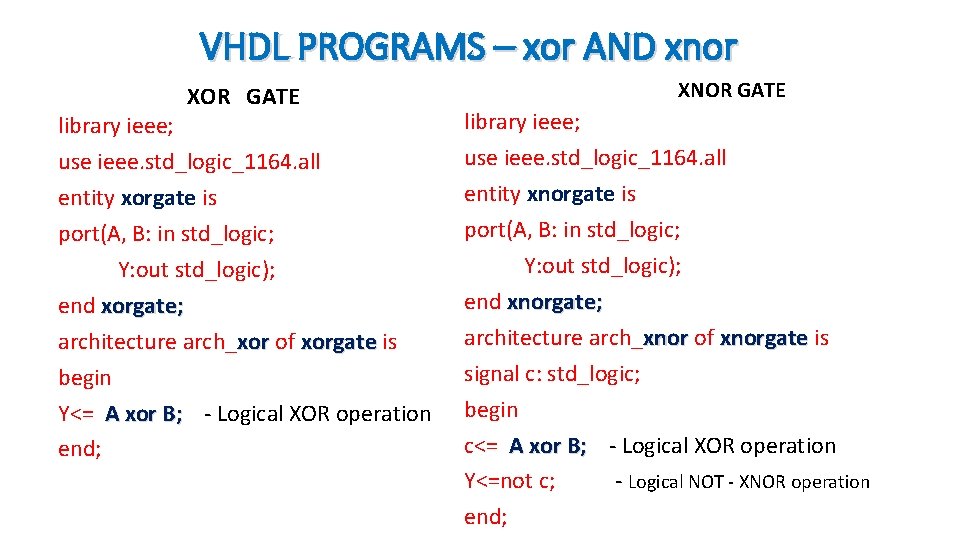

VHDL PROGRAMS – xor AND xnor XOR GATE library ieee; use ieee. std_logic_1164. all entity xorgate is port(A, B: in std_logic; Y: out std_logic); end xorgate; architecture arch_xor of xorgate is begin Y<= A xor B; - Logical XOR operation end; XNOR GATE library ieee; use ieee. std_logic_1164. all entity xnorgate is port(A, B: in std_logic; Y: out std_logic); end xnorgate; architecture arch_xnor of xnorgate is signal c: std_logic; begin c<= A xor B; - Logical XOR operation Y<=not c; - Logical NOT - XNOR operation end;

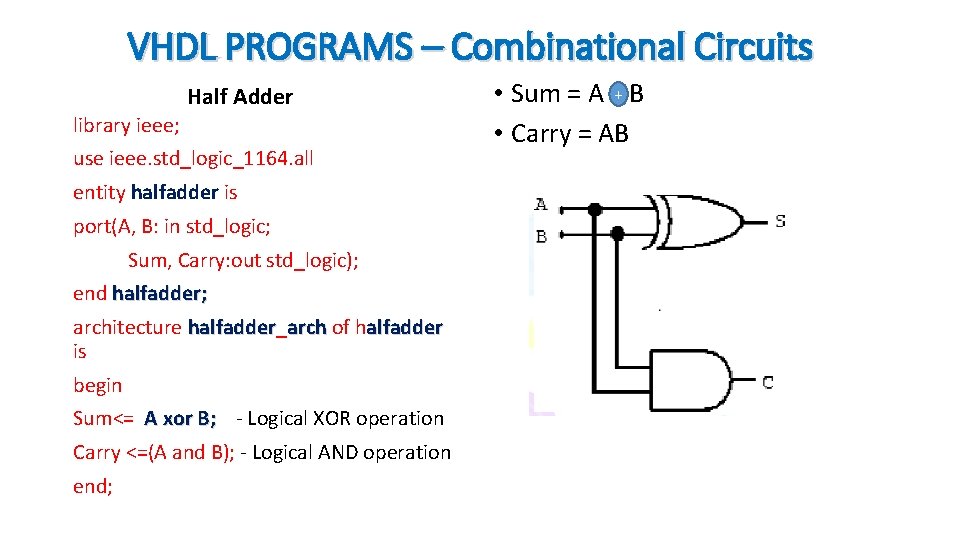

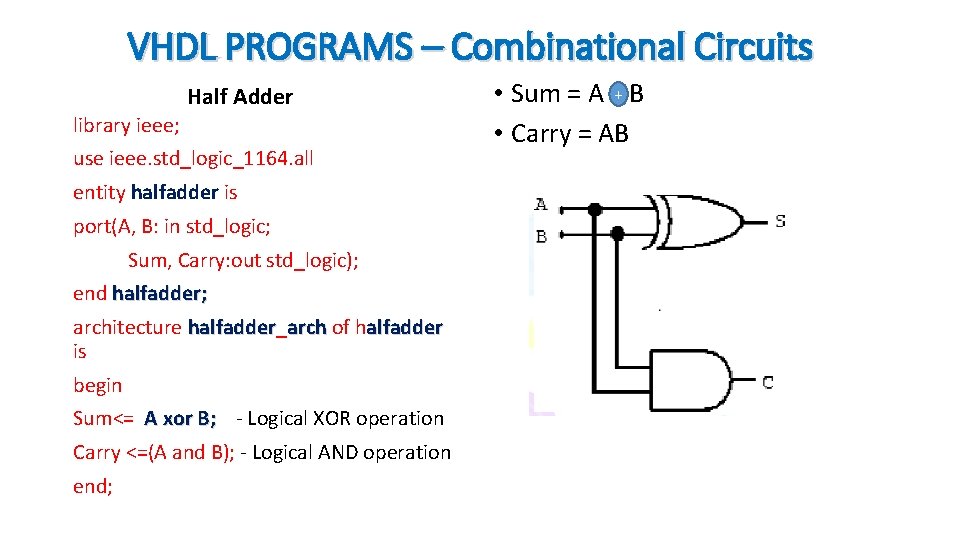

VHDL PROGRAMS – Combinational Circuits Half Adder library ieee; use ieee. std_logic_1164. all entity halfadder is port(A, B: in std_logic; Sum, Carry: out std_logic); end halfadder; architecture halfadder_ halfadder arch of halfadder is begin Sum<= A xor B; - Logical XOR operation Carry <=(A and B); - Logical AND operation end; • Sum = A + B • Carry = AB

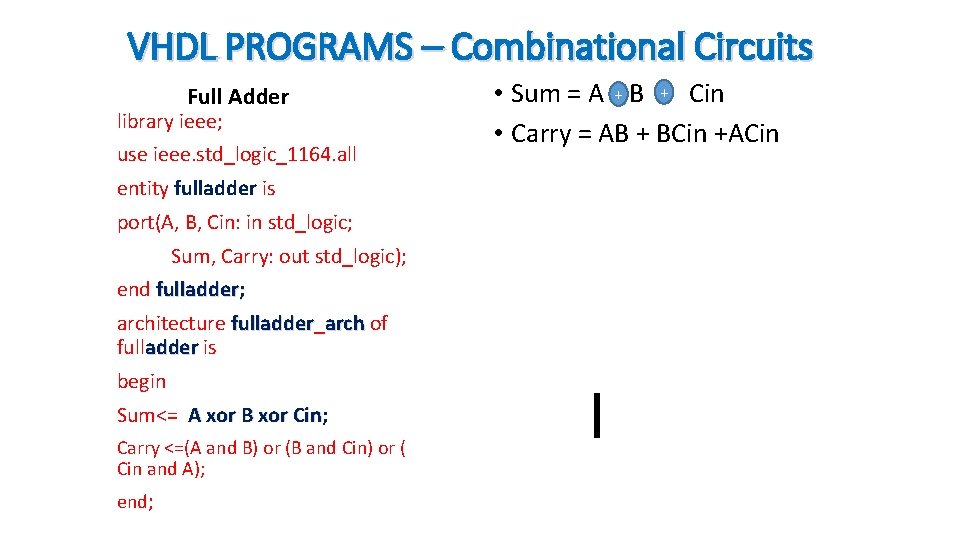

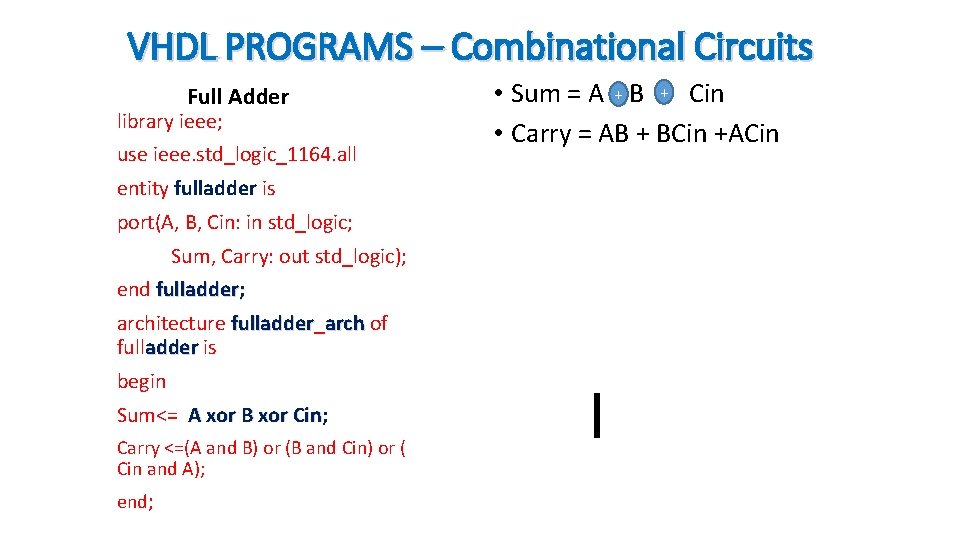

VHDL PROGRAMS – Combinational Circuits Full Adder library ieee; use ieee. std_logic_1164. all entity fulladder is port(A, B, Cin: in std_logic; Sum, Carry: out std_logic); end fulladder; architecture fulladder_ fulladder arch of fulladder is begin Sum<= A xor B xor Cin; Carry <=(A and B) or (B and Cin) or ( Cin and A); end; • Sum = A + B + Cin • Carry = AB + BCin +ACin

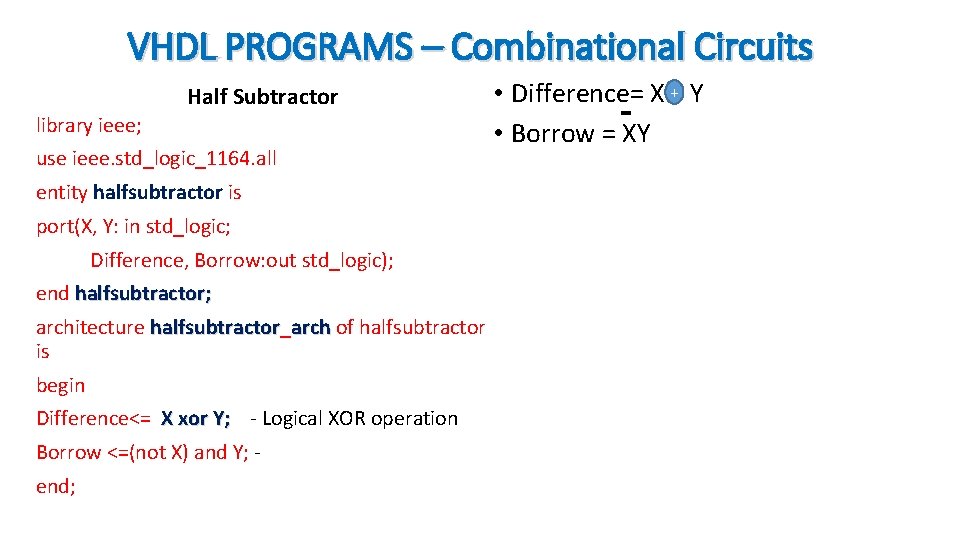

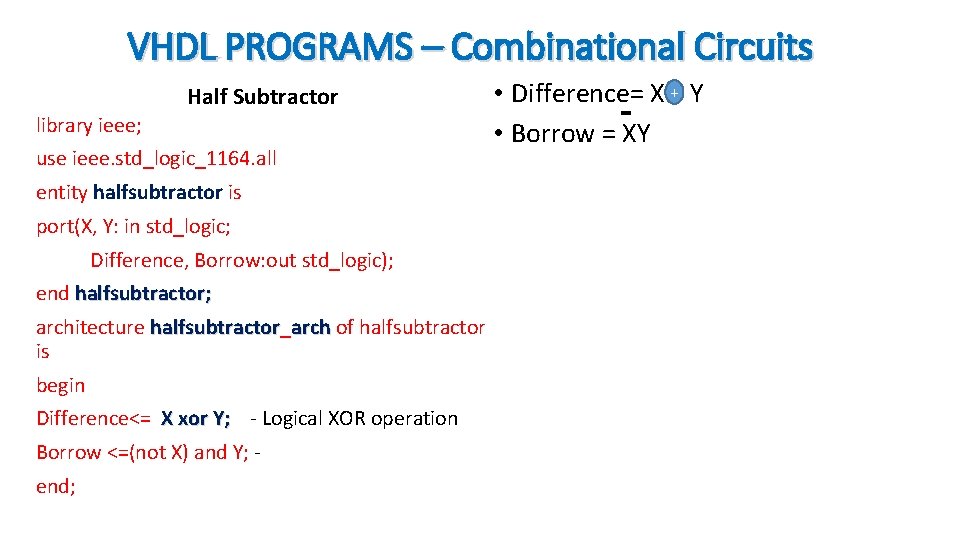

VHDL PROGRAMS – Combinational Circuits Half Subtractor library ieee; use ieee. std_logic_1164. all entity halfsubtractor is port(X, Y: in std_logic; Difference, Borrow: out std_logic); end halfsubtractor; architecture halfsubtractor_ halfsubtractor arch of halfsubtractor is begin Difference<= X xor Y; - Logical XOR operation Borrow <=(not X) and Y; end; • Difference= X + Y • Borrow = XY

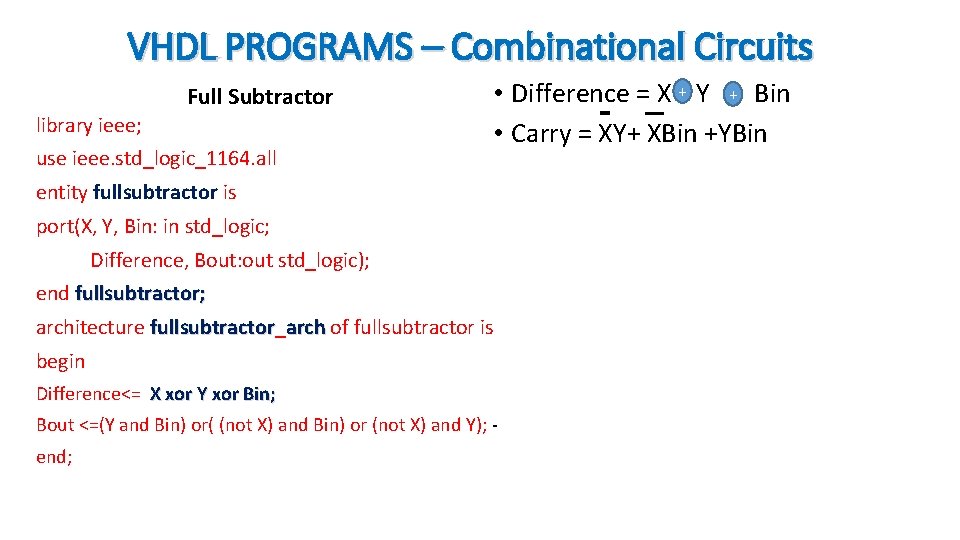

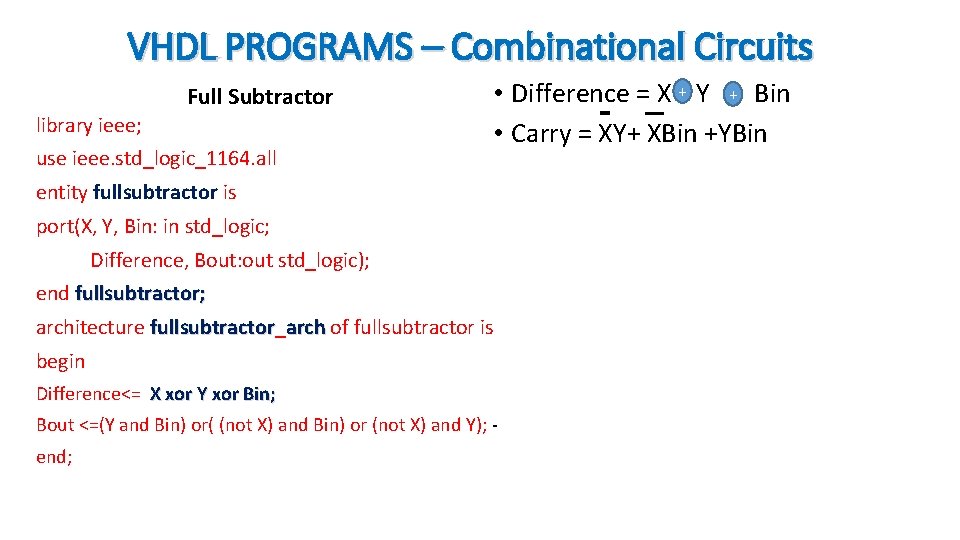

VHDL PROGRAMS – Combinational Circuits Full Subtractor library ieee; use ieee. std_logic_1164. all • Difference = X + Y + Bin • Carry = XY+ XBin +YBin entity fullsubtractor is port(X, Y, Bin: in std_logic; Difference, Bout: out std_logic); end fullsubtractor; architecture fullsubtractor_ fullsubtractor arch of fullsubtractor is begin Difference<= X xor Y xor Bin; Bout <=(Y and Bin) or( (not X) and Bin) or (not X) and Y); end;

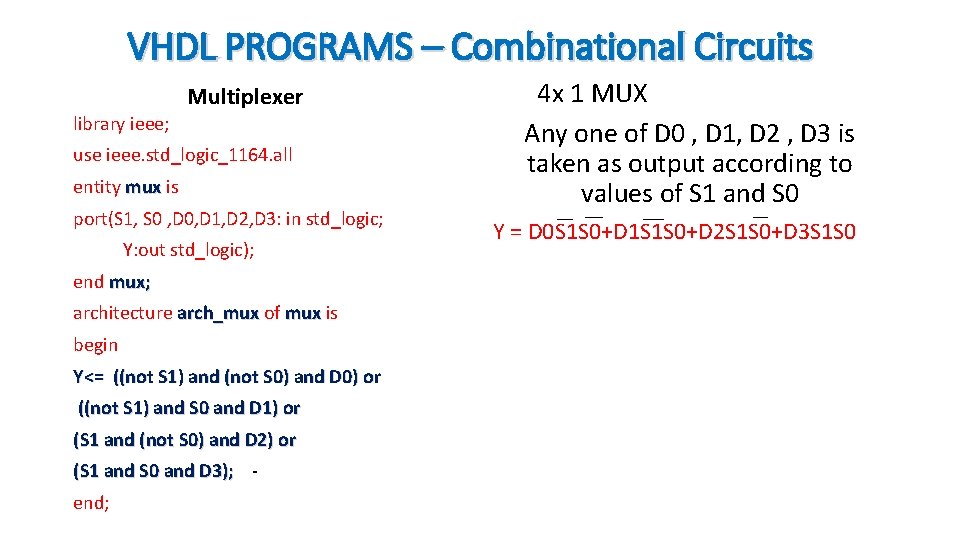

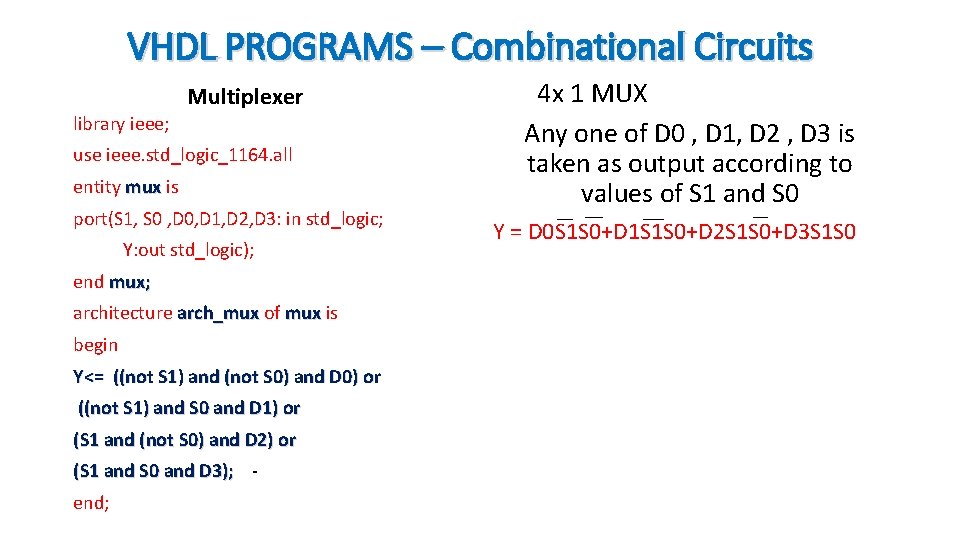

VHDL PROGRAMS – Combinational Circuits Multiplexer library ieee; use ieee. std_logic_1164. all entity mux is port(S 1, S 0 , D 0, D 1, D 2, D 3: in std_logic; Y: out std_logic); end mux; architecture arch_mux of mux is begin Y<= ((not S 1) and (not S 0) and D 0) or ((not S 1) and S 0 and D 1) or (S 1 and (not S 0) and D 2) or (S 1 and S 0 and D 3); end; 4 x 1 MUX Any one of D 0 , D 1, D 2 , D 3 is taken as output according to values of S 1 and S 0 Y = D 0 S 1 S 0+D 1 S 1 S 0+D 2 S 1 S 0+D 3 S 1 S 0

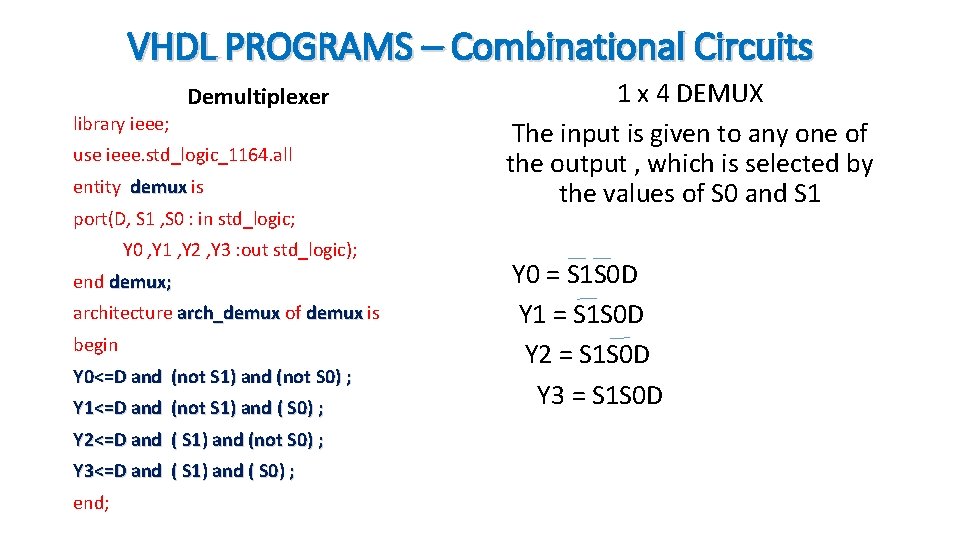

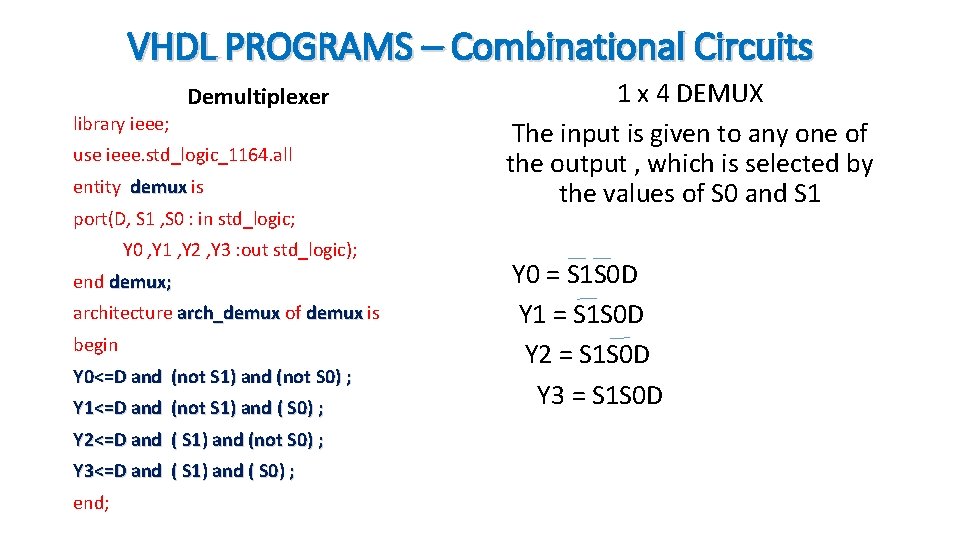

VHDL PROGRAMS – Combinational Circuits Demultiplexer library ieee; use ieee. std_logic_1164. all entity demux is port(D, S 1 , S 0 : in std_logic; Y 0 , Y 1 , Y 2 , Y 3 : out std_logic); end demux; architecture arch_demux of demux is begin Y 0<=D and (not S 1) and (not S 0) ; Y 1<=D and (not S 1) and ( S 0) ; Y 2<=D and ( S 1) and (not S 0) ; Y 3<=D and ( S 1) and ( S 0) ; end; 1 x 4 DEMUX The input is given to any one of the output , which is selected by the values of S 0 and S 1 Y 0 = S 1 S 0 D Y 1 = S 1 S 0 D Y 2 = S 1 S 0 D Y 3 = S 1 S 0 D

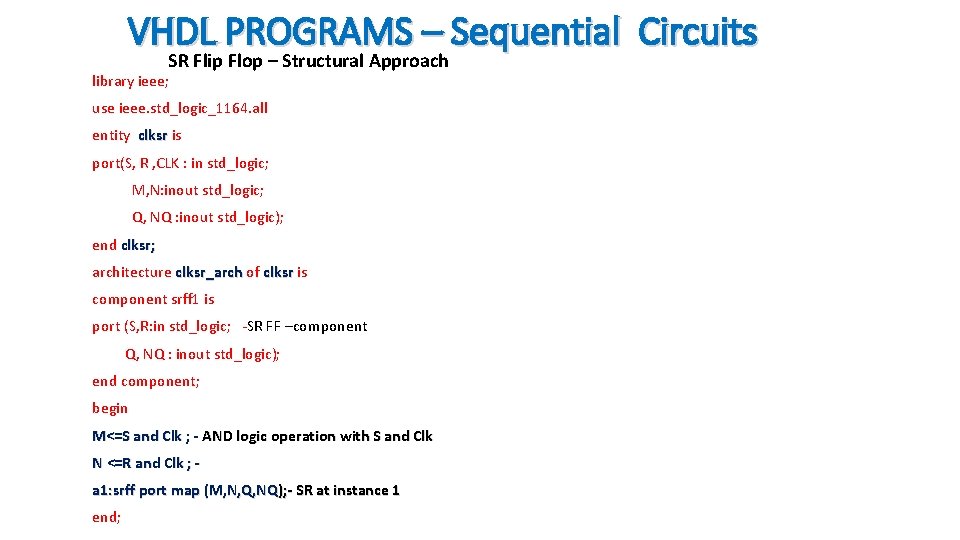

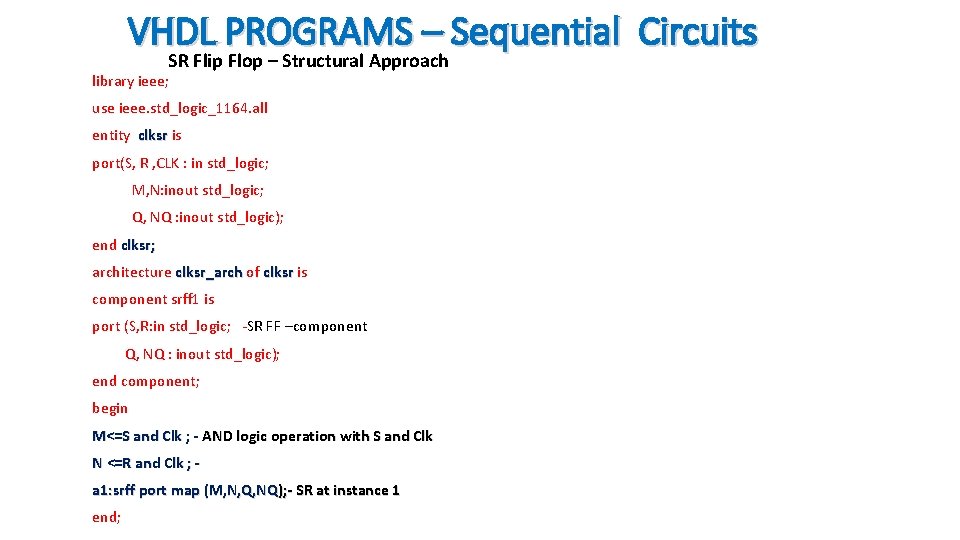

VHDL PROGRAMS – Sequential Circuits SR Flip Flop – Structural Approach library ieee; use ieee. std_logic_1164. all entity clksr is port(S, R , CLK : in std_logic; M, N: inout std_logic; Q, NQ : inout std_logic); end clksr; architecture clksr_arch of clksr is component srff 1 is port (S, R: in std_logic; -SR FF –component Q, NQ : inout std_logic); end component; begin M<=S and Clk ; - AND logic operation with S and Clk N <=R and Clk ; a 1: srff port map (M, N, Q, NQ); - SR at instance 1 end;

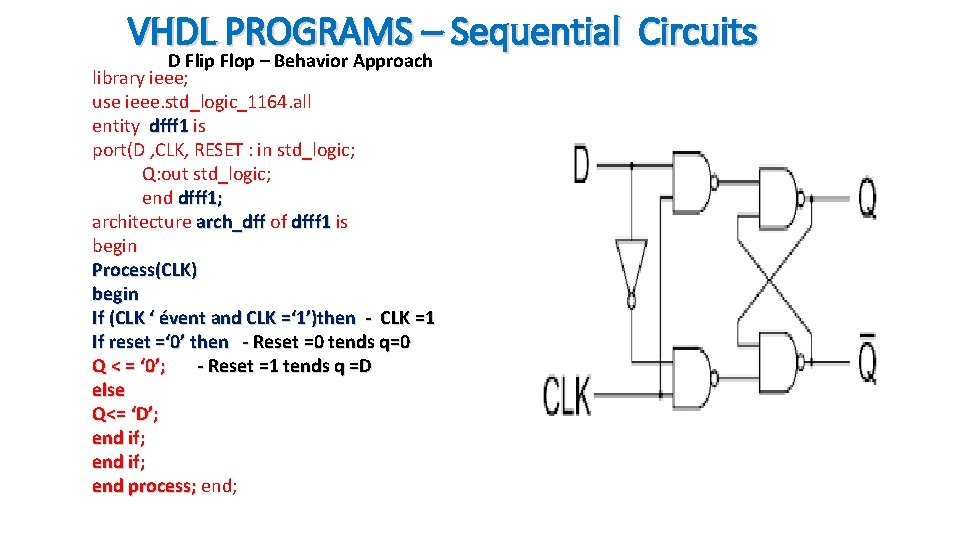

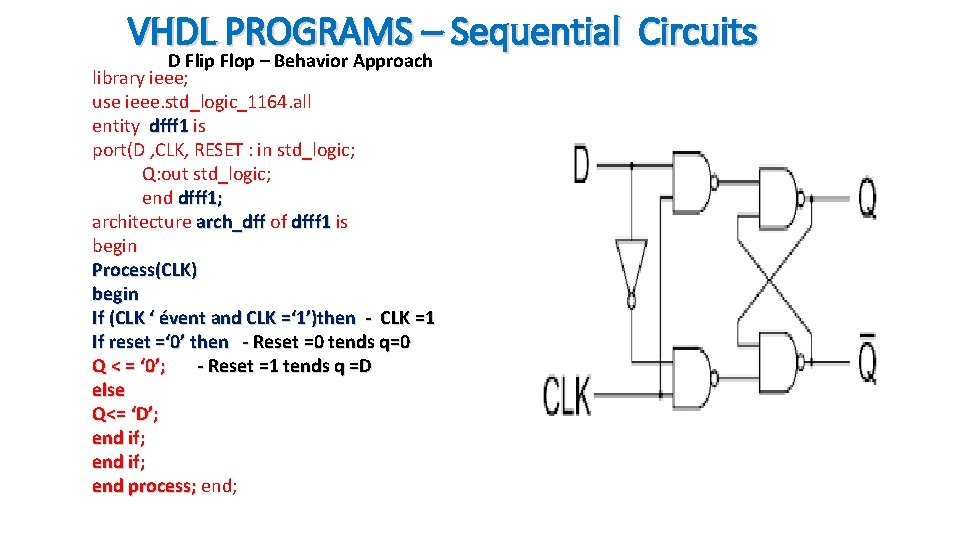

VHDL PROGRAMS – Sequential Circuits D Flip Flop – Behavior Approach library ieee; use ieee. std_logic_1164. all entity dfff 1 is port(D , CLK, RESET : in std_logic; Q: out std_logic; end dfff 1; architecture arch_dff of dfff 1 is begin Process(CLK) begin If (CLK ‘ évent and CLK =‘ 1’)then - CLK =1 If reset =‘ 0’ then - Reset =0 tends q=0 Q < = ‘ 0’; - Reset =1 tends q =D else Q<= ‘D’; end if; end process; end;

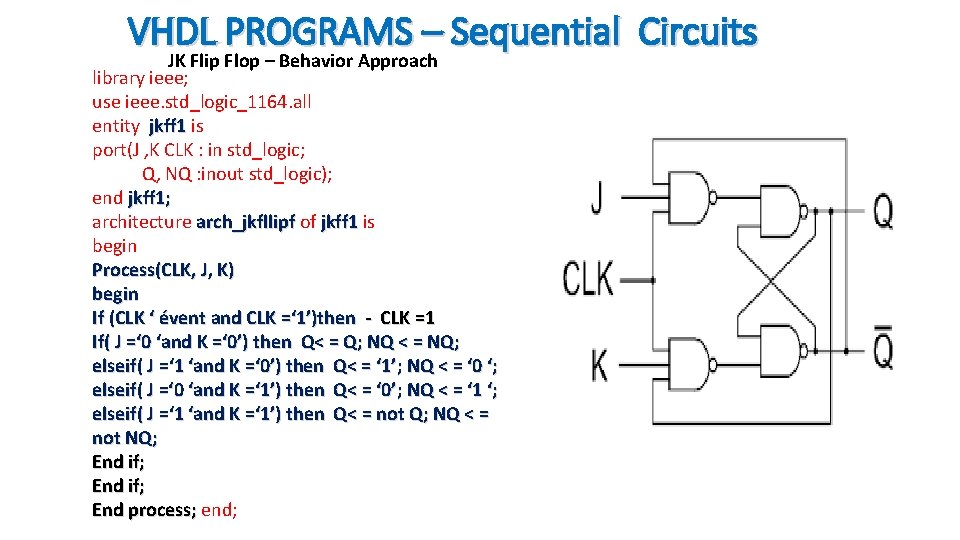

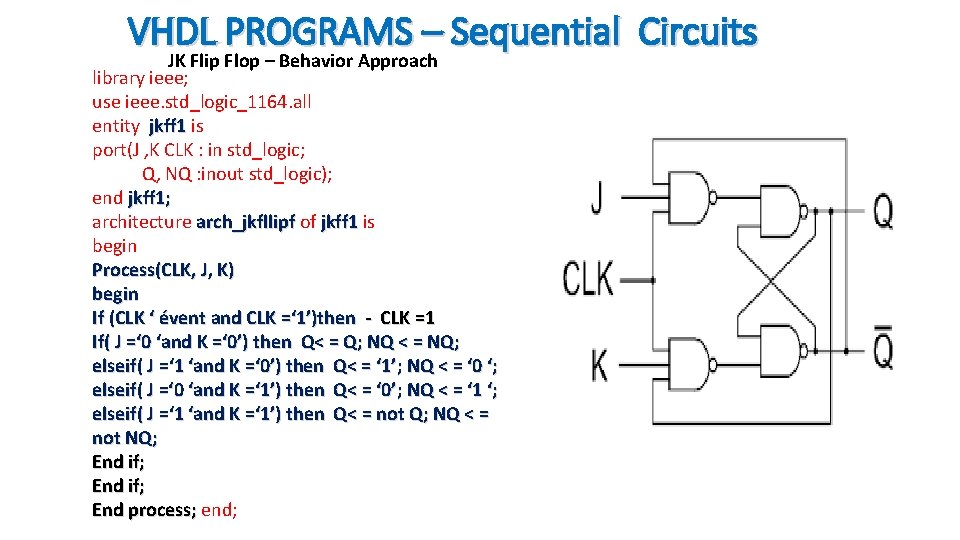

VHDL PROGRAMS – Sequential Circuits JK Flip Flop – Behavior Approach library ieee; use ieee. std_logic_1164. all entity jkff 1 is port(J , K CLK : in std_logic; Q, NQ : inout std_logic); end jkff 1; architecture arch_jkfllipf of jkff 1 is begin Process(CLK, J, K) begin If (CLK ‘ évent and CLK =‘ 1’)then - CLK =1 If( J =‘ 0 ‘and K =‘ 0’) then Q< = Q; NQ < = NQ; elseif( J =‘ 1 ‘and K =‘ 0’) then Q< = ‘ 1’; NQ < = ‘ 0 ‘; elseif( J =‘ 0 ‘and K =‘ 1’) then Q< = ‘ 0’; NQ < = ‘ 1 ‘; elseif( J =‘ 1 ‘and K =‘ 1’) then Q< = not Q; NQ < = not NQ; End if; End process; end;

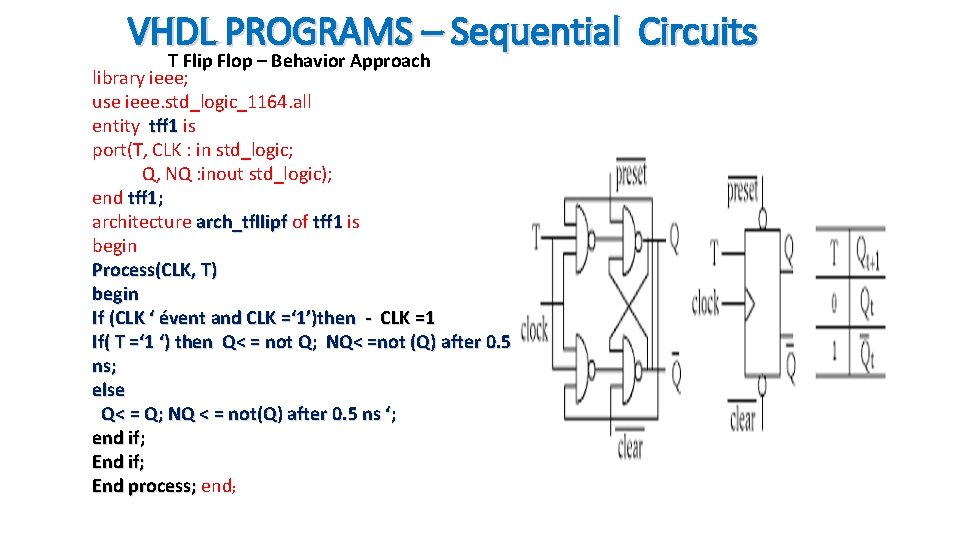

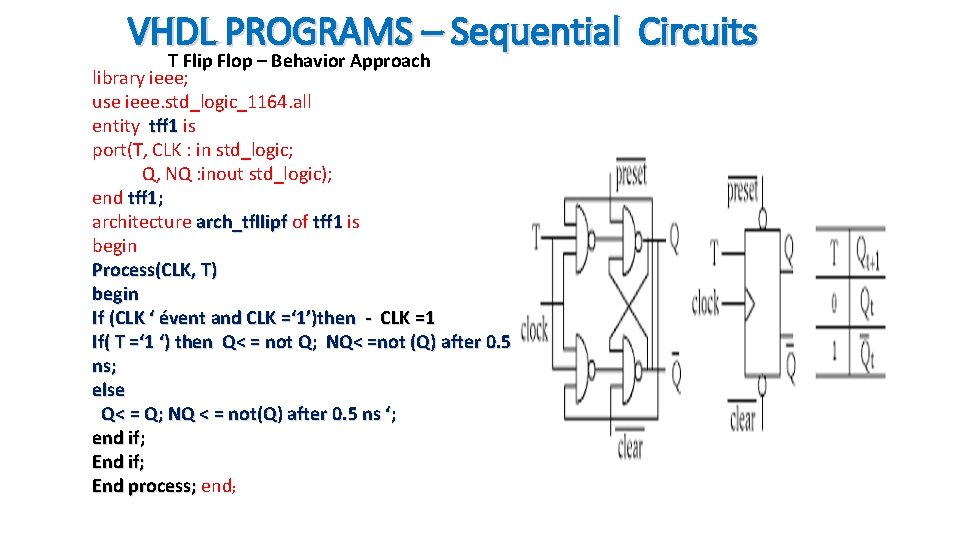

VHDL PROGRAMS – Sequential Circuits T Flip Flop – Behavior Approach library ieee; use ieee. std_logic_1164. all entity tff 1 is port(T, CLK : in std_logic; Q, NQ : inout std_logic); end tff 1; architecture arch_tfllipf of tff 1 is begin Process(CLK, T) begin If (CLK ‘ évent and CLK =‘ 1’)then - CLK =1 If( T =‘ 1 ‘) then Q< = not Q; NQ< =not (Q) after 0. 5 ns; else Q< = Q; NQ < = not(Q) after 0. 5 ns ‘; end if; End process; end;

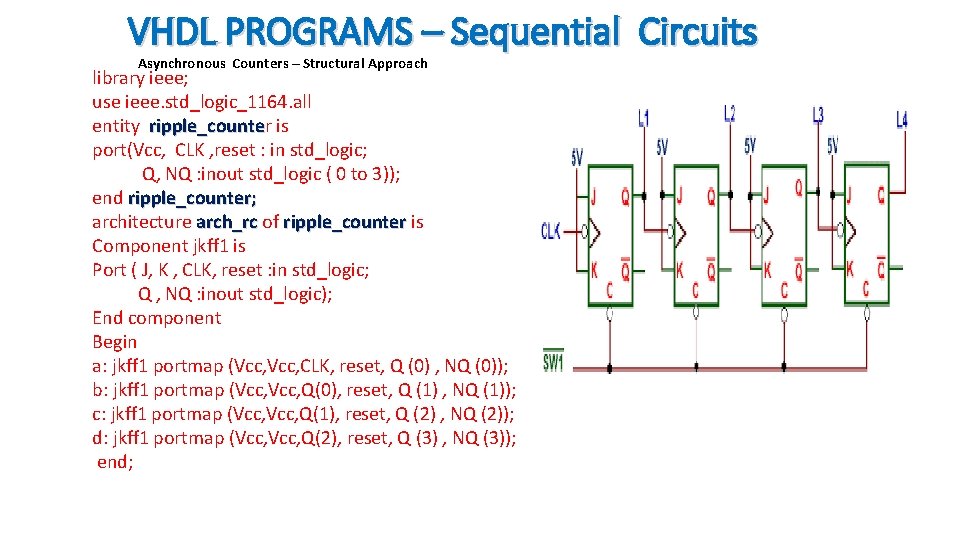

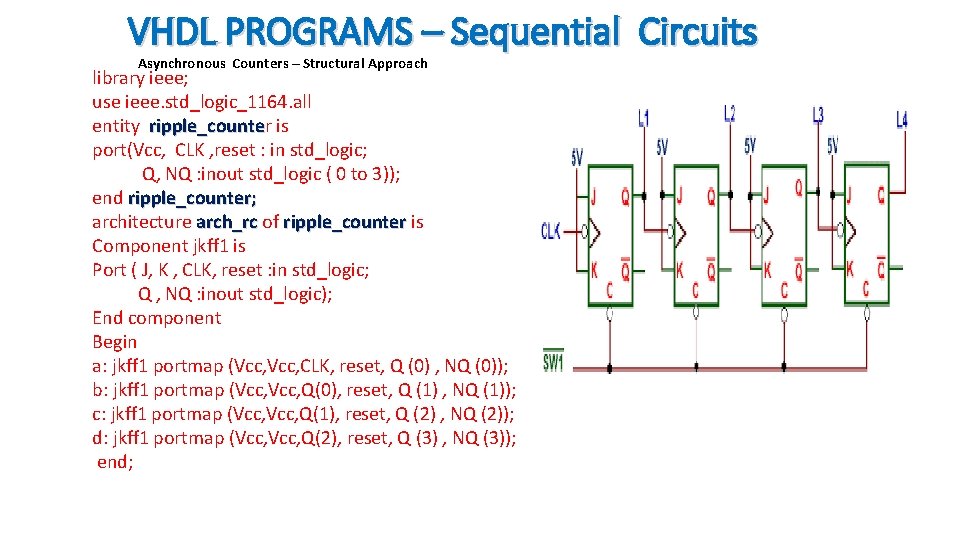

VHDL PROGRAMS – Sequential Circuits Asynchronous Counters – Structural Approach library ieee; use ieee. std_logic_1164. all entity ripple_counter ripple_counte is port(Vcc, CLK , reset : in std_logic; Q, NQ : inout std_logic ( 0 to 3)); end ripple_counter; architecture arch_rc of ripple_counter is Component jkff 1 is Port ( J, K , CLK, reset : in std_logic; Q , NQ : inout std_logic); End component Begin a: jkff 1 portmap (Vcc, CLK, reset, Q (0) , NQ (0)); b: jkff 1 portmap (Vcc, Q(0), reset, Q (1) , NQ (1)); c: jkff 1 portmap (Vcc, Q(1), reset, Q (2) , NQ (2)); d: jkff 1 portmap (Vcc, Q(2), reset, Q (3) , NQ (3)); end;

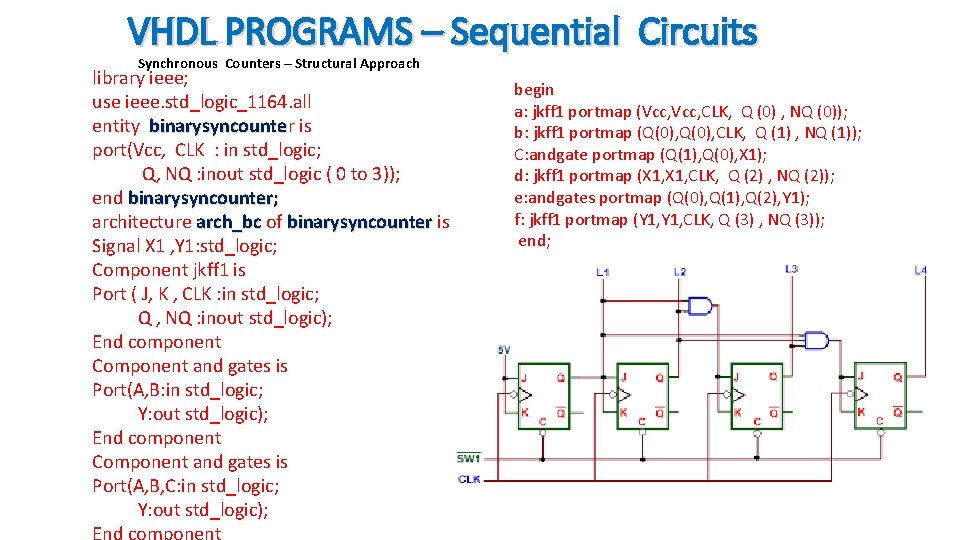

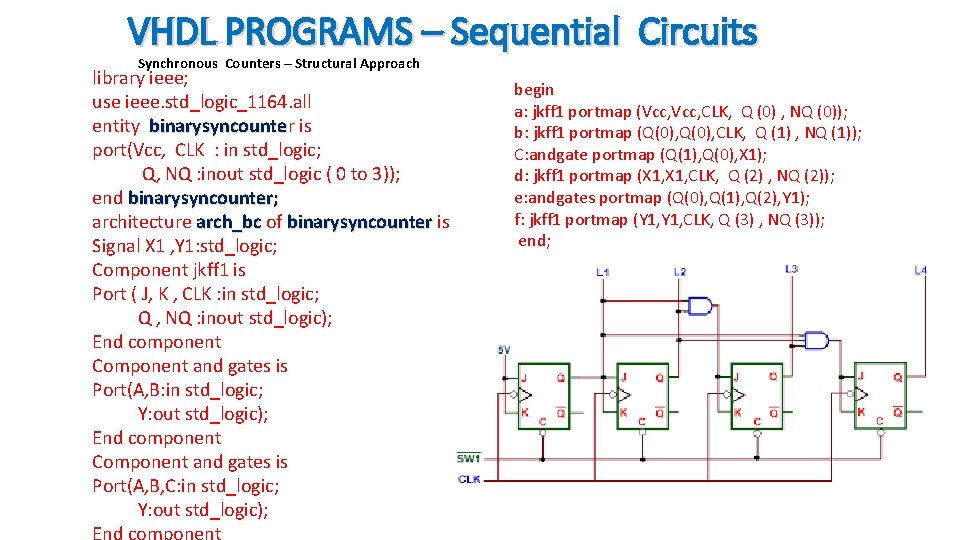

VHDL PROGRAMS – Sequential Circuits Synchronous Counters – Structural Approach library ieee; use ieee. std_logic_1164. all entity binarysyncounter binarysyncounte is port(Vcc, CLK : in std_logic; Q, NQ : inout std_logic ( 0 to 3)); end binarysyncounter; architecture arch_bc of binarysyncounter is Signal X 1 , Y 1: std_logic; Component jkff 1 is Port ( J, K , CLK : in std_logic; Q , NQ : inout std_logic); End component Component and gates is Port(A, B: in std_logic; Y: out std_logic); End component Component and gates is Port(A, B, C: in std_logic; Y: out std_logic); begin a: jkff 1 portmap (Vcc, CLK, Q (0) , NQ (0)); b: jkff 1 portmap (Q(0), CLK, Q (1) , NQ (1)); C: andgate portmap (Q(1), Q(0), X 1); d: jkff 1 portmap (X 1, CLK, Q (2) , NQ (2)); e: andgates portmap (Q(0), Q(1), Q(2), Y 1); f: jkff 1 portmap (Y 1, CLK, Q (3) , NQ (3)); end;

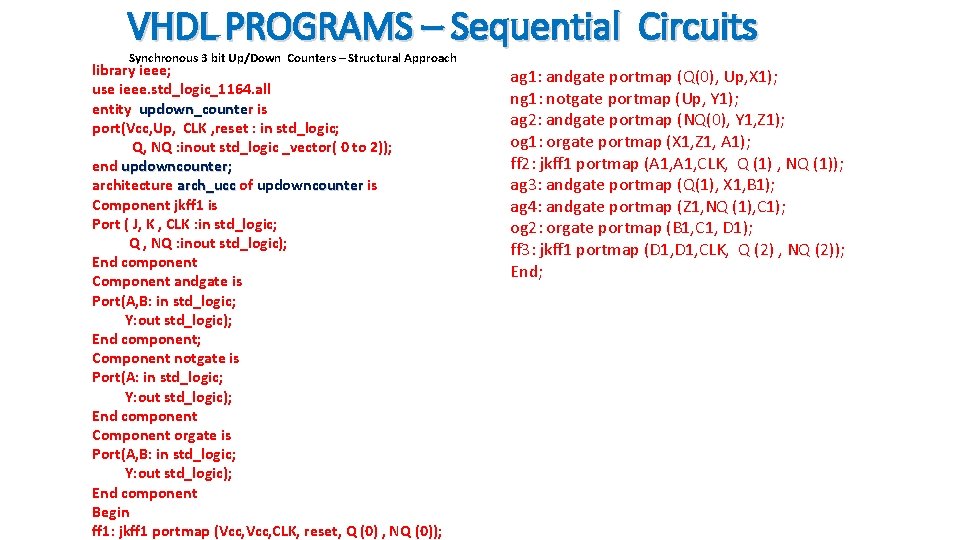

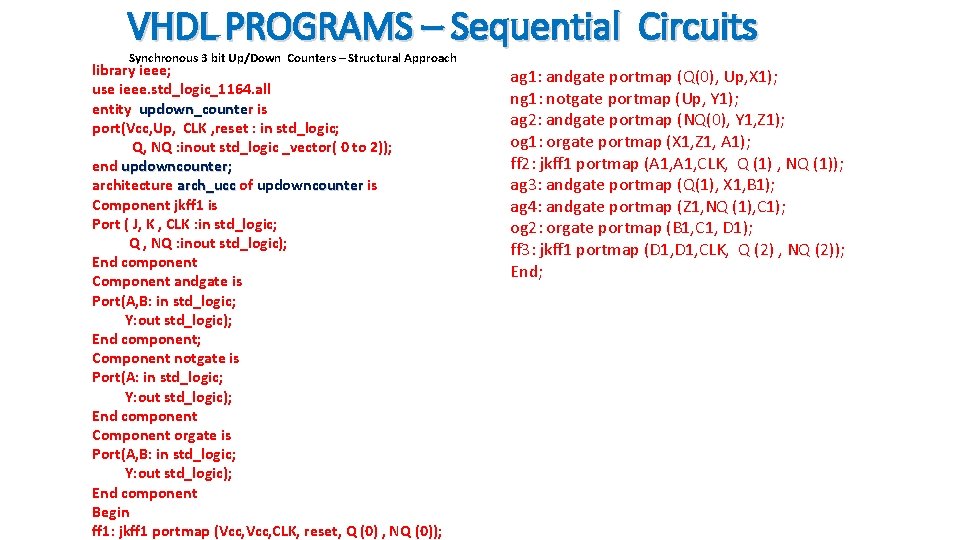

VHDL PROGRAMS – Sequential Circuits Synchronous 3 bit Up/Down Counters – Structural Approach library ieee; use ieee. std_logic_1164. all entity updown_counter updown_counte is port(Vcc, Up, CLK , reset : in std_logic; Q, NQ : inout std_logic _vector( 0 to 2)); end updowncounter; architecture arch_ucc of updowncounter is Component jkff 1 is Port ( J, K , CLK : in std_logic; Q , NQ : inout std_logic); End component Component andgate is Port(A, B: in std_logic; Y: out std_logic); End component; Component notgate is Port(A: in std_logic; Y: out std_logic); End component Component orgate is Port(A, B: in std_logic; Y: out std_logic); End component Begin ff 1: jkff 1 portmap (Vcc, CLK, reset, Q (0) , NQ (0)); ag 1: andgate portmap (Q(0), Up, X 1); ng 1: notgate portmap (Up, Y 1); ag 2: andgate portmap (NQ(0), Y 1, Z 1); og 1: orgate portmap (X 1, Z 1, A 1); ff 2: jkff 1 portmap (A 1, CLK, Q (1) , NQ (1)); ag 3: andgate portmap (Q(1), X 1, B 1); ag 4: andgate portmap (Z 1, NQ (1), C 1); og 2: orgate portmap (B 1, C 1, D 1); ff 3: jkff 1 portmap (D 1, CLK, Q (2) , NQ (2)); End;

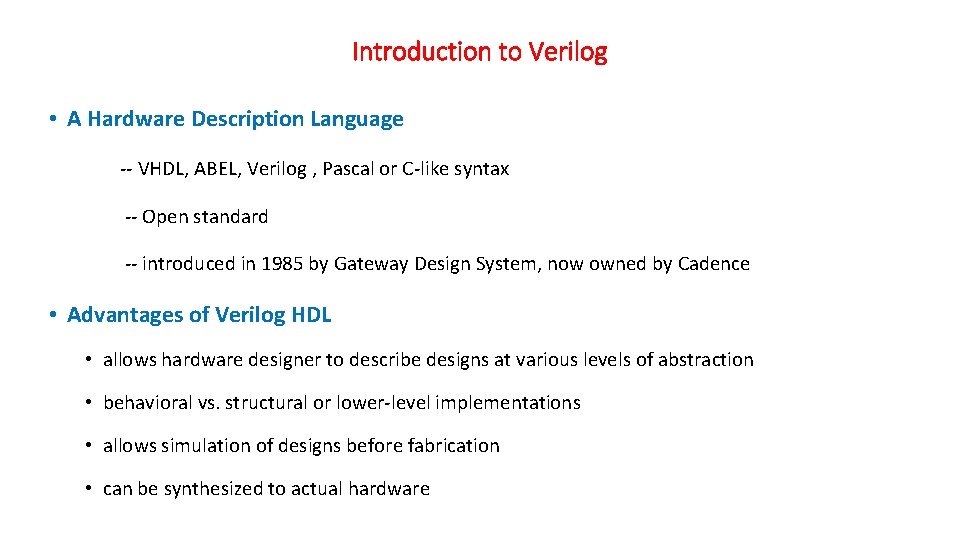

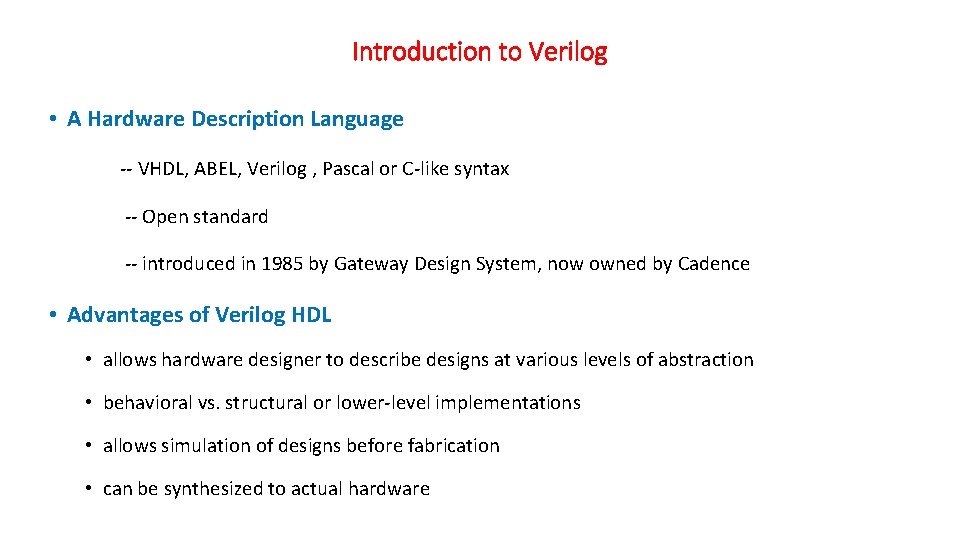

Introduction to Verilog • A Hardware Description Language -- VHDL, ABEL, Verilog , Pascal or C-like syntax -- Open standard -- introduced in 1985 by Gateway Design System, now owned by Cadence • Advantages of Verilog HDL • allows hardware designer to describe designs at various levels of abstraction • behavioral vs. structural or lower-level implementations • allows simulation of designs before fabrication • can be synthesized to actual hardware

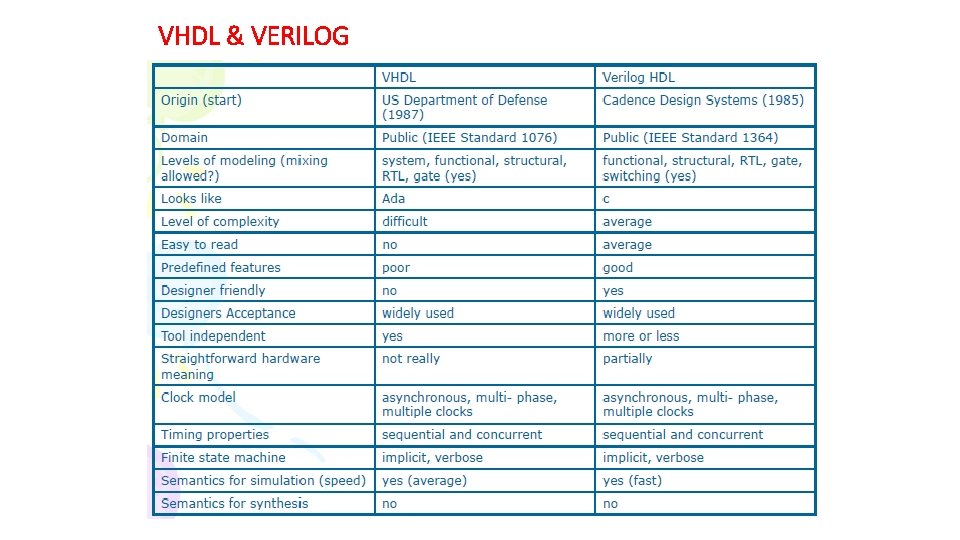

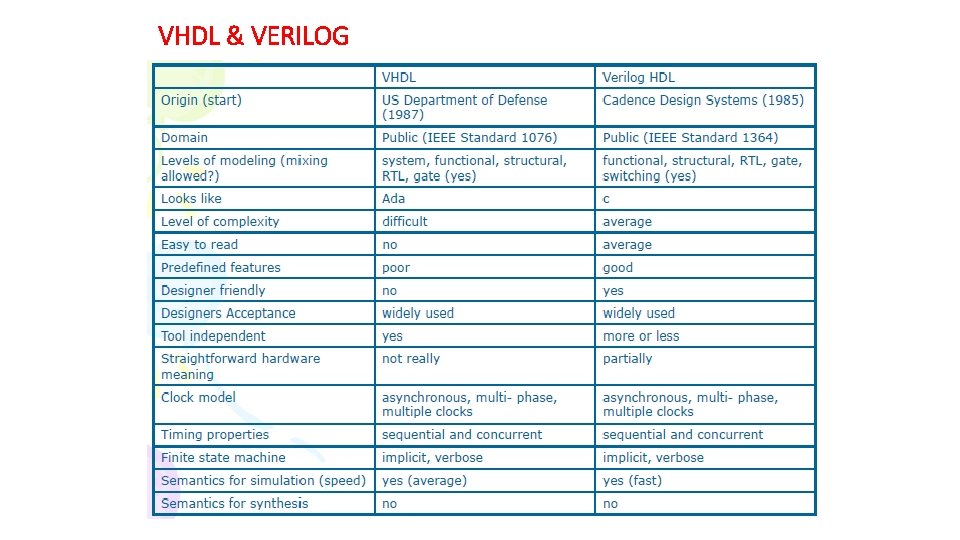

VHDL & VERILOG

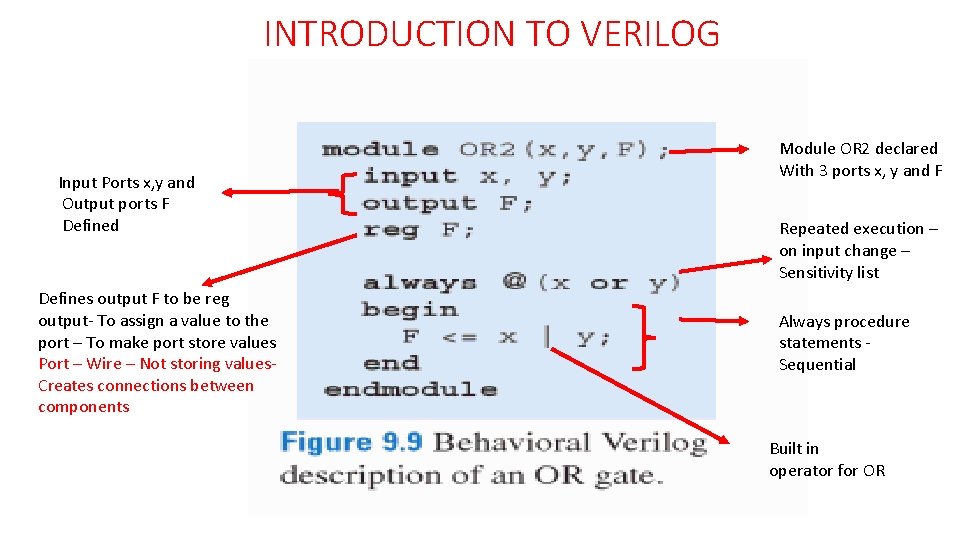

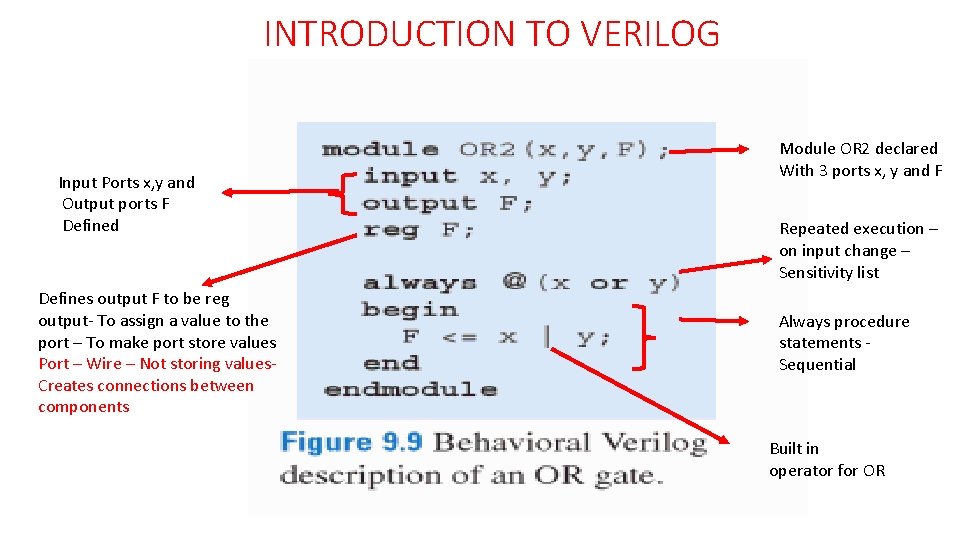

INTRODUCTION TO VERILOG Input Ports x, y and Output ports F Defined Defines output F to be reg output- To assign a value to the port – To make port store values Port – Wire – Not storing values. Creates connections between components Module OR 2 declared With 3 ports x, y and F Repeated execution – on input change – Sensitivity list Always procedure statements Sequential Built in operator for OR