VHDL Hardware Description Language GUIDELINES n How to

![Sequential statements (1) process [process_name: ] PROCESS (sensitivity list) BEGIN sequential statements END PROCESS Sequential statements (1) process [process_name: ] PROCESS (sensitivity list) BEGIN sequential statements END PROCESS](https://slidetodoc.com/presentation_image_h/2e63da5b23a2767091cced57da40cfb8/image-39.jpg)

![for loop statement – shift register [label]: for identifier in range loop statements end for loop statement – shift register [label]: for identifier in range loop statements end](https://slidetodoc.com/presentation_image_h/2e63da5b23a2767091cced57da40cfb8/image-48.jpg)

- Slides: 88

VHDL Hardware Description Language

GUIDELINES n How to write HDL code:

GUIDELINES n How NOT to write HDL code:

Think Hardware NOT Software n Poorly written VHDL code will either be: – Unsynthesizable – Functionally incorrect – Lead to poor performance/area/power results

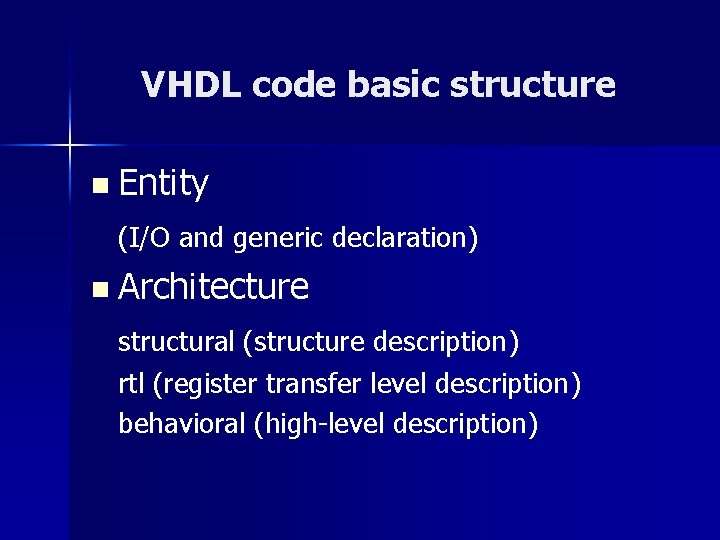

VHDL code basic structure n Entity (I/O and generic declaration) n Architecture structural (structure description) rtl (register transfer level description) behavioral (high-level description)

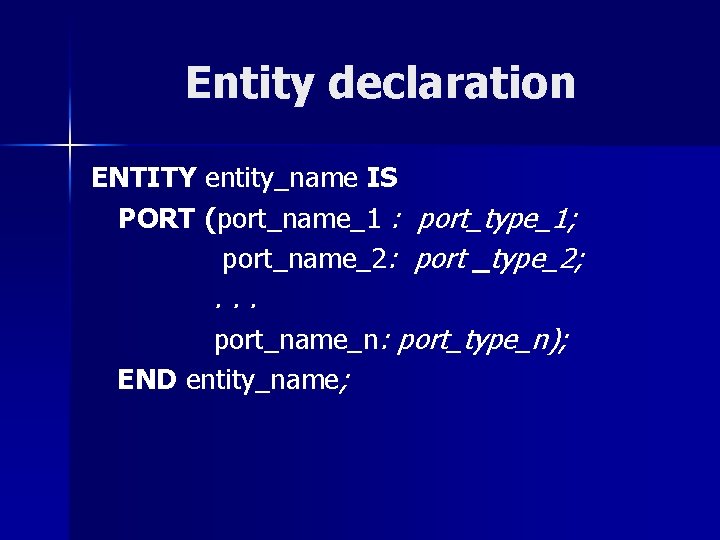

Entity declaration ENTITY entity_name IS PORT (port_name_1 : port_type_1; port_name_2: port _type_2; . . . port_name_n: port_type_n); END entity_name;

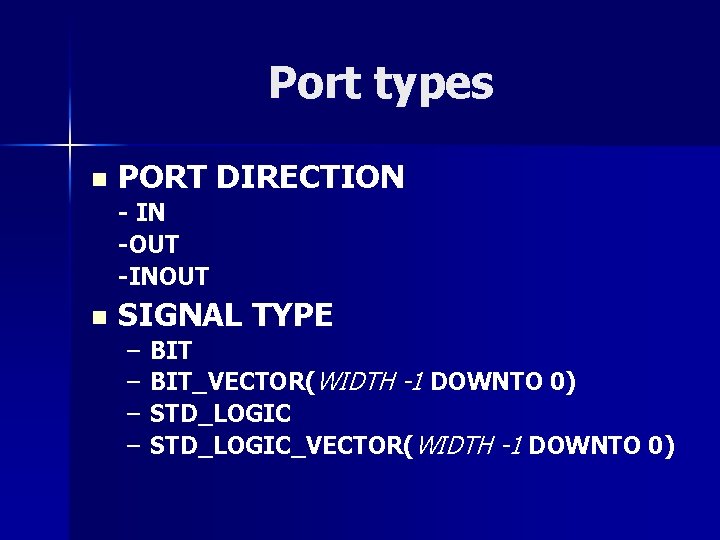

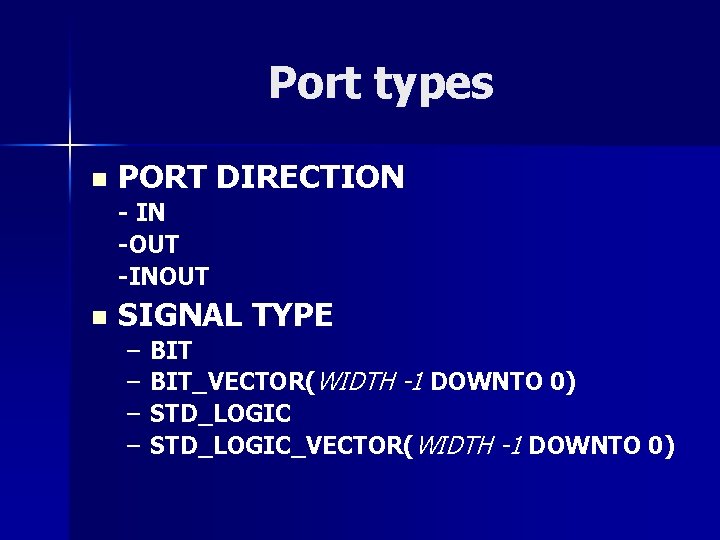

Port types n PORT DIRECTION - IN -OUT -INOUT n SIGNAL TYPE – – BIT_VECTOR(WIDTH -1 DOWNTO 0) STD_LOGIC_VECTOR(WIDTH -1 DOWNTO 0)

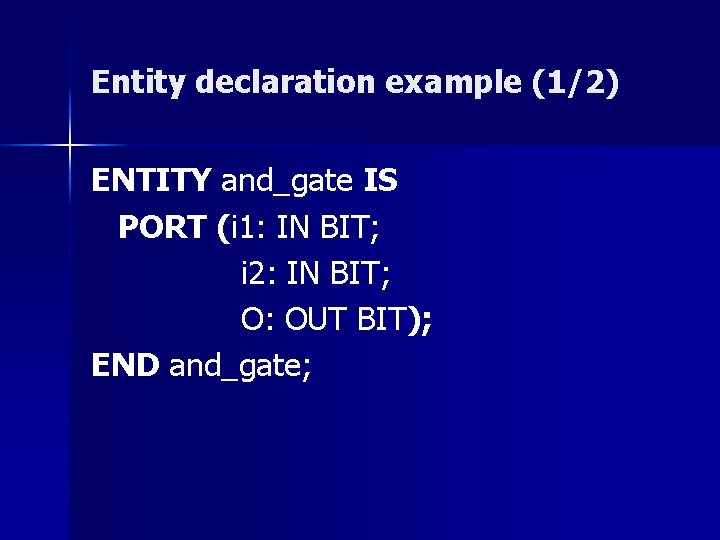

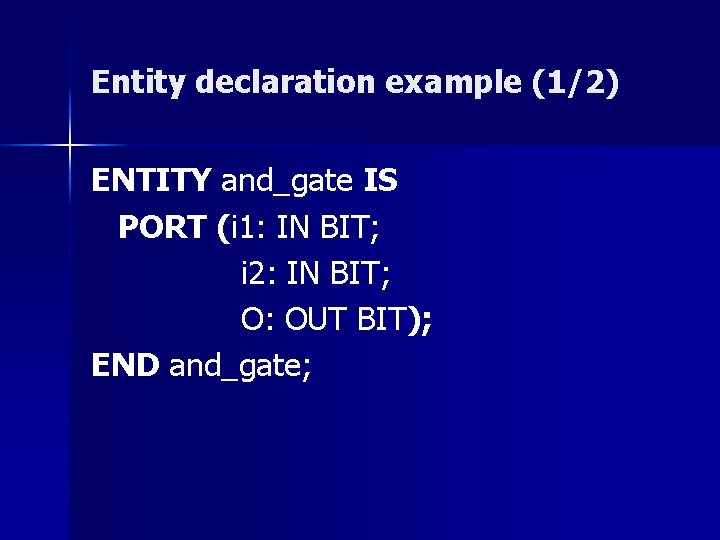

Entity declaration example (1/2) ENTITY and_gate IS PORT (i 1: IN BIT; i 2: IN BIT; O: OUT BIT); END and_gate;

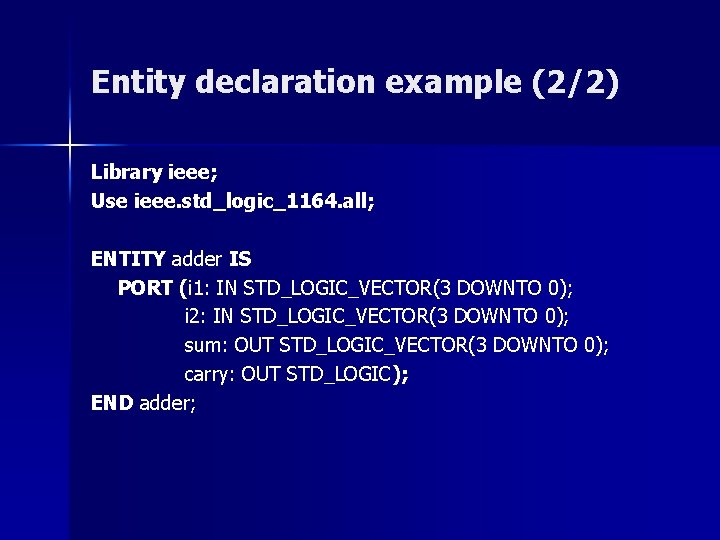

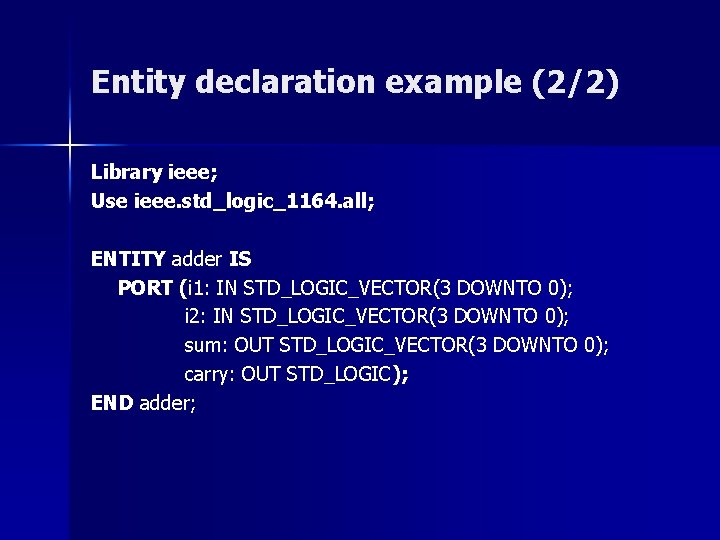

Entity declaration example (2/2) Library ieee; Use ieee. std_logic_1164. all; ENTITY adder IS PORT (i 1: IN STD_LOGIC_VECTOR(3 DOWNTO 0); i 2: IN STD_LOGIC_VECTOR(3 DOWNTO 0); sum: OUT STD_LOGIC_VECTOR(3 DOWNTO 0); carry: OUT STD_LOGIC); END adder;

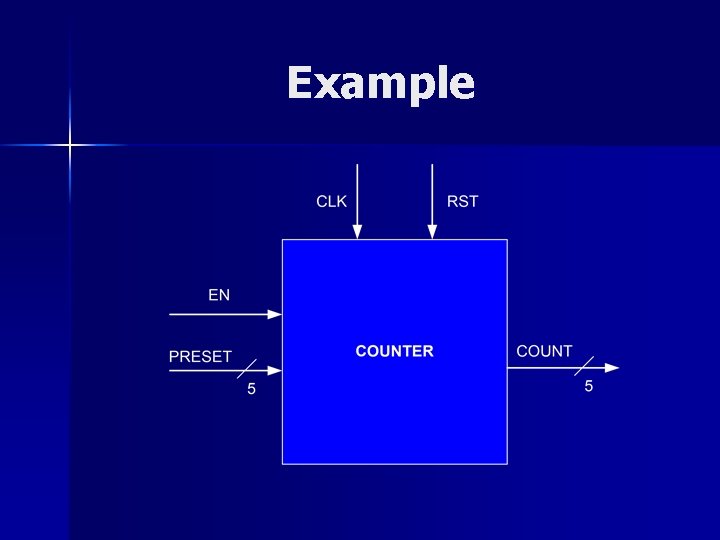

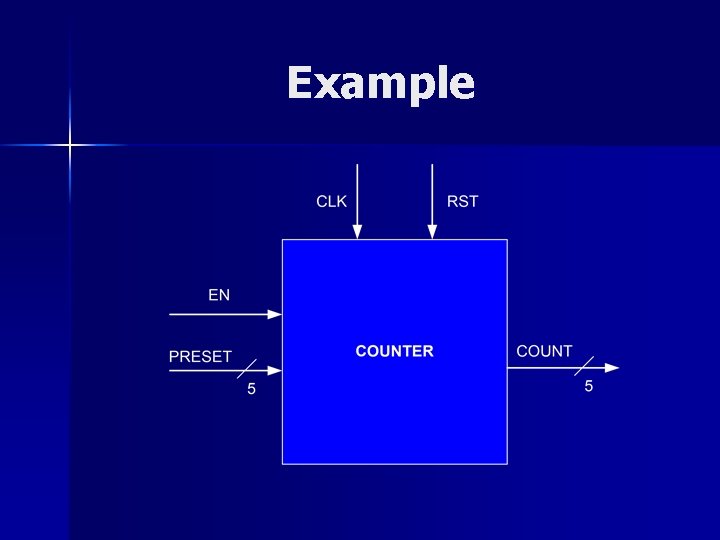

Example

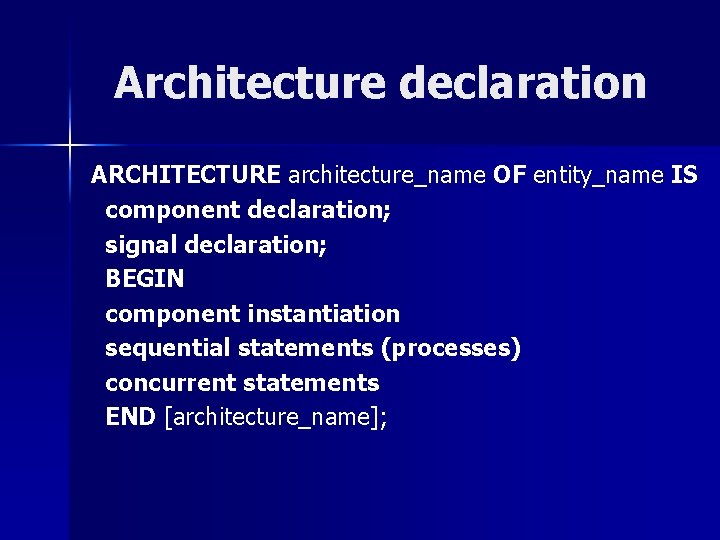

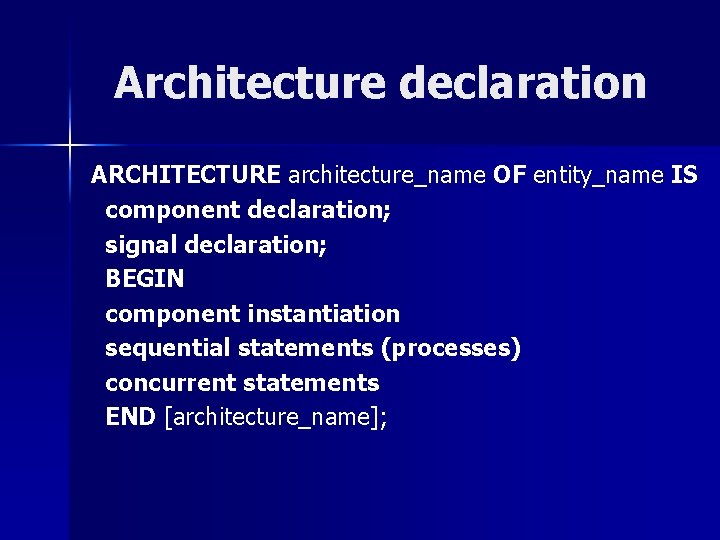

Architecture declaration ARCHITECTURE architecture_name OF entity_name IS component declaration; signal declaration; BEGIN component instantiation sequential statements (processes) concurrent statements END [architecture_name];

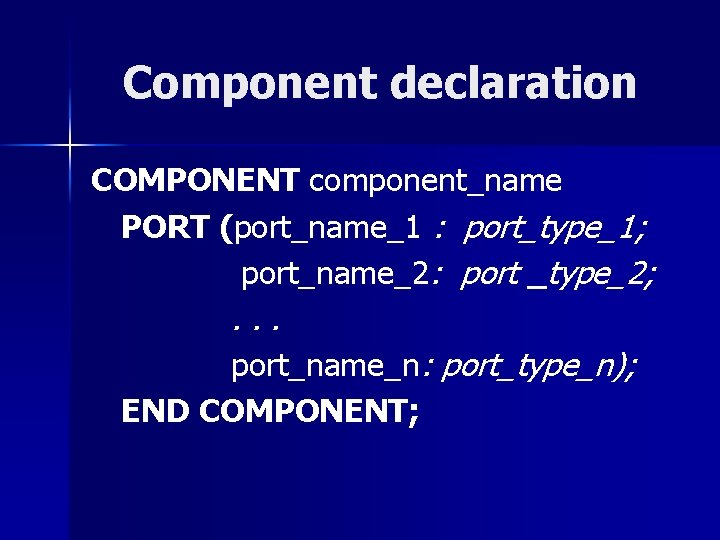

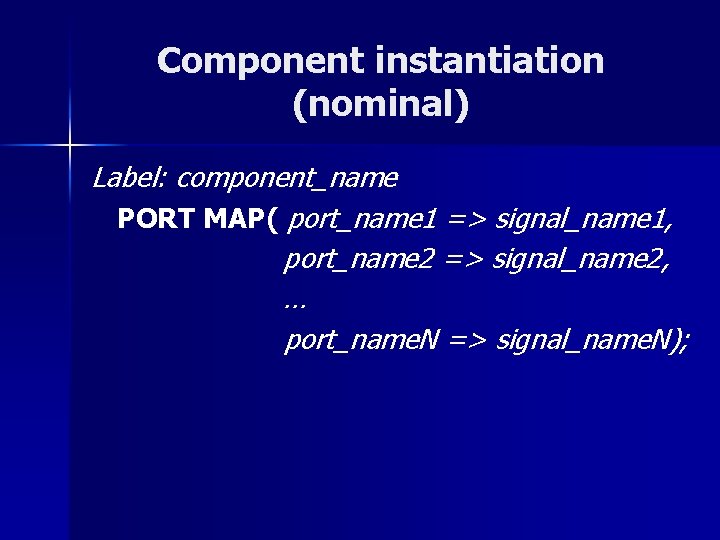

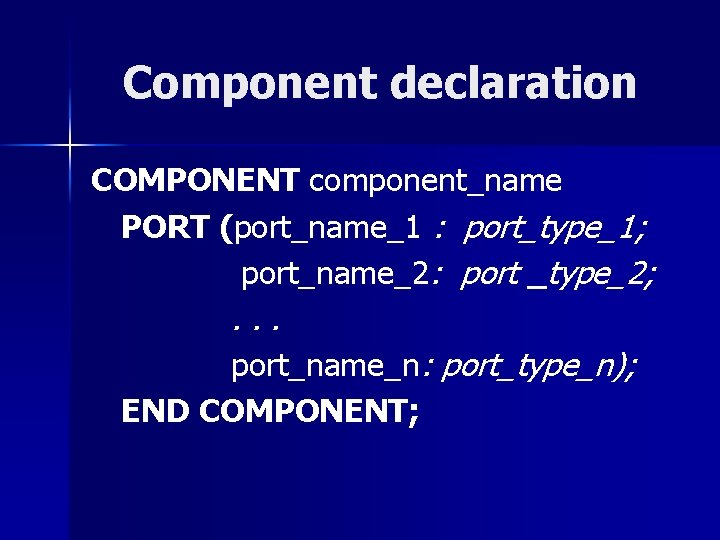

Component declaration COMPONENT component_name PORT (port_name_1 : port_type_1; port_name_2: port _type_2; . . . port_name_n: port_type_n); END COMPONENT;

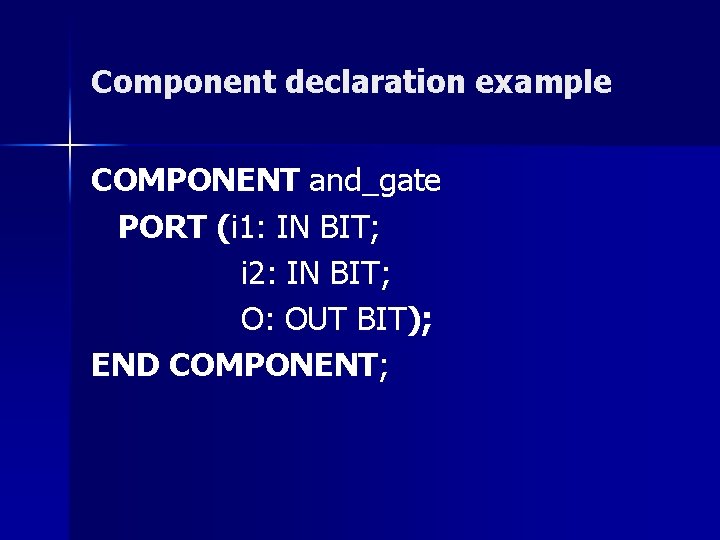

Component declaration example COMPONENT and_gate PORT (i 1: IN BIT; i 2: IN BIT; O: OUT BIT); END COMPONENT;

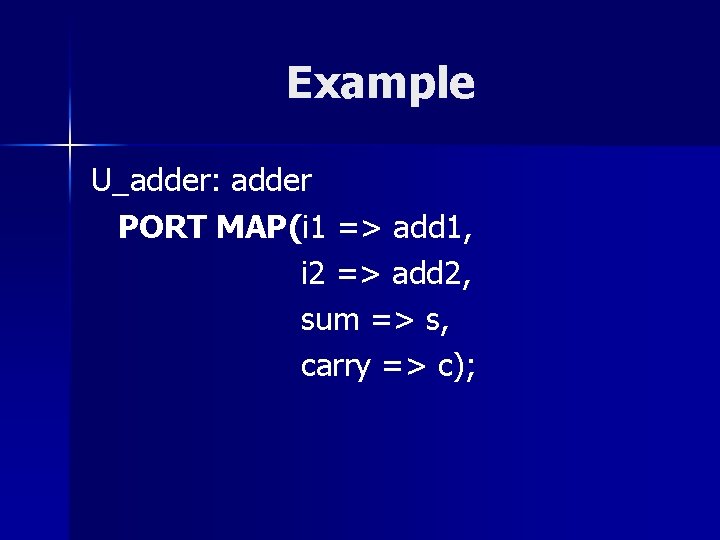

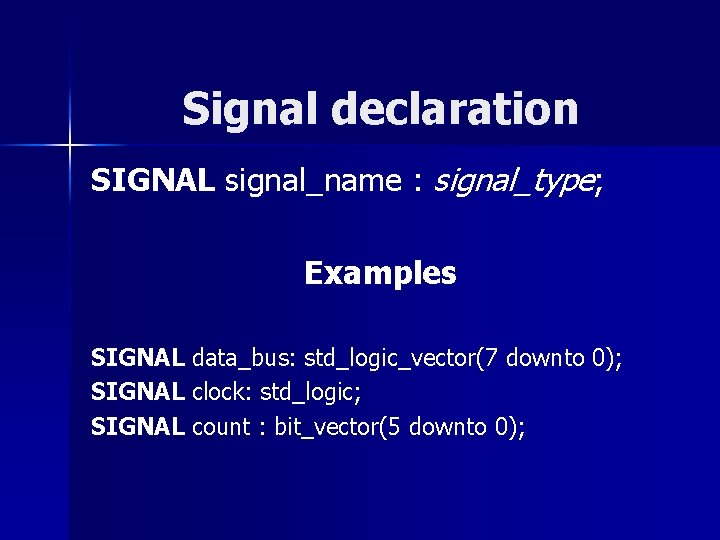

Signal declaration SIGNAL signal_name : signal_type; Examples SIGNAL data_bus: std_logic_vector(7 downto 0); SIGNAL clock: std_logic; SIGNAL count : bit_vector(5 downto 0);

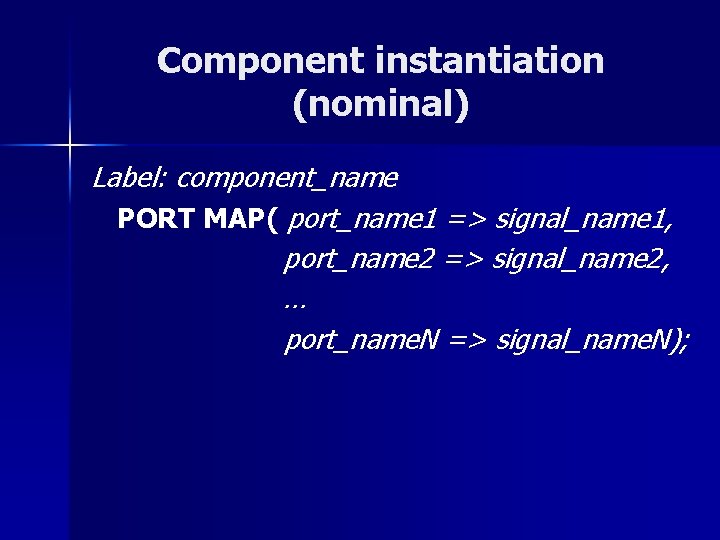

Component instantiation (nominal) Label: component_name PORT MAP( port_name 1 => signal_name 1, port_name 2 => signal_name 2, … port_name. N => signal_name. N);

Example U_adder: adder PORT MAP(i 1 => add 1, i 2 => add 2, sum => s, carry => c);

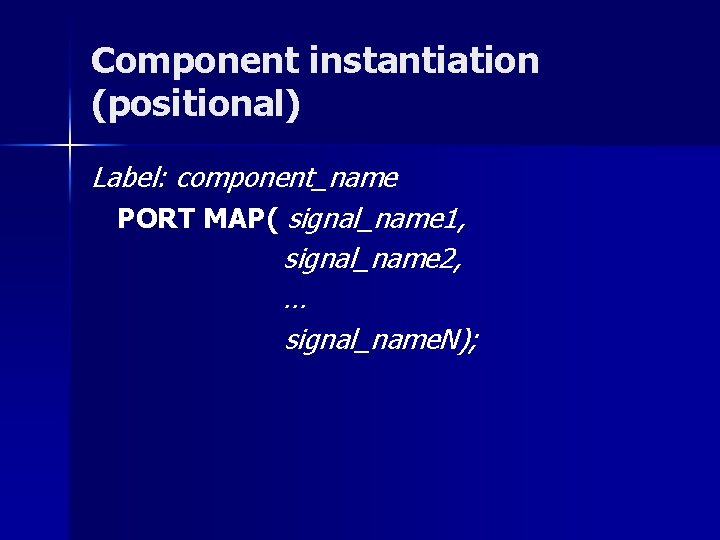

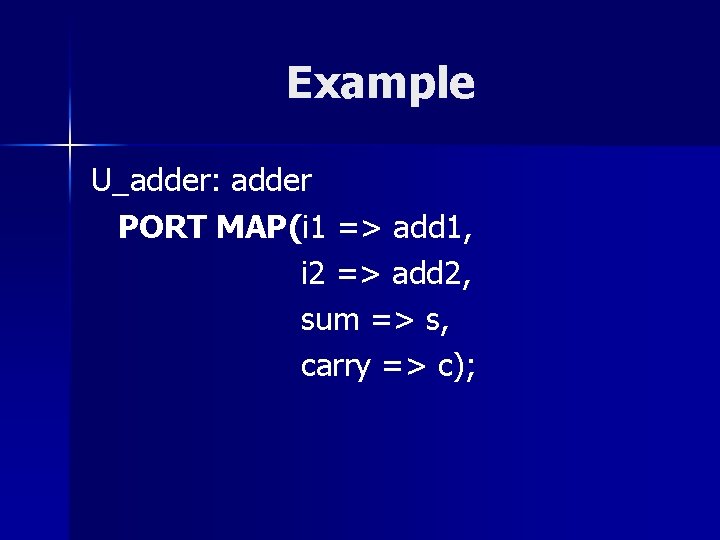

Component instantiation (positional) Label: component_name PORT MAP( signal_name 1, signal_name 2, … signal_name. N);

Example U_adder: adder PORT MAP(add 1, add 2, s, c);

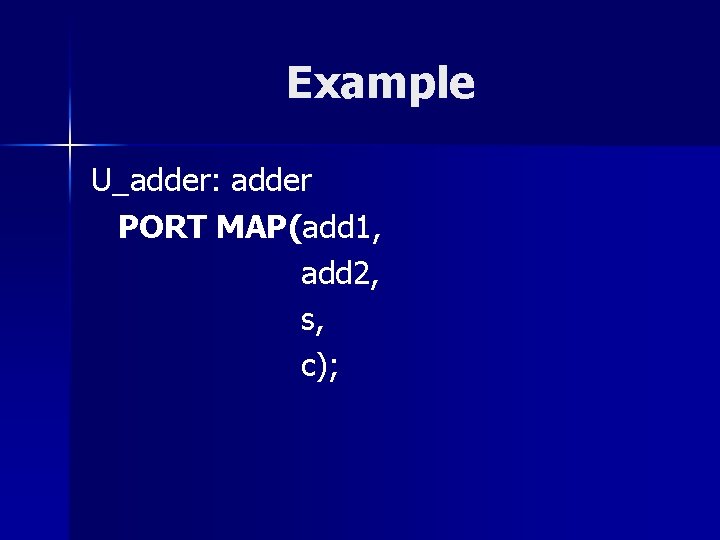

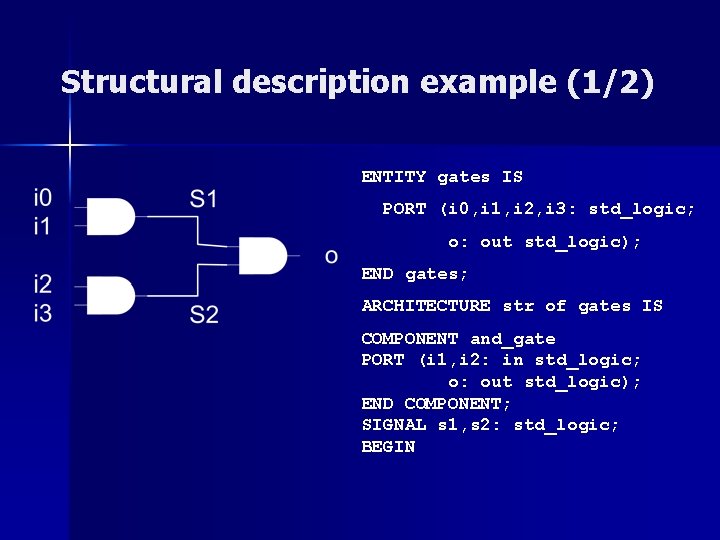

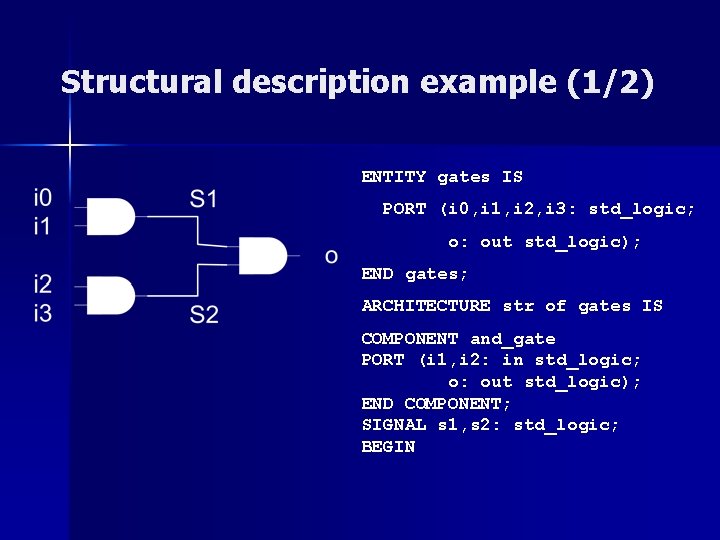

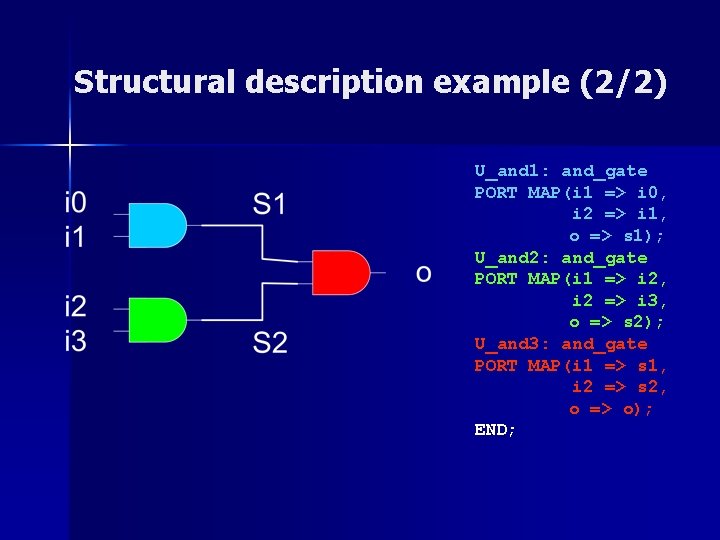

Structural description example (1/2) ENTITY gates IS PORT (i 0, i 1, i 2, i 3: std_logic; o: out std_logic); END gates; ARCHITECTURE str of gates IS COMPONENT and_gate PORT (i 1, i 2: in std_logic; o: out std_logic); END COMPONENT; SIGNAL s 1, s 2: std_logic; BEGIN

Structural description example (2/2) U_and 1: and_gate PORT MAP(i 1 => i 0, i 2 => i 1, o => s 1); U_and 2: and_gate PORT MAP(i 1 => i 2, i 2 => i 3, o => s 2); U_and 3: and_gate PORT MAP(i 1 => s 1, i 2 => s 2, o => o); END;

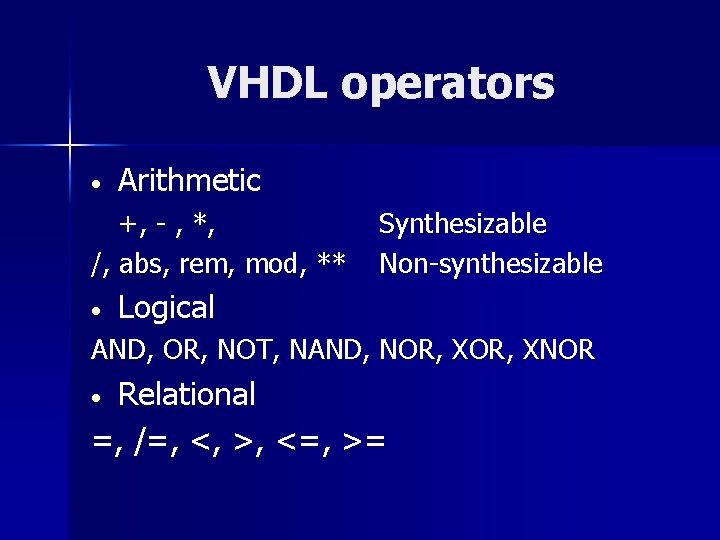

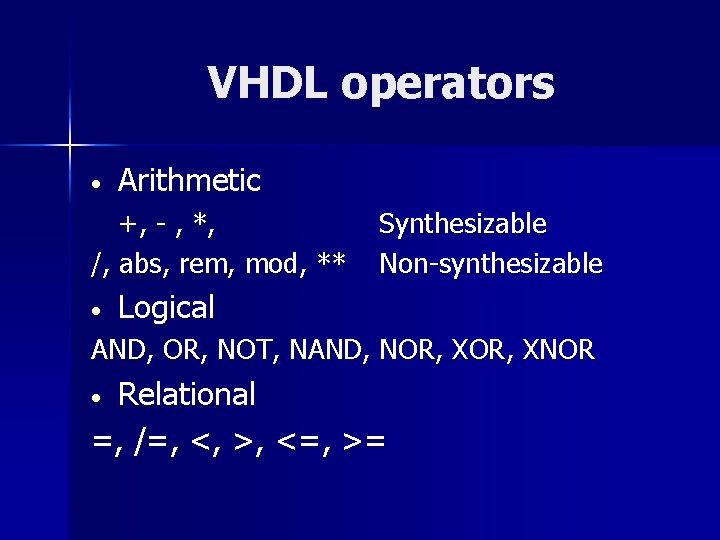

VHDL operators • Arithmetic +, - , *, /, abs, rem, mod, ** • Synthesizable Non-synthesizable Logical AND, OR, NOT, NAND, NOR, XNOR Relational =, /=, <, >, <=, >= •

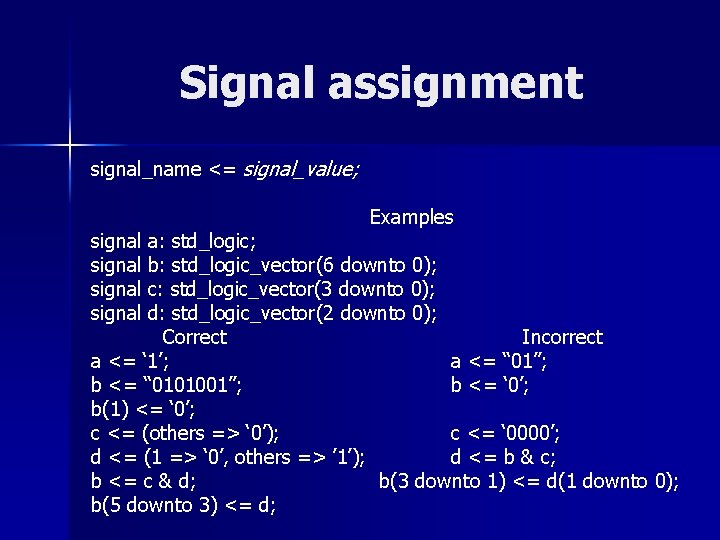

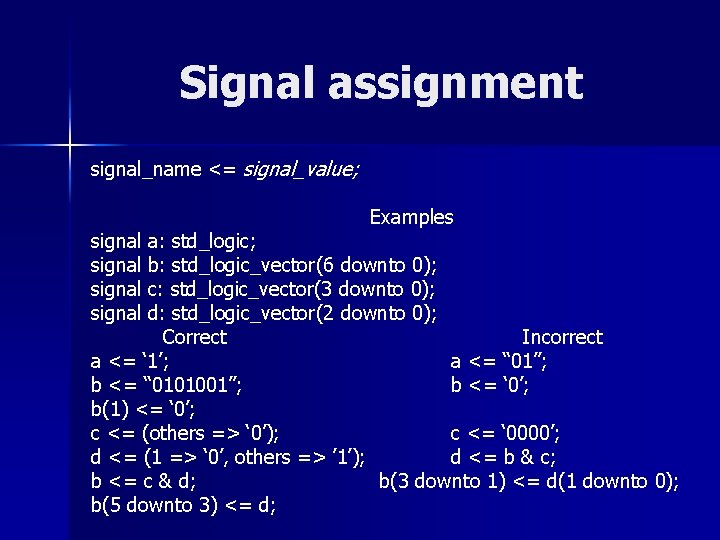

Signal assignment signal_name <= signal_value; Examples signal a: std_logic; signal b: std_logic_vector(6 downto 0); signal c: std_logic_vector(3 downto 0); signal d: std_logic_vector(2 downto 0); Correct Incorrect a <= ‘ 1’; a <= “ 01”; b <= “ 0101001”; b <= ‘ 0’; b(1) <= ‘ 0’; c <= (others => ‘ 0’); c <= ‘ 0000’; d <= (1 => ‘ 0’, others => ’ 1’); d <= b & c; b <= c & d; b(3 downto 1) <= d(1 downto 0); b(5 downto 3) <= d;

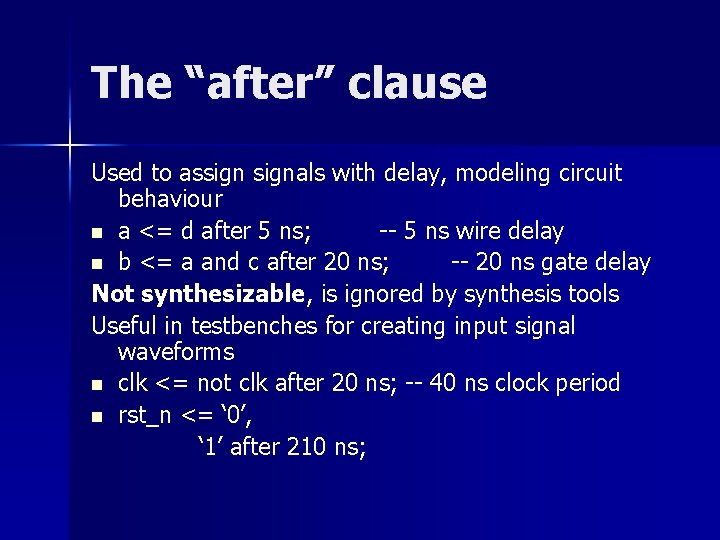

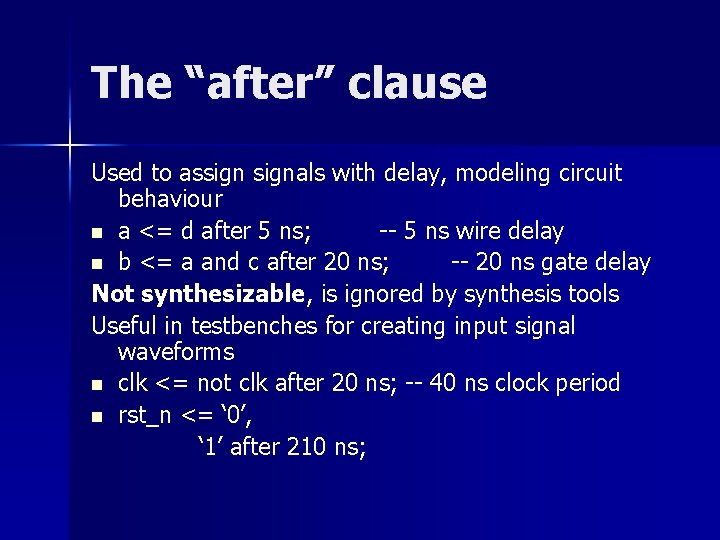

The “after” clause Used to assignals with delay, modeling circuit behaviour n a <= d after 5 ns; -- 5 ns wire delay n b <= a and c after 20 ns; -- 20 ns gate delay Not synthesizable, is ignored by synthesis tools Useful in testbenches for creating input signal waveforms n clk <= not clk after 20 ns; -- 40 ns clock period n rst_n <= ‘ 0’, ‘ 1’ after 210 ns;

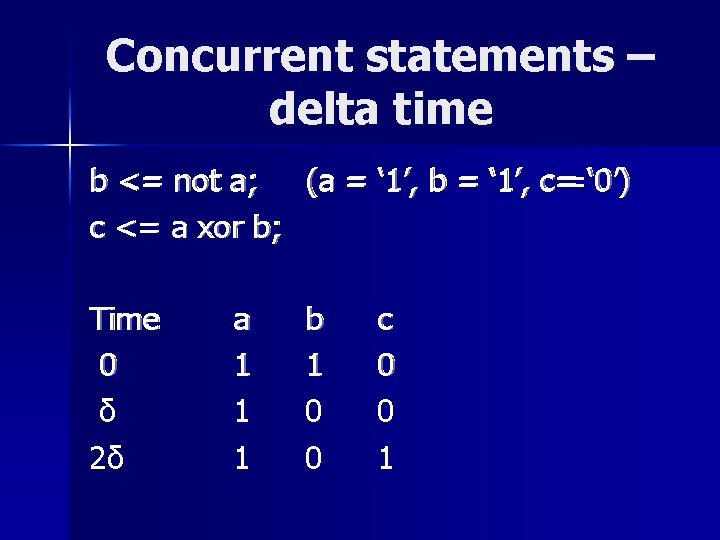

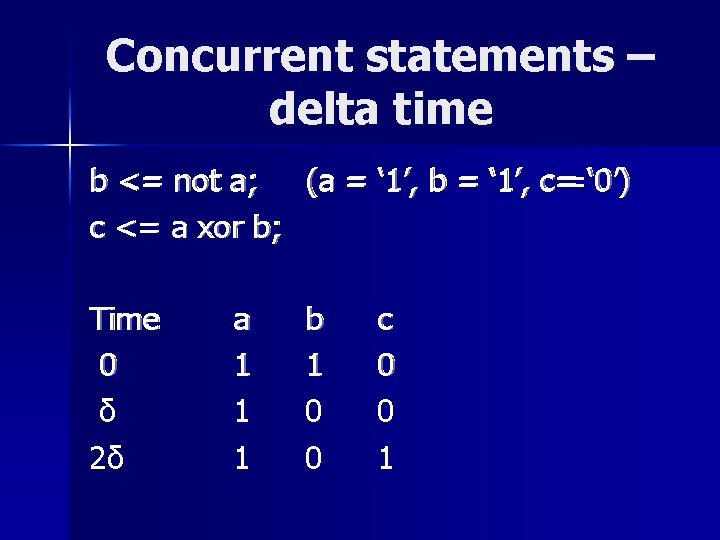

Concurrent statements – delta time b <= not a; (a = ‘ 1’, b = ‘ 1’, cc==‘ 0’) cc <= <= aa xor b; b; Time 0 δ 2δ aa 1 1 1 bb 1 0 0 cc 0 0 1

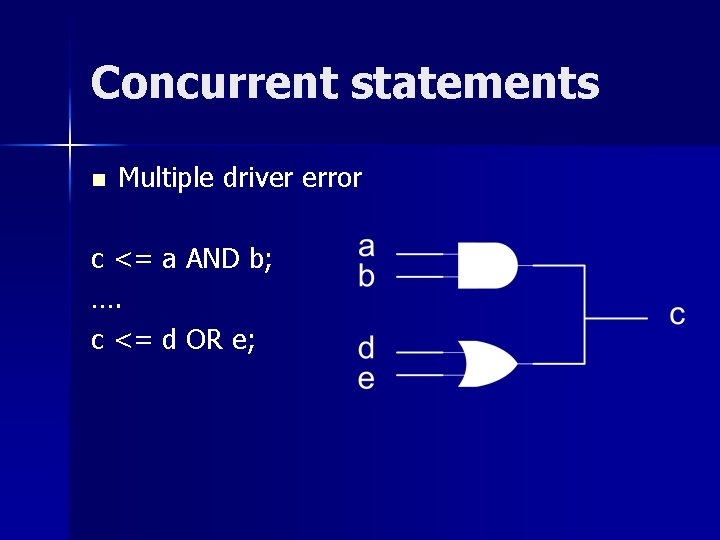

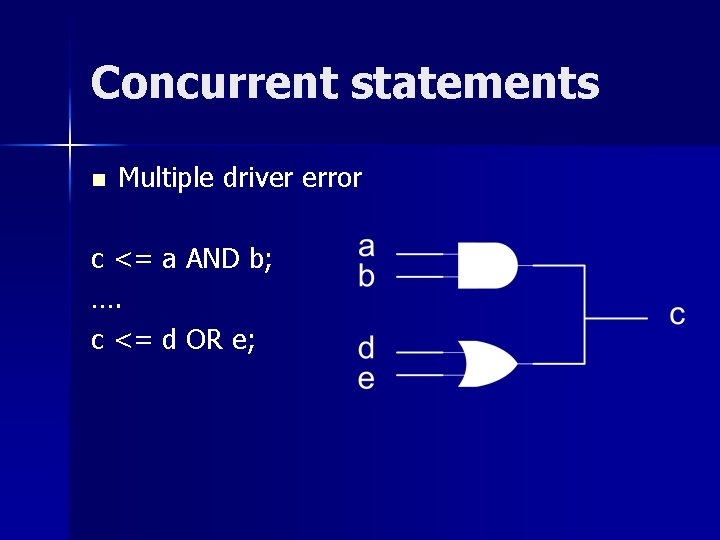

Concurrent statements n Multiple driver error c <= a AND b; …. c <= d OR e;

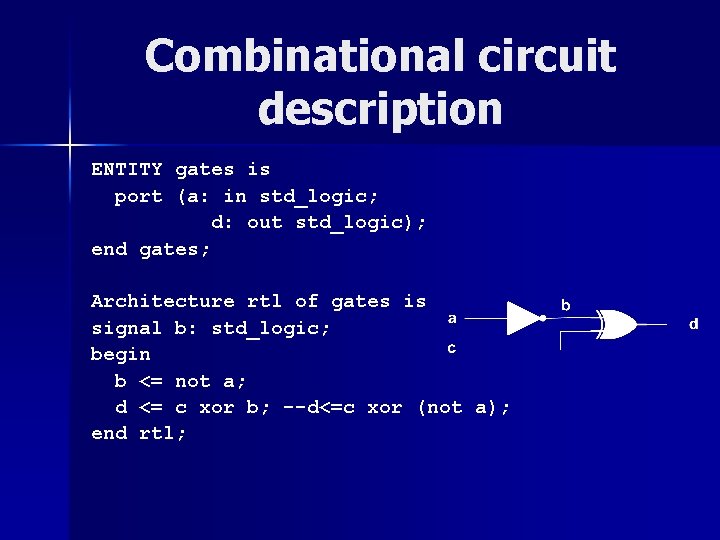

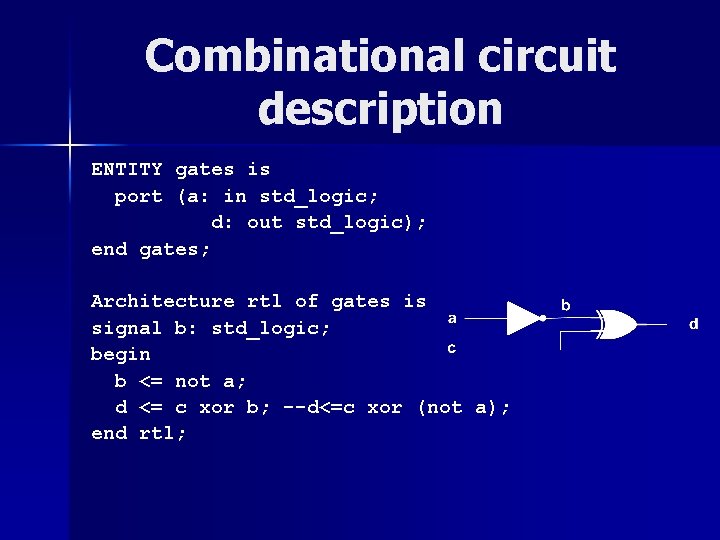

Combinational circuit description ENTITY gates is port (a: in std_logic; d: out std_logic); end gates; Architecture rtl of gates is signal b: std_logic; begin b <= not a; d <= c xor b; --d<=c xor (not a); end rtl;

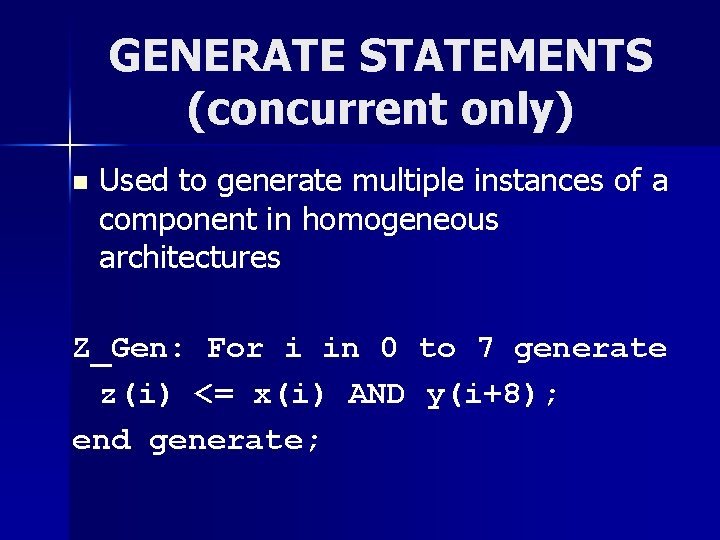

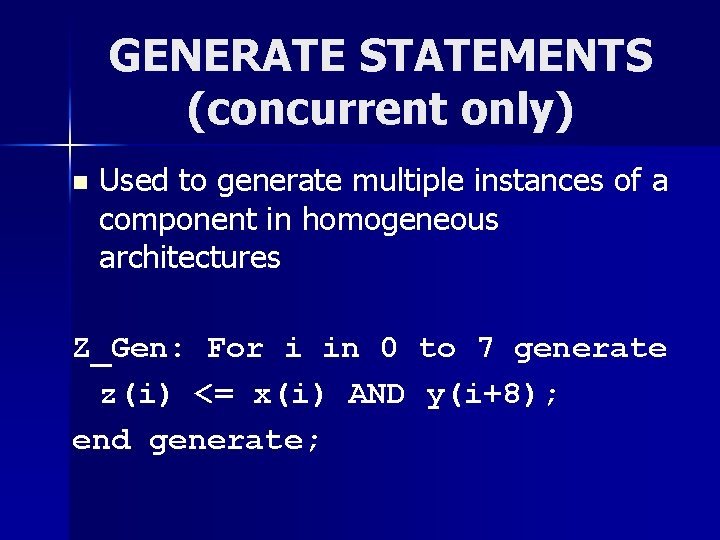

GENERATE STATEMENTS (concurrent only) n Used to generate multiple instances of a component in homogeneous architectures Z_Gen: For i in 0 to 7 generate z(i) <= x(i) AND y(i+8); end generate;

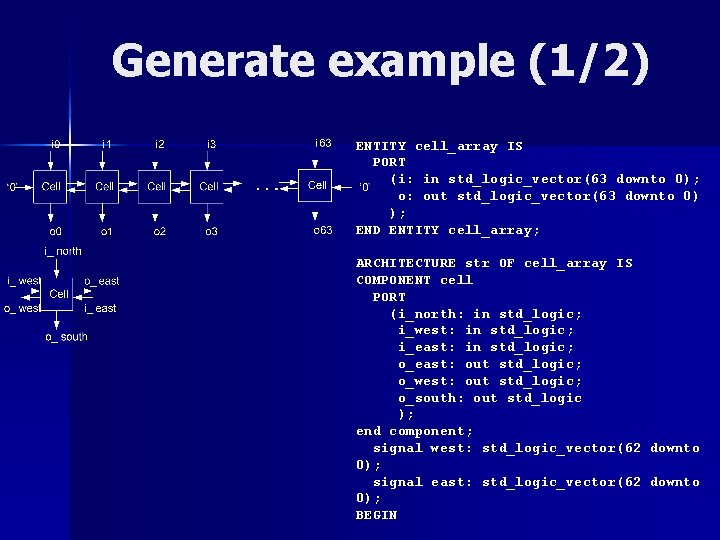

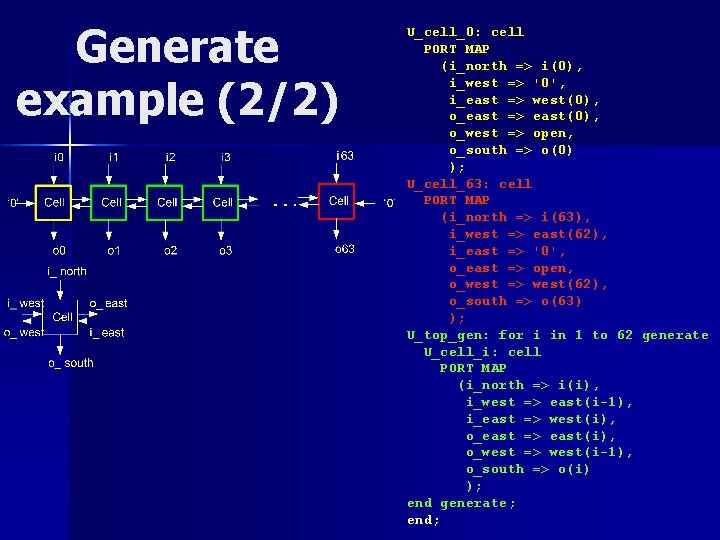

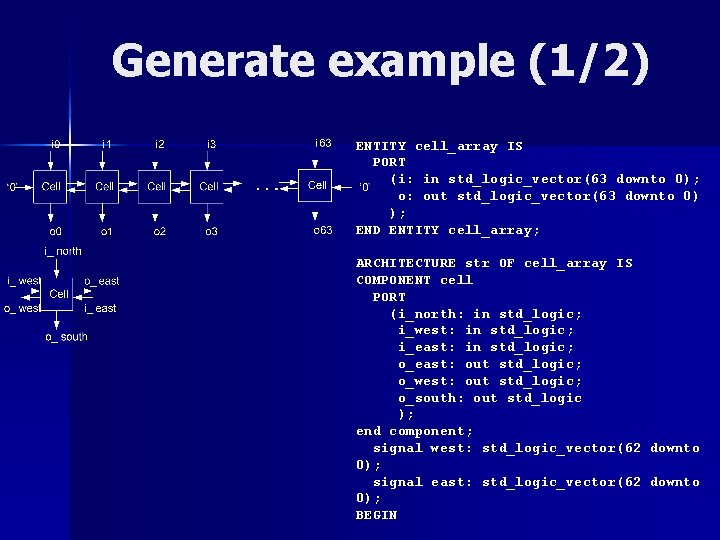

Generate example (1/2) ENTITY cell_array IS PORT (i: in std_logic_vector(63 downto 0); o: out std_logic_vector(63 downto 0) ); END ENTITY cell_array; ARCHITECTURE str OF cell_array IS COMPONENT cell PORT (i_north: in std_logic; i_west: in std_logic; i_east: in std_logic; o_east: out std_logic; o_west: out std_logic; o_south: out std_logic ); end component; signal west: std_logic_vector(62 downto 0); signal east: std_logic_vector(62 downto 0); BEGIN

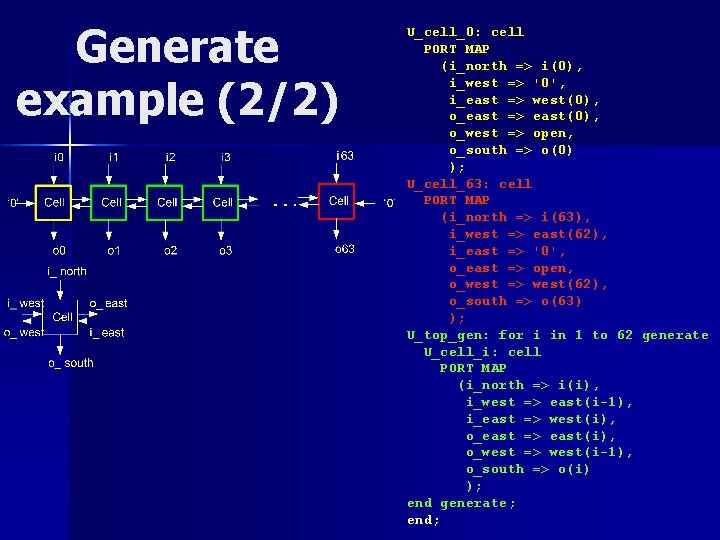

Generate example (2/2) U_cell_0: cell PORT MAP (i_north => i(0), i_west => '0', i_east => west(0), o_east => east(0), o_west => open, o_south => o(0) ); U_cell_63: cell PORT MAP (i_north => i(63), i_west => east(62), i_east => '0', o_east => open, o_west => west(62), o_south => o(63) ); U_top_gen: for i in 1 to 62 generate U_cell_i: cell PORT MAP (i_north => i(i), i_west => east(i-1), i_east => west(i), o_east => east(i), o_west => west(i-1), o_south => o(i) ); end generate; end;

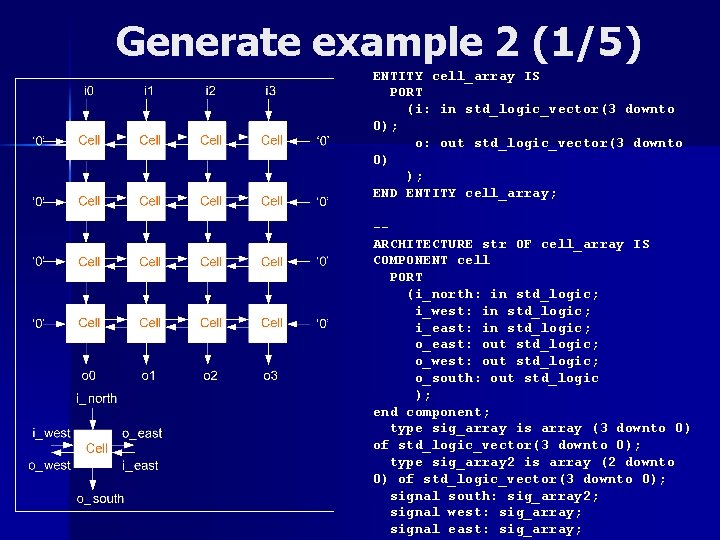

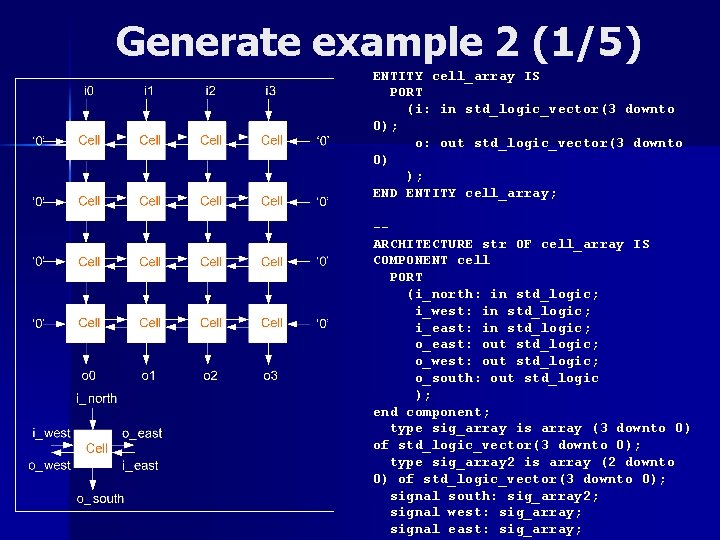

Generate example 2 (1/5) ENTITY cell_array IS PORT (i: in std_logic_vector(3 downto 0); o: out std_logic_vector(3 downto 0) ); END ENTITY cell_array; -ARCHITECTURE str OF cell_array IS COMPONENT cell PORT (i_north: in std_logic; i_west: in std_logic; i_east: in std_logic; o_east: out std_logic; o_west: out std_logic; o_south: out std_logic ); end component; type sig_array is array (3 downto 0) of std_logic_vector(3 downto 0); type sig_array 2 is array (2 downto 0) of std_logic_vector(3 downto 0); signal south: sig_array 2; signal west: sig_array; signal east: sig_array;

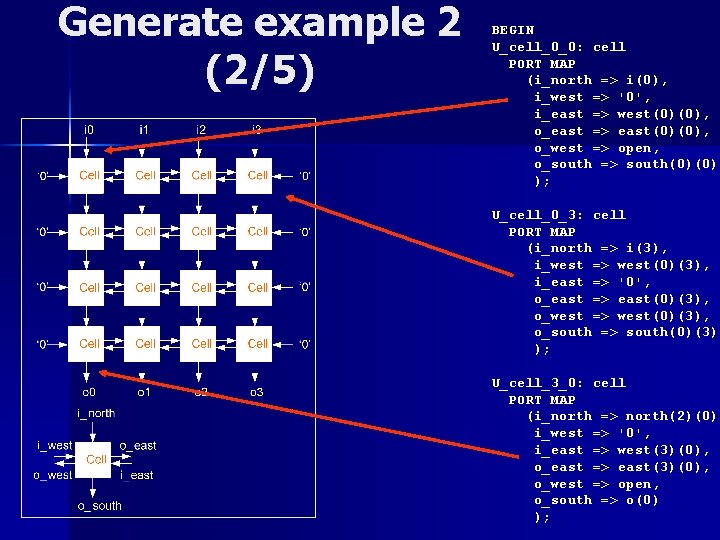

Generate example 2 (2/5) BEGIN U_cell_0_0: cell PORT MAP (i_north => i(0), i_west => '0', i_east => west(0)(0), o_east => east(0)(0), o_west => open, o_south => south(0)(0) ); U_cell_0_3: cell PORT MAP (i_north => i(3), i_west => west(0)(3), i_east => '0', o_east => east(0)(3), o_west => west(0)(3), o_south => south(0)(3) ); U_cell_3_0: cell PORT MAP (i_north => north(2)(0), i_west => '0', i_east => west(3)(0), o_east => east(3)(0), o_west => open, o_south => o(0) );

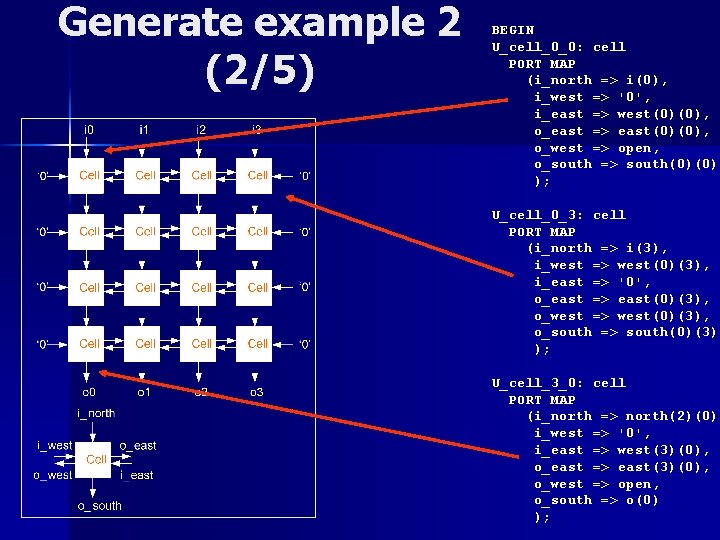

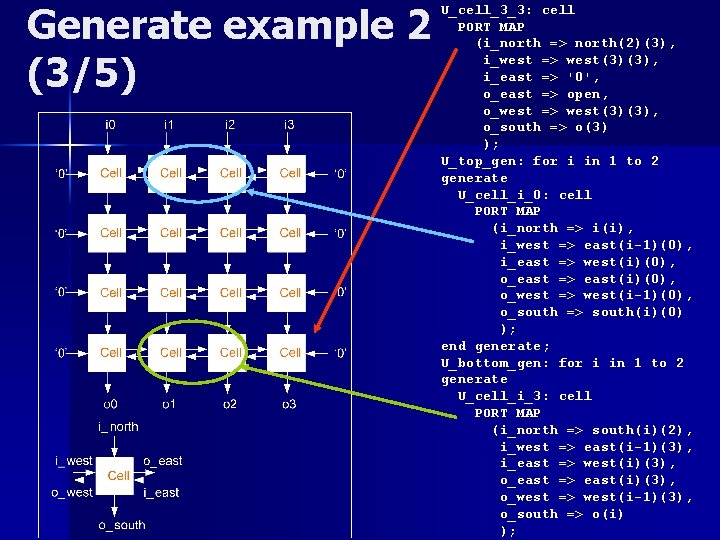

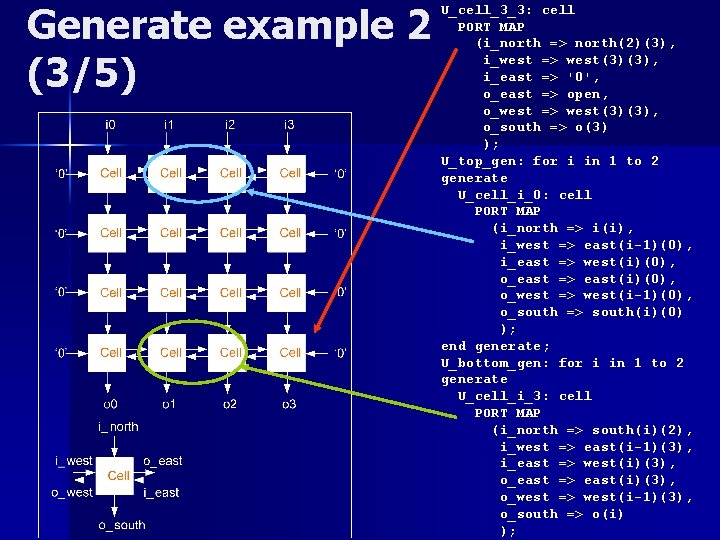

Generate example 2 (3/5) U_cell_3_3: cell PORT MAP (i_north => north(2)(3), i_west => west(3)(3), i_east => '0', o_east => open, o_west => west(3)(3), o_south => o(3) ); U_top_gen: for i in 1 to 2 generate U_cell_i_0: cell PORT MAP (i_north => i(i), i_west => east(i-1)(0), i_east => west(i)(0), o_east => east(i)(0), o_west => west(i-1)(0), o_south => south(i)(0) ); end generate; U_bottom_gen: for i in 1 to 2 generate U_cell_i_3: cell PORT MAP (i_north => south(i)(2), i_west => east(i-1)(3), i_east => west(i)(3), o_east => east(i)(3), o_west => west(i-1)(3), o_south => o(i) );

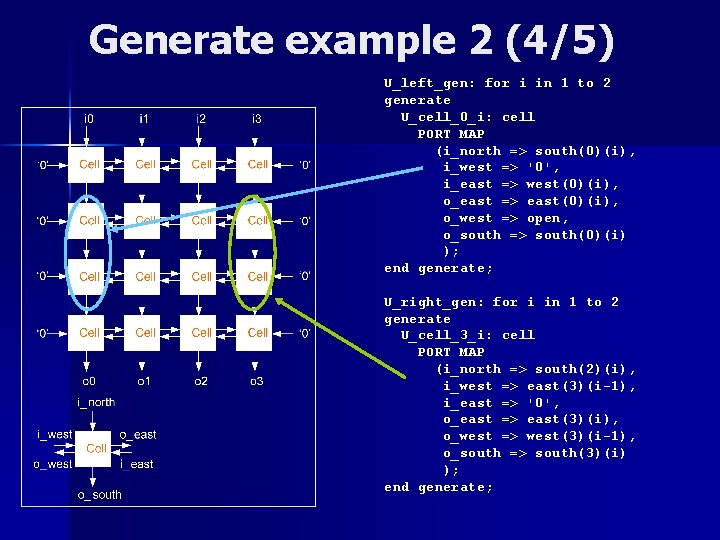

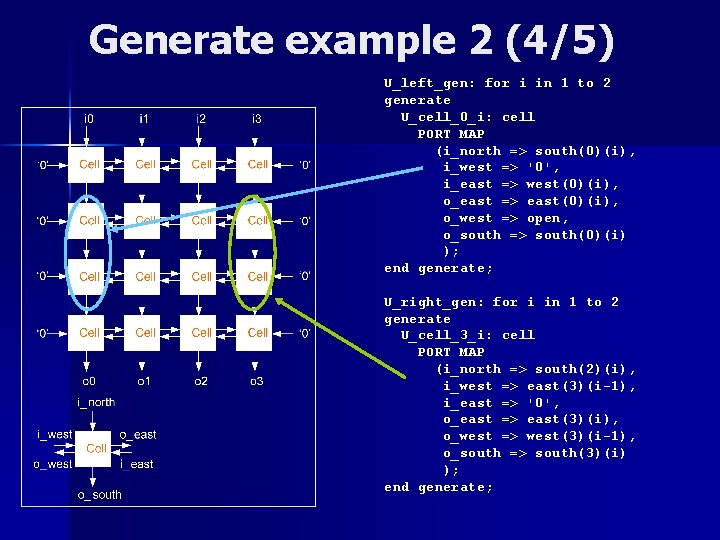

Generate example 2 (4/5) U_left_gen: for i in 1 to 2 generate U_cell_0_i: cell PORT MAP (i_north => south(0)(i), i_west => '0', i_east => west(0)(i), o_east => east(0)(i), o_west => open, o_south => south(0)(i) ); end generate; U_right_gen: for i in 1 to 2 generate U_cell_3_i: cell PORT MAP (i_north => south(2)(i), i_west => east(3)(i-1), i_east => '0', o_east => east(3)(i), o_west => west(3)(i-1), o_south => south(3)(i) ); end generate;

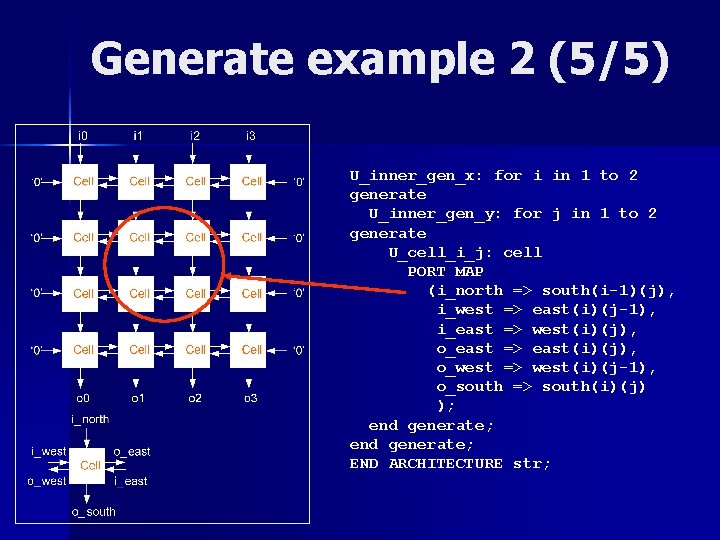

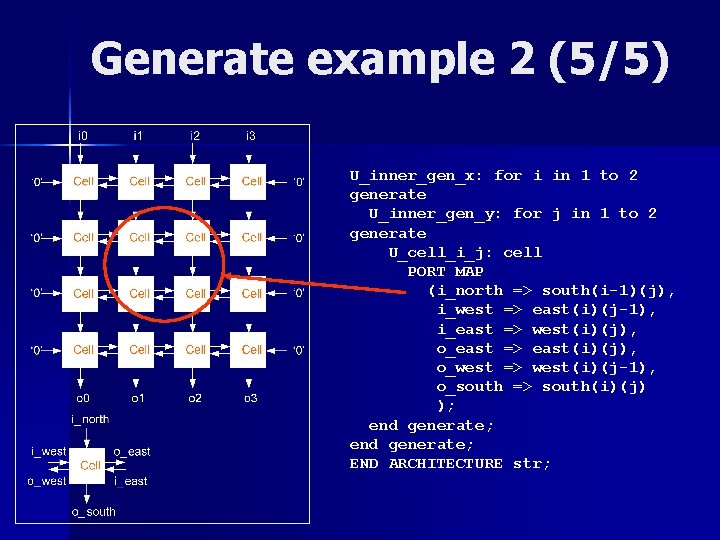

Generate example 2 (5/5) U_inner_gen_x: for i in 1 to 2 generate U_inner_gen_y: for j in 1 to 2 generate U_cell_i_j: cell PORT MAP (i_north => south(i-1)(j), i_west => east(i)(j-1), i_east => west(i)(j), o_east => east(i)(j), o_west => west(i)(j-1), o_south => south(i)(j) ); end generate; END ARCHITECTURE str;

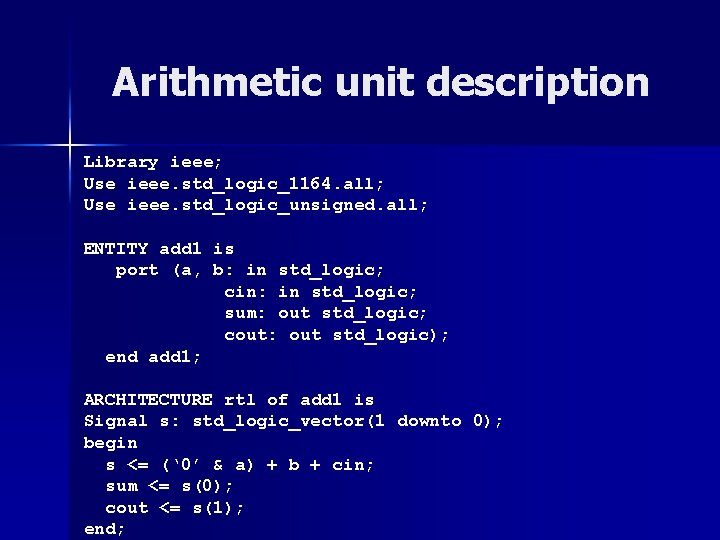

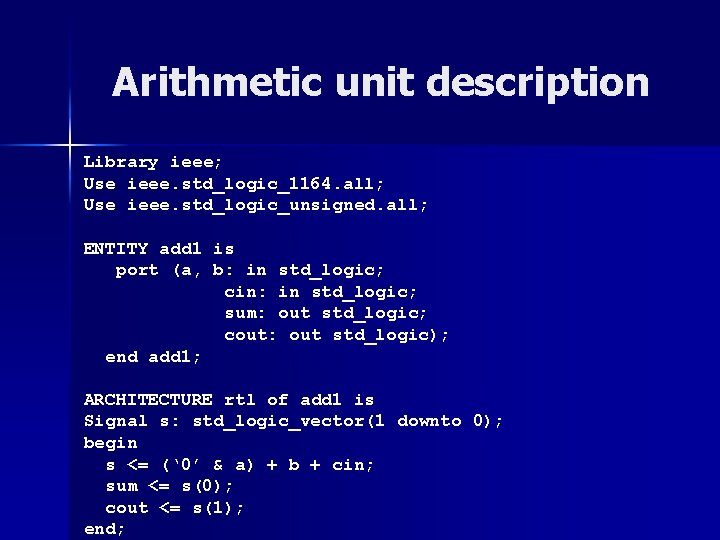

Arithmetic unit description Library ieee; Use ieee. std_logic_1164. all; Use ieee. std_logic_unsigned. all; ENTITY add 1 is port (a, b: in std_logic; cin: in std_logic; sum: out std_logic; cout: out std_logic); end add 1; ARCHITECTURE rtl of add 1 is Signal s: std_logic_vector(1 downto 0); begin s <= (‘ 0’ & a) + b + cin; sum <= s(0); cout <= s(1); end;

Example Describe a 5 -bit multiplier in VHDL.

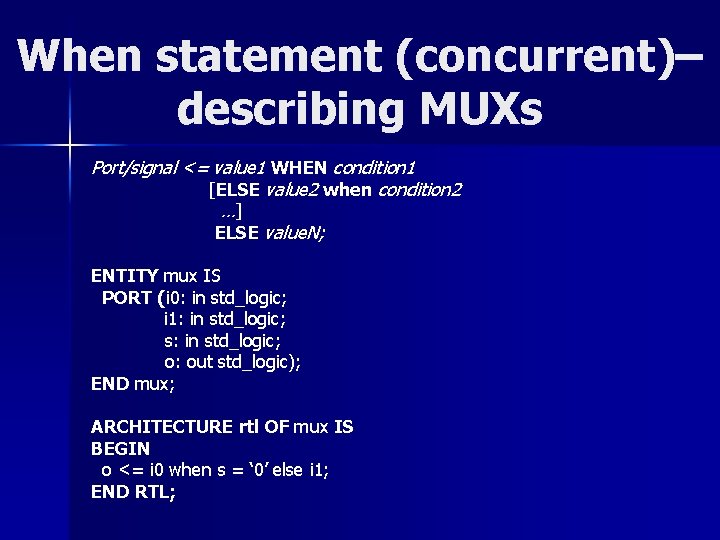

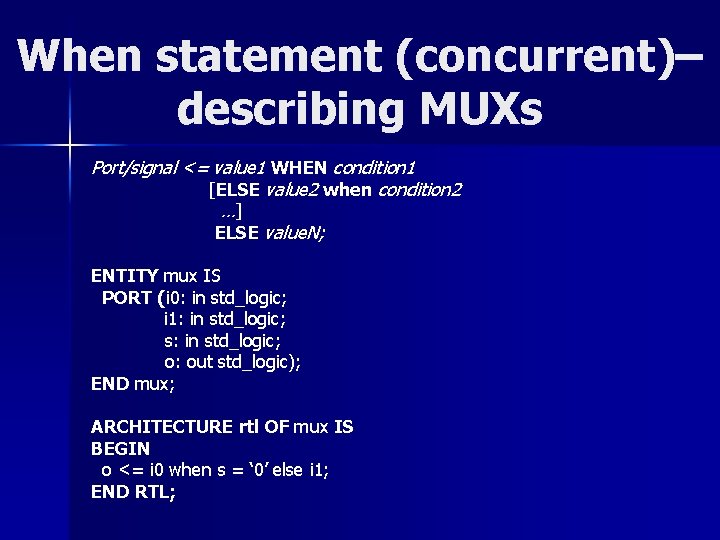

When statement (concurrent)– describing MUXs Port/signal <= value 1 WHEN condition 1 [ELSE value 2 when condition 2 …] ELSE value. N; ENTITY mux IS PORT (i 0: in std_logic; i 1: in std_logic; s: in std_logic; o: out std_logic); END mux; ARCHITECTURE rtl OF mux IS BEGIN o <= i 0 when s = ‘ 0’ else i 1; END RTL;

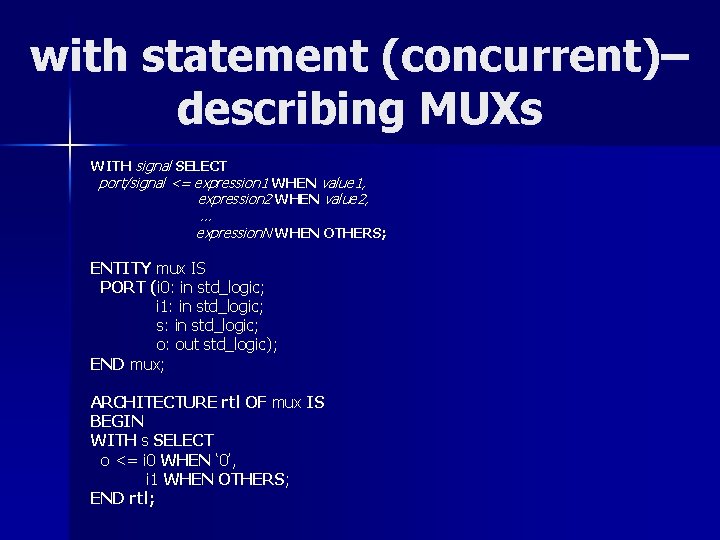

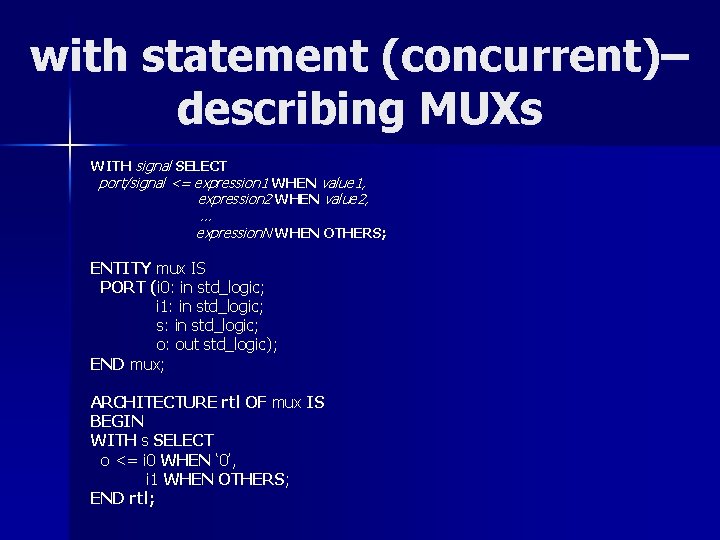

with statement (concurrent)– describing MUXs WITH signal SELECT port/signal <= expression 1 WHEN value 1, expression 2 WHEN value 2, … expression. N WHEN OTHERS; ENTITY mux IS PORT (i 0: in std_logic; i 1: in std_logic; s: in std_logic; o: out std_logic); END mux; ARCHITECTURE rtl OF mux IS BEGIN WITH s SELECT o <= i 0 WHEN ‘ 0’, i 1 WHEN OTHERS; END rtl;

![Sequential statements 1 process processname PROCESS sensitivity list BEGIN sequential statements END PROCESS Sequential statements (1) process [process_name: ] PROCESS (sensitivity list) BEGIN sequential statements END PROCESS](https://slidetodoc.com/presentation_image_h/2e63da5b23a2767091cced57da40cfb8/image-39.jpg)

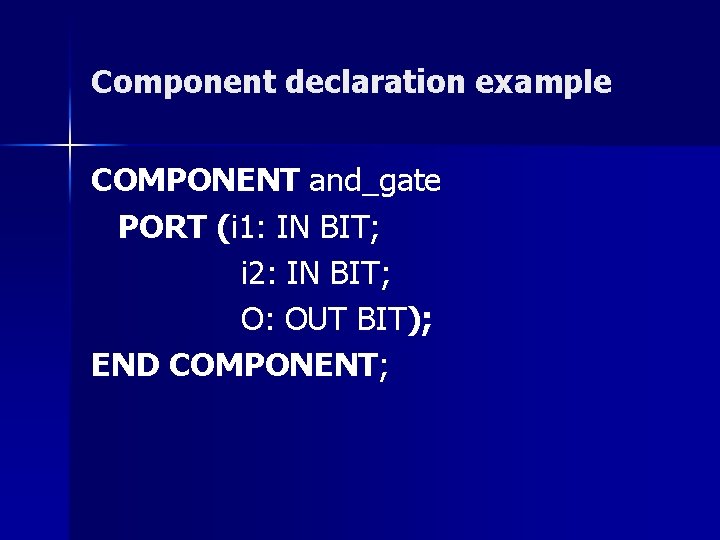

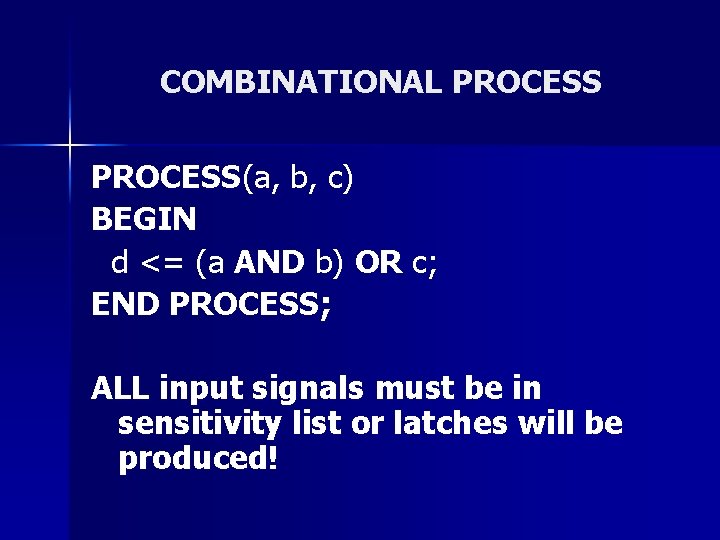

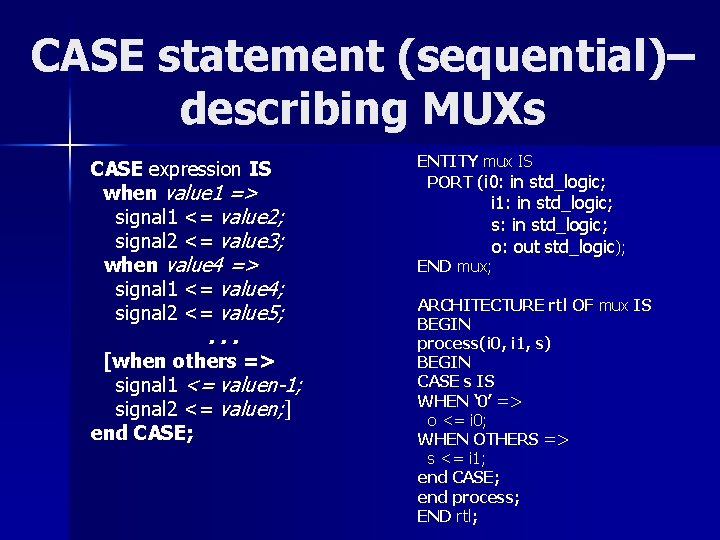

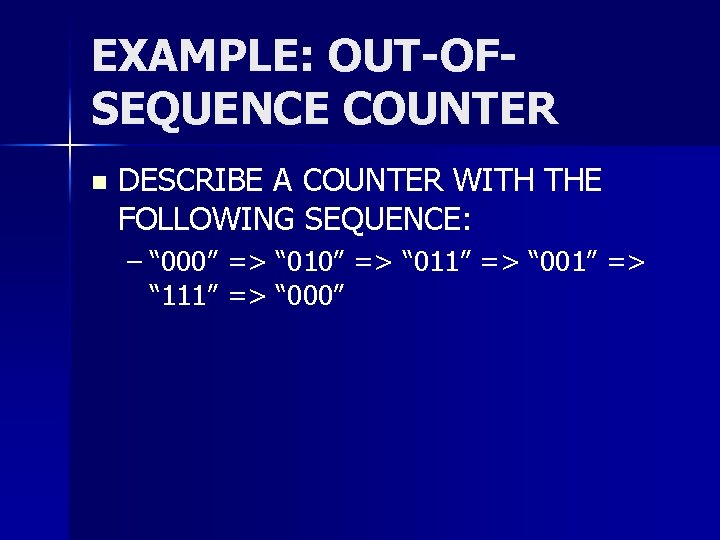

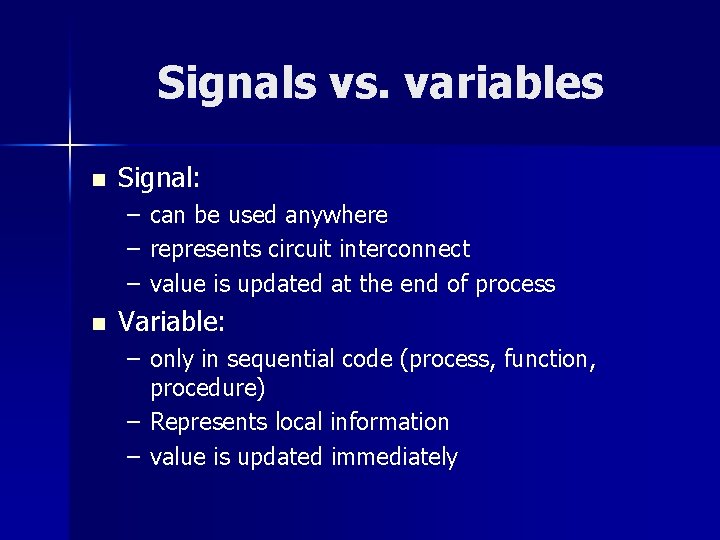

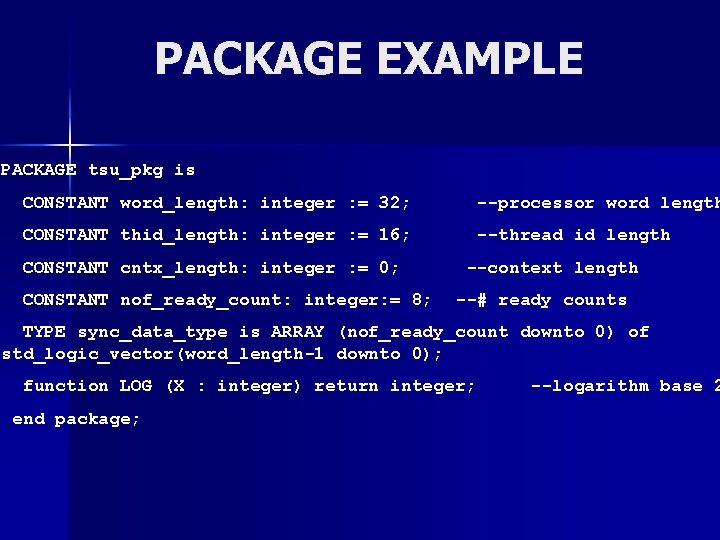

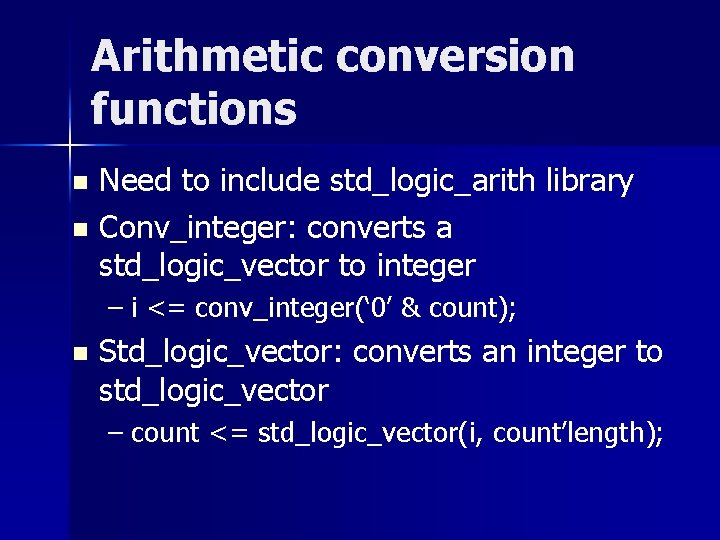

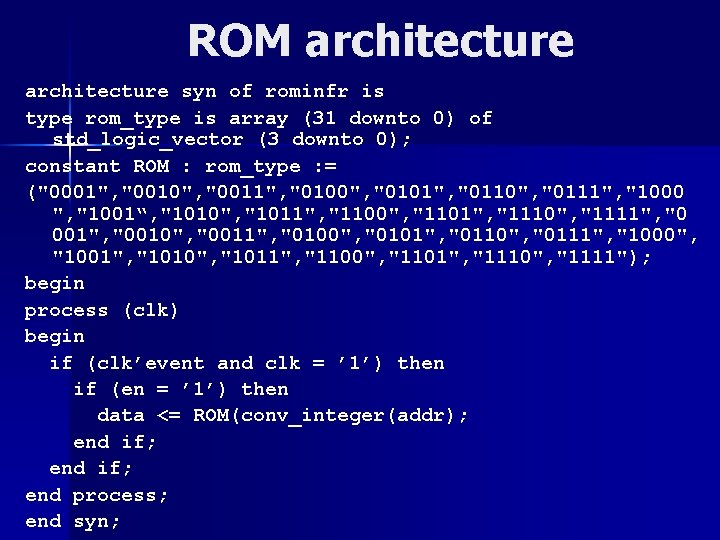

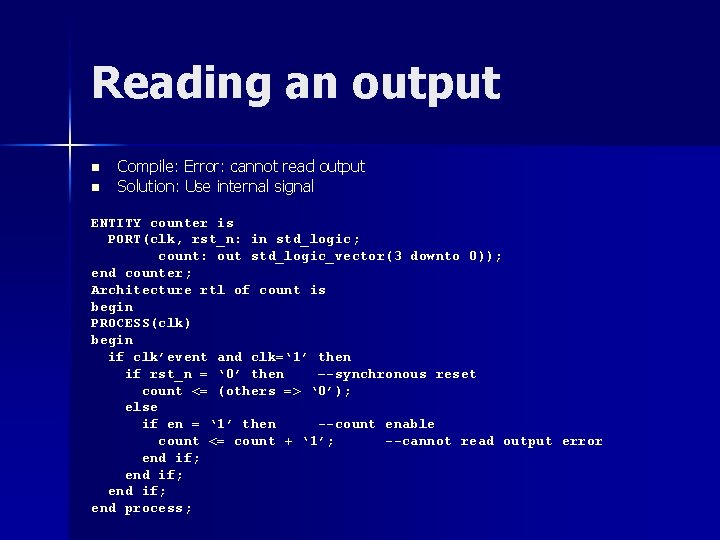

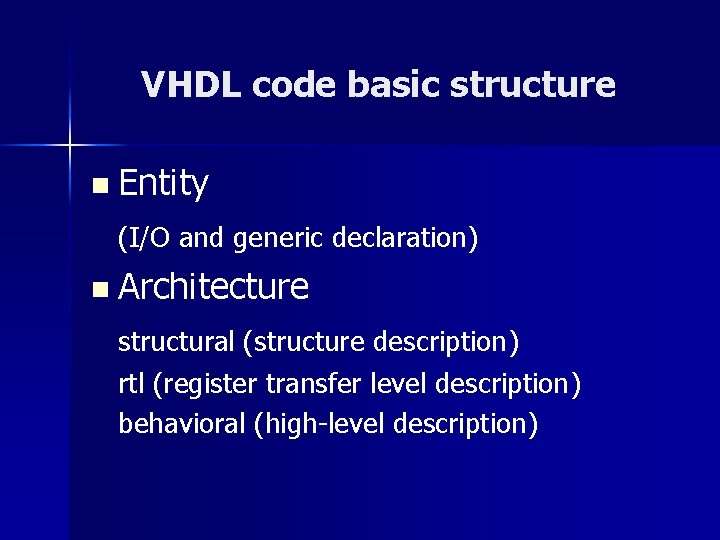

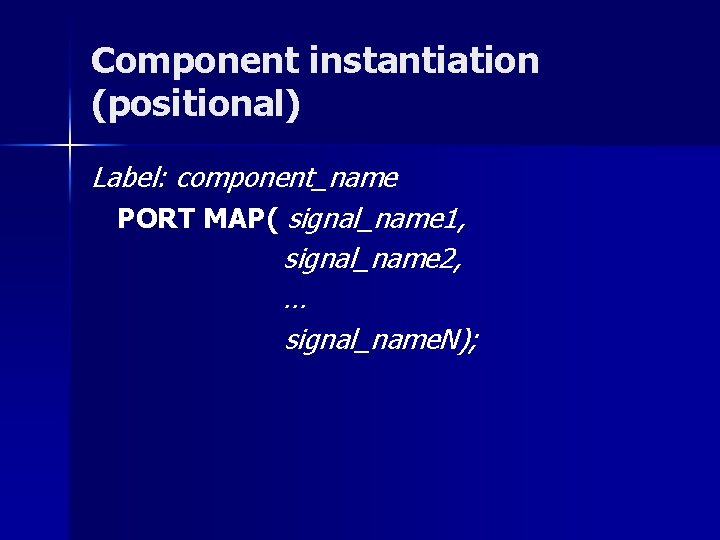

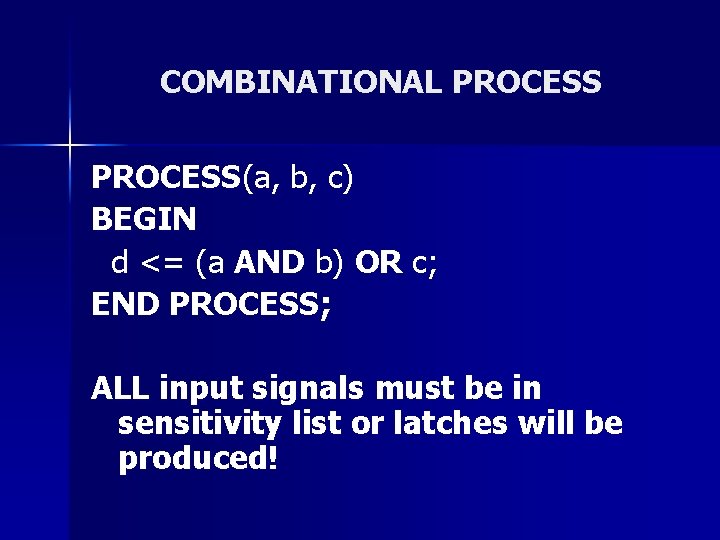

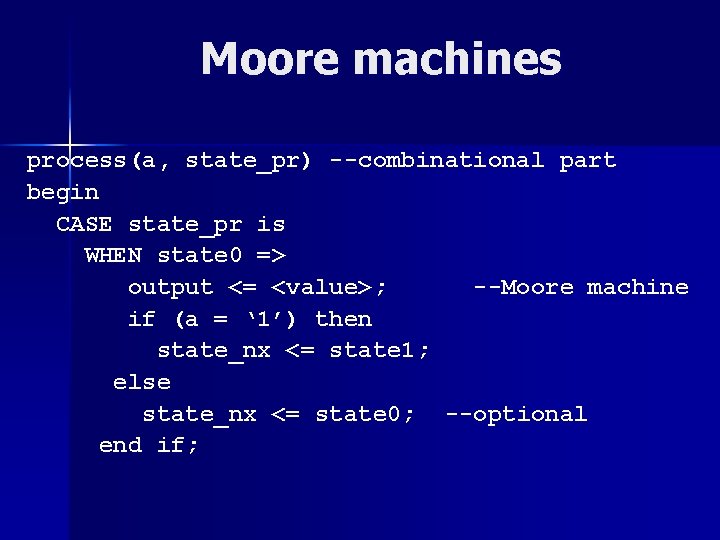

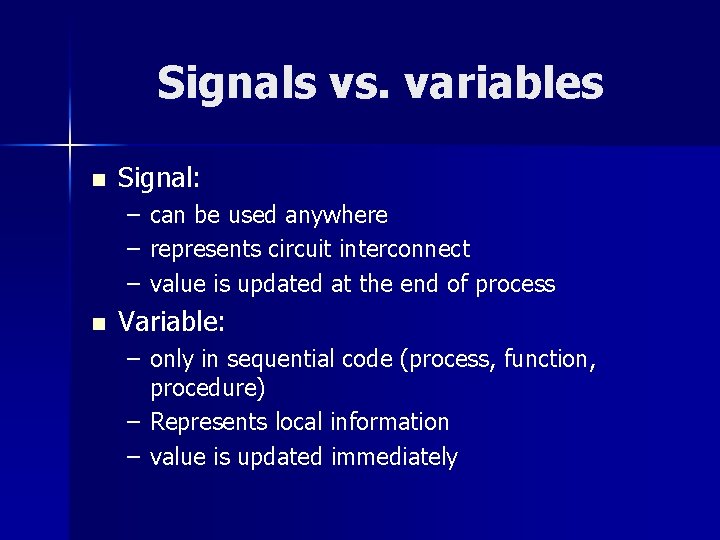

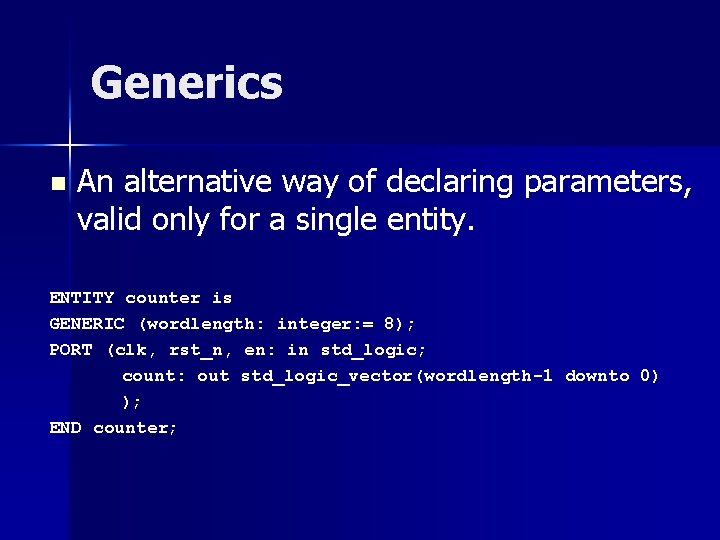

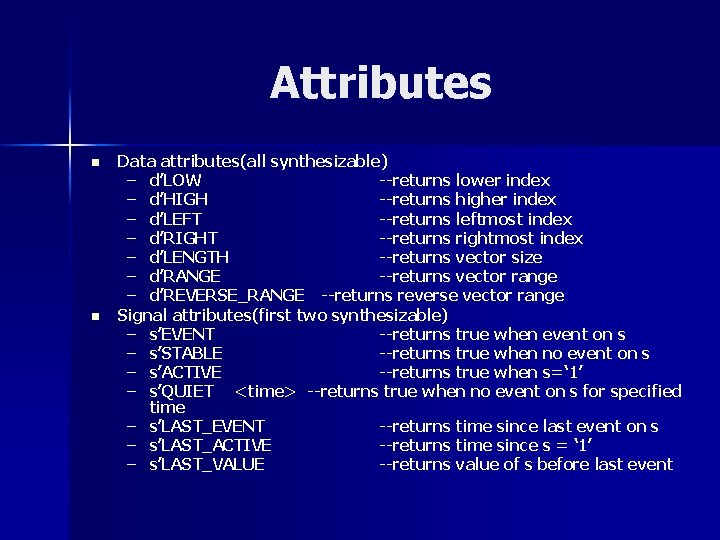

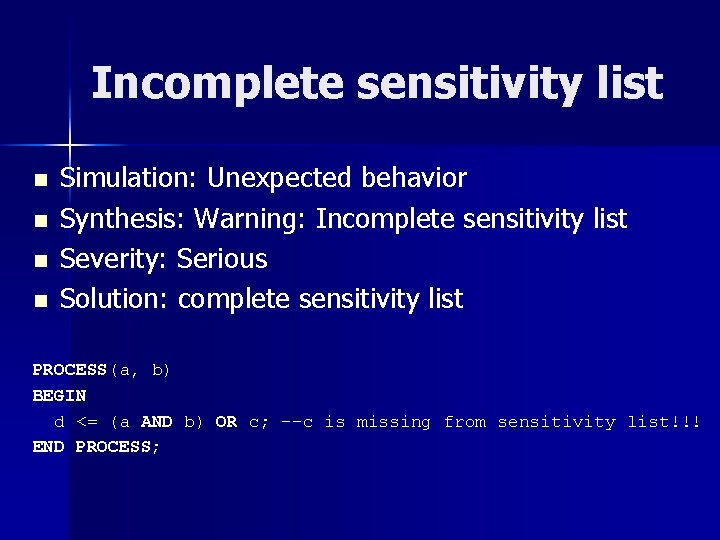

Sequential statements (1) process [process_name: ] PROCESS (sensitivity list) BEGIN sequential statements END PROCESS [process_name];

COMBINATIONAL PROCESS(a, b, c) BEGIN d <= (a AND b) OR c; END PROCESS; ALL input signals must be in sensitivity list or latches will be produced!

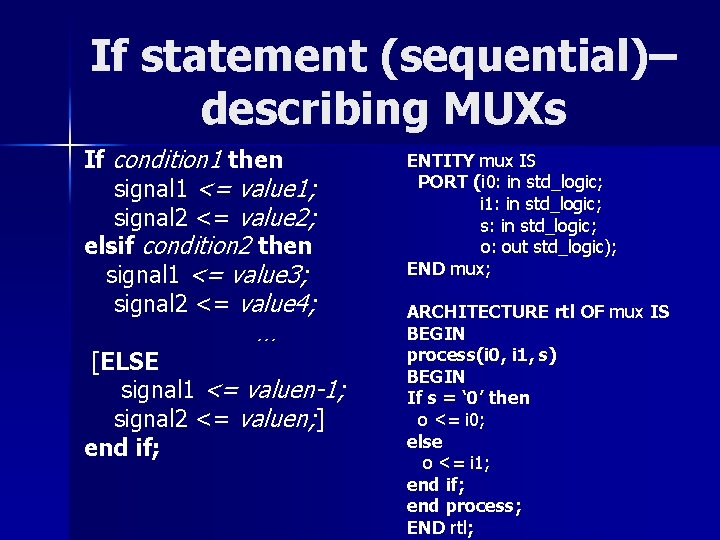

If statement (sequential)– describing MUXs If condition 1 then signal 1 <= value 1; signal 2 <= value 2; elsif condition 2 then signal 1 <= value 3; signal 2 <= value 4; … [ELSE signal 1 <= valuen-1; signal 2 <= valuen; ] end if; ENTITY mux IS PORT (i 0: in std_logic; i 1: in std_logic; s: in std_logic; o: out std_logic); END mux; ARCHITECTURE rtl OF mux IS BEGIN process(i 0, i 1, s) BEGIN If s = ‘ 0’ then o <= i 0; else o <= i 1; end if; end process; END rtl;

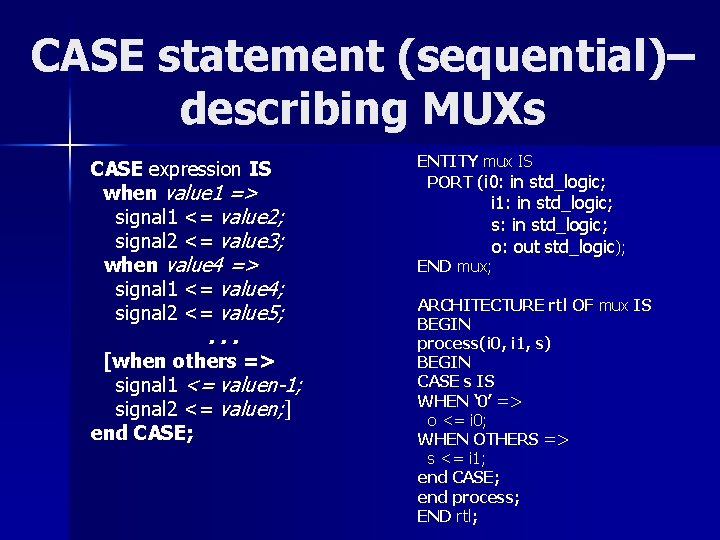

CASE statement (sequential)– describing MUXs CASE expression IS when value 1 => signal 1 <= value 2; signal 2 <= value 3; when value 4 => signal 1 <= value 4; signal 2 <= value 5; . . . [when others => signal 1 <= valuen-1; signal 2 <= valuen; ] end CASE; ENTITY mux IS PORT (i 0: in std_logic; i 1: in std_logic; s: in std_logic; o: out std_logic); END mux; ARCHITECTURE rtl OF mux IS BEGIN process(i 0, i 1, s) BEGIN CASE s IS WHEN ‘ 0’ => o <= i 0; WHEN OTHERS => s <= i 1; end CASE; end process; END rtl;

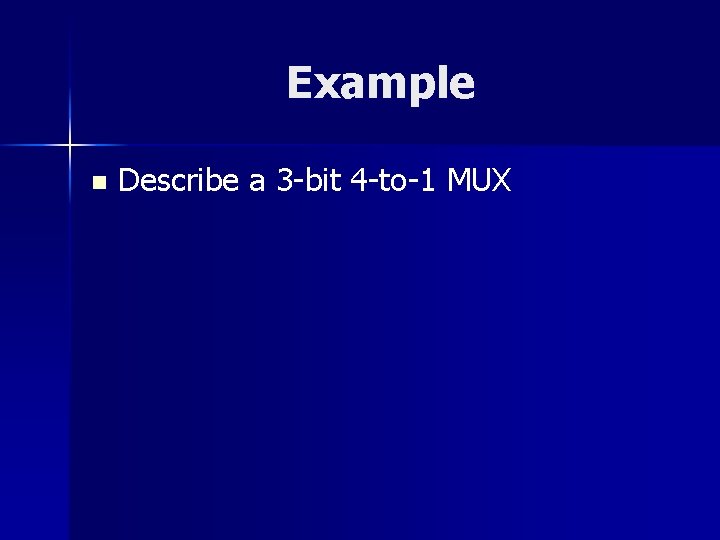

Example n Describe a 3 -bit 4 -to-1 MUX

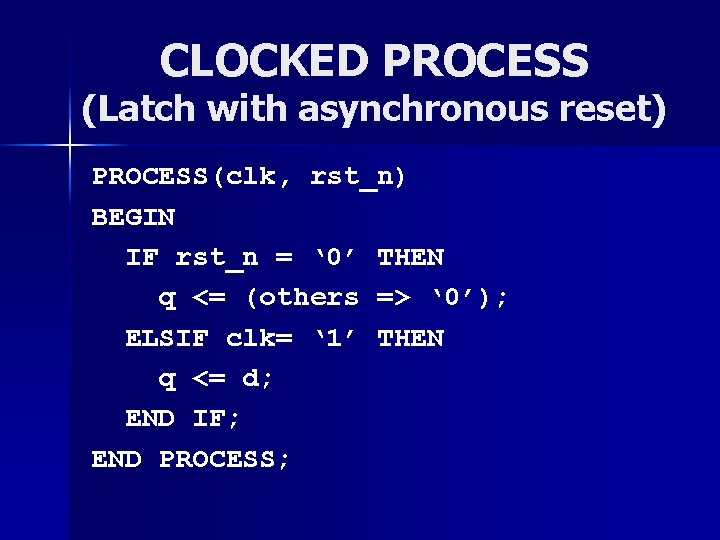

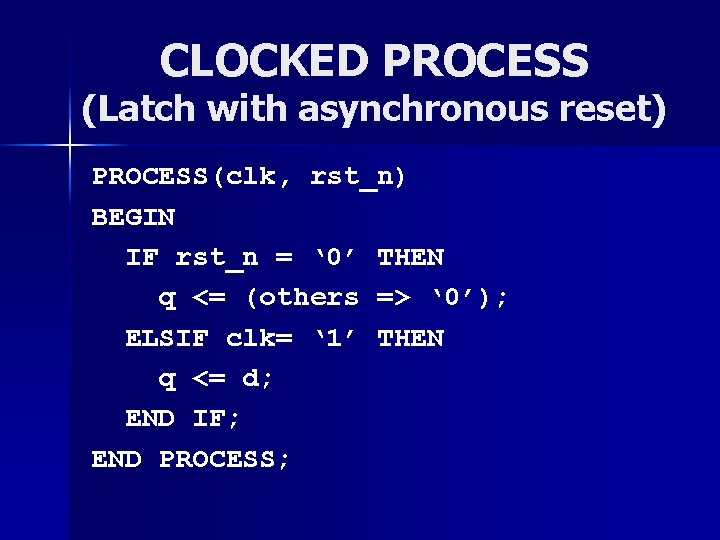

CLOCKED PROCESS (Latch with asynchronous reset) PROCESS(clk, rst_n) BEGIN IF rst_n = ‘ 0’ THEN q <= (others => ‘ 0’); ELSIF clk= ‘ 1’ THEN q <= d; END IF; END PROCESS;

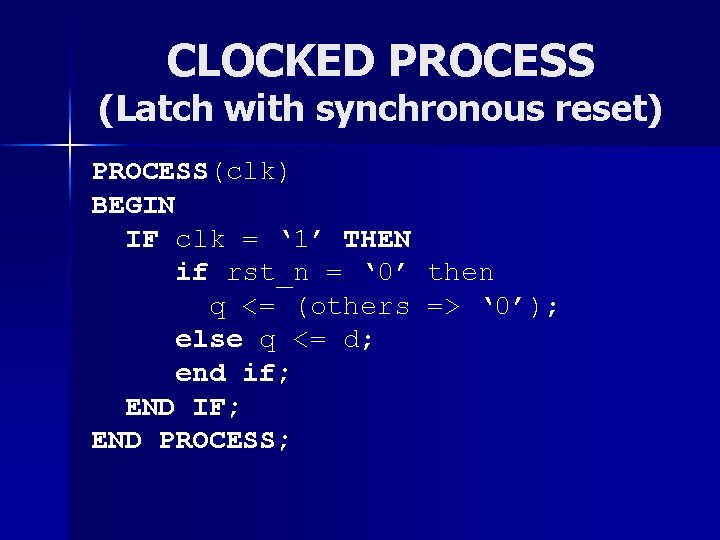

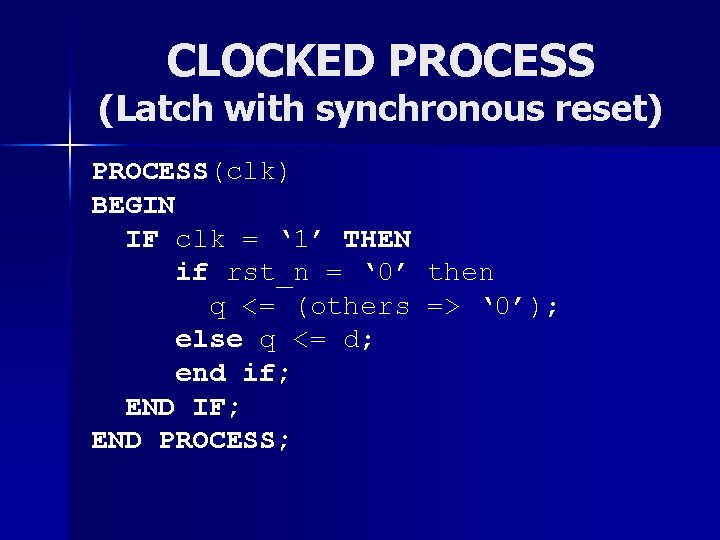

CLOCKED PROCESS (Latch with synchronous reset) PROCESS(clk) BEGIN IF clk = ‘ 1’ THEN if rst_n = ‘ 0’ then q <= (others => ‘ 0’); else q <= d; end if; END IF; END PROCESS;

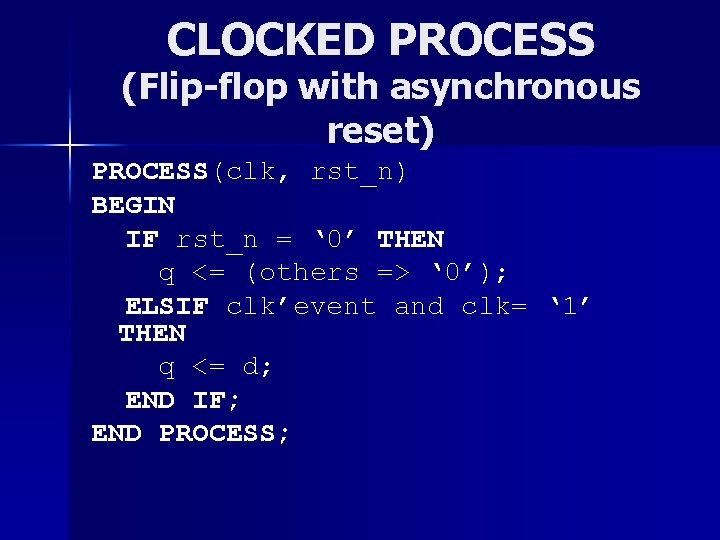

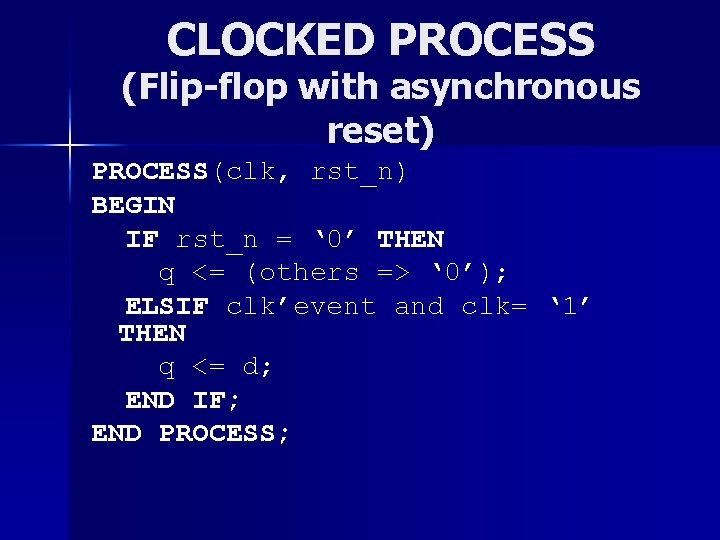

CLOCKED PROCESS (Flip-flop with asynchronous reset) PROCESS(clk, rst_n) BEGIN IF rst_n = ‘ 0’ THEN q <= (others => ‘ 0’); ELSIF clk’event and clk= ‘ 1’ THEN q <= d; END IF; END PROCESS;

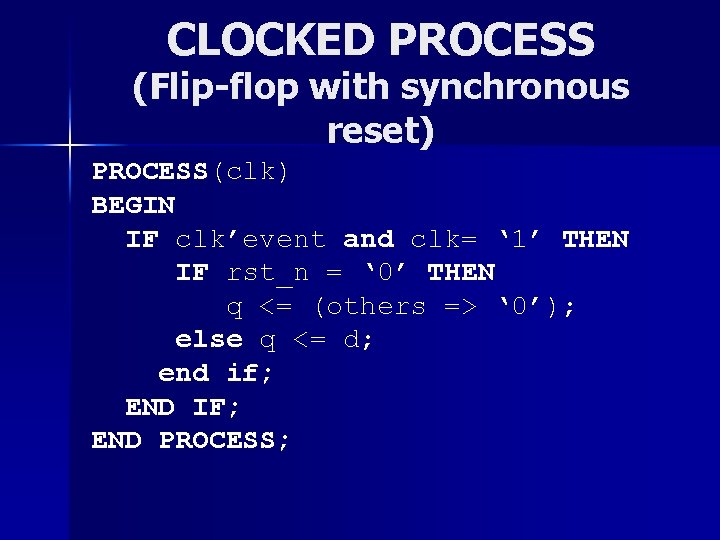

CLOCKED PROCESS (Flip-flop with synchronous reset) PROCESS(clk) BEGIN IF clk’event and clk= ‘ 1’ THEN IF rst_n = ‘ 0’ THEN q <= (others => ‘ 0’); else q <= d; end if; END IF; END PROCESS;

![for loop statement shift register label for identifier in range loop statements end for loop statement – shift register [label]: for identifier in range loop statements end](https://slidetodoc.com/presentation_image_h/2e63da5b23a2767091cced57da40cfb8/image-48.jpg)

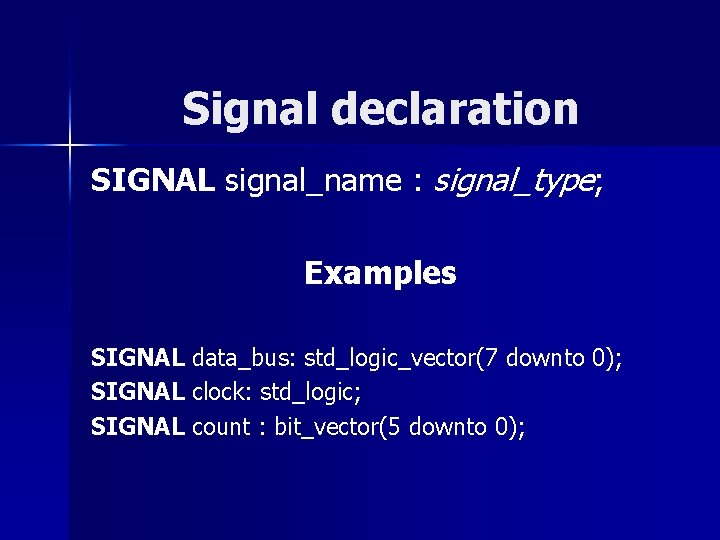

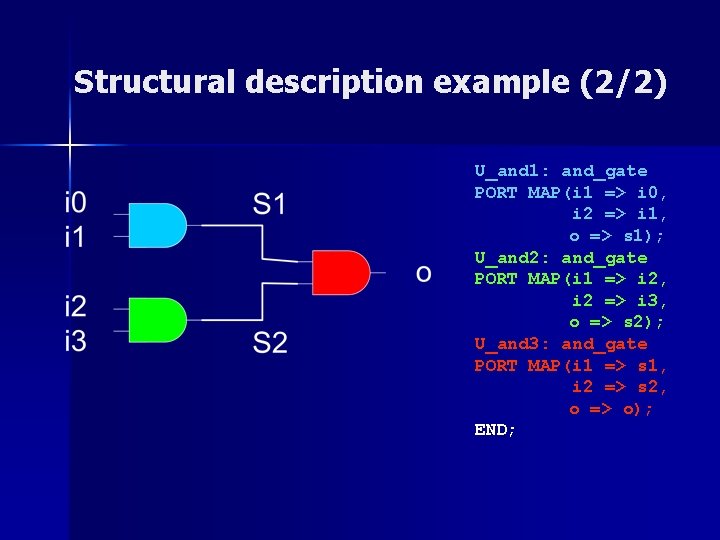

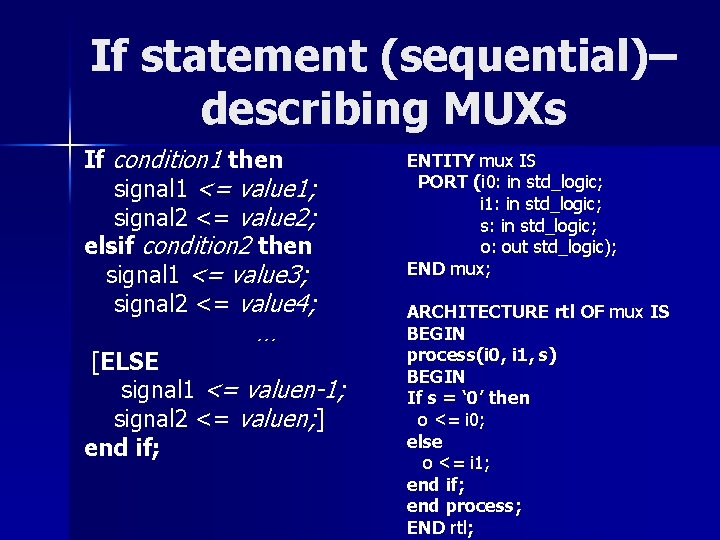

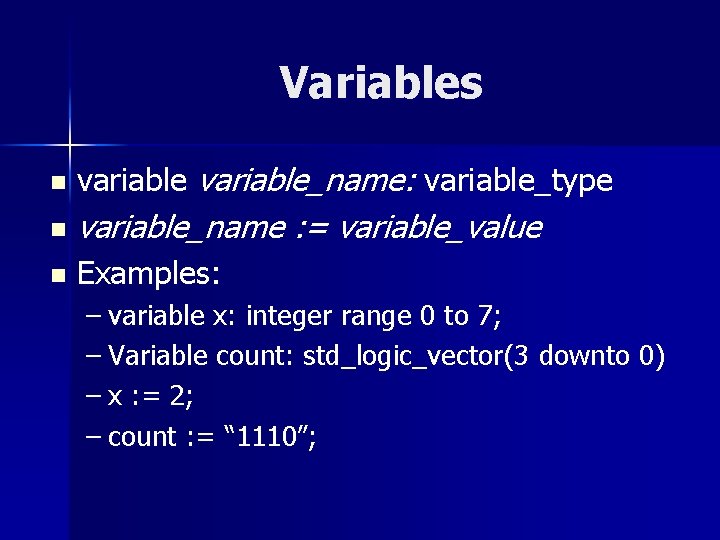

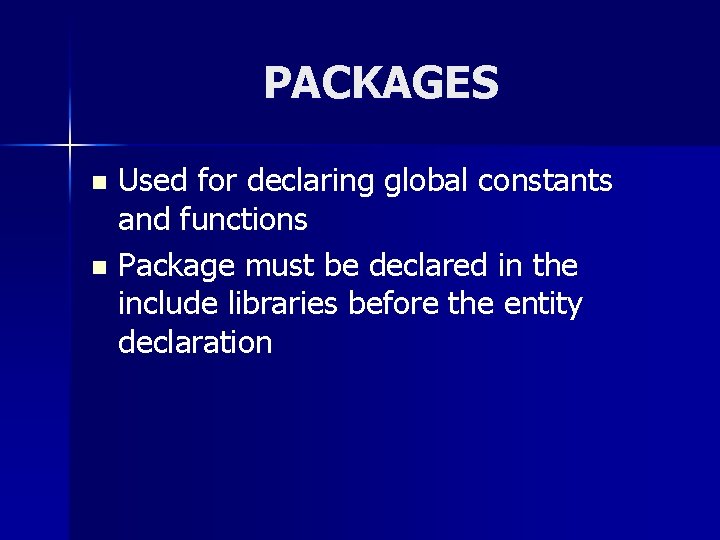

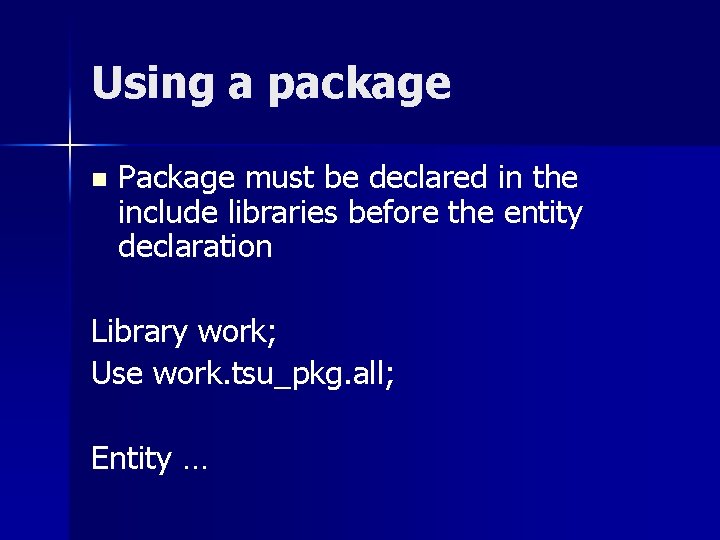

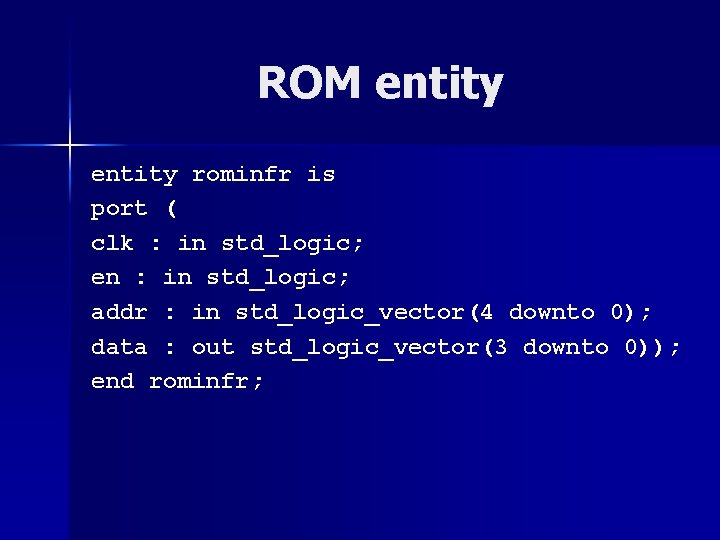

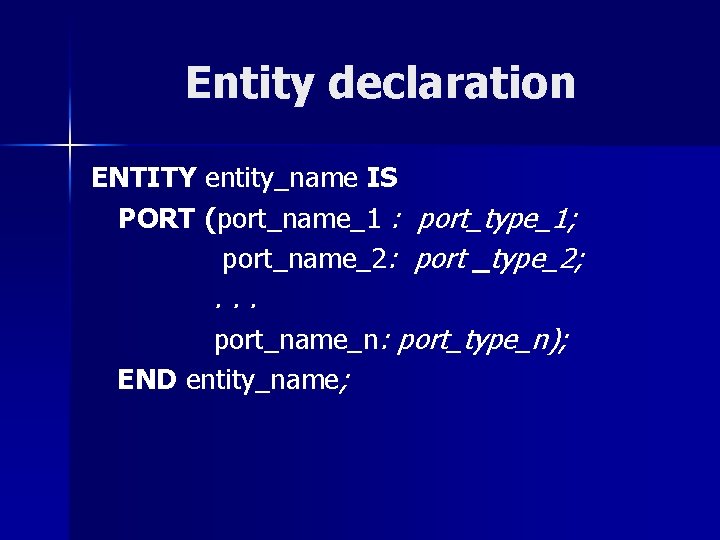

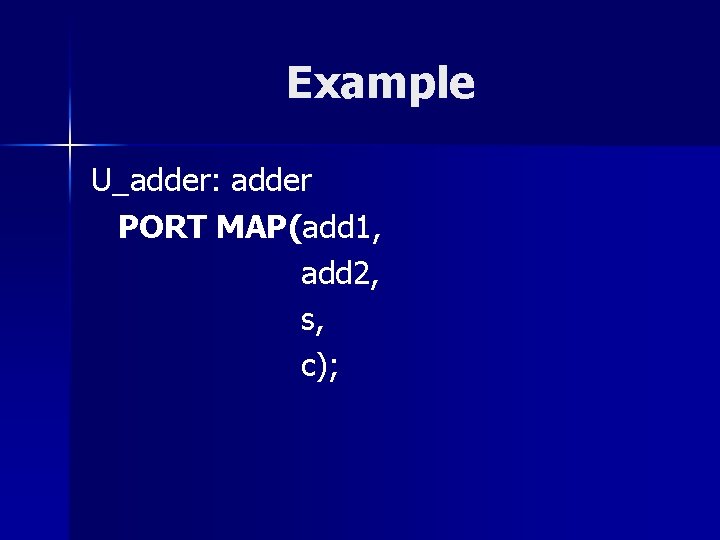

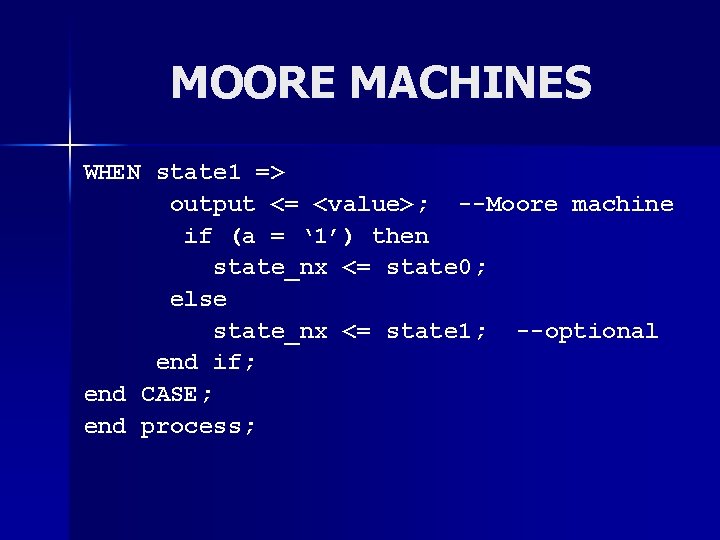

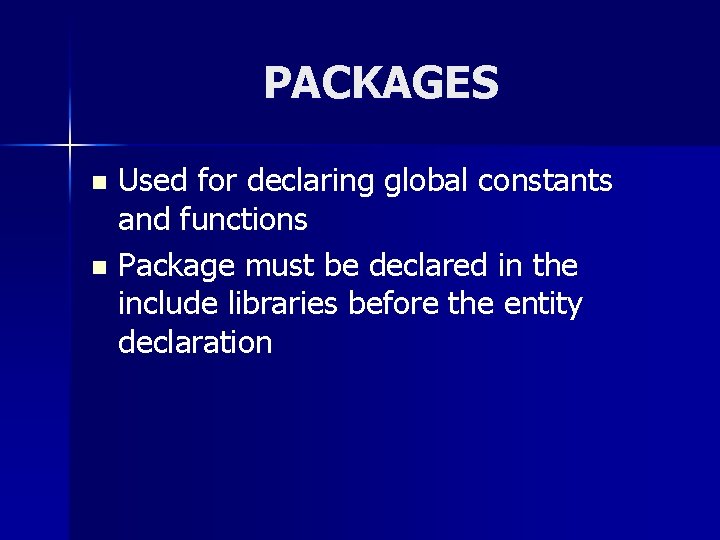

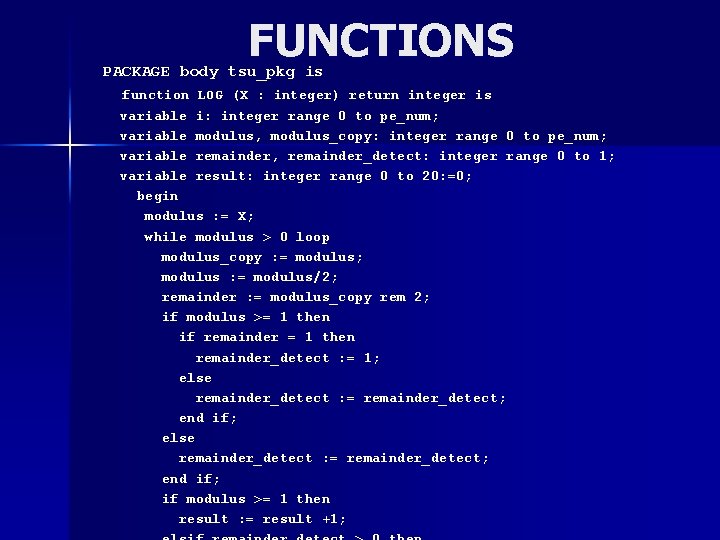

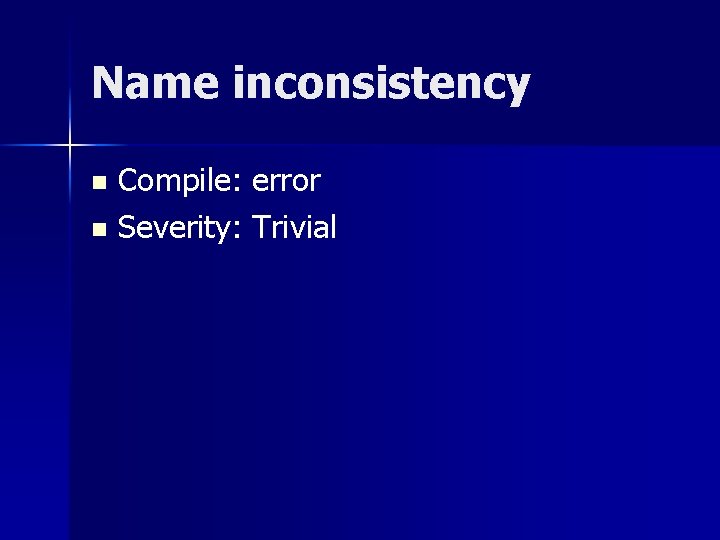

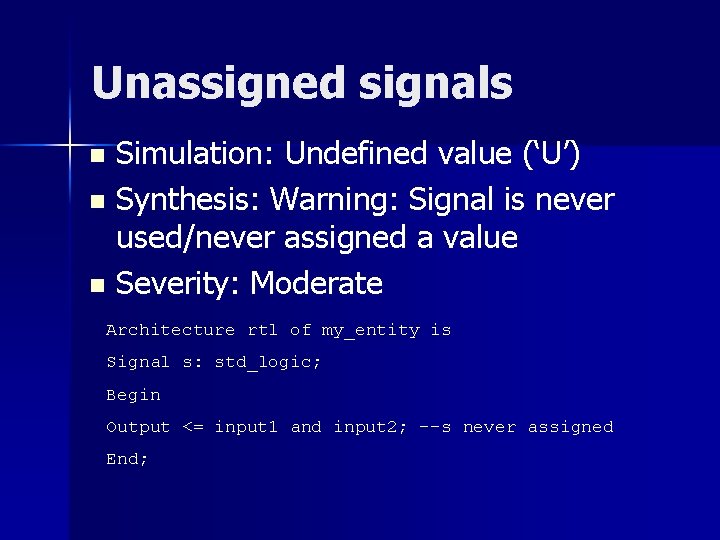

for loop statement – shift register [label]: for identifier in range loop statements end loop; ENTITY shift_reg is port(clk, rst_n: in std_logic; input: in std_logic; output: out std_logic); end shift_reg; Architecture rtl of shift_reg is signal d: std_logic_vector(3 downto 0); begin process(clk, rst_n) begin if rst_n = ‘ 0’ then d <= (others => ‘ 0’); elsif rising_edge(clk) then d(0) <= input; for i in 0 to 3 loop d(i+1) <= d(i); end loop; end if; end process; output <= d(3); end;

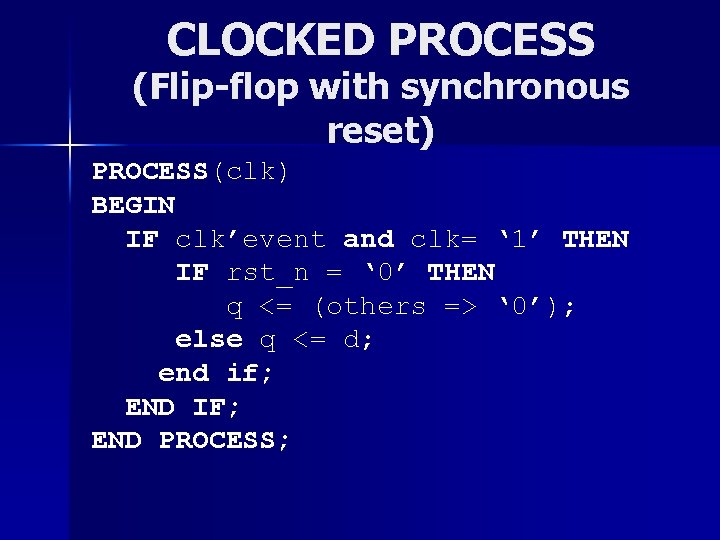

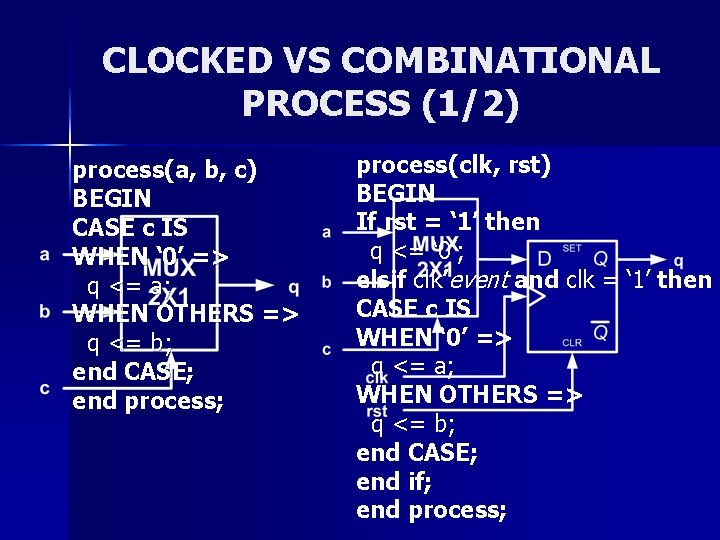

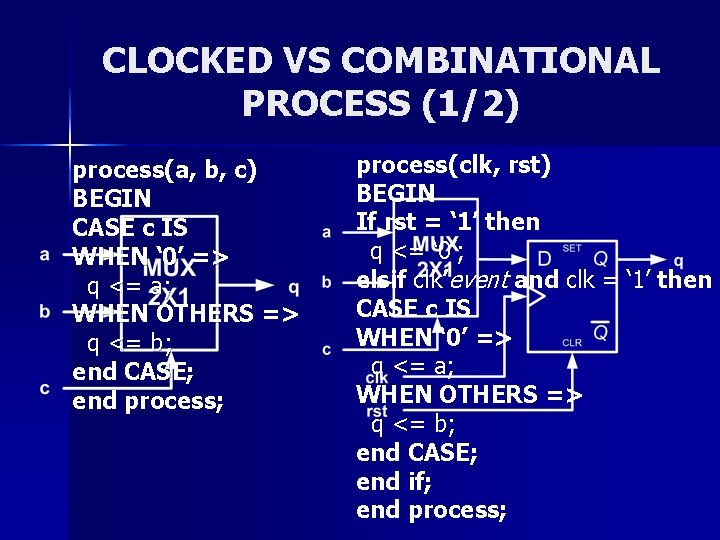

CLOCKED VS COMBINATIONAL PROCESS (1/2) process(a, b, c) BEGIN CASE c IS WHEN ‘ 0’ => q <= a; WHEN OTHERS => q <= b; end CASE; end process; process(clk, rst) BEGIN If rst = ‘ 1’ then q <= ‘ 0’; elsif clk’event and clk = ‘ 1’ then CASE c IS WHEN ‘ 0’ => q <= a; WHEN OTHERS => q <= b; end CASE; end if; end process;

CLOCKED VS COMBINATIONAL PROCESS (2/2) PROCESS(a, b, c) BEGIN d <= (a AND b) OR c; END PROCESS; PROCESS(clk, rst) BEGIN if rst = ‘ 1’ then d <= ‘ 0’; elsif clk’event and clk= ‘ 1’ then d <= (a AND b) OR c; end if; END PROCESS;

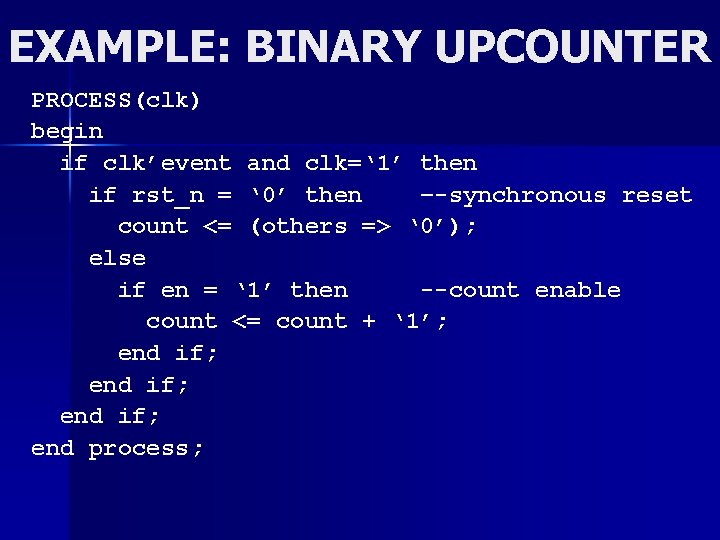

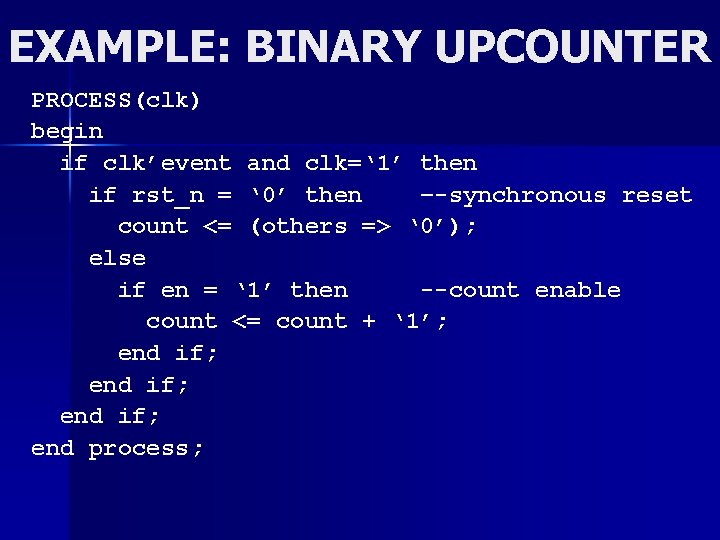

EXAMPLE: BINARY UPCOUNTER PROCESS(clk) begin if clk’event and clk=‘ 1’ then if rst_n = ‘ 0’ then –-synchronous reset count <= (others => ‘ 0’); else if en = ‘ 1’ then --count enable count <= count + ‘ 1’; end if; end process;

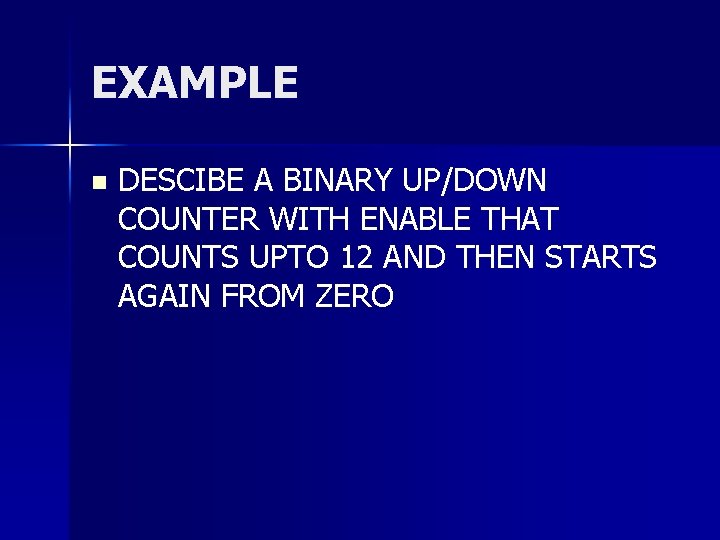

EXAMPLE n DESCIBE A BINARY UP/DOWN COUNTER WITH ENABLE THAT COUNTS UPTO 12 AND THEN STARTS AGAIN FROM ZERO

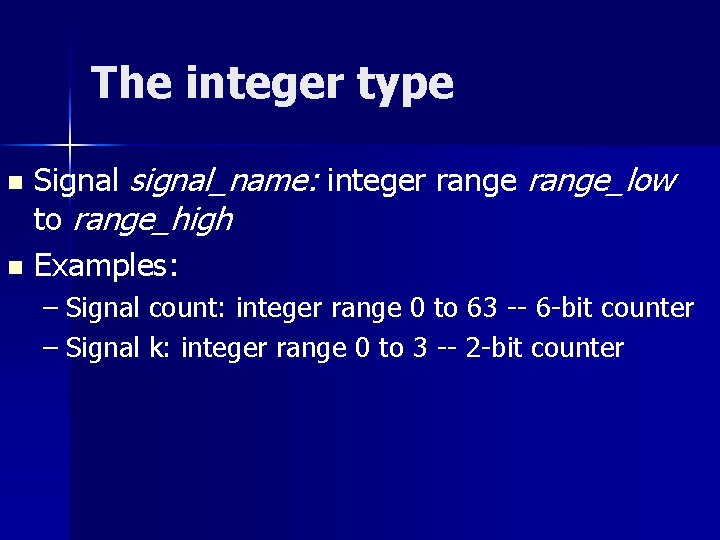

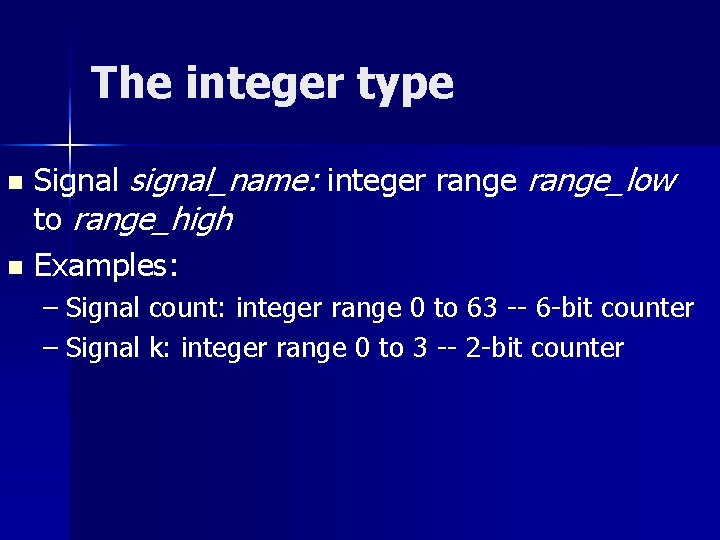

The integer type Signal signal_name: integer range_low to range_high n Examples: n – Signal count: integer range 0 to 63 -- 6 -bit counter – Signal k: integer range 0 to 3 -- 2 -bit counter

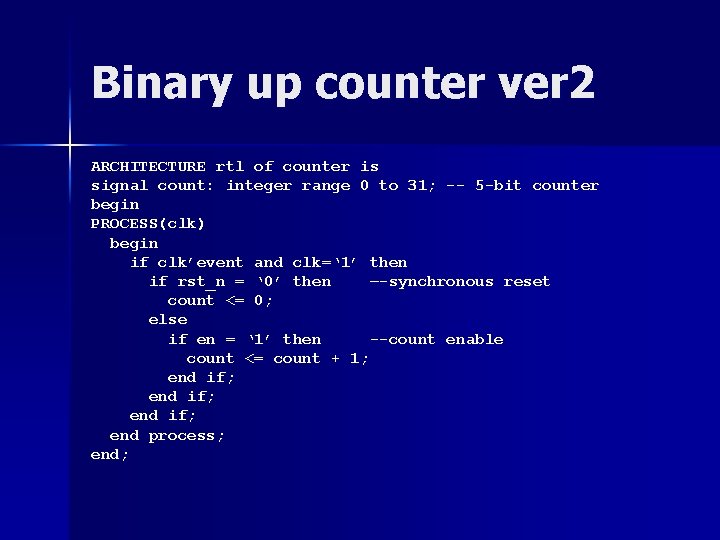

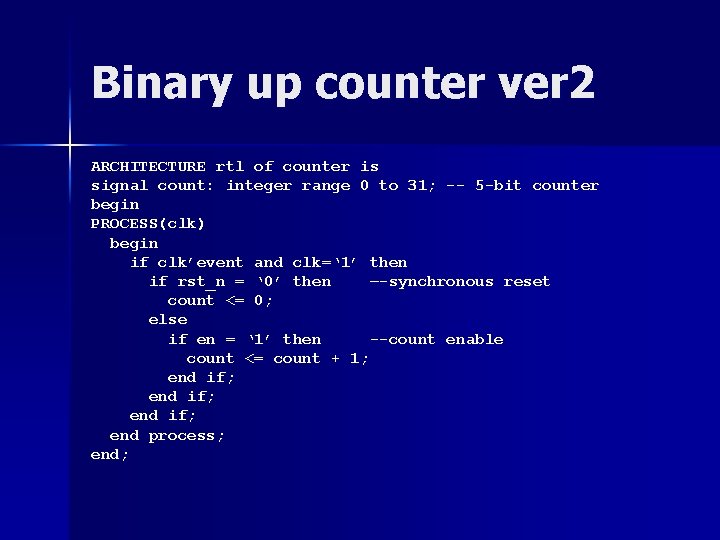

Binary up counter ver 2 ARCHITECTURE rtl of counter is signal count: integer range 0 to 31; -- 5 -bit counter begin PROCESS(clk) begin if clk’event and clk=‘ 1’ then if rst_n = ‘ 0’ then –-synchronous reset count <= 0; else if en = ‘ 1’ then --count enable count <= count + 1; end if; end process; end;

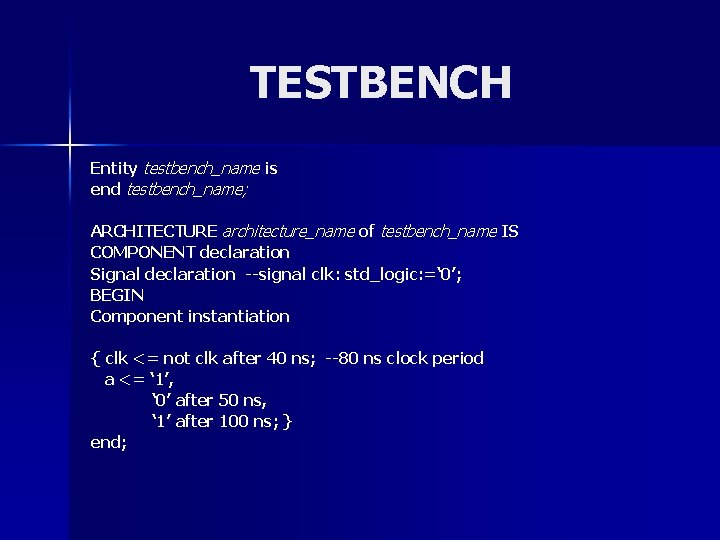

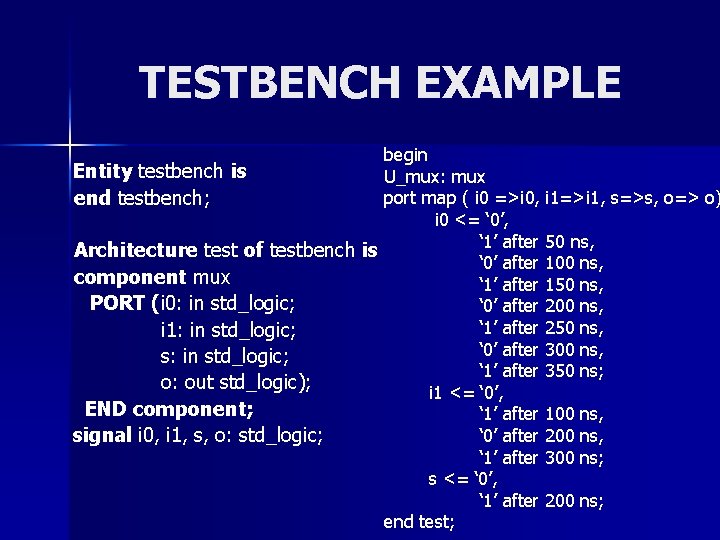

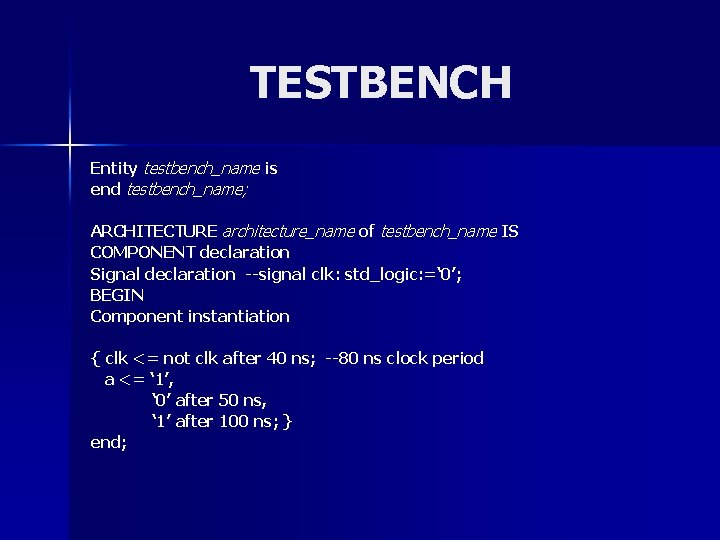

TESTBENCH Entity testbench_name is end testbench_name; ARCHITECTURE architecture_name of testbench_name IS COMPONENT declaration Signal declaration --signal clk: std_logic: =‘ 0’; BEGIN Component instantiation { clk <= not clk after 40 ns; --80 ns clock period a <= ‘ 1’, ‘ 0’ after 50 ns, ‘ 1’ after 100 ns; } end;

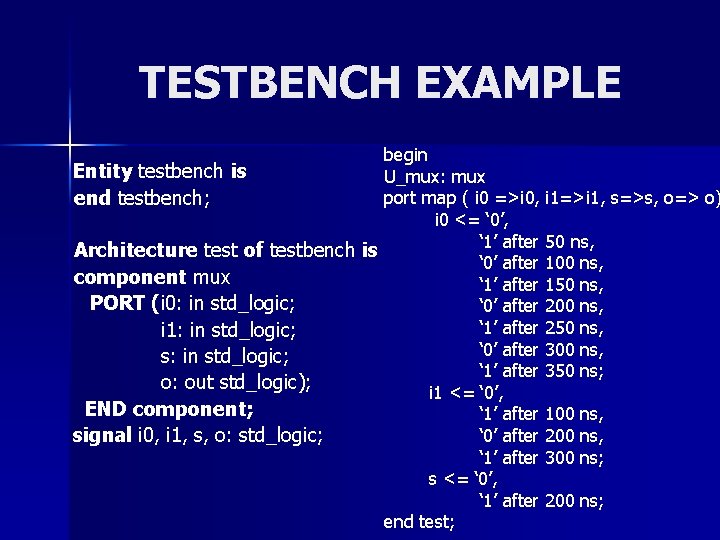

TESTBENCH EXAMPLE begin Entity testbench is U_mux: mux port map ( i 0 =>i 0, i 1=>i 1, s=>s, o=> o) end testbench; i 0 <= ‘ 0’, ‘ 1’ after 50 ns, Architecture test of testbench is ‘ 0’ after 100 ns, component mux ‘ 1’ after 150 ns, PORT (i 0: in std_logic; ‘ 0’ after 200 ns, ‘ 1’ after 250 ns, i 1: in std_logic; ‘ 0’ after 300 ns, s: in std_logic; ‘ 1’ after 350 ns; o: out std_logic); i 1 <= ‘ 0’, END component; ‘ 1’ after 100 ns, ‘ 0’ after 200 ns, signal i 0, i 1, s, o: std_logic; ‘ 1’ after 300 ns; s <= ‘ 0’, ‘ 1’ after 200 ns; end test;

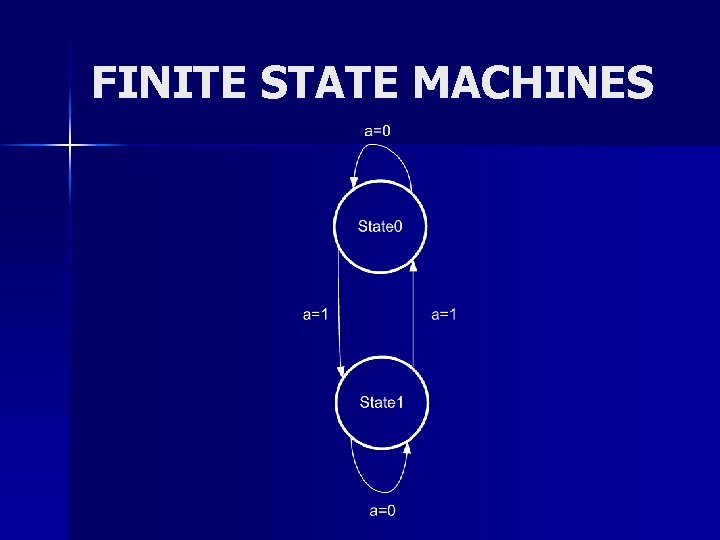

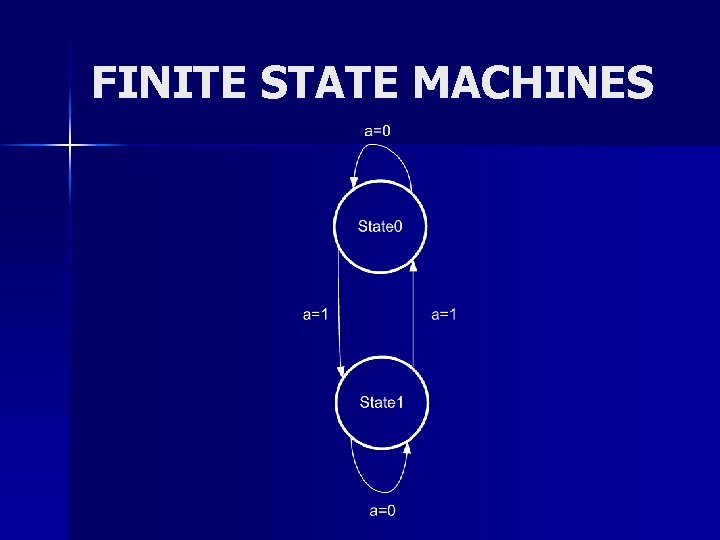

FINITE STATE MACHINES

FINITE STATE MACHINE IMPLEMENTATION

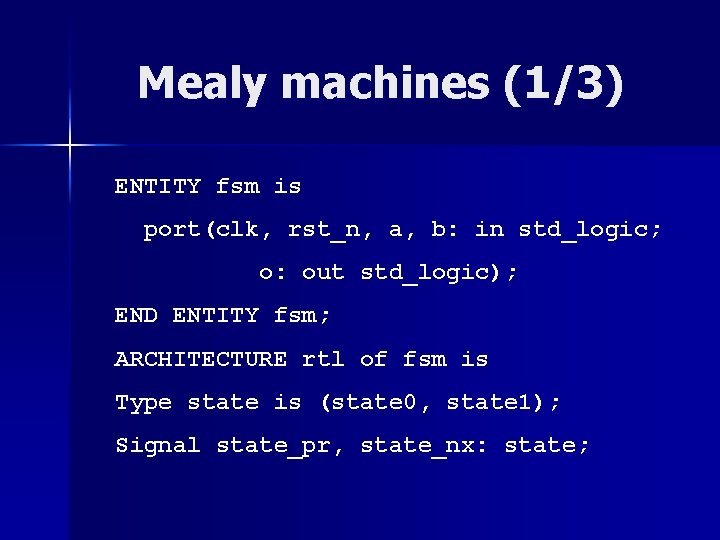

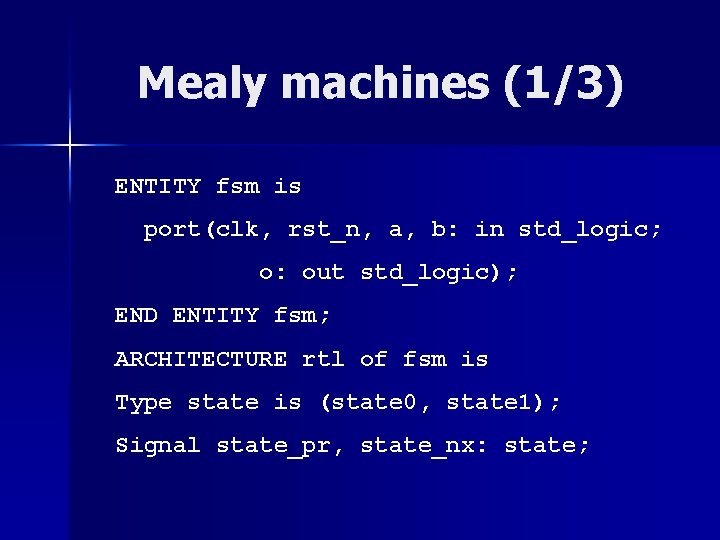

Mealy machines (1/3) ENTITY fsm is port(clk, rst_n, a, b: in std_logic; o: out std_logic); END ENTITY fsm; ARCHITECTURE rtl of fsm is Type state is (state 0, state 1); Signal state_pr, state_nx: state;

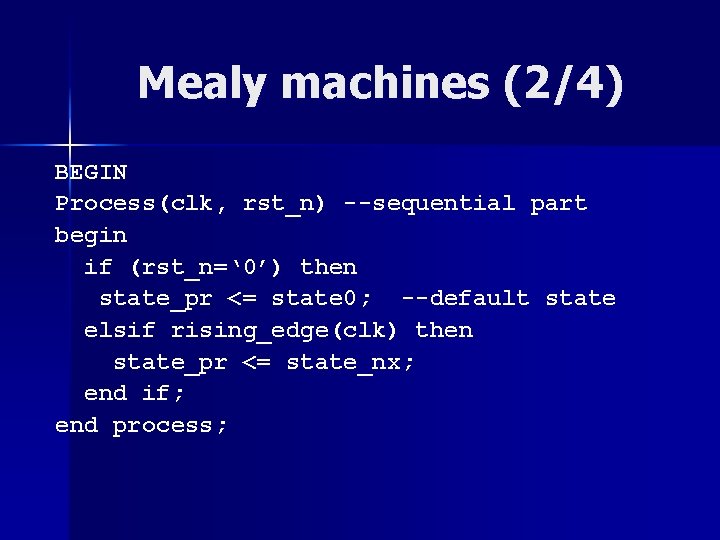

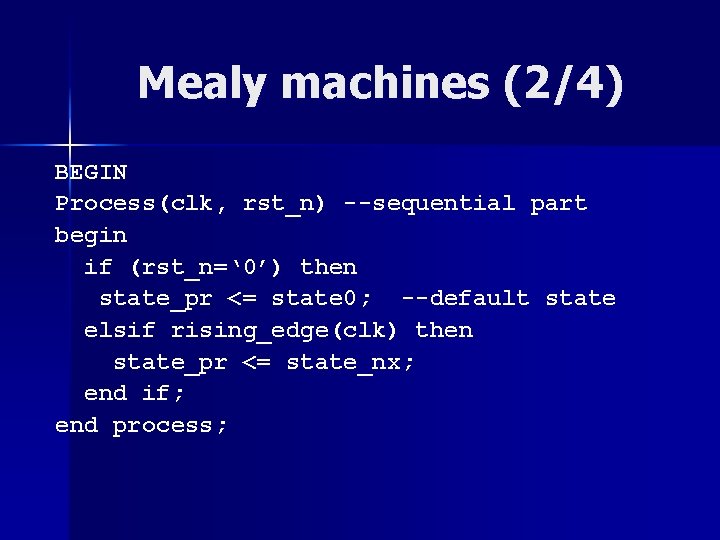

Mealy machines (2/4) BEGIN Process(clk, rst_n) --sequential part begin if (rst_n=‘ 0’) then state_pr <= state 0; --default state elsif rising_edge(clk) then state_pr <= state_nx; end if; end process;

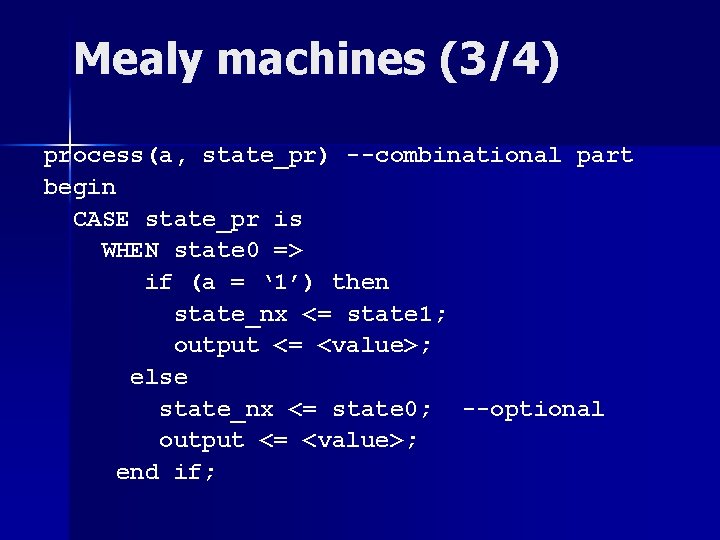

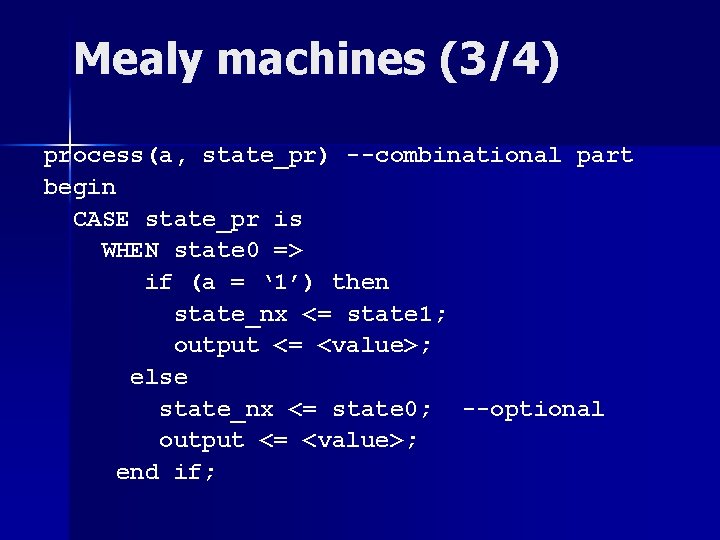

Mealy machines (3/4) process(a, state_pr) --combinational part begin CASE state_pr is WHEN state 0 => if (a = ‘ 1’) then state_nx <= state 1; output <= <value>; else state_nx <= state 0; --optional output <= <value>; end if;

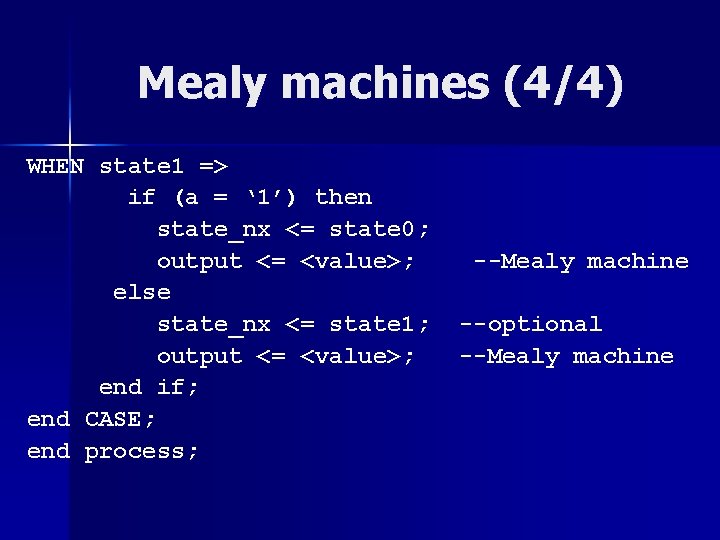

Mealy machines (4/4) WHEN state 1 => if (a = ‘ 1’) then state_nx <= state 0; output <= <value>; else state_nx <= state 1; output <= <value>; end if; end CASE; end process; --Mealy machine --optional --Mealy machine

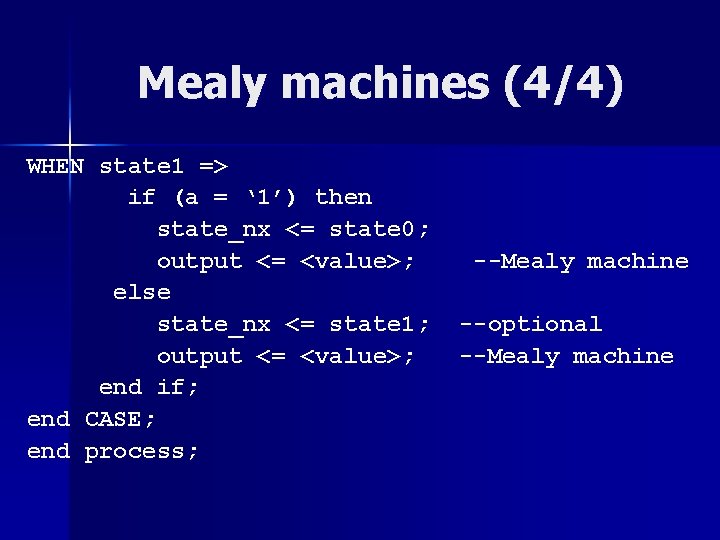

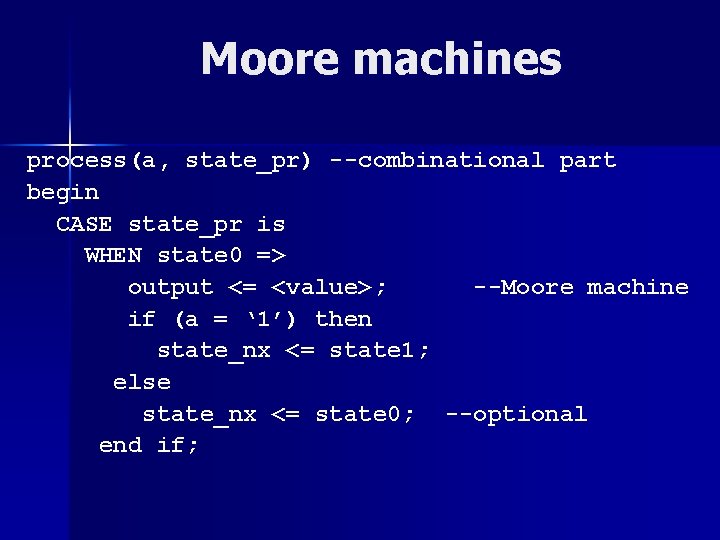

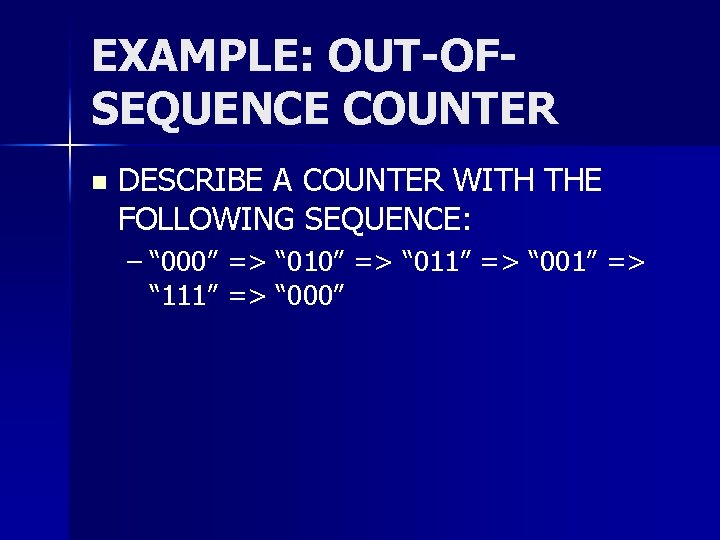

Moore machines process(a, state_pr) --combinational part begin CASE state_pr is WHEN state 0 => output <= <value>; --Moore machine if (a = ‘ 1’) then state_nx <= state 1; else state_nx <= state 0; --optional end if;

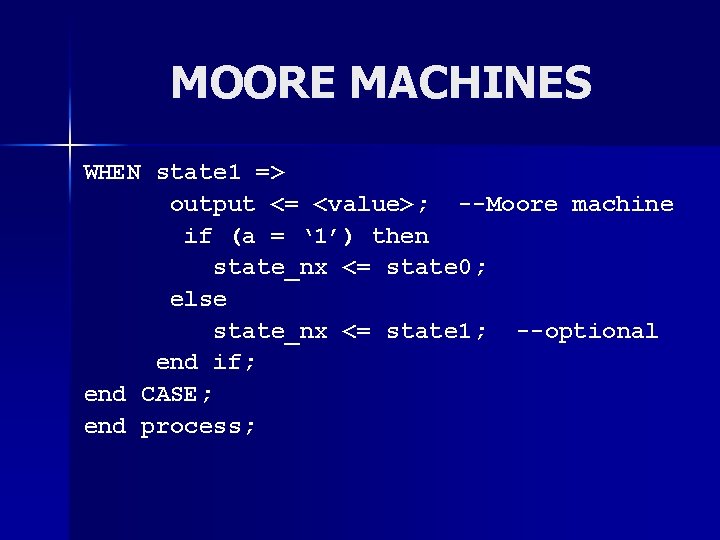

MOORE MACHINES WHEN state 1 => output <= <value>; --Moore machine if (a = ‘ 1’) then state_nx <= state 0; else state_nx <= state 1; --optional end if; end CASE; end process;

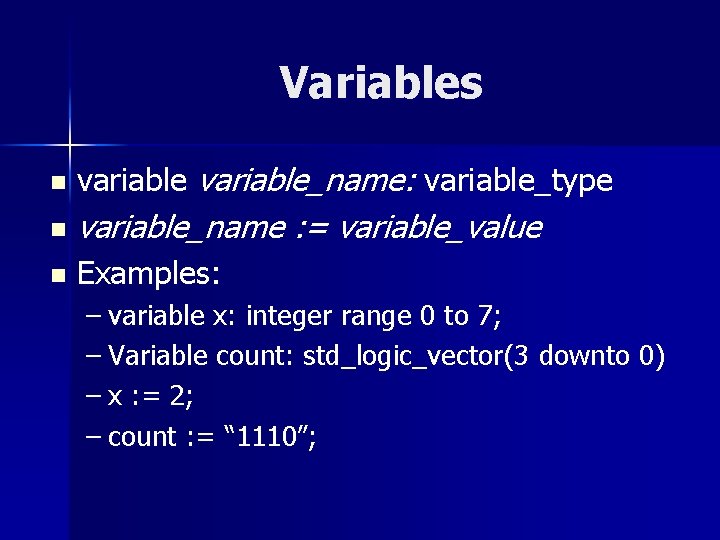

EXAMPLE: OUT-OFSEQUENCE COUNTER n DESCRIBE A COUNTER WITH THE FOLLOWING SEQUENCE: – “ 000” => “ 011” => “ 001” => “ 111” => “ 000”

Variables n variable_name: variable_type n variable_name : = variable_value n Examples: – variable x: integer range 0 to 7; – Variable count: std_logic_vector(3 downto 0) – x : = 2; – count : = “ 1110”;

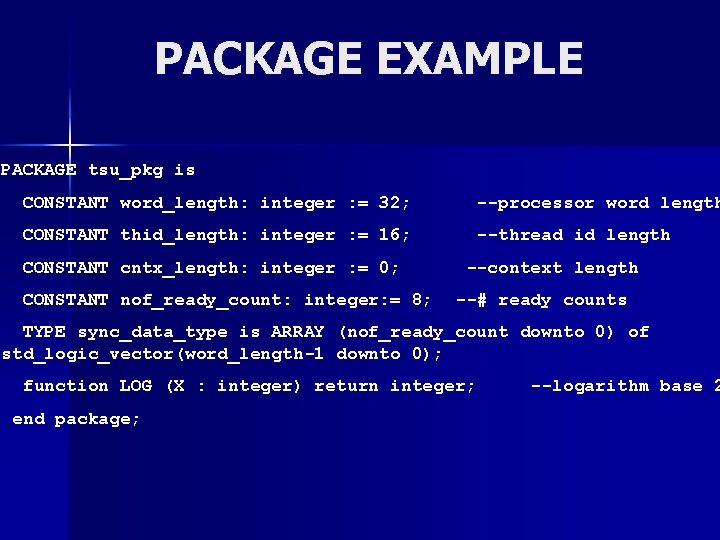

Signals vs. variables n Signal: – – – n can be used anywhere represents circuit interconnect value is updated at the end of process Variable: – only in sequential code (process, function, procedure) – Represents local information – value is updated immediately

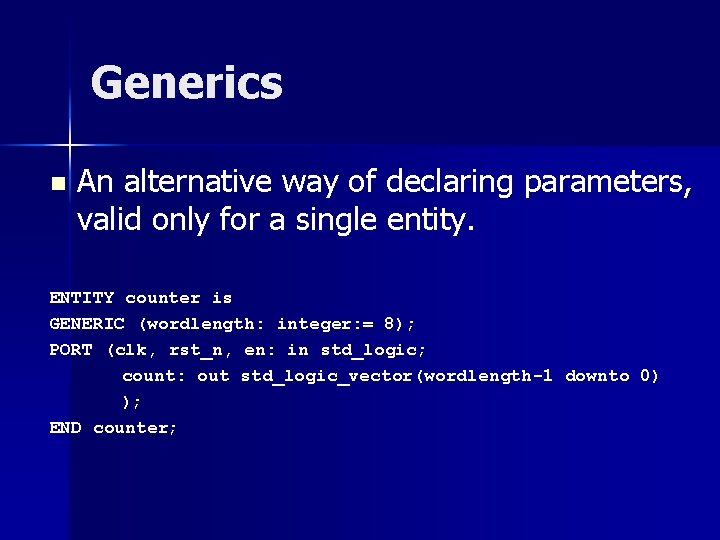

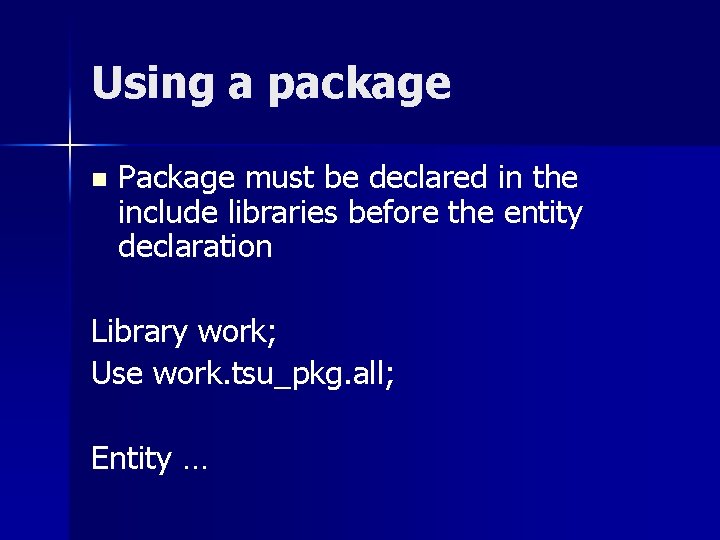

PACKAGES Used for declaring global constants and functions n Package must be declared in the include libraries before the entity declaration n

PACKAGE EXAMPLE PACKAGE tsu_pkg is CONSTANT word_length: integer : = 32; --processor word length CONSTANT thid_length: integer : = 16; --thread id length CONSTANT cntx_length: integer : = 0; CONSTANT nof_ready_count: integer: = 8; --context length --# ready counts TYPE sync_data_type is ARRAY (nof_ready_count downto 0) of std_logic_vector(word_length-1 downto 0); function LOG (X : integer) return integer; end package; --logarithm base 2

Using a package n Package must be declared in the include libraries before the entity declaration Library work; Use work. tsu_pkg. all; Entity …

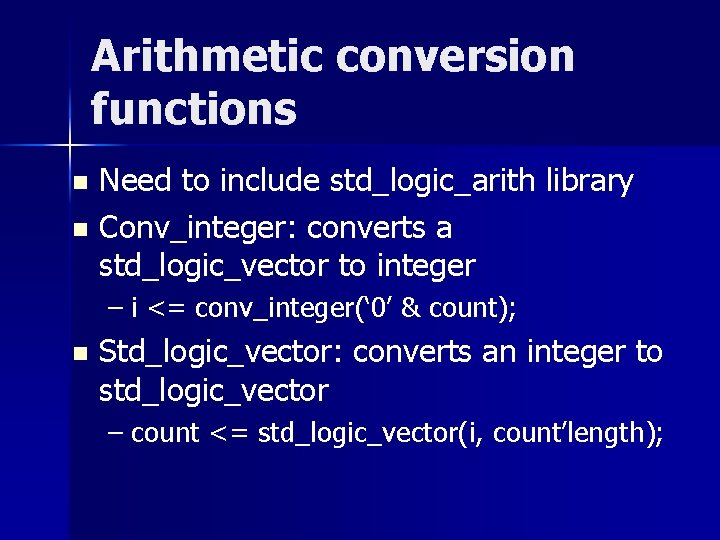

Generics n An alternative way of declaring parameters, valid only for a single entity. ENTITY counter is GENERIC (wordlength: integer: = 8); PORT (clk, rst_n, en: in std_logic; count: out std_logic_vector(wordlength-1 downto 0) ); END counter;

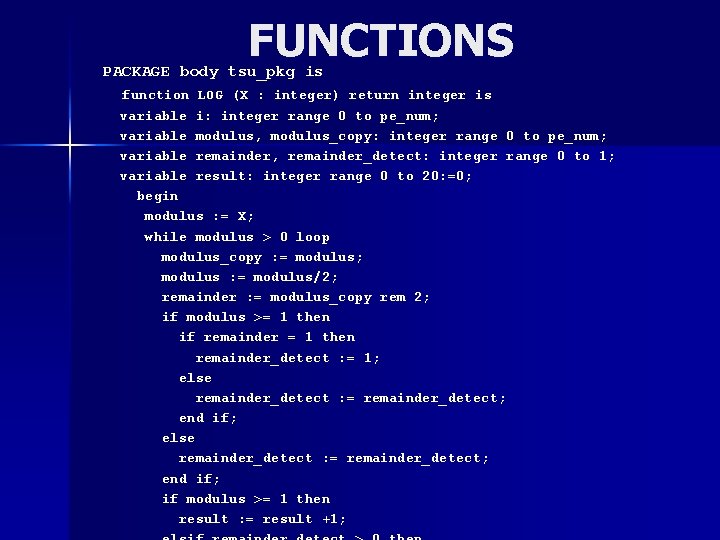

FUNCTIONS PACKAGE body tsu_pkg is function LOG (X : integer) return integer is variable i: integer range 0 to pe_num; variable modulus, modulus_copy: integer range 0 to pe_num; variable remainder, remainder_detect: integer range 0 to 1; variable result: integer range 0 to 20: =0; begin modulus : = X; while modulus > 0 loop modulus_copy : = modulus; modulus : = modulus/2; remainder : = modulus_copy rem 2; if modulus >= 1 then if remainder = 1 then remainder_detect : = 1; else remainder_detect : = remainder_detect; end if; if modulus >= 1 then result : = result +1;

Arithmetic conversion functions Need to include std_logic_arith library n Conv_integer: converts a std_logic_vector to integer n – i <= conv_integer(‘ 0’ & count); n Std_logic_vector: converts an integer to std_logic_vector – count <= std_logic_vector(i, count’length);

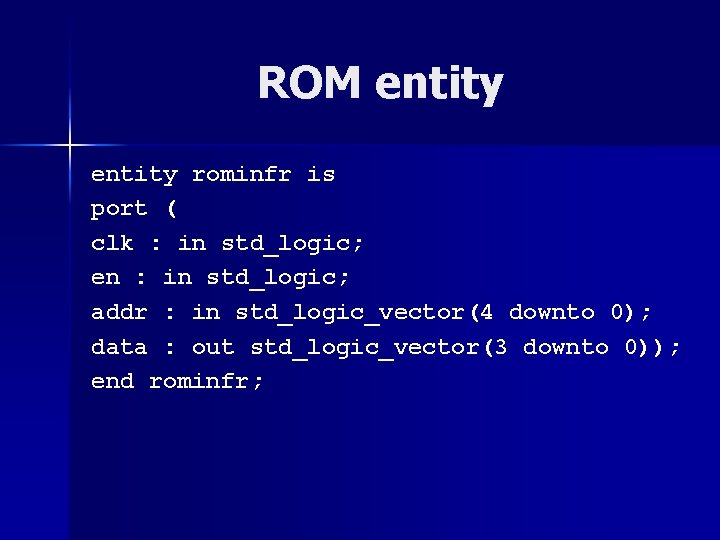

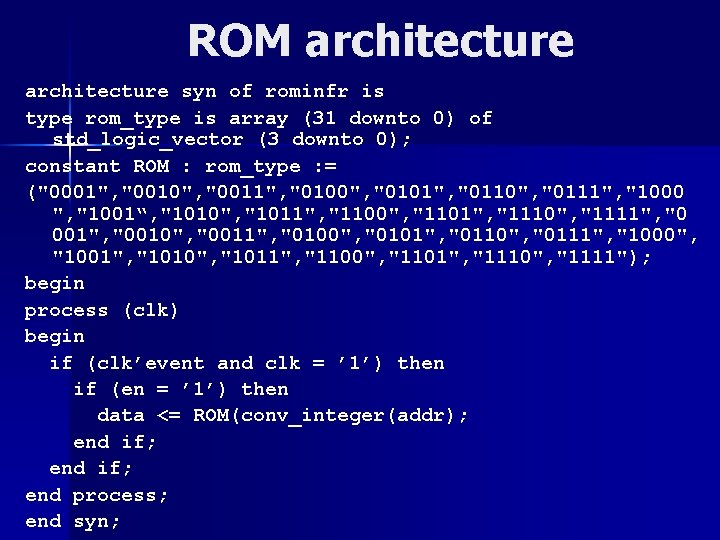

ROM entity rominfr is port ( clk : in std_logic; en : in std_logic; addr : in std_logic_vector(4 downto 0); data : out std_logic_vector(3 downto 0)); end rominfr;

ROM architecture syn of rominfr is type rom_type is array (31 downto 0) of std_logic_vector (3 downto 0); constant ROM : rom_type : = ("0001", "0010", "0011", "0100", "0101", "0110", "0111", "1000 ", "1001“, "1010", "1011", "1100", "1101", "1110", "1111", "0 001", "0010", "0011", "0100", "0101", "0110", "0111", "1000", "1001", "1010", "1011", "1100", "1101", "1110", "1111"); begin process (clk) begin if (clk’event and clk = ’ 1’) then if (en = ’ 1’) then data <= ROM(conv_integer(addr); end if; end process; end syn;

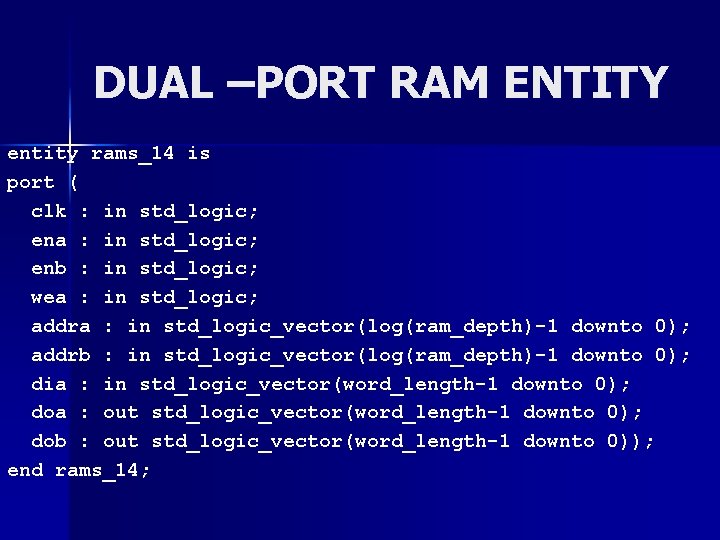

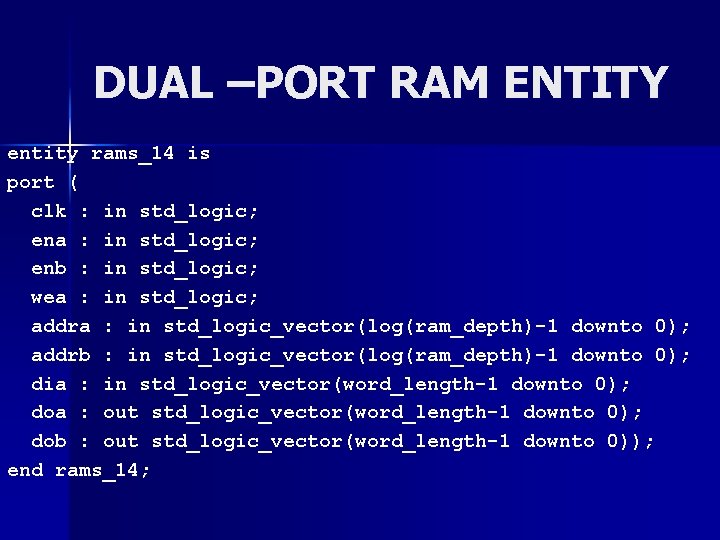

DUAL –PORT RAM ENTITY entity rams_14 is port ( clk : in std_logic; ena : in std_logic; enb : in std_logic; wea : in std_logic; addra : in std_logic_vector(log(ram_depth)-1 downto 0); addrb : in std_logic_vector(log(ram_depth)-1 downto 0); dia : in std_logic_vector(word_length-1 downto 0); doa : out std_logic_vector(word_length-1 downto 0); dob : out std_logic_vector(word_length-1 downto 0)); end rams_14;

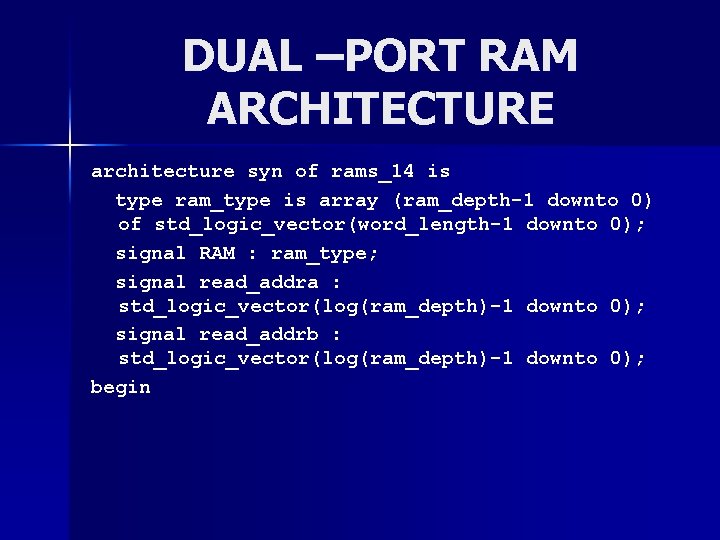

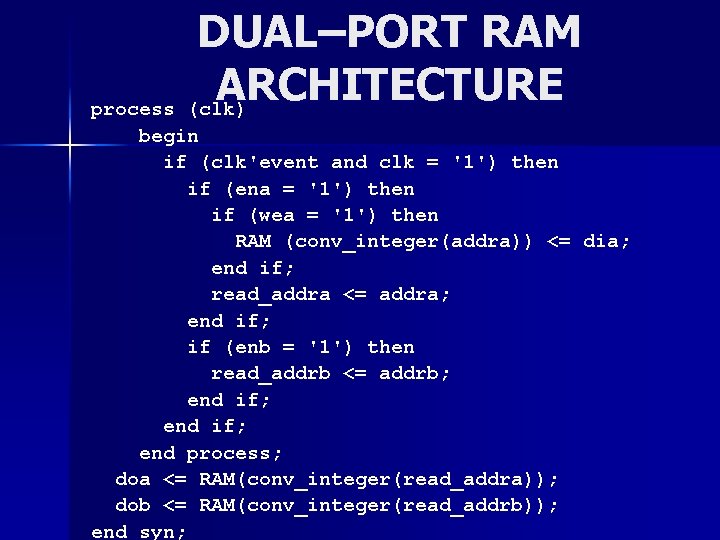

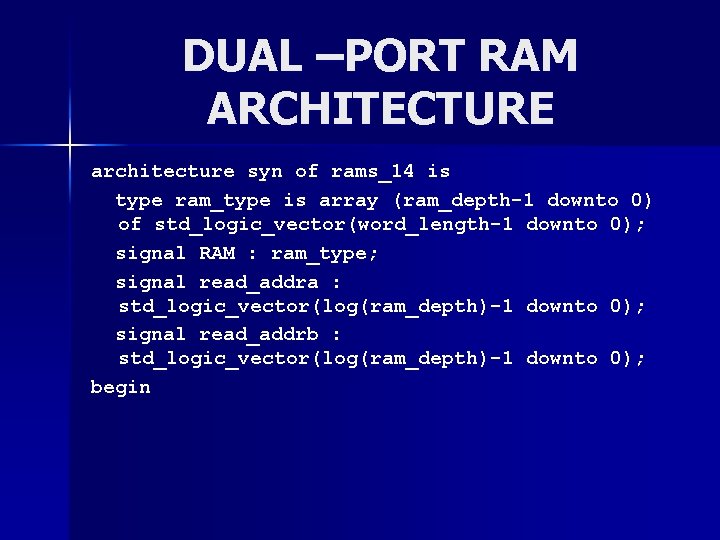

DUAL –PORT RAM ARCHITECTURE architecture syn of rams_14 is type ram_type is array (ram_depth-1 downto 0) of std_logic_vector(word_length-1 downto 0); signal RAM : ram_type; signal read_addra : std_logic_vector(log(ram_depth)-1 downto 0); signal read_addrb : std_logic_vector(log(ram_depth)-1 downto 0); begin

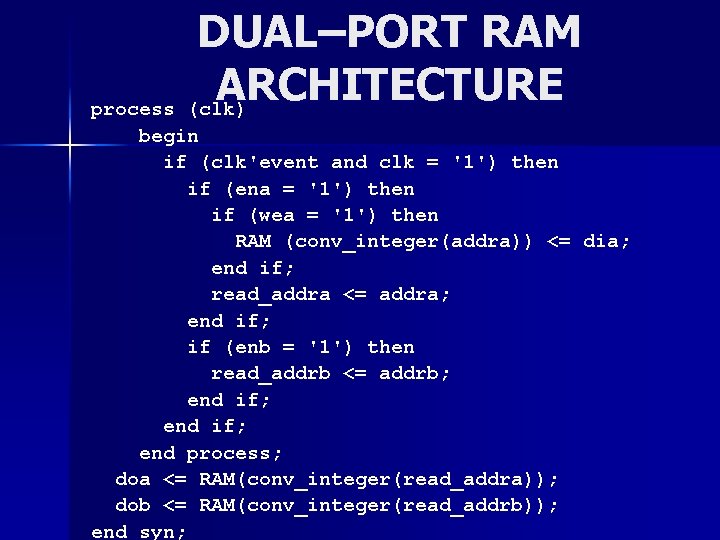

DUAL–PORT RAM ARCHITECTURE process (clk) begin if (clk'event and clk = '1') then if (ena = '1') then if (wea = '1') then RAM (conv_integer(addra)) <= dia; end if; read_addra <= addra; end if; if (enb = '1') then read_addrb <= addrb; end if; end process; doa <= RAM(conv_integer(read_addra)); dob <= RAM(conv_integer(read_addrb)); end syn;

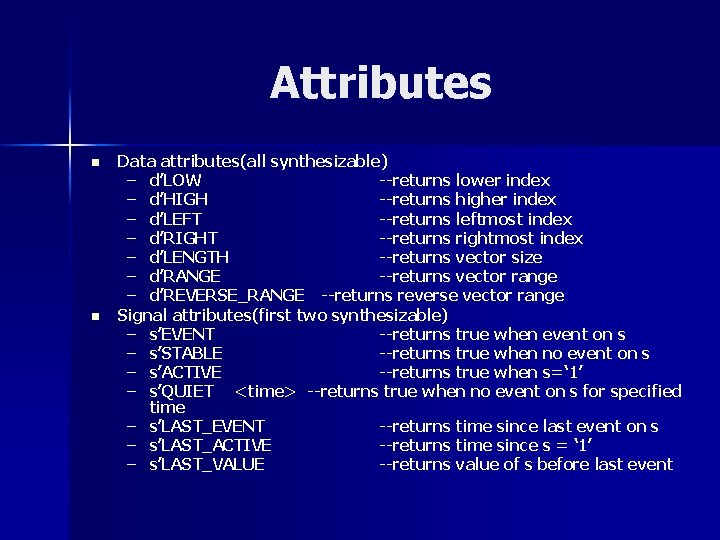

Attributes n n Data attributes(all synthesizable) – d’LOW --returns lower index – d’HIGH --returns higher index – d’LEFT --returns leftmost index – d’RIGHT --returns rightmost index – d’LENGTH --returns vector size – d’RANGE --returns vector range – d’REVERSE_RANGE --returns reverse vector range Signal attributes(first two synthesizable) – s’EVENT --returns true when event on s – s’STABLE --returns true when no event on s – s’ACTIVE --returns true when s=‘ 1’ – s’QUIET <time> --returns true when no event on s for specified time – s’LAST_EVENT --returns time since last event on s – s’LAST_ACTIVE --returns time since s = ‘ 1’ – s’LAST_VALUE --returns value of s before last event

Common VHDL Pitfalls

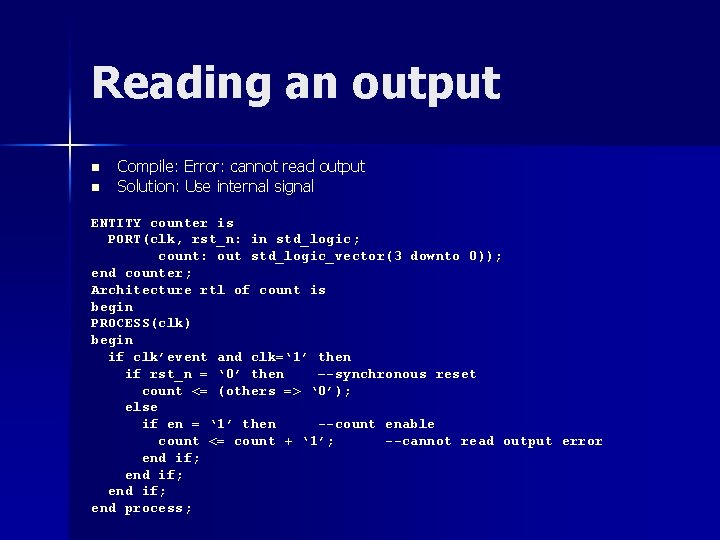

Name inconsistency Compile: error n Severity: Trivial n

Reading an output n n Compile: Error: cannot read output Solution: Use internal signal ENTITY counter is PORT(clk, rst_n: in std_logic; count: out std_logic_vector(3 downto 0)); end counter; Architecture rtl of count is begin PROCESS(clk) begin if clk’event and clk=‘ 1’ then if rst_n = ‘ 0’ then –-synchronous reset count <= (others => ‘ 0’); else if en = ‘ 1’ then --count enable count <= count + ‘ 1’; --cannot read output error end if; end process;

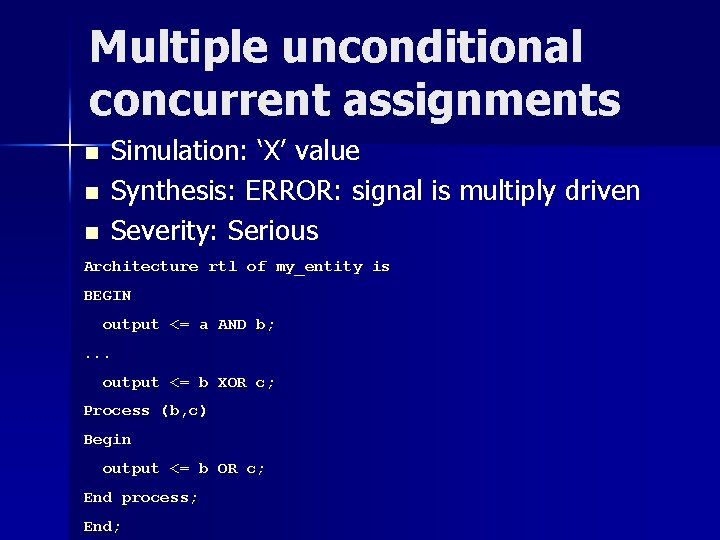

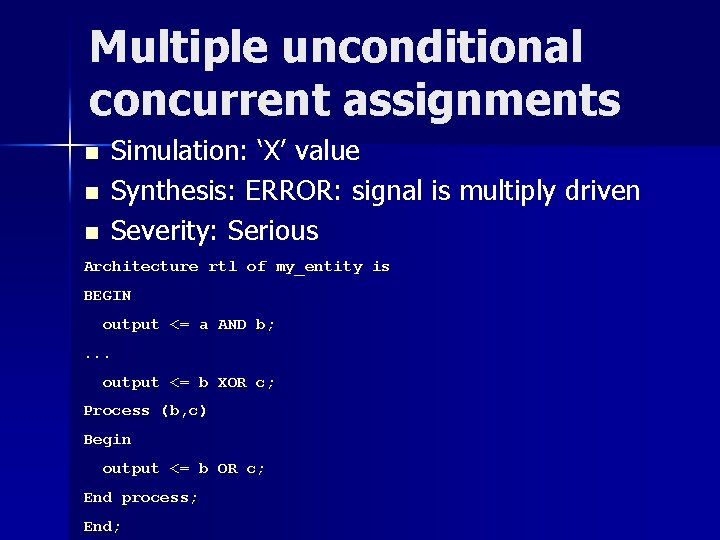

Multiple unconditional concurrent assignments n n n Simulation: ‘X’ value Synthesis: ERROR: signal is multiply driven Severity: Serious Architecture rtl of my_entity is BEGIN output <= a AND b; . . . output <= b XOR c; Process (b, c) Begin output <= b OR c; End process; End;

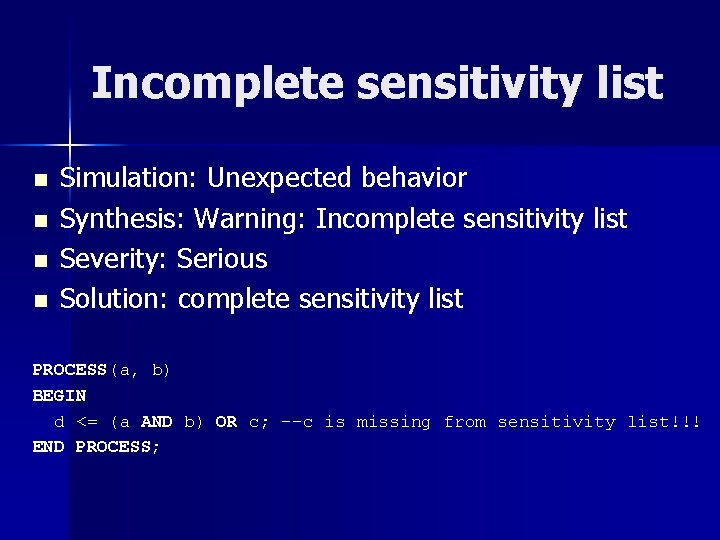

Incomplete sensitivity list n n Simulation: Unexpected behavior Synthesis: Warning: Incomplete sensitivity list Severity: Serious Solution: complete sensitivity list PROCESS(a, b) BEGIN d <= (a AND b) OR c; --c is missing from sensitivity list!!! END PROCESS;

Not assigning all outputs in combinational process n n Simulation: Synthesis: Warning: Signal not always assigned, storage may be needed Severity: Serious Solution: assign all signals PROCESS(a, b, c) BEGIN if c = ‘ 0’ then d <= (a AND b) OR c; --d assigned only first time, else e <= a; --e assigned only second time!!! END PROCESS;

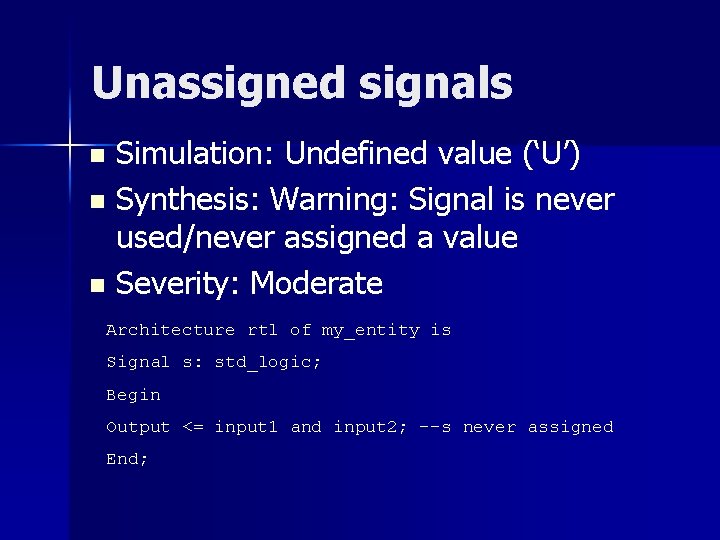

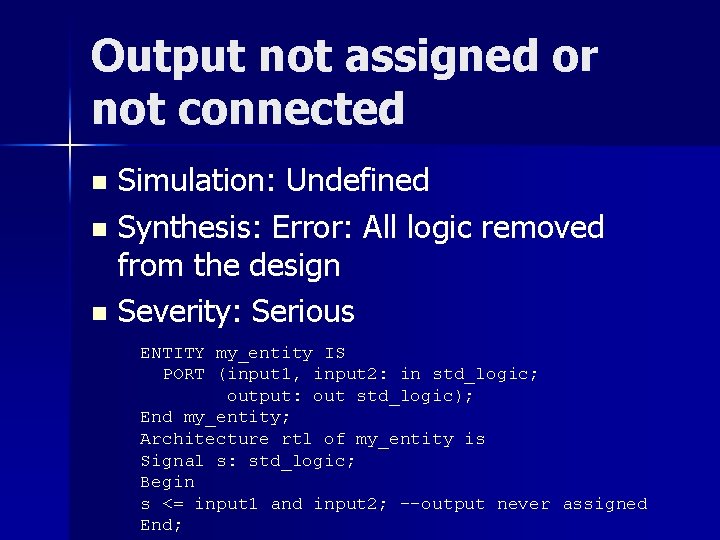

Unassigned signals Simulation: Undefined value (‘U’) n Synthesis: Warning: Signal is never used/never assigned a value n Severity: Moderate n Architecture rtl of my_entity is Signal s: std_logic; Begin Output <= input 1 and input 2; --s never assigned End;

Output not assigned or not connected Simulation: Undefined n Synthesis: Error: All logic removed from the design n Severity: Serious n ENTITY my_entity IS PORT (input 1, input 2: in std_logic; output: out std_logic); End my_entity; Architecture rtl of my_entity is Signal s: std_logic; Begin s <= input 1 and input 2; --output never assigned End;

Using sequential instead of concurrent process Simulation: Unexpectedly delayed signals n Synthesis: More FFs than expected n