VHDL Data Type l Scaler Type l Enumeration

![Concurrent(Block) l Syntex block_name : block (동작 제한식) [generic (generic_list); ] [port (port_list); ] Concurrent(Block) l Syntex block_name : block (동작 제한식) [generic (generic_list); ] [port (port_list); ]](https://slidetodoc.com/presentation_image/4aa6f098779bfc7488ee8d5f6fd176bb/image-23.jpg)

- Slides: 33

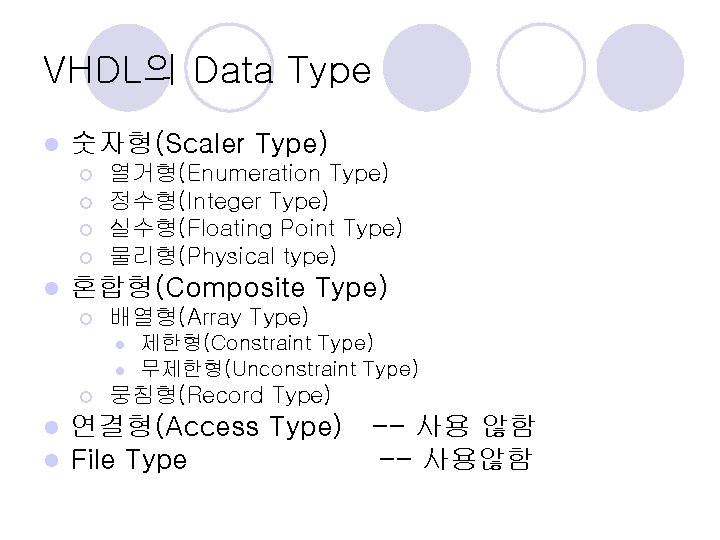

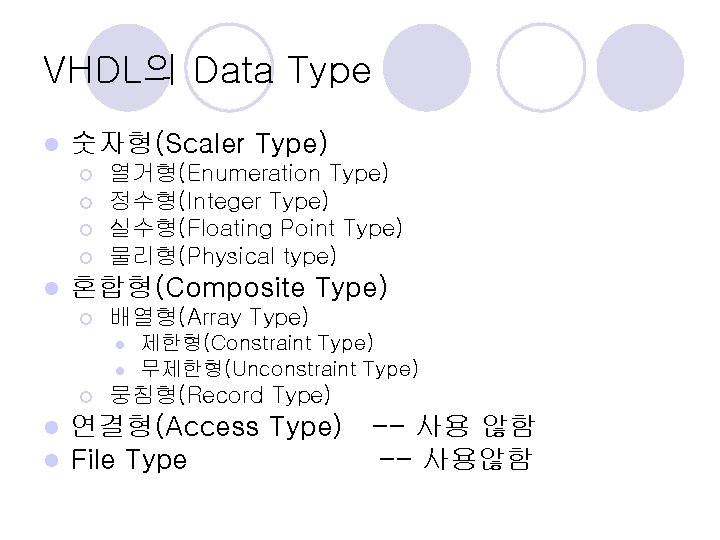

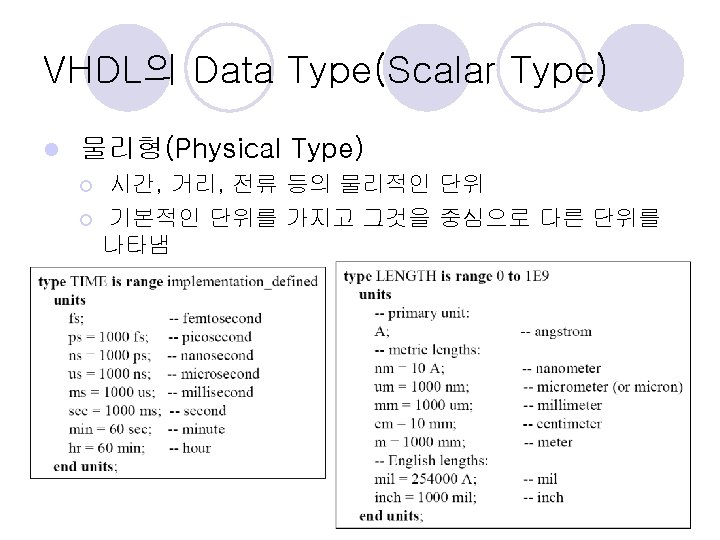

VHDL의 Data Type l 숫자형(Scaler Type) ¡ ¡ l 열거형(Enumeration Type) 정수형(Integer Type) 실수형(Floating Point Type) 물리형(Physical type) 혼합형(Composite Type) ¡ 배열형(Array Type) l l ¡ l l 제한형(Constraint Type) 무제한형(Unconstraint Type) 뭉침형(Record Type) 연결형(Access Type) -- 사용 않함 File Type -- 사용않함

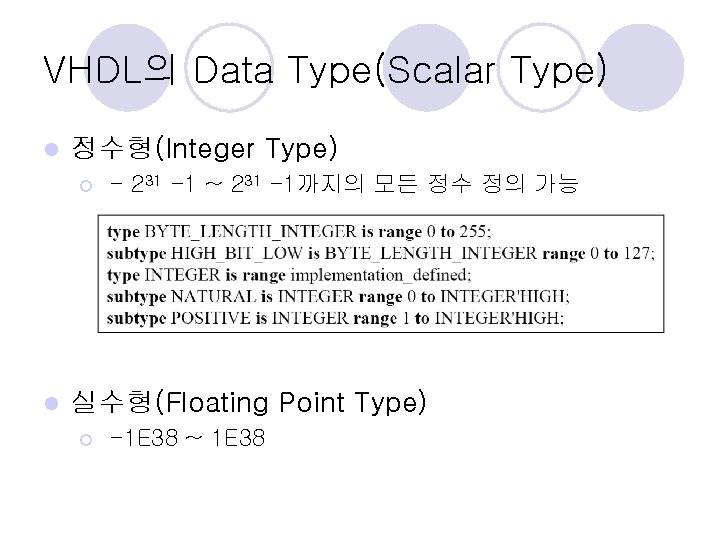

VHDL의 Data Type(Scalar Type) l 정수형(Integer Type) ¡ l - 231 -1 ~ 231 -1까지의 모든 정수 정의 가능 실수형(Floating Point Type) ¡ -1 E 38 ~ 1 E 38

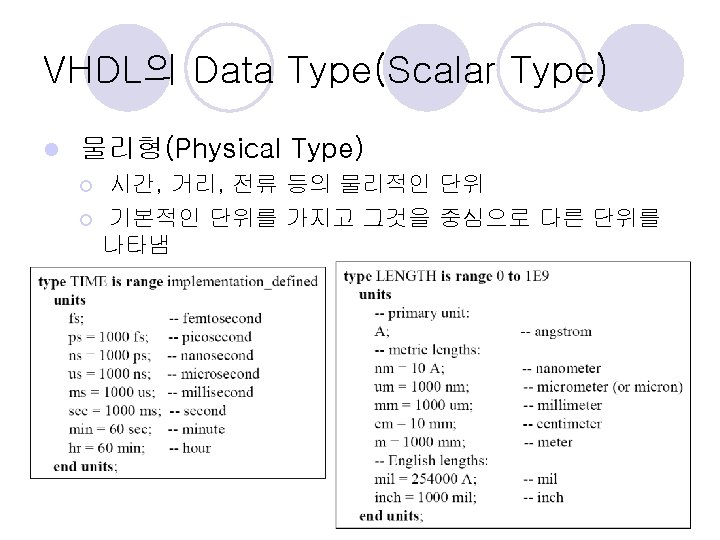

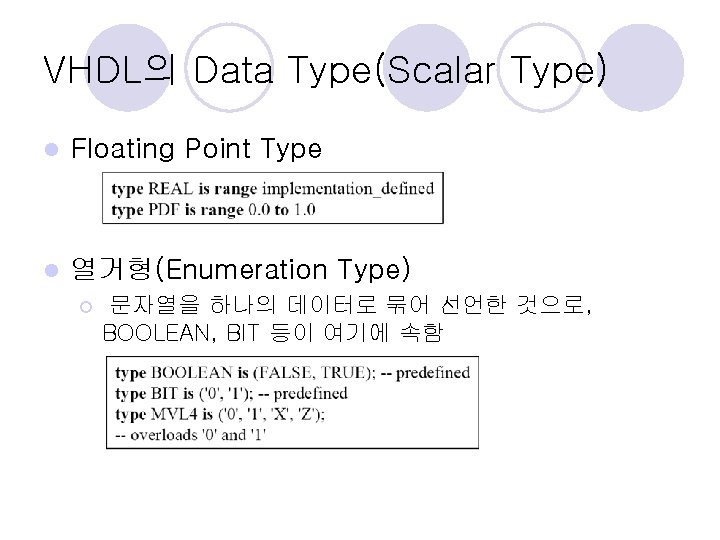

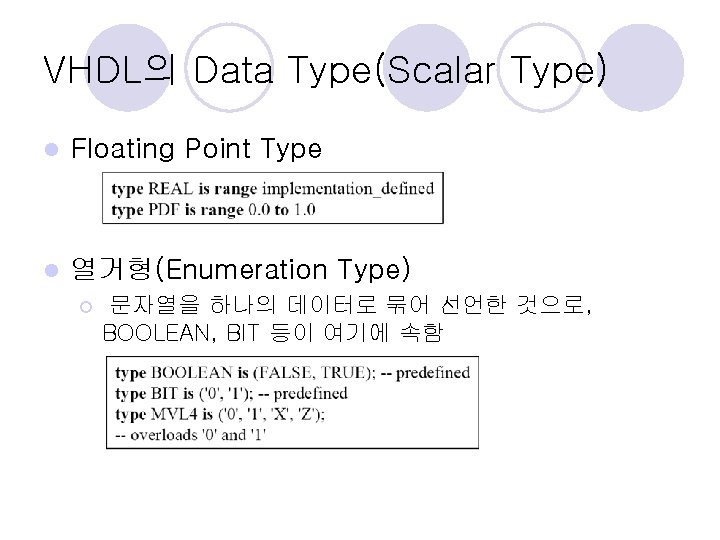

VHDL의 Data Type(Scalar Type) l Floating Point Type l 열거형(Enumeration Type) ¡ 문자열을 하나의 데이터로 묶어 선언한 것으로, BOOLEAN, BIT 등이 여기에 속함

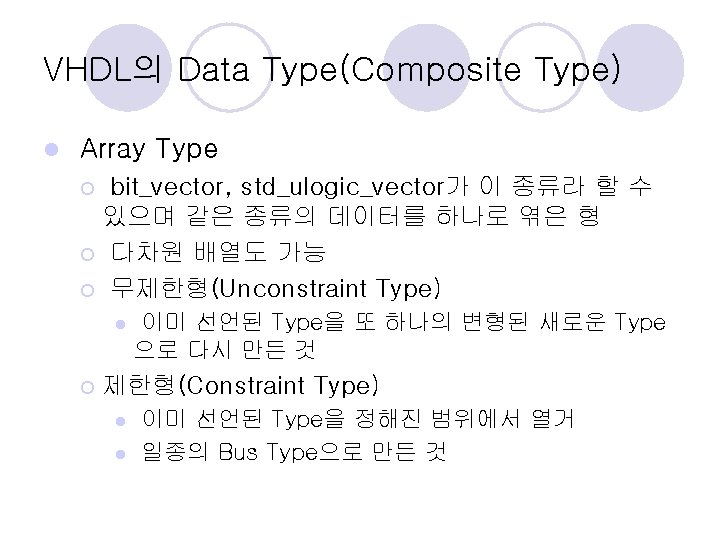

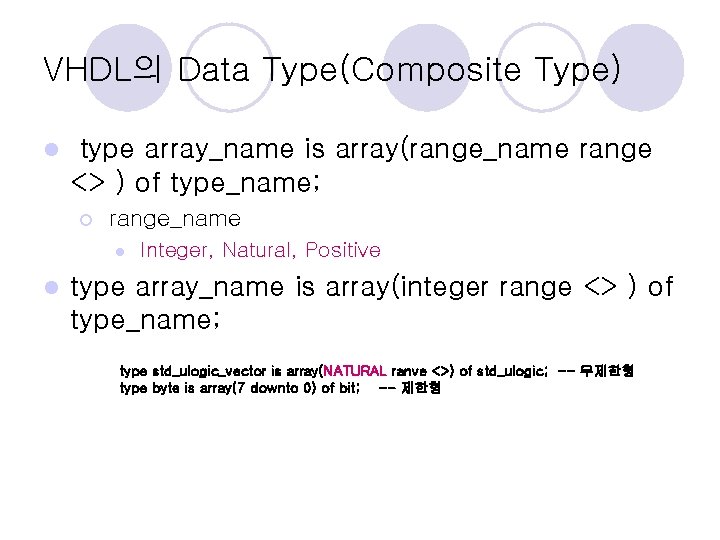

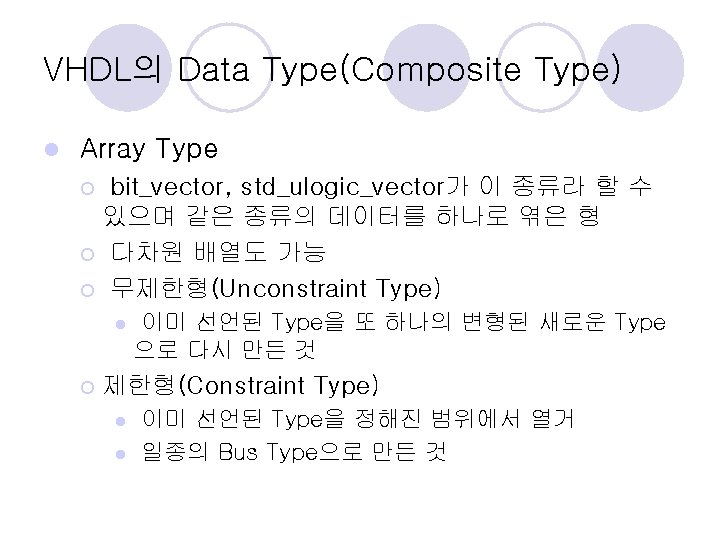

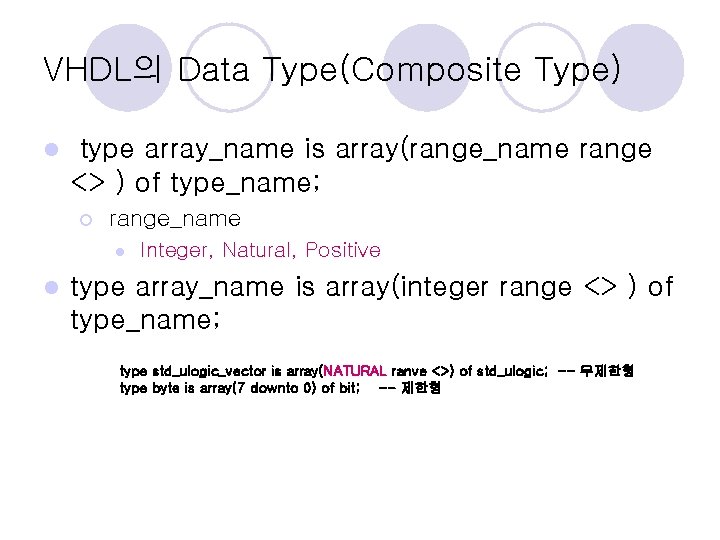

VHDL의 Data Type(Composite Type) l type array_name is array(range_name range <> ) of type_name; ¡ range_name l l Integer, Natural, Positive type array_name is array(integer range <> ) of type_name; type std_ulogic_vector is array(NATURAL ranve <>) of std_ulogic; -- 무제한형 type byte is array(7 downto 0) of bit; -- 제한형

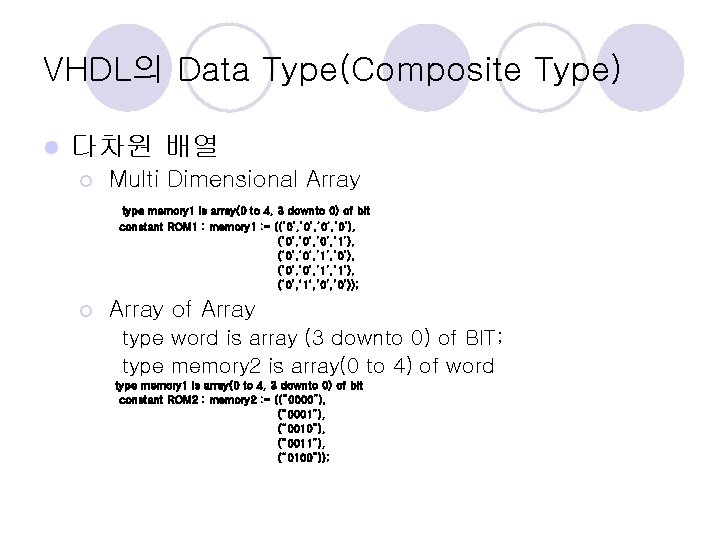

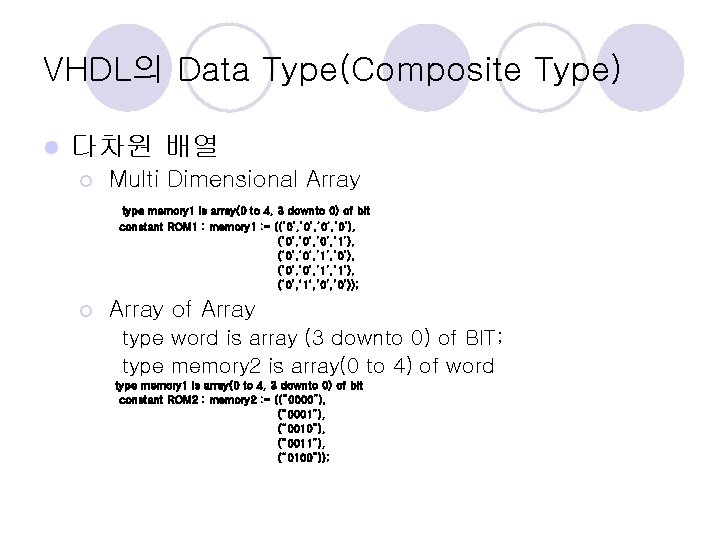

VHDL의 Data Type(Composite Type) l 다차원 배열 ¡ Multi Dimensional Array type memory 1 is array(0 to 4, 3 downto 0) of bit constant ROM 1 : memory 1 : = ((‘ 0’, ’ 0’), (‘ 0’, ’ 1’), (‘ 0’, ’ 1’, ’ 0’), (‘ 0’, ’ 1’, ’ 1’), (‘ 0’, ’ 1’, ’ 0’)); ¡ Array of Array type word is array (3 downto 0) of BIT; type memory 2 is array(0 to 4) of word type memory 1 is array(0 to 4, 3 downto 0) of bit constant ROM 2 : memory 2 : = ((“ 0000”), (“ 0001”), (“ 0010”), (“ 0011”), (“ 0100”));

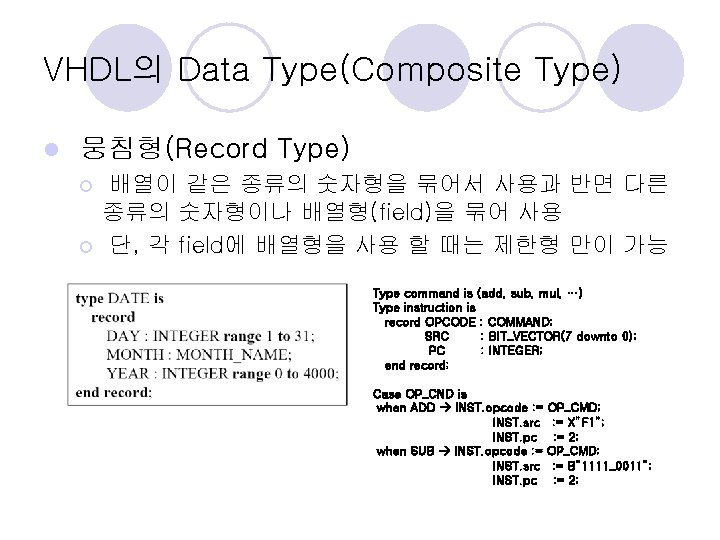

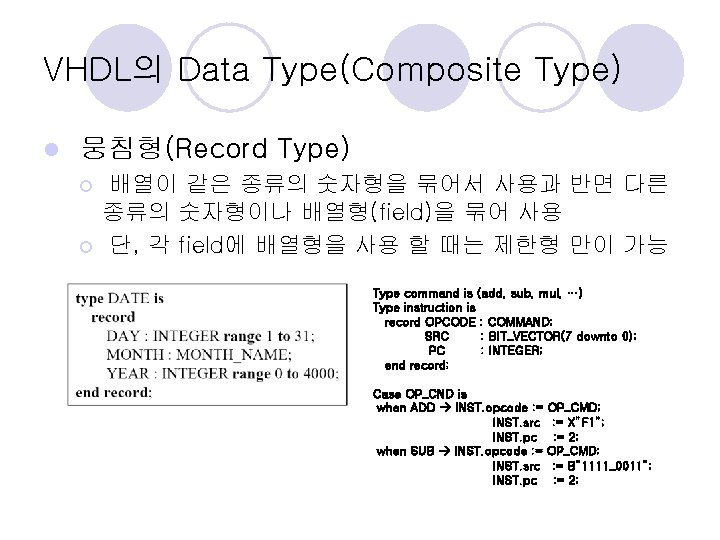

VHDL의 Data Type(Composite Type) l 뭉침형(Record Type) ¡ ¡ 배열이 같은 종류의 숫자형을 묶어서 사용과 반면 다른 종류의 숫자형이나 배열형(field)을 묶어 사용 단, 각 field에 배열형을 사용 할 때는 제한형 만이 가능 Type command is (add, sub, mul, …) Type instruction is record OPCODE : COMMAND; SRC : BIT_VECTOR(7 downto 0); PC : INTEGER; end record; Case OP_CND is when ADD INST. opcode : = OP_CMD; INST. src : = X”F 1”; INST. pc : = 2; when SUB INST. opcode : = OP_CMD; INST. src : = B” 1111_0011”; INST. pc : = 2;

VHDL의 Data Type(Composite Type) l File type ¡ ¡ 외부와의 입출력이나 특정 File의 변수를 선언 VHDL Package의 TEXTIO 부분에 선언 회로에 대한 검증단계에서 많이 사용됨 type TEXT is file of STRING

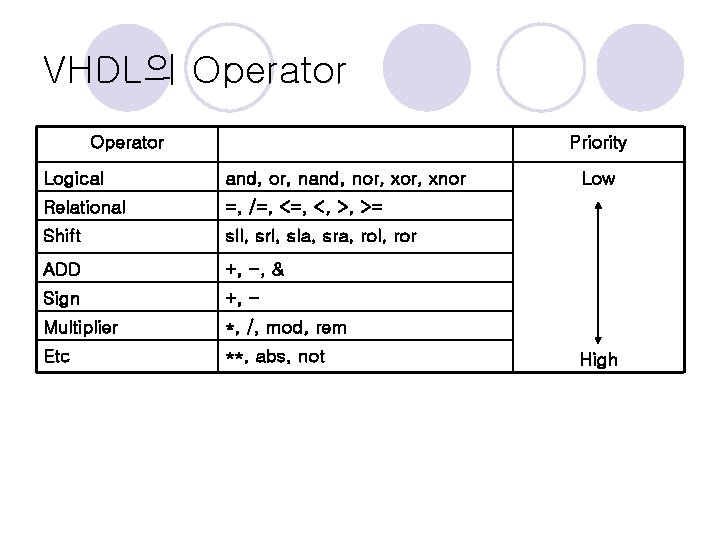

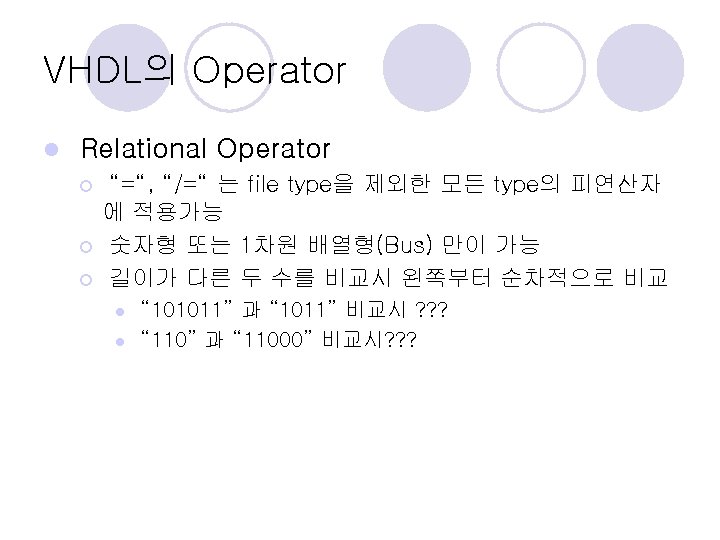

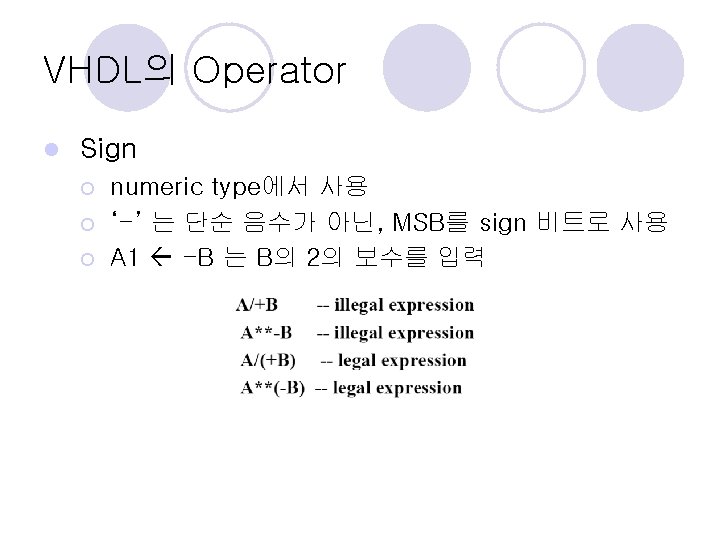

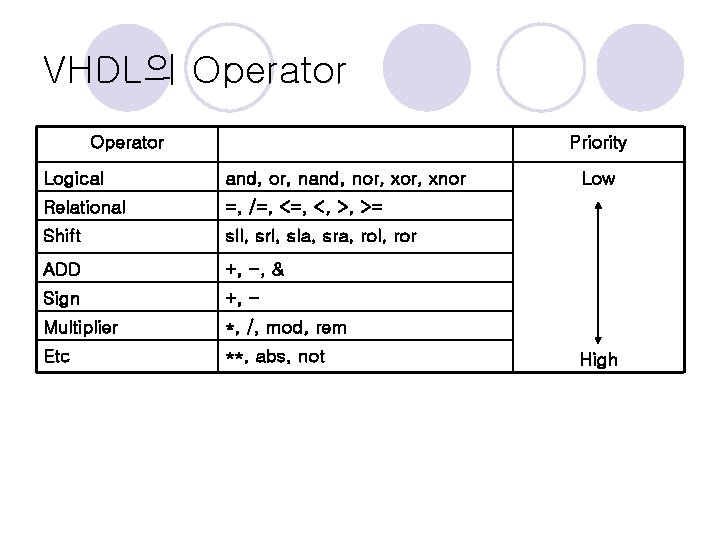

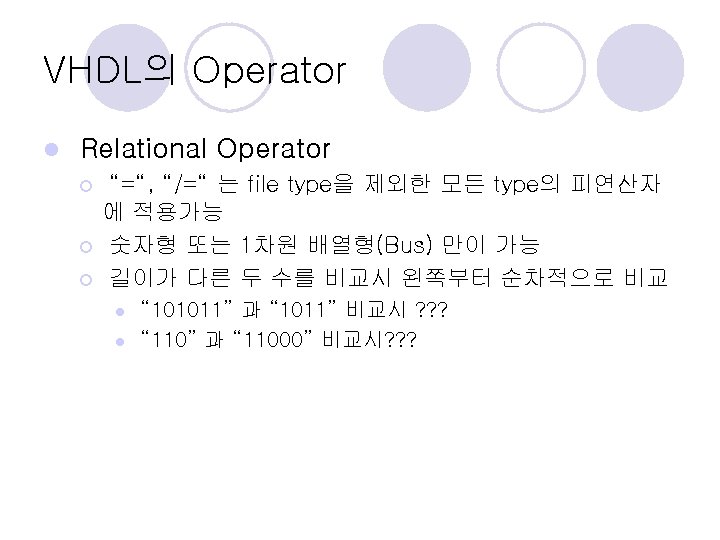

VHDL의 Operator Priority Logical and, or, nand, nor, xnor Relational =, /=, <, >, >= Shift sll, srl, sla, sra, rol, ror ADD +, -, & Sign +, - Multiplier *, /, mod, rem Etc **, abs, not Low High

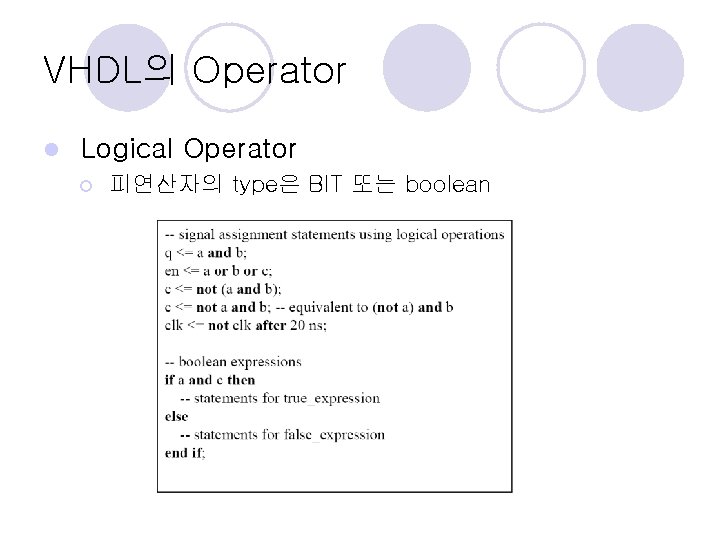

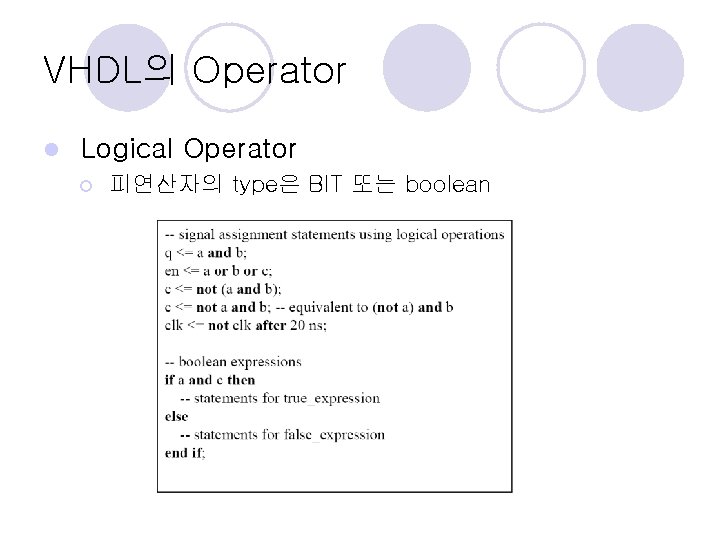

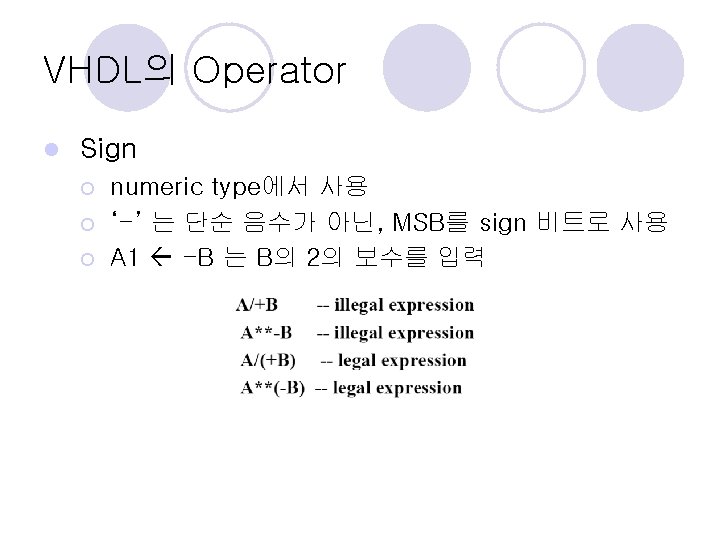

VHDL의 Operator l Logical Operator ¡ 피연산자의 type은 BIT 또는 boolean

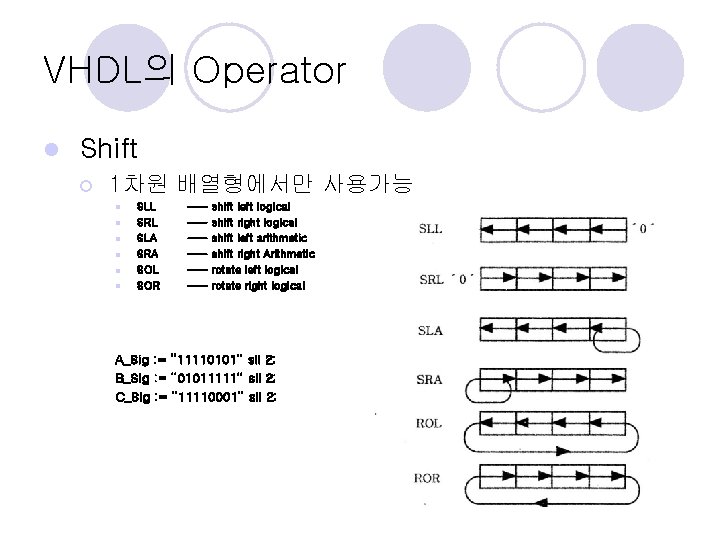

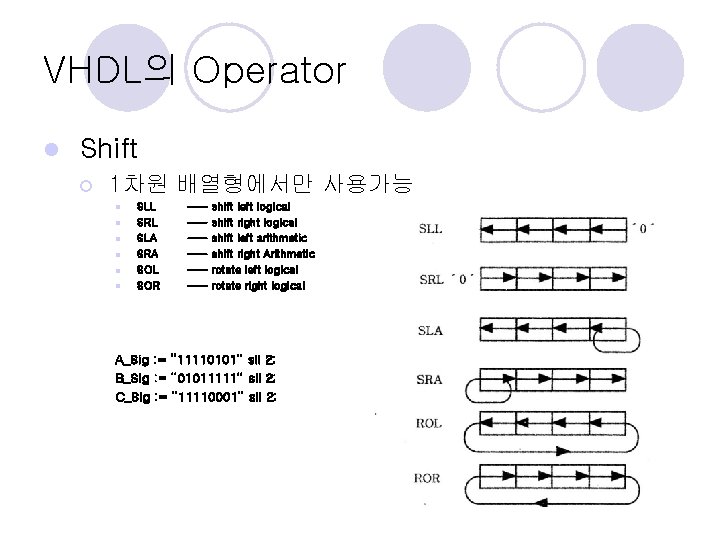

VHDL의 Operator l Shift ¡ 1차원 배열형에서만 사용가능 l l l SLL SRL SLA SRA SOL SOR ------- shift left logical shift right logical shift left arithmetic shift right Arithmetic rotate left logical rotate right logical A_Sig : = “ 11110101” sll 2; B_Sig : = “ 01011111” sll 2; C_Sig : = “ 11110001” sll 2;

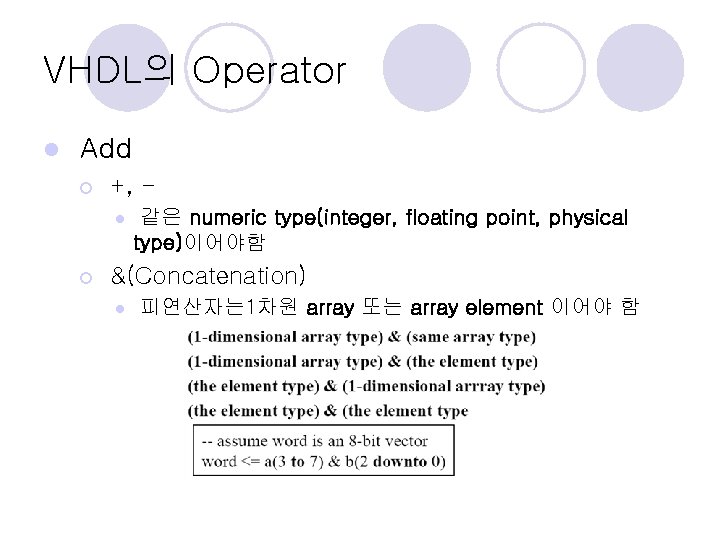

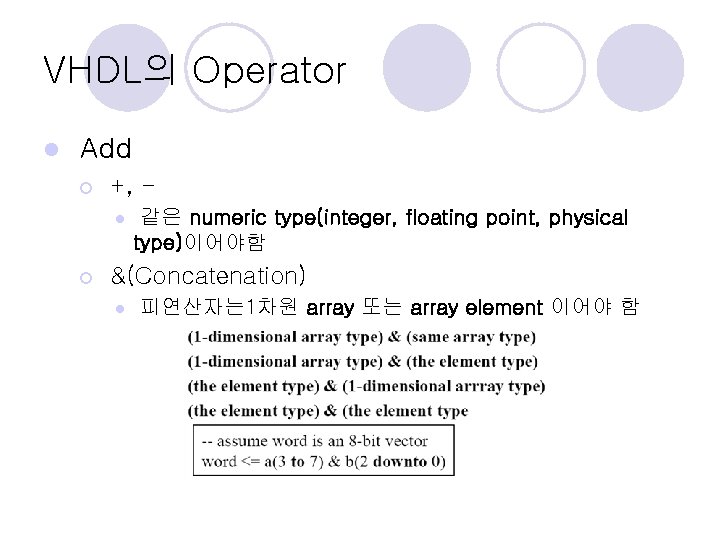

VHDL의 Operator l Add ¡ +, l ¡ 같은 numeric type(integer, floating point, physical type)이어야함 &(Concatenation) l 피연산자는 1차원 array 또는 array element 이어야 함

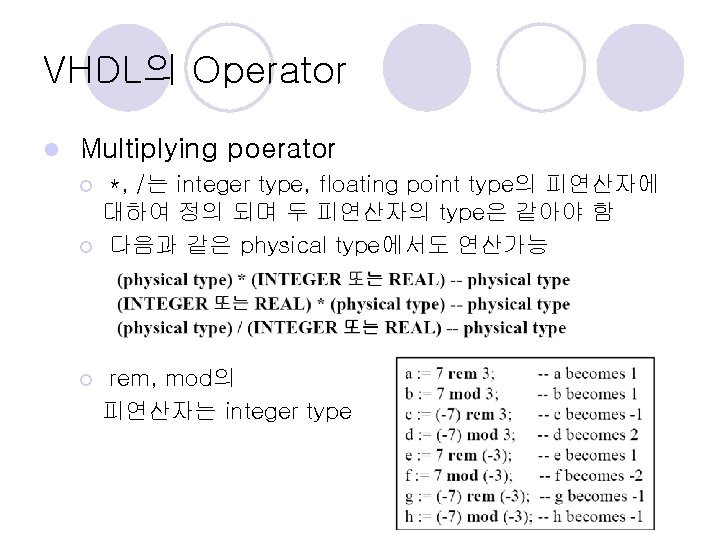

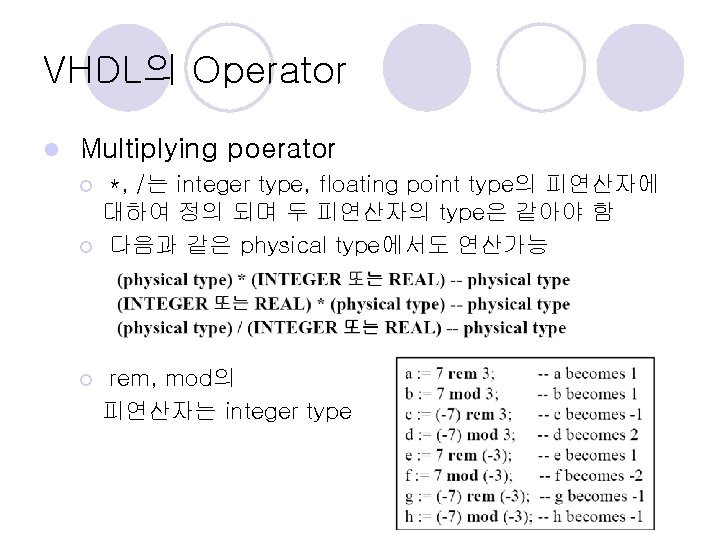

VHDL의 Operator l Multiplying poerator ¡ ¡ ¡ *, /는 integer type, floating point type의 피연산자에 대하여 정의 되며 두 피연산자의 type은 같아야 함 다음과 같은 physical type에서도 연산가능 rem, mod의 피연산자는 integer type

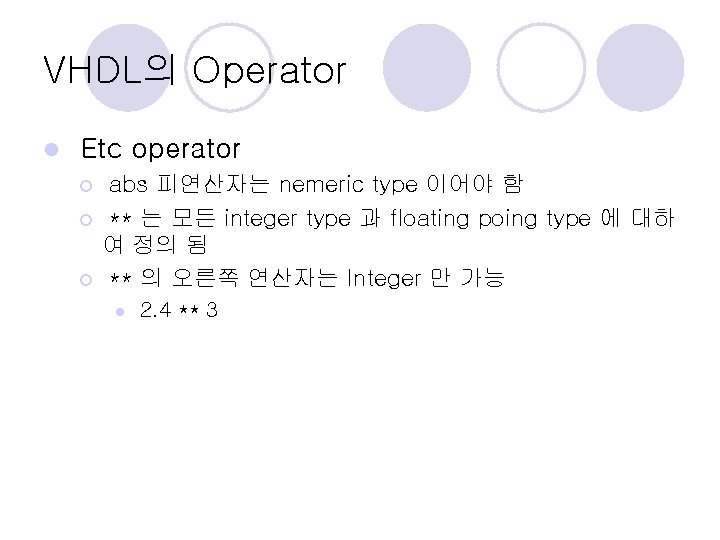

VHDL의 Operator l Etc operator ¡ ¡ ¡ abs 피연산자는 nemeric type 이어야 함 ** 는 모든 integer type 과 floating poing type 에 대하 여 정의 됨 ** 의 오른쪽 연산자는 Integer 만 가능 l 2. 4 ** 3

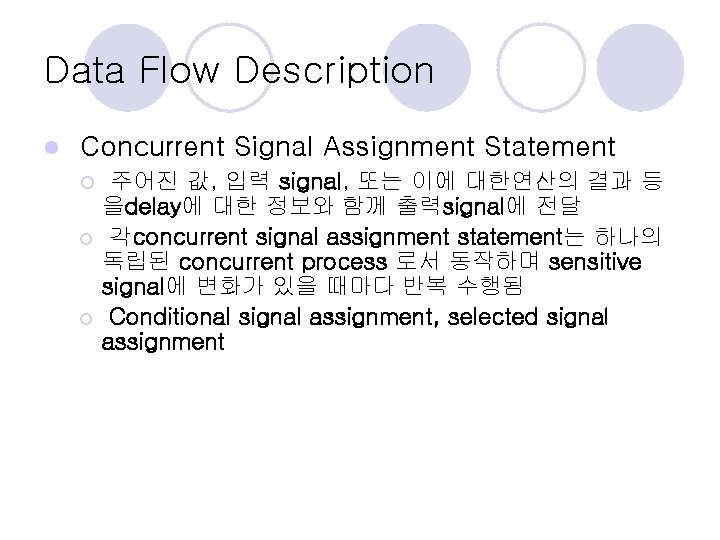

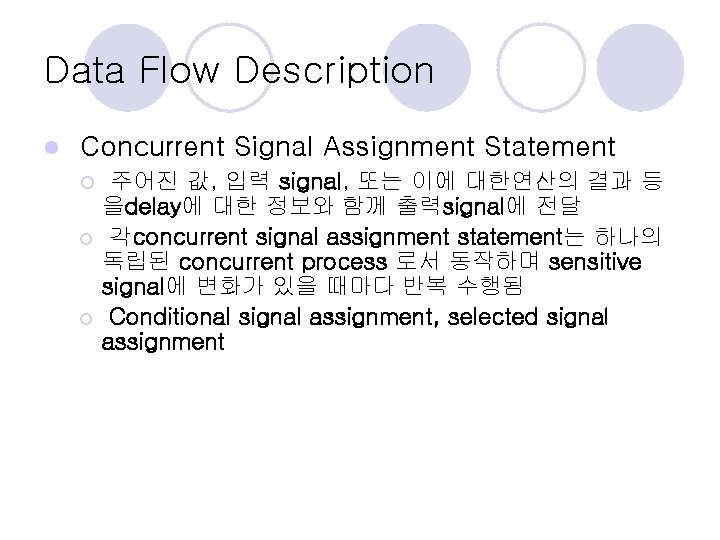

Data Flow Description l Concurrent Signal Assignment Statement ¡ ¡ ¡ 주어진 값, 입력 signal, 또는 이에 대한연산의 결과 등 을delay에 대한 정보와 함께 출력signal에 전달 각concurrent signal assignment statement는 하나의 독립된 concurrent process 로서 동작하며 sensitive signal에 변화가 있을 때마다 반복 수행됨 Conditional signal assignment, selected signal assignment

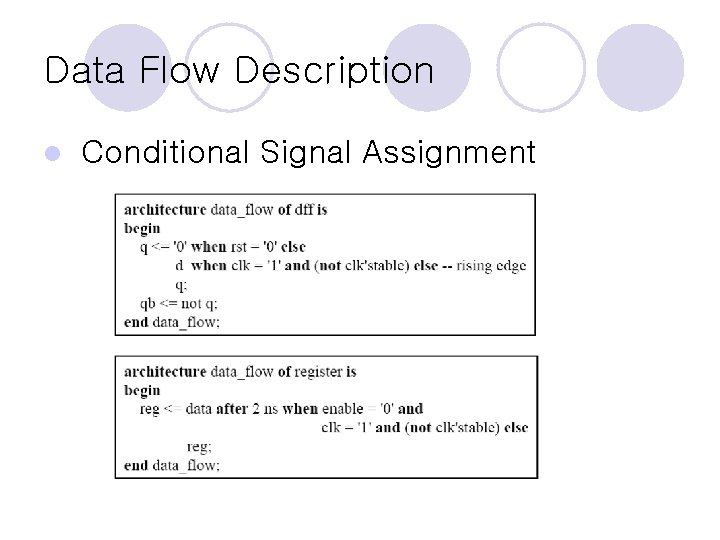

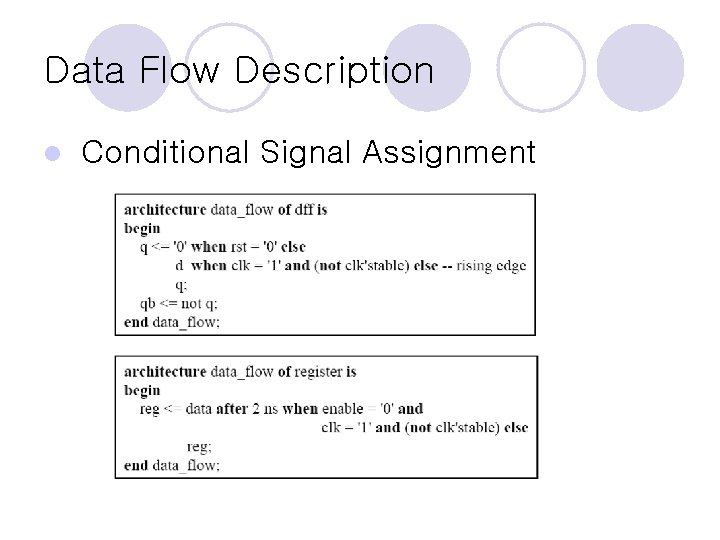

Data Flow Description l Conditional Signal Assignment

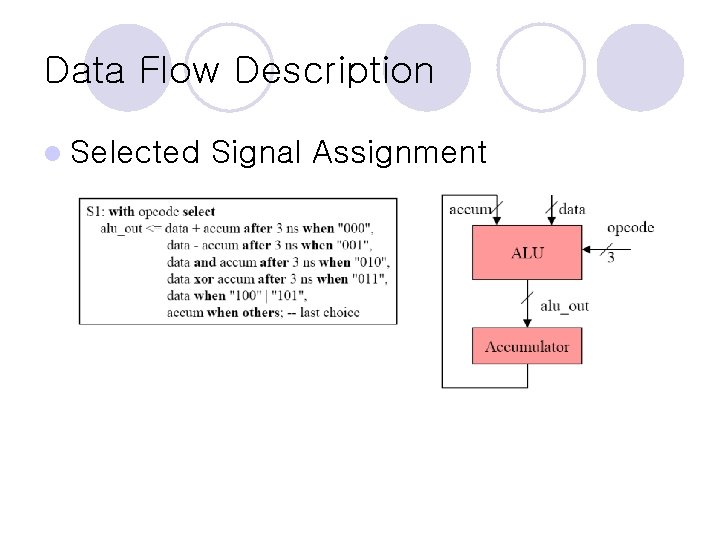

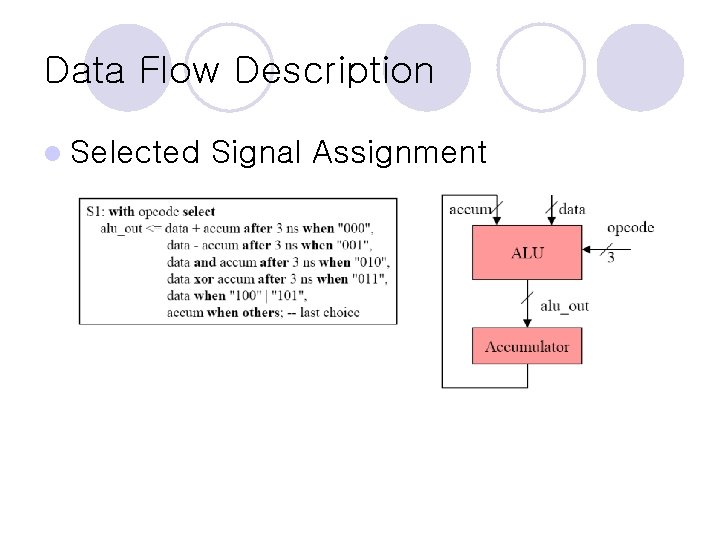

Data Flow Description l Selected Signal Assignment

![ConcurrentBlock l Syntex blockname block 동작 제한식 generic genericlist port portlist Concurrent(Block) l Syntex block_name : block (동작 제한식) [generic (generic_list); ] [port (port_list); ]](https://slidetodoc.com/presentation_image/4aa6f098779bfc7488ee8d5f6fd176bb/image-23.jpg)

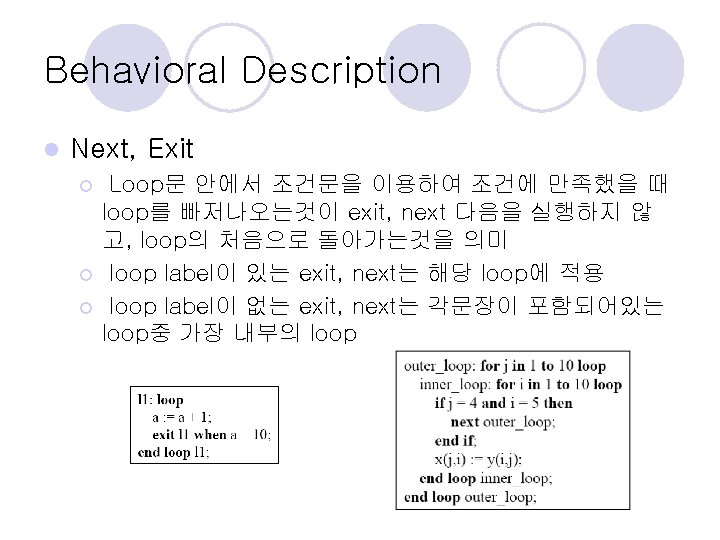

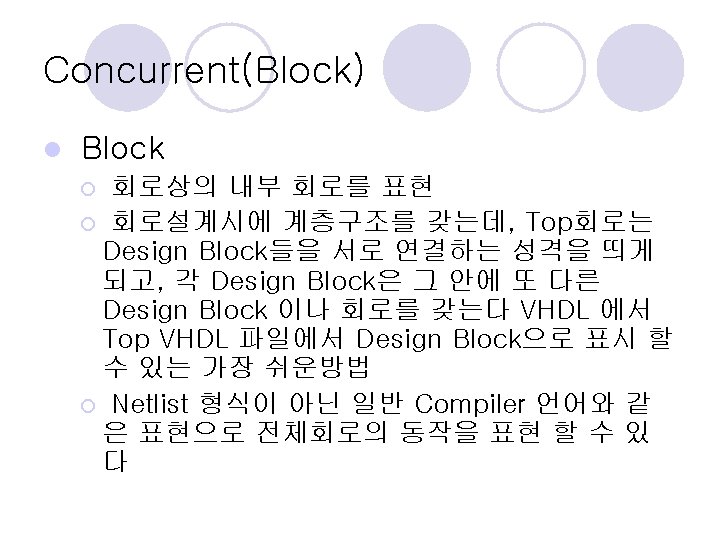

Concurrent(Block) l Syntex block_name : block (동작 제한식) [generic (generic_list); ] [port (port_list); ] begin Concurrent 문 end block[Block_name] Ex) B 1: block(EMB = ‘ 0’) signal S : bit; begin S <= A and B; B 2: block signal S: bit; begin S <= C or D; out 1 <= S; end block B 2; out 2 <= S; end block B 1;

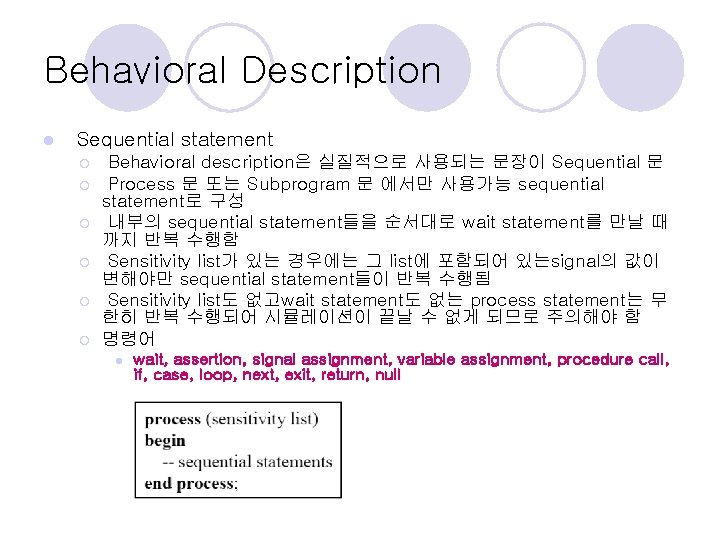

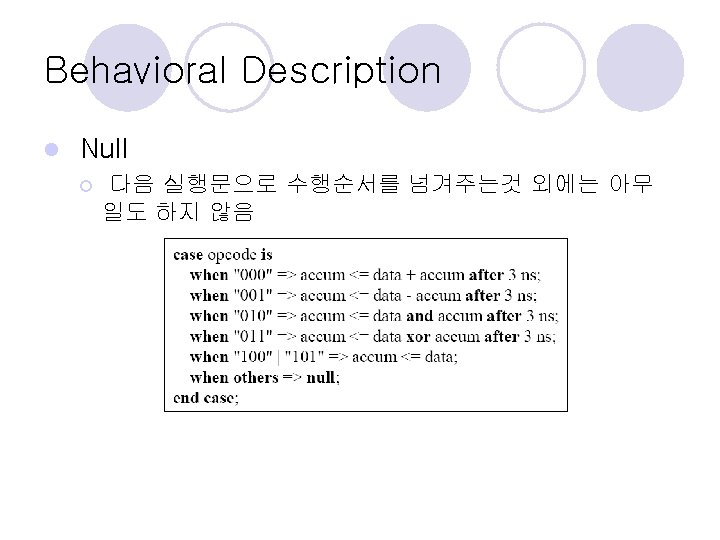

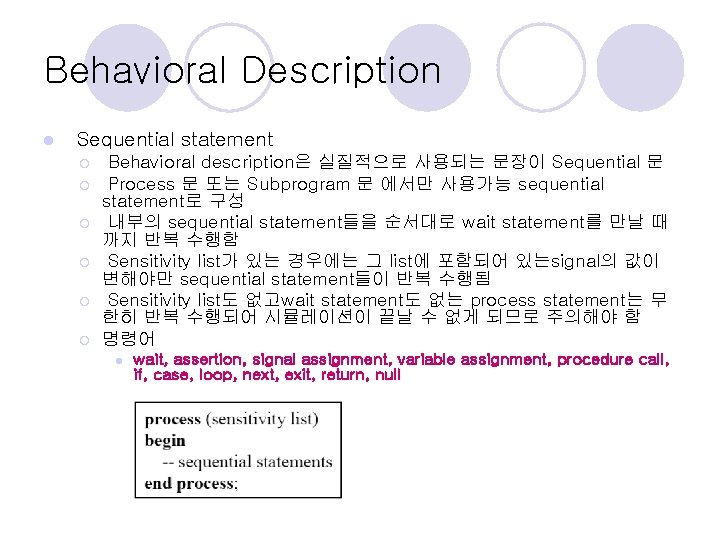

Behavioral Description l Sequential statement ¡ ¡ ¡ Behavioral description은 실질적으로 사용되는 문장이 Sequential 문 Process 문 또는 Subprogram 문 에서만 사용가능 sequential statement로 구성 내부의 sequential statement들을 순서대로 wait statement를 만날 때 까지 반복 수행함 Sensitivity list가 있는 경우에는 그 list에 포함되어 있는signal의 값이 변해야만 sequential statement들이 반복 수행됨 Sensitivity list도 없고wait statement도 없는 process statement는 무 한히 반복 수행되어 시뮬레이션이 끝날 수 없게 되므로 주의해야 함 명령어 l wait, assertion, signal assignment, variable assignment, procedure call, if, case, loop, next, exit, return, null

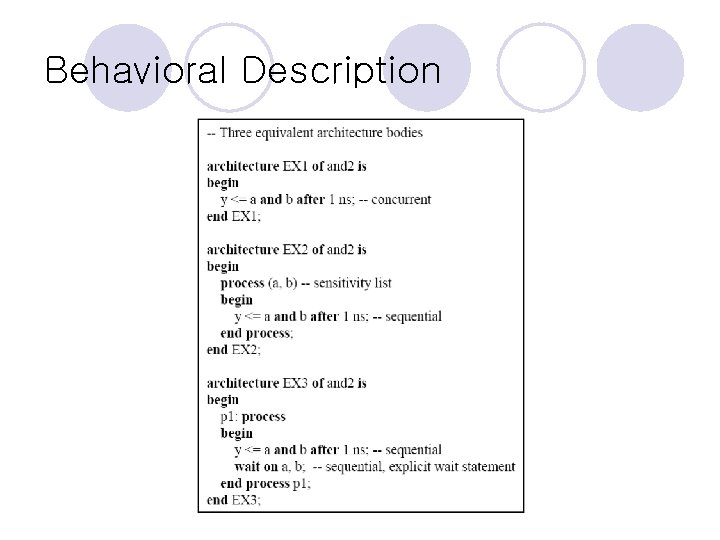

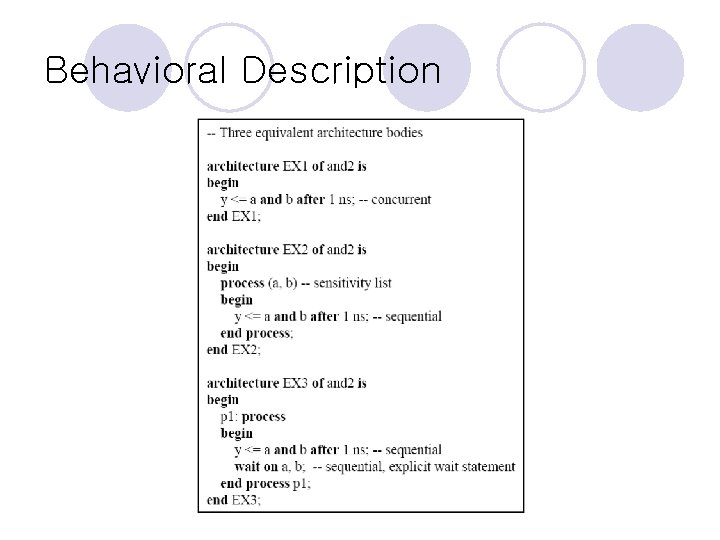

Behavioral Description

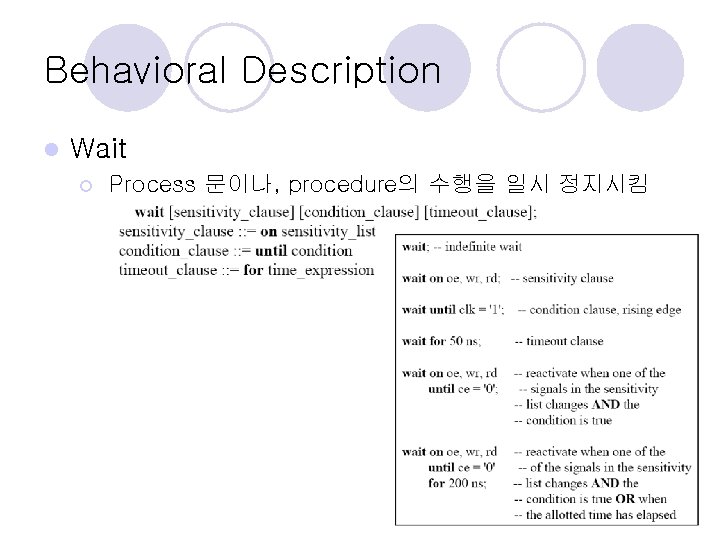

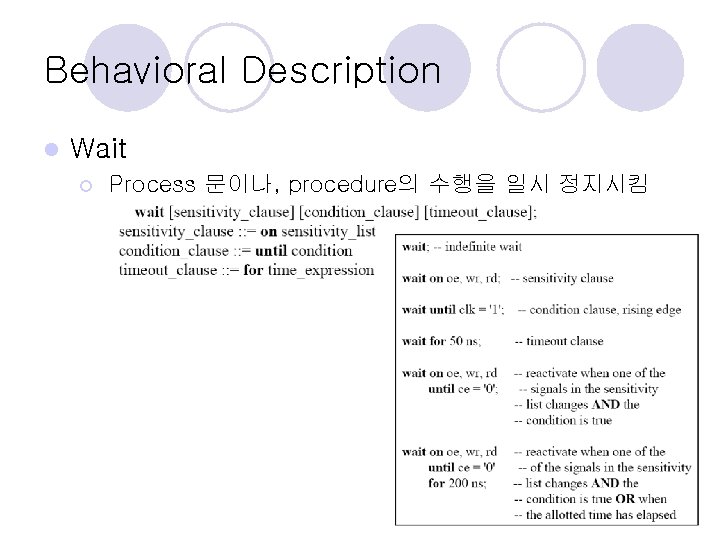

Behavioral Description l Wait ¡ Process 문이나, procedure의 수행을 일시 정지시킴

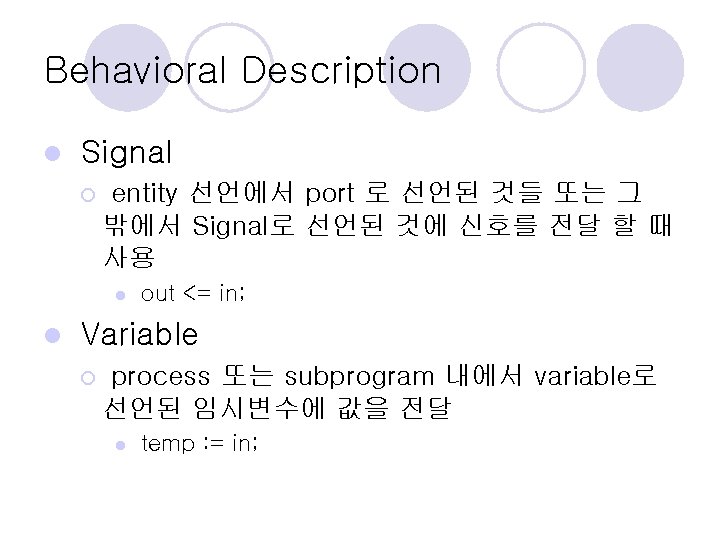

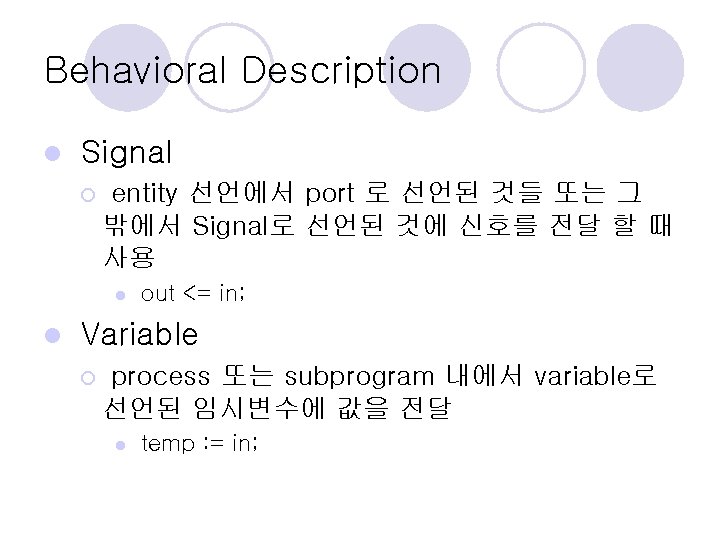

Behavioral Description l Signal ¡ entity 선언에서 port 로 선언된 것들 또는 그 밖에서 Signal로 선언된 것에 신호를 전달 할 때 사용 l l out <= in; Variable ¡ process 또는 subprogram 내에서 variable로 선언된 임시변수에 값을 전달 l temp : = in;

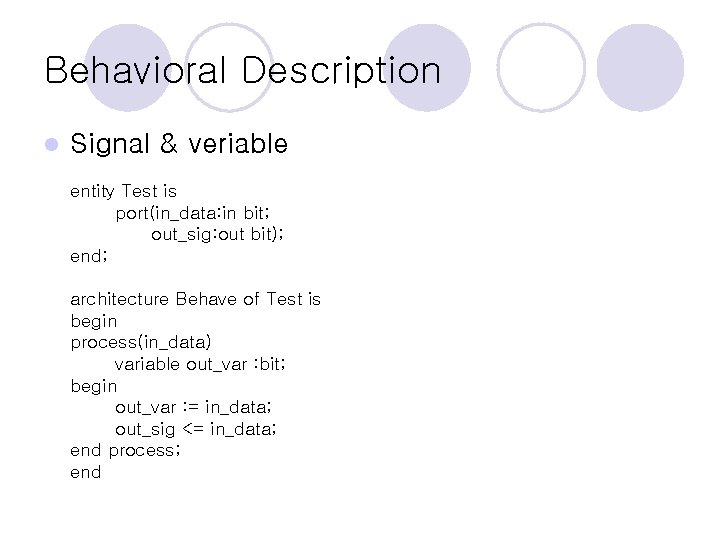

Behavioral Description l Signal & veriable entity Test is port(in_data: in bit; out_sig: out bit); end; architecture Behave of Test is begin process(in_data) variable out_var : bit; begin out_var : = in_data; out_sig <= in_data; end process; end

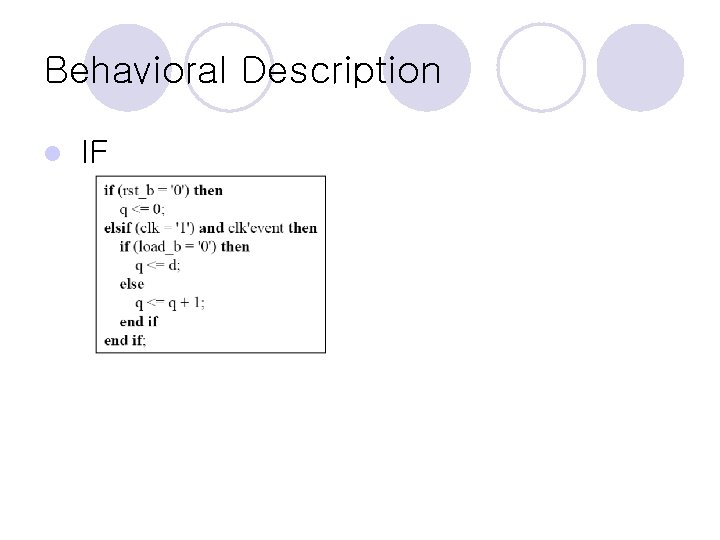

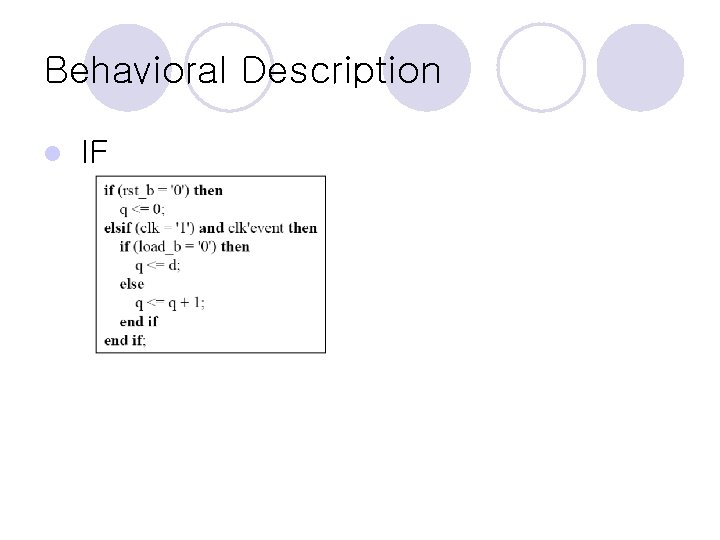

Behavioral Description l IF

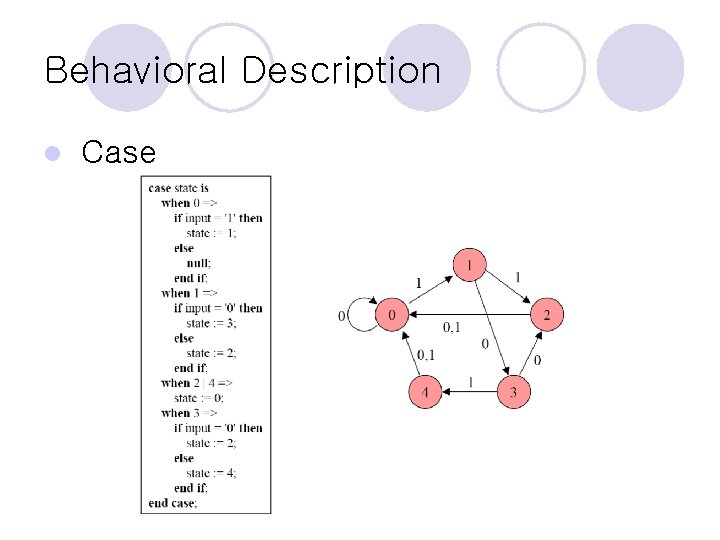

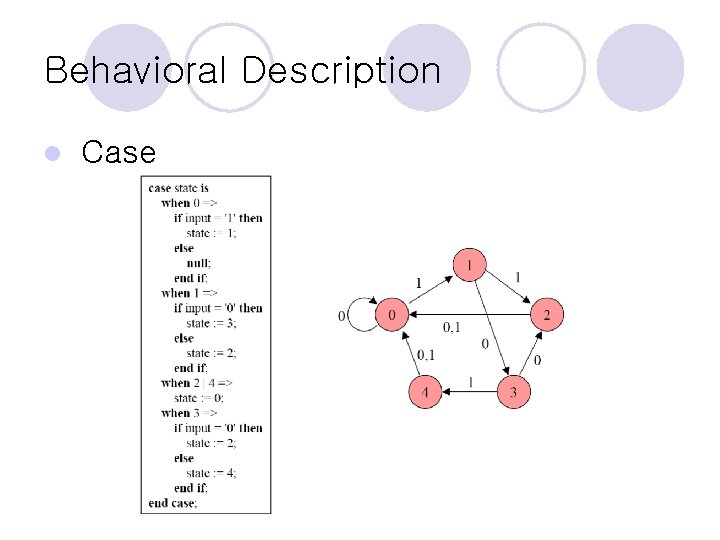

Behavioral Description l Case

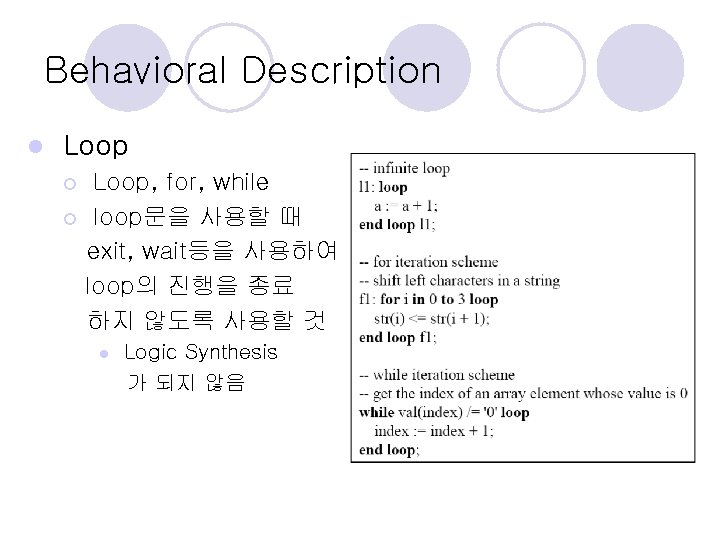

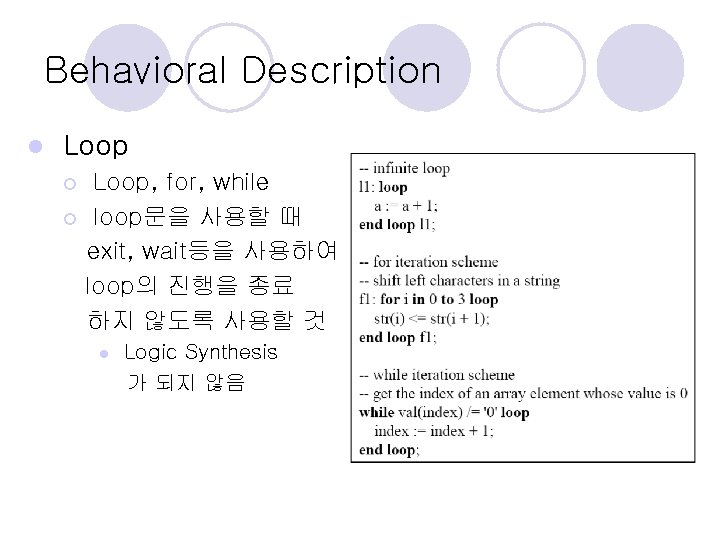

Behavioral Description l Loop, for, while ¡ loop문을 사용할 때 exit, wait등을 사용하여 loop의 진행을 종료 하지 않도록 사용할 것 ¡ l Logic Synthesis 가 되지 않음