VHDL code for basic digital circuits using data

VHDL code for basic digital circuits using data flow modelling The VHDL code is written for following circuits • AND Gate • OR Gate • Half Adder • Full adder • 2: 1 MUX • 4: 1 MUX • 8: 1 MUX • 1: 2 DEMUX • 1: 4 DEMUX • 1: 8 DEMUX

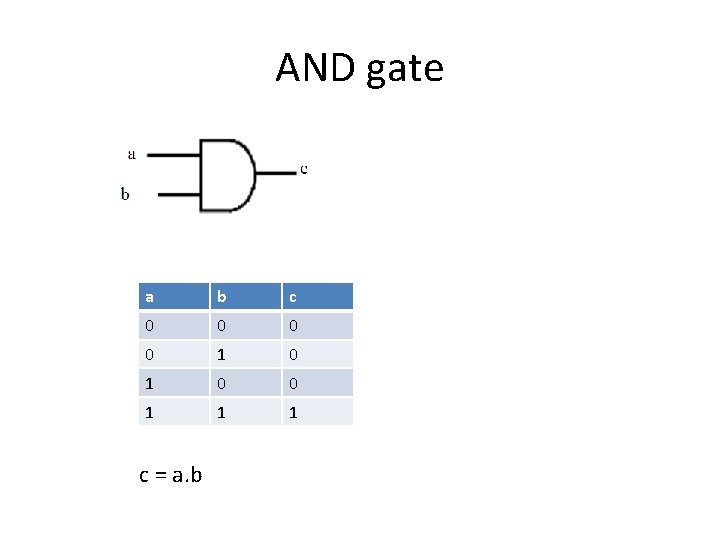

AND gate a b c 0 0 1 1 1 c = a. b

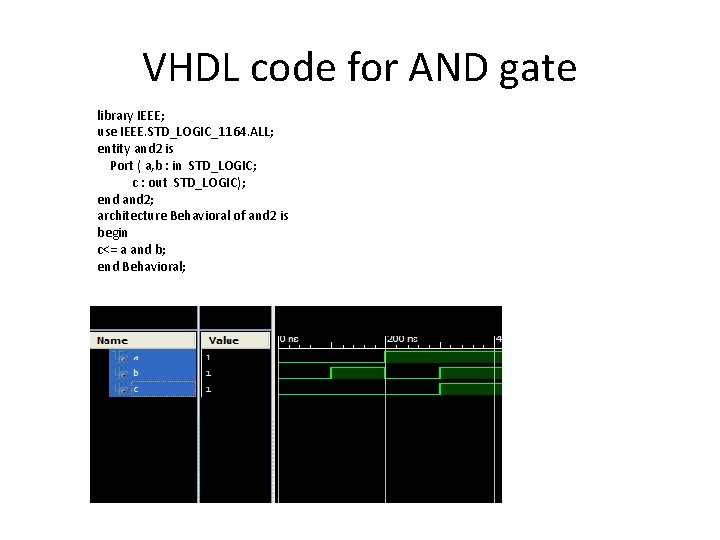

VHDL code for AND gate library IEEE; use IEEE. STD_LOGIC_1164. ALL; entity and 2 is Port ( a, b : in STD_LOGIC; c : out STD_LOGIC); end and 2; architecture Behavioral of and 2 is begin c<= a and b; end Behavioral;

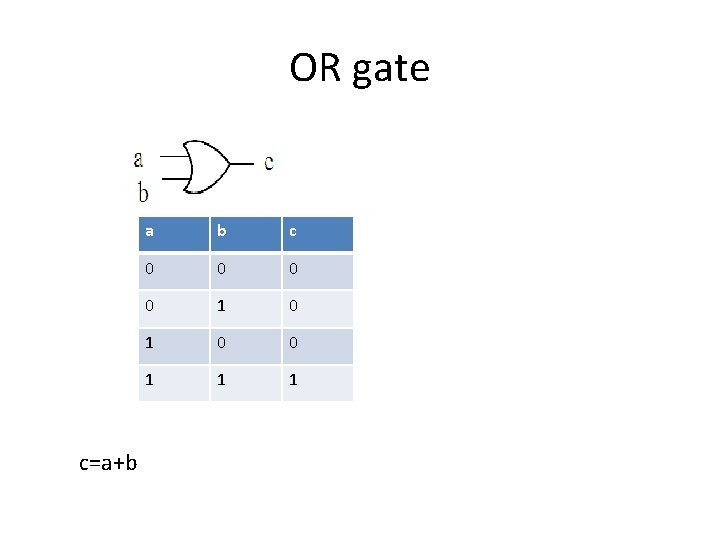

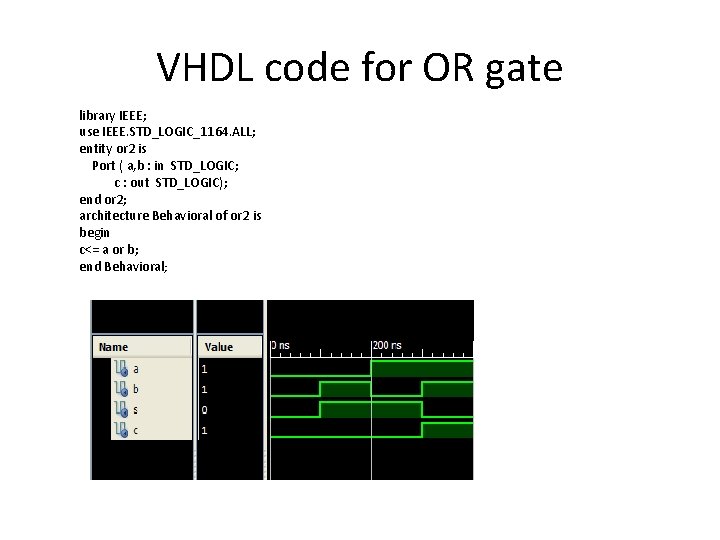

OR gate c=a+b a b c 0 0 1 1 1

VHDL code for OR gate library IEEE; use IEEE. STD_LOGIC_1164. ALL; entity or 2 is Port ( a, b : in STD_LOGIC; c : out STD_LOGIC); end or 2; architecture Behavioral of or 2 is begin c<= a or b; end Behavioral;

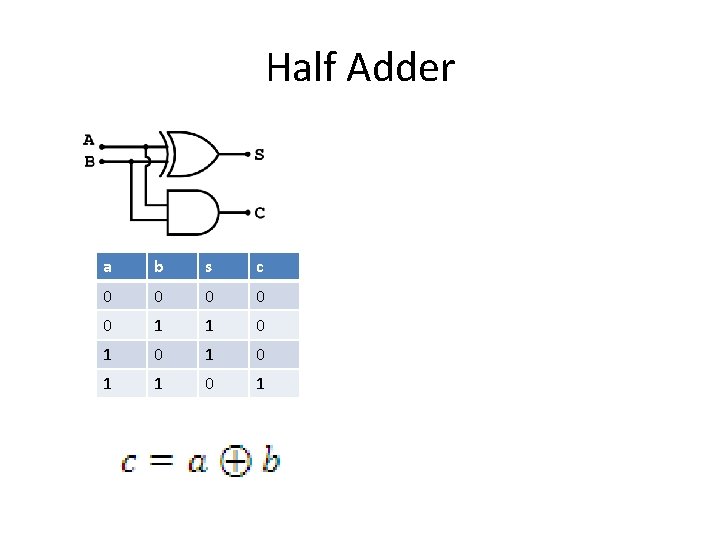

Half Adder a b s c 0 0 0 1 1 0 1 0 1

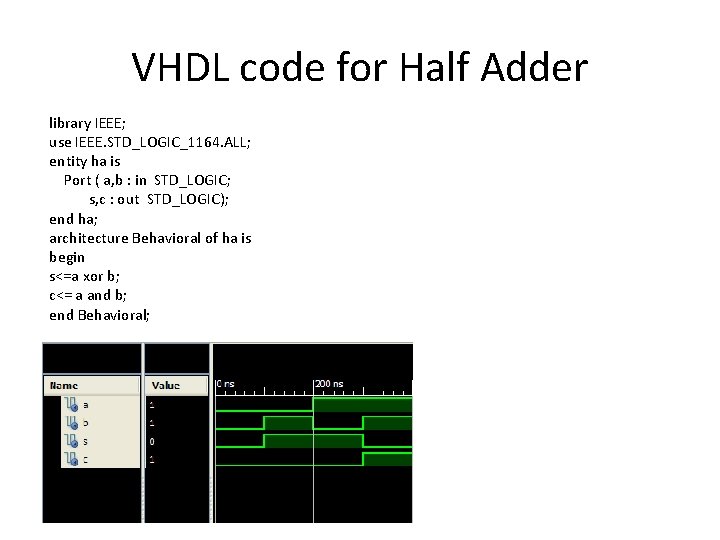

VHDL code for Half Adder library IEEE; use IEEE. STD_LOGIC_1164. ALL; entity ha is Port ( a, b : in STD_LOGIC; s, c : out STD_LOGIC); end ha; architecture Behavioral of ha is begin s<=a xor b; c<= a and b; end Behavioral;

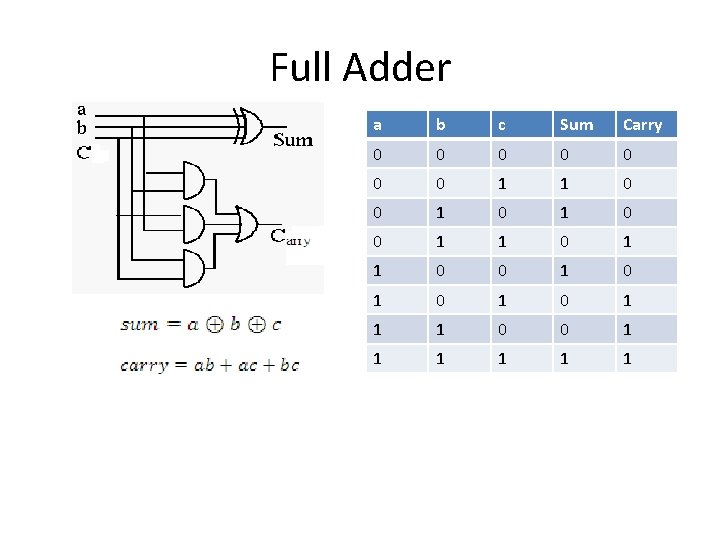

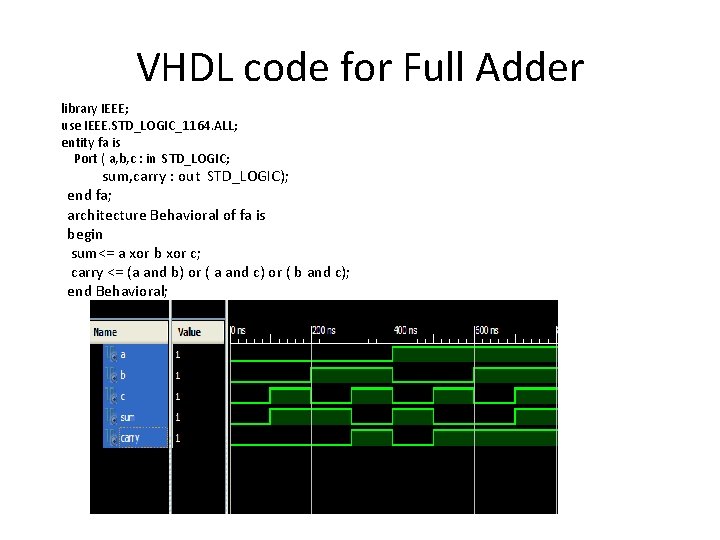

Full Adder a b c Sum Carry 0 0 0 0 1 1 0 0 1 0 1 1 1 0 0 1 1 1

VHDL code for Full Adder library IEEE; use IEEE. STD_LOGIC_1164. ALL; entity fa is Port ( a, b, c : in STD_LOGIC; sum, carry : out STD_LOGIC); end fa; architecture Behavioral of fa is begin sum<= a xor b xor c; carry <= (a and b) or ( a and c) or ( b and c); end Behavioral;

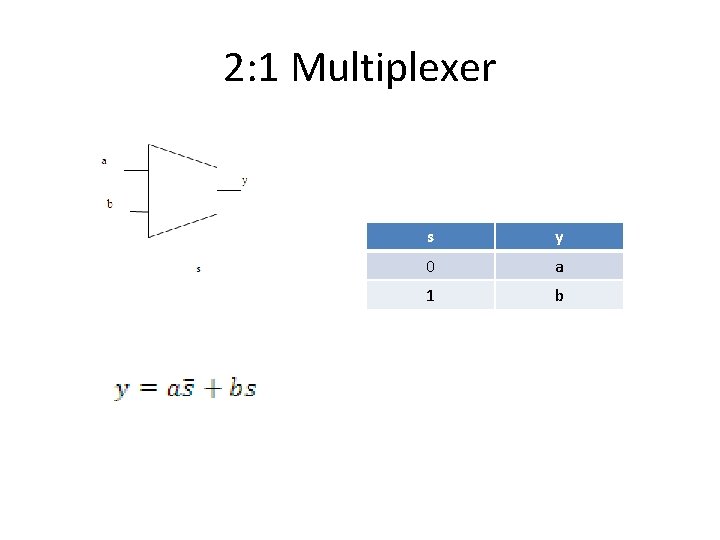

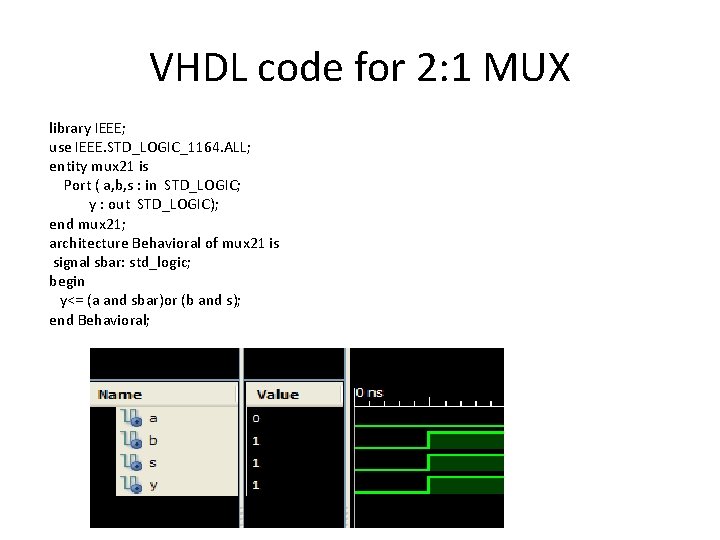

2: 1 Multiplexer s y 0 a 1 b

VHDL code for 2: 1 MUX library IEEE; use IEEE. STD_LOGIC_1164. ALL; entity mux 21 is Port ( a, b, s : in STD_LOGIC; y : out STD_LOGIC); end mux 21; architecture Behavioral of mux 21 is signal sbar: std_logic; begin y<= (a and sbar)or (b and s); end Behavioral;

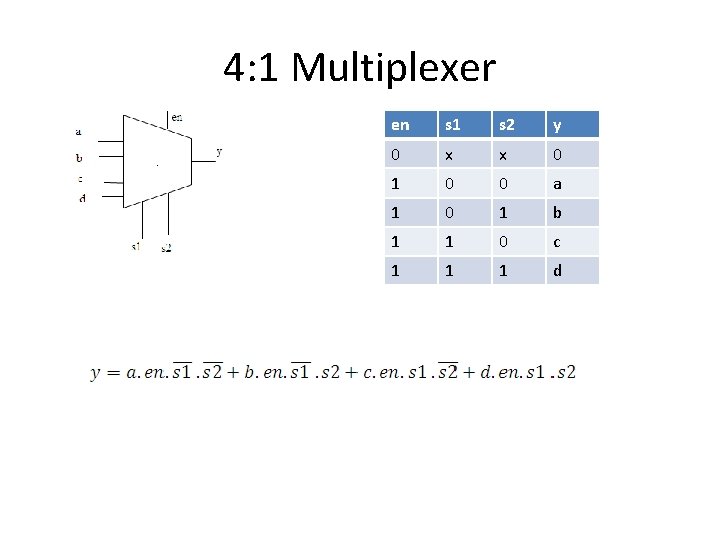

4: 1 Multiplexer en s 1 s 2 y 0 x x 0 1 0 0 a 1 0 1 b 1 1 0 c 1 1 1 d

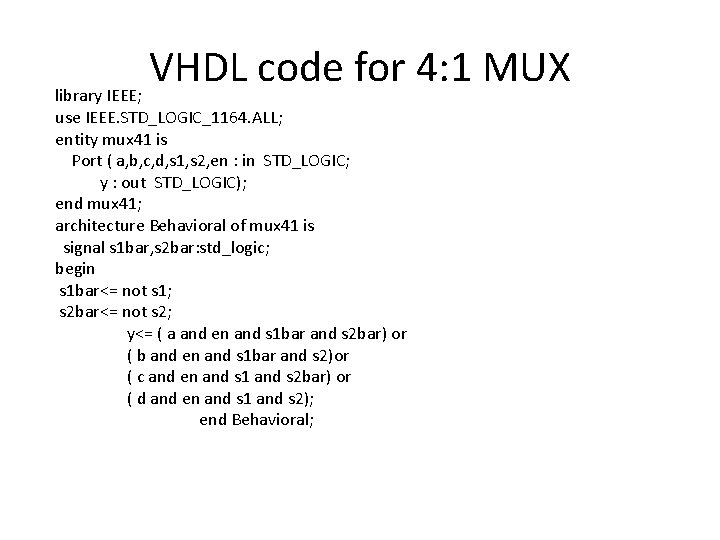

VHDL code for 4: 1 MUX library IEEE; use IEEE. STD_LOGIC_1164. ALL; entity mux 41 is Port ( a, b, c, d, s 1, s 2, en : in STD_LOGIC; y : out STD_LOGIC); end mux 41; architecture Behavioral of mux 41 is signal s 1 bar, s 2 bar: std_logic; begin s 1 bar<= not s 1; s 2 bar<= not s 2; y<= ( a and en and s 1 bar and s 2 bar) or ( b and en and s 1 bar and s 2)or ( c and en and s 1 and s 2 bar) or ( d and en and s 1 and s 2); end Behavioral;

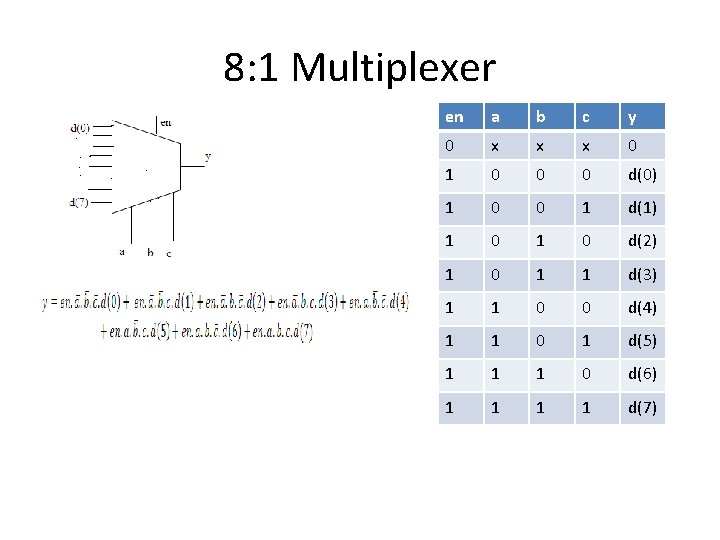

8: 1 Multiplexer en a b c y 0 x x x 0 1 0 0 0 d(0) 1 0 0 1 d(1) 1 0 d(2) 1 0 1 1 d(3) 1 1 0 0 d(4) 1 1 0 1 d(5) 1 1 1 0 d(6) 1 1 d(7)

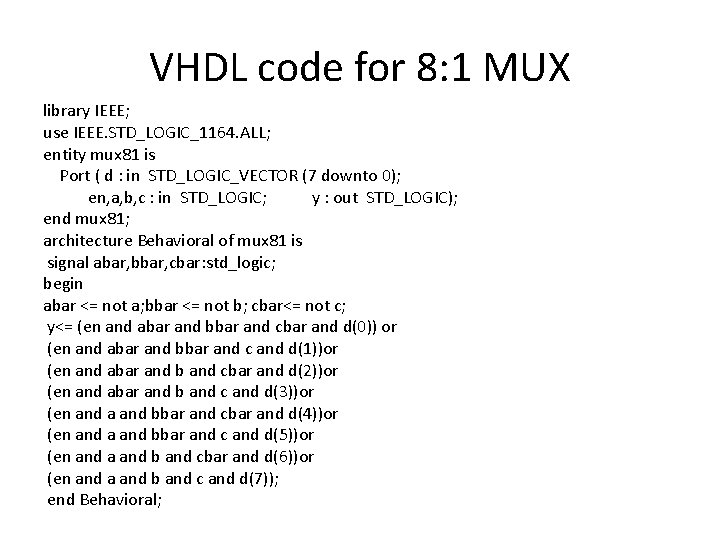

VHDL code for 8: 1 MUX library IEEE; use IEEE. STD_LOGIC_1164. ALL; entity mux 81 is Port ( d : in STD_LOGIC_VECTOR (7 downto 0); en, a, b, c : in STD_LOGIC; y : out STD_LOGIC); end mux 81; architecture Behavioral of mux 81 is signal abar, bbar, cbar: std_logic; begin abar <= not a; bbar <= not b; cbar<= not c; y<= (en and abar and bbar and cbar and d(0)) or (en and abar and bbar and c and d(1))or (en and abar and b and cbar and d(2))or (en and abar and b and c and d(3))or (en and a and bbar and cbar and d(4))or (en and a and bbar and c and d(5))or (en and a and b and cbar and d(6))or (en and a and b and c and d(7)); end Behavioral;

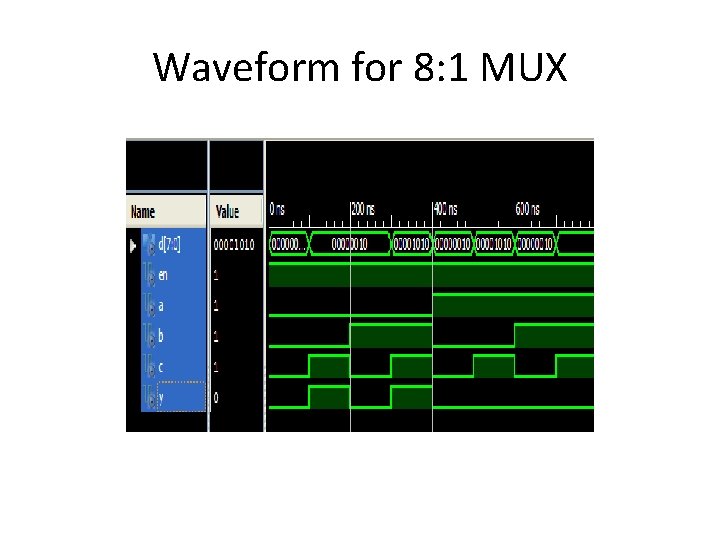

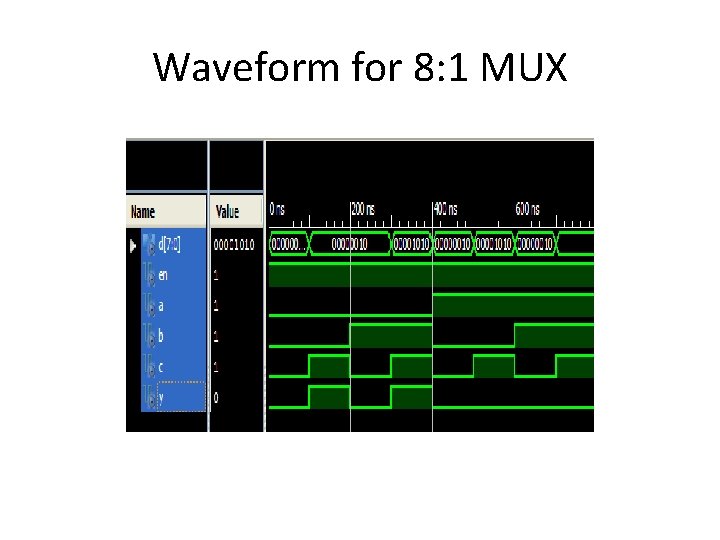

Waveform for 8: 1 MUX

Waveform for 8: 1 MUX

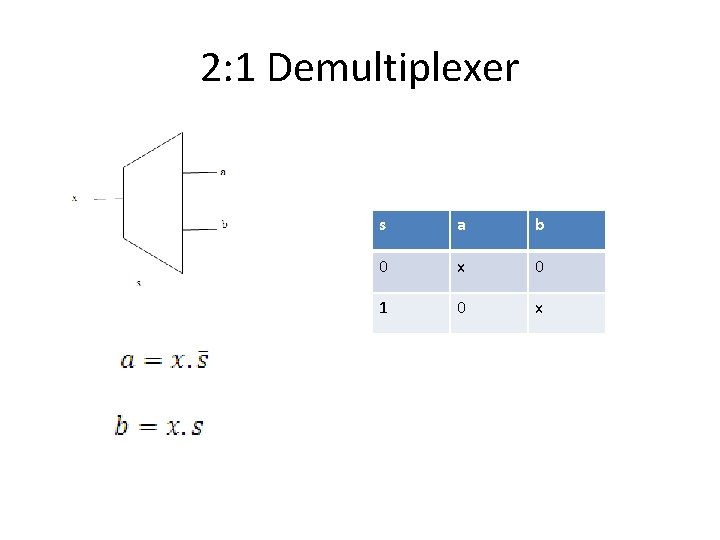

2: 1 Demultiplexer s a b 0 x 0 1 0 x

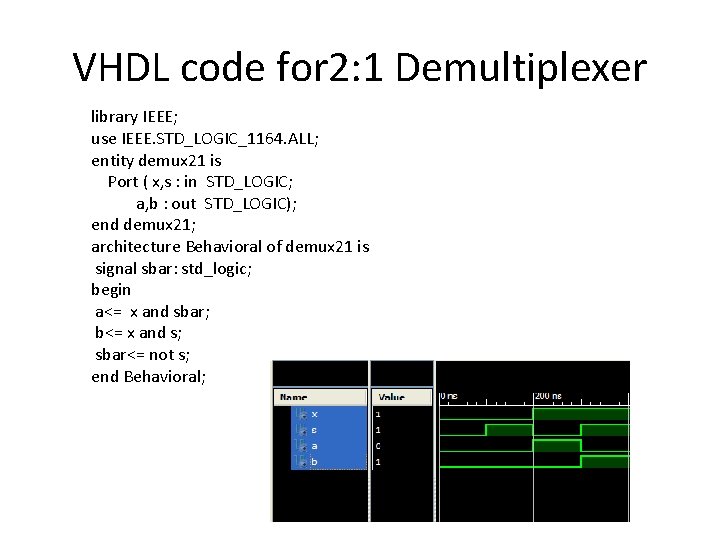

VHDL code for 2: 1 Demultiplexer library IEEE; use IEEE. STD_LOGIC_1164. ALL; entity demux 21 is Port ( x, s : in STD_LOGIC; a, b : out STD_LOGIC); end demux 21; architecture Behavioral of demux 21 is signal sbar: std_logic; begin a<= x and sbar; b<= x and s; sbar<= not s; end Behavioral;

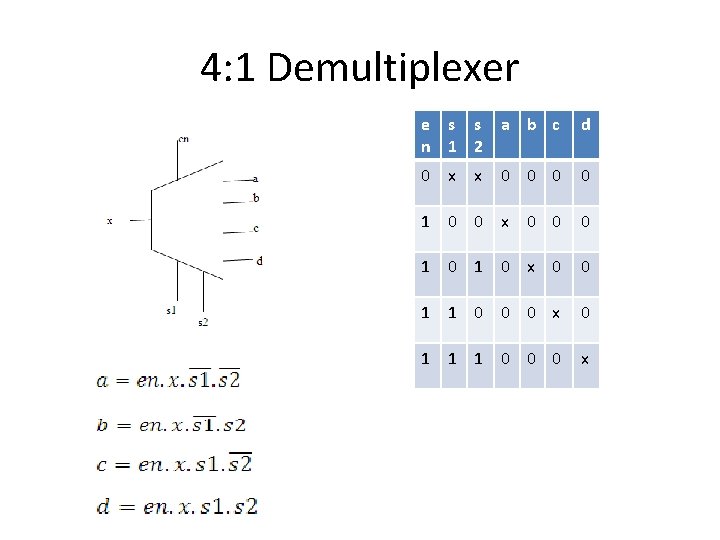

4: 1 Demultiplexer e s s a b c n 1 2 d 0 x 0 0 0 1 0 x 0 0 1 1 0 0 0 x 0 1 1 1 0 0 0 x

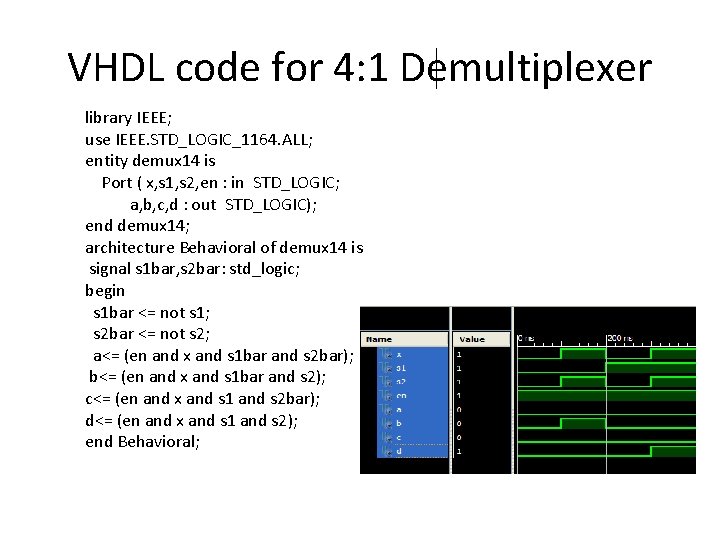

VHDL code for 4: 1 Demultiplexer library IEEE; use IEEE. STD_LOGIC_1164. ALL; entity demux 14 is Port ( x, s 1, s 2, en : in STD_LOGIC; a, b, c, d : out STD_LOGIC); end demux 14; architecture Behavioral of demux 14 is signal s 1 bar, s 2 bar: std_logic; begin s 1 bar <= not s 1; s 2 bar <= not s 2; a<= (en and x and s 1 bar and s 2 bar); b<= (en and x and s 1 bar and s 2); c<= (en and x and s 1 and s 2 bar); d<= (en and x and s 1 and s 2); end Behavioral;

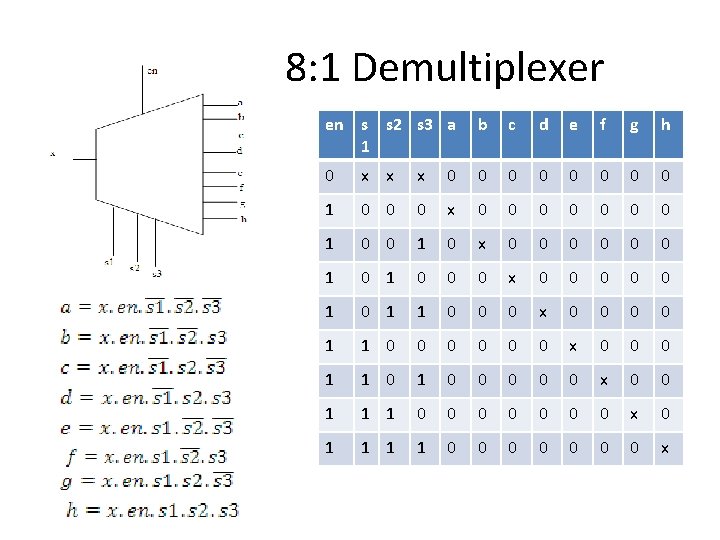

8: 1 Demultiplexer en s s 2 s 3 a 1 b c d e f g h 0 x x x 0 0 0 0 1 0 0 0 x 0 0 0 0 1 0 x 0 0 0 1 0 0 0 x 0 0 0 1 1 0 0 0 x 0 0 1 1 1 0 0 0 0 x 0 1 1 0 0 0 0 x

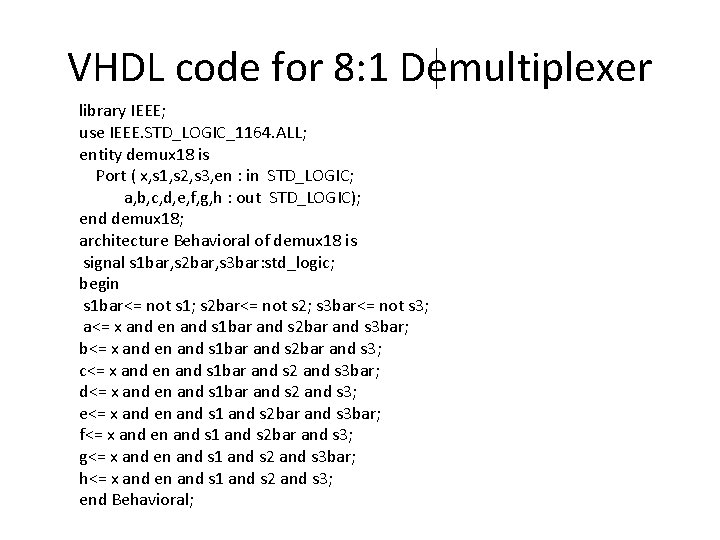

VHDL code for 8: 1 Demultiplexer library IEEE; use IEEE. STD_LOGIC_1164. ALL; entity demux 18 is Port ( x, s 1, s 2, s 3, en : in STD_LOGIC; a, b, c, d, e, f, g, h : out STD_LOGIC); end demux 18; architecture Behavioral of demux 18 is signal s 1 bar, s 2 bar, s 3 bar: std_logic; begin s 1 bar<= not s 1; s 2 bar<= not s 2; s 3 bar<= not s 3; a<= x and en and s 1 bar and s 2 bar and s 3 bar; b<= x and en and s 1 bar and s 2 bar and s 3; c<= x and en and s 1 bar and s 2 and s 3 bar; d<= x and en and s 1 bar and s 2 and s 3; e<= x and en and s 1 and s 2 bar and s 3 bar; f<= x and en and s 1 and s 2 bar and s 3; g<= x and en and s 1 and s 2 and s 3 bar; h<= x and en and s 1 and s 2 and s 3; end Behavioral;

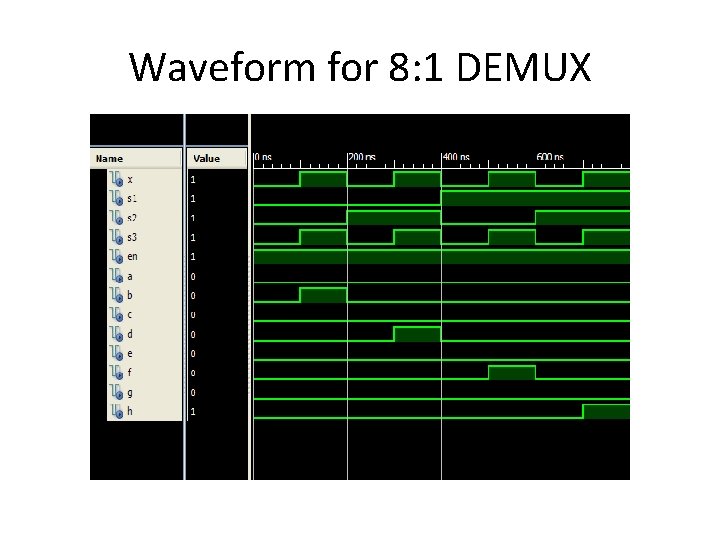

Waveform for 8: 1 DEMUX

- Slides: 24