VHDL Advanced Process Statements Ver 1 1 Copyright

- Slides: 16

VHDL Advanced Process Statements Ver 1. 1, Copyright 1997, TS, Inc. Advanced Process Statements Page 1

Objectives VHDL • Examine the broader capabilities of the process. • Topics Include – – Process Overview Sequential Statements Simulation Cycle Variables Ver 1. 1, Copyright 1997, TS, Inc. Advanced Process Statements Page 2

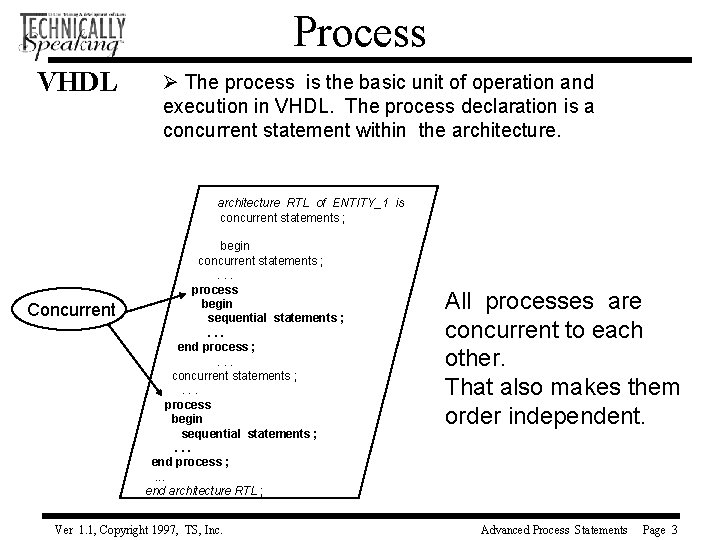

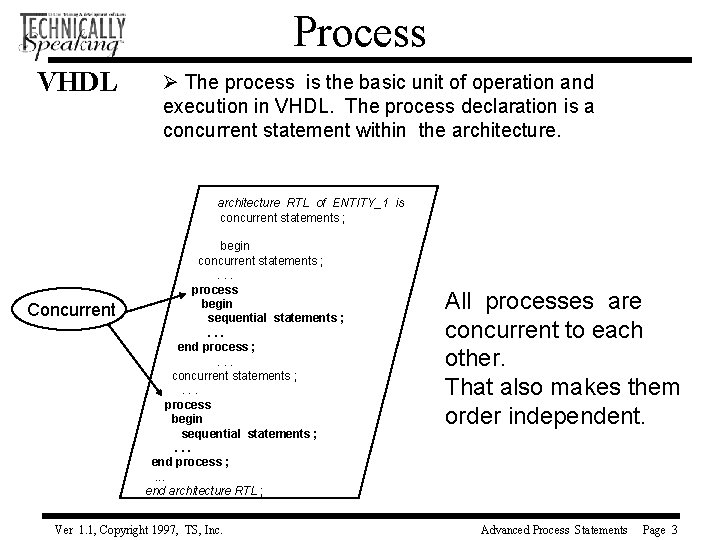

Process VHDL Ø The process is the basic unit of operation and execution in VHDL. The process declaration is a concurrent statement within the architecture RTL of ENTITY_1 is concurrent statements ; . . Concurrent . begin concurrent statements ; . . . process begin sequential statements ; . . . end process ; . . . end architecture RTL ; Ver 1. 1, Copyright 1997, TS, Inc. All processes are concurrent to each other. That also makes them order independent. Advanced Process Statements Page 3

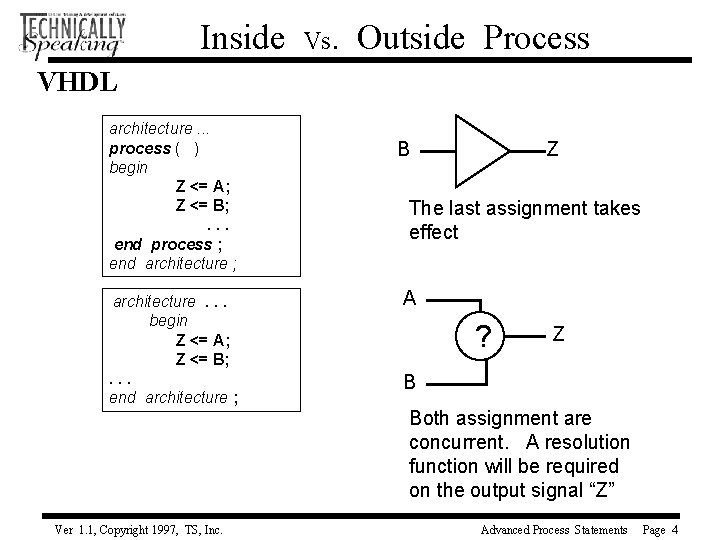

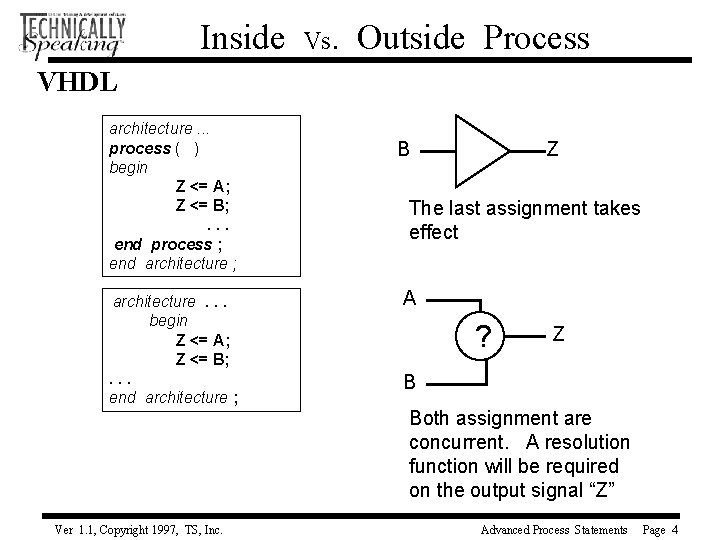

Inside Vs. Outside Process VHDL architecture. . . process ( ) begin Z <= A; Z <= B; . . . end process ; end architecture ; architecture. . . begin Z <= A; Z <= B; . . . end architecture ; B Z The last assignment takes effect A ? Z B Both assignment are concurrent. A resolution function will be required on the output signal “Z” Ver 1. 1, Copyright 1997, TS, Inc. Advanced Process Statements Page 4

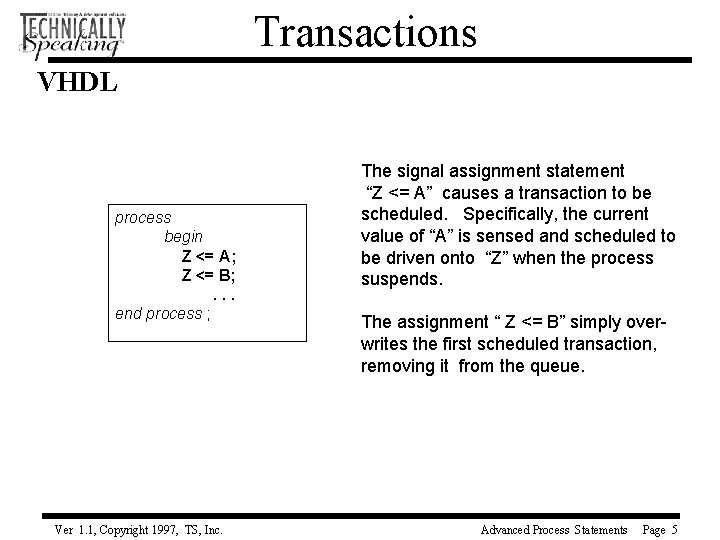

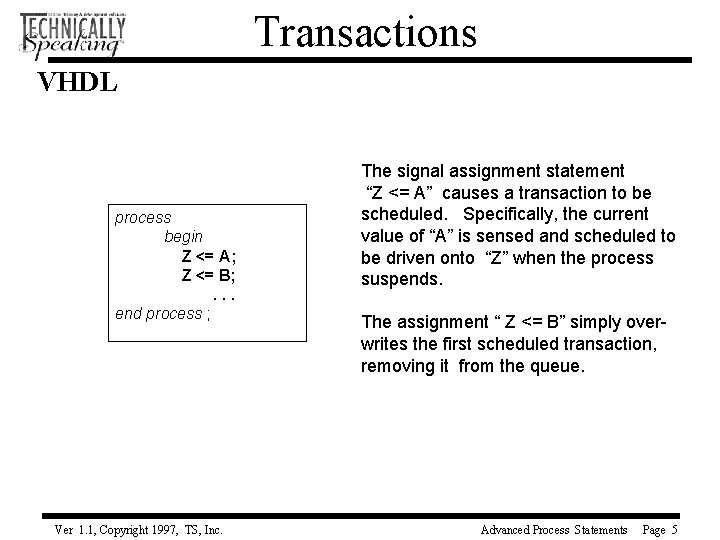

Transactions VHDL process begin Z <= A; Z <= B; . . . end process ; Ver 1. 1, Copyright 1997, TS, Inc. The signal assignment statement “Z <= A” causes a transaction to be scheduled. Specifically, the current value of “A” is sensed and scheduled to be driven onto “Z” when the process suspends. The assignment “ Z <= B” simply overwrites the first scheduled transaction, removing it from the queue. Advanced Process Statements Page 5

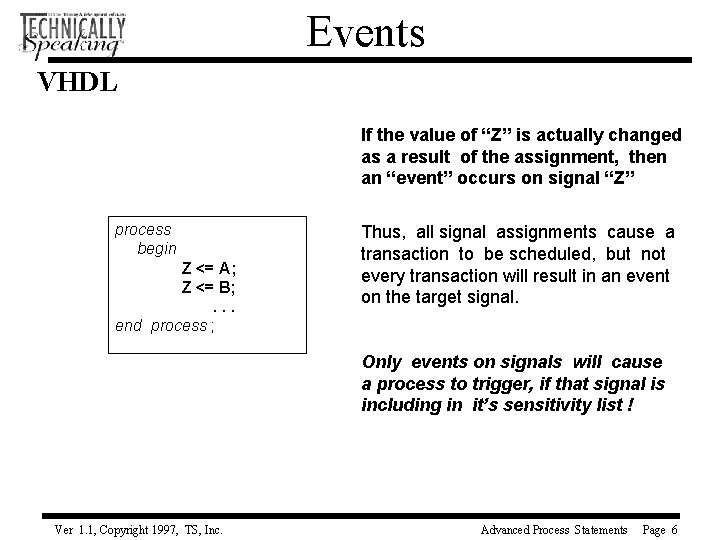

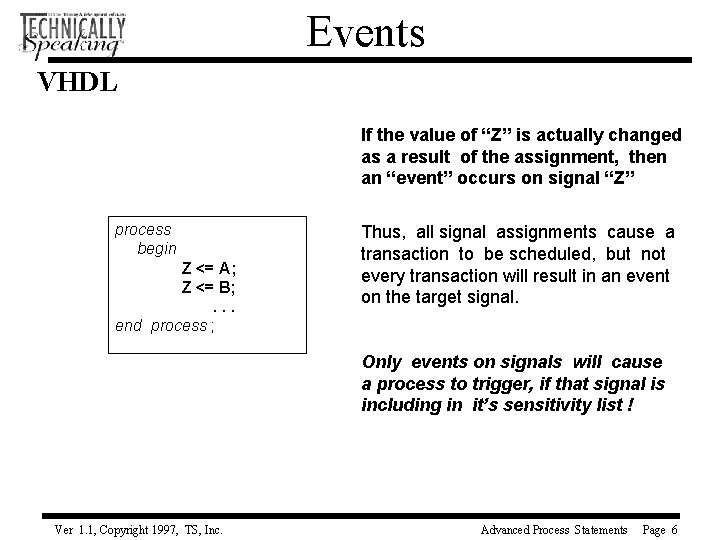

Events VHDL If the value of “Z” is actually changed as a result of the assignment, then an “event” occurs on signal “Z” process begin Z <= A; Z <= B; . . . end process ; Thus, all signal assignments cause a transaction to be scheduled, but not every transaction will result in an event on the target signal. Only events on signals will cause a process to trigger, if that signal is including in it’s sensitivity list ! Ver 1. 1, Copyright 1997, TS, Inc. Advanced Process Statements Page 6

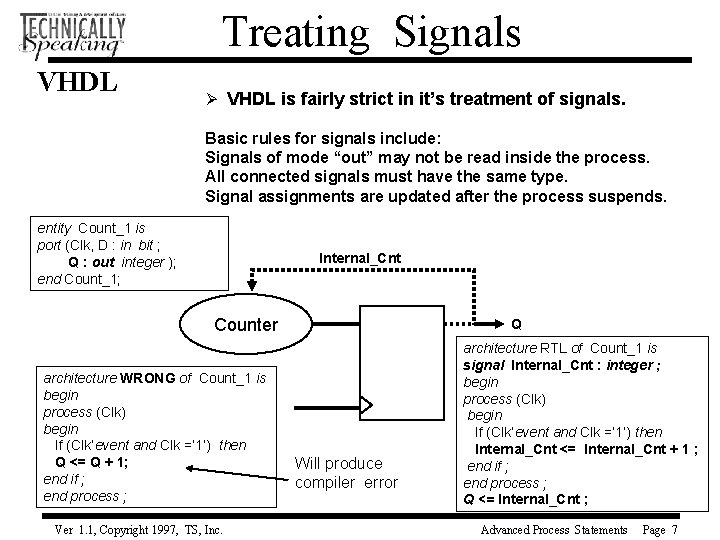

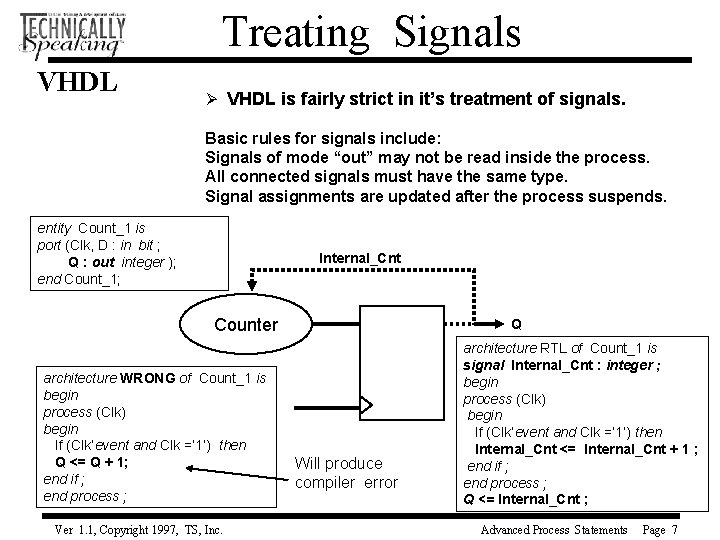

Treating Signals VHDL Ø VHDL is fairly strict in it’s treatment of signals. Basic rules for signals include: Signals of mode “out” may not be read inside the process. All connected signals must have the same type. Signal assignments are updated after the process suspends. entity Count_1 is port (Clk, D : in bit ; Q : out integer ); end Count_1; Internal_Cnt Counter architecture WRONG of Count_1 is begin process (Clk) begin If (Clk’event and Clk =‘ 1’) then Q <= Q + 1; end if ; end process ; Ver 1. 1, Copyright 1997, TS, Inc. Q Will produce compiler error architecture RTL of Count_1 is signal Internal_Cnt : integer ; begin process (Clk) begin If (Clk’event and Clk =‘ 1’) then Internal_Cnt <= Internal_Cnt + 1 ; end if ; end process ; Q <= Internal_Cnt ; Advanced Process Statements Page 7

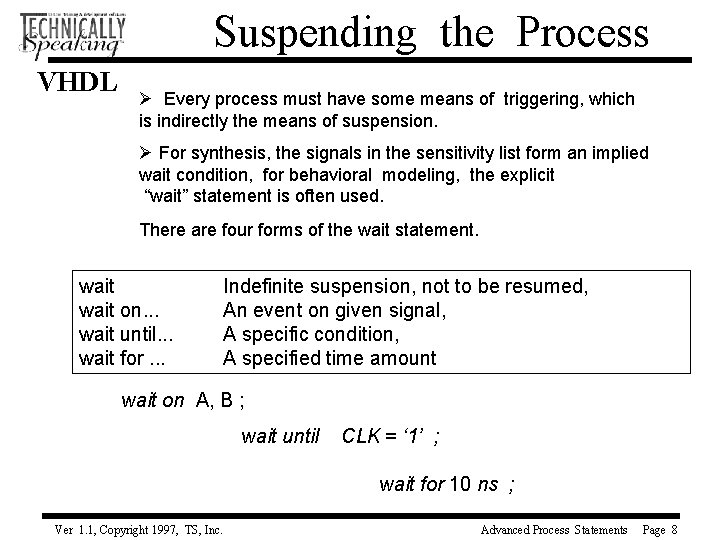

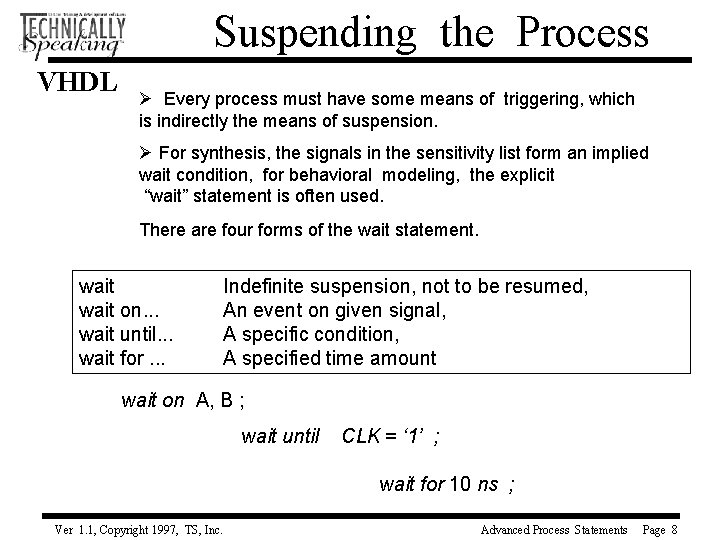

Suspending the Process VHDL Ø Every process must have some means of triggering, which is indirectly the means of suspension. Ø For synthesis, the signals in the sensitivity list form an implied wait condition, for behavioral modeling, the explicit “wait” statement is often used. There are four forms of the wait statement. wait on. . . wait until. . . wait for. . . Indefinite suspension, not to be resumed, An event on given signal, A specific condition, A specified time amount wait on A, B ; wait until CLK = ‘ 1’ ; wait for 10 ns ; Ver 1. 1, Copyright 1997, TS, Inc. Advanced Process Statements Page 8

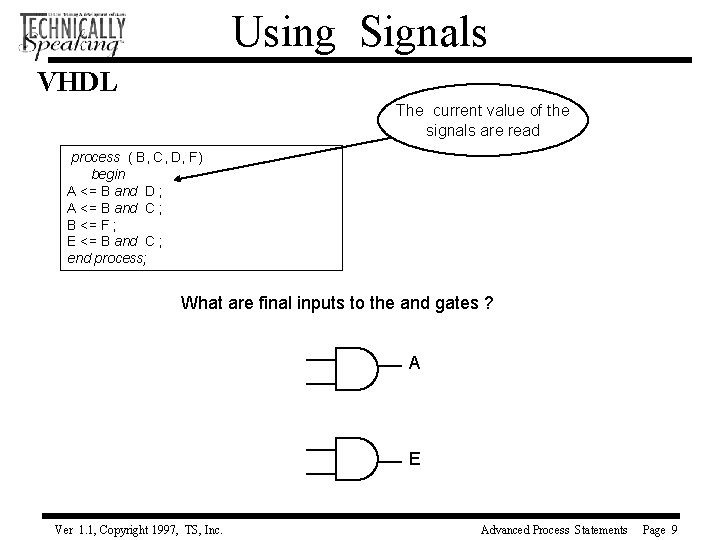

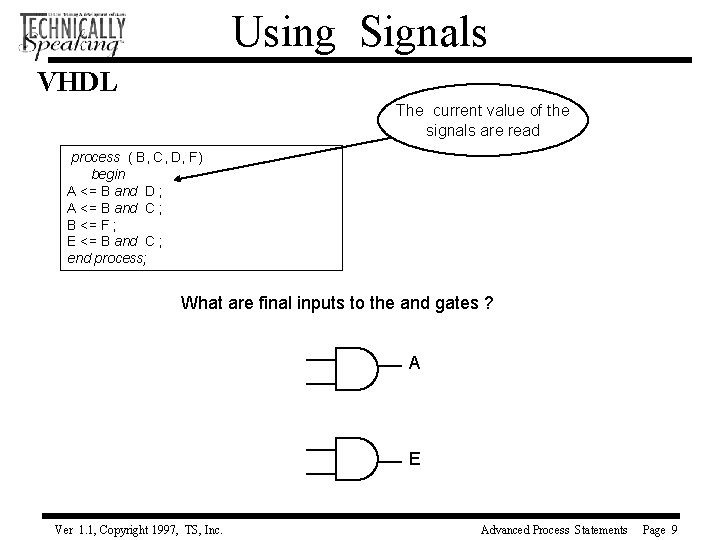

Using Signals VHDL The current value of the signals are read process ( B, C, D, F) begin A <= B and D ; A <= B and C ; B <= F ; E <= B and C ; end process; What are final inputs to the and gates ? A E Ver 1. 1, Copyright 1997, TS, Inc. Advanced Process Statements Page 9

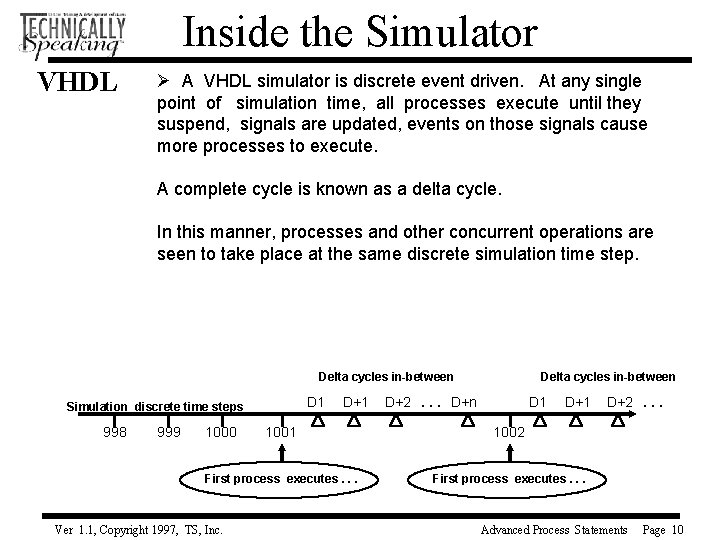

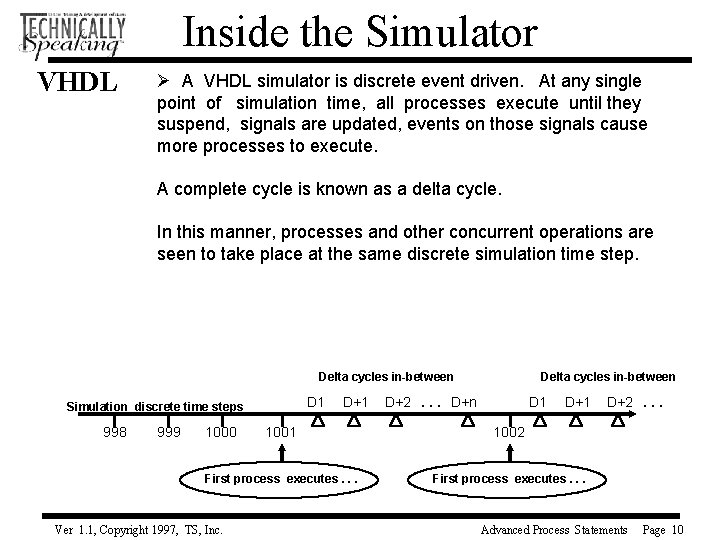

Inside the Simulator VHDL Ø A VHDL simulator is discrete event driven. At any single point of simulation time, all processes execute until they suspend, signals are updated, events on those signals cause more processes to execute. A complete cycle is known as a delta cycle. In this manner, processes and other concurrent operations are seen to take place at the same discrete simulation time step. Delta cycles in-between D 1 Simulation discrete time steps 998 999 1000 D+1 Delta cycles in-between D+2. . . D+n D 1 D+1 1002 First process executes. . . Ver 1. 1, Copyright 1997, TS, Inc. D+2. . . Advanced Process Statements Page 10

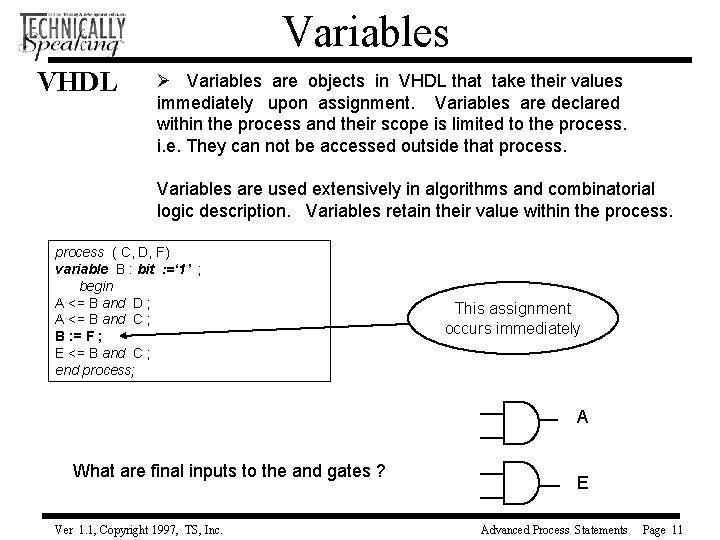

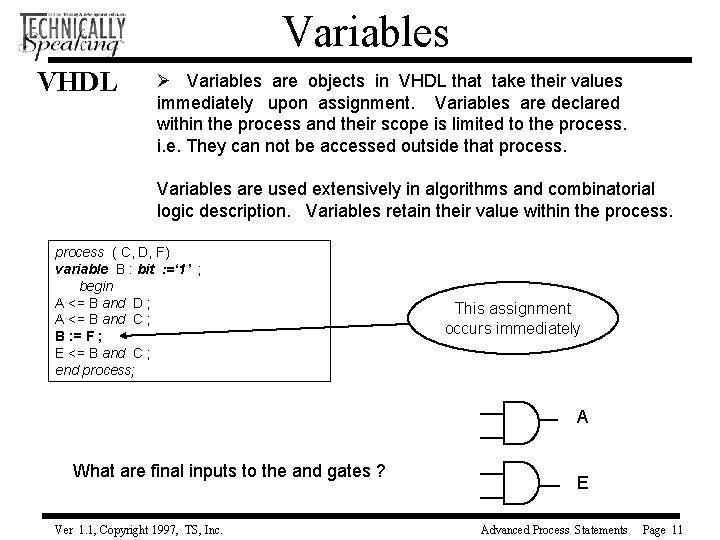

Variables VHDL Ø Variables are objects in VHDL that take their values immediately upon assignment. Variables are declared within the process and their scope is limited to the process. i. e. They can not be accessed outside that process. Variables are used extensively in algorithms and combinatorial logic description. Variables retain their value within the process ( C, D, F) variable B : bit : =‘ 1’ ; begin A <= B and D ; A <= B and C ; B : = F ; E <= B and C ; end process; This assignment occurs immediately A What are final inputs to the and gates ? Ver 1. 1, Copyright 1997, TS, Inc. E Advanced Process Statements Page 11

Using Variables VHDL Ø Because a variable’s scope is generally limited to the process in which it is declared, they can not be used to carry values to other modules, like signals. They are however, highly recommended for combinatorial logic. They have the added advantage of speeding up simulation run-time since there are fewer delta cycles involved and fewer signals to be monitored for the occurrence of events. The last point is that since they retain their value within the process, any variable assigned before its value is declared will infer a register in hardware. For that reason, variables are not recommended for clocked processes. Ver 1. 1, Copyright 1997, TS, Inc. Advanced Process Statements Page 12

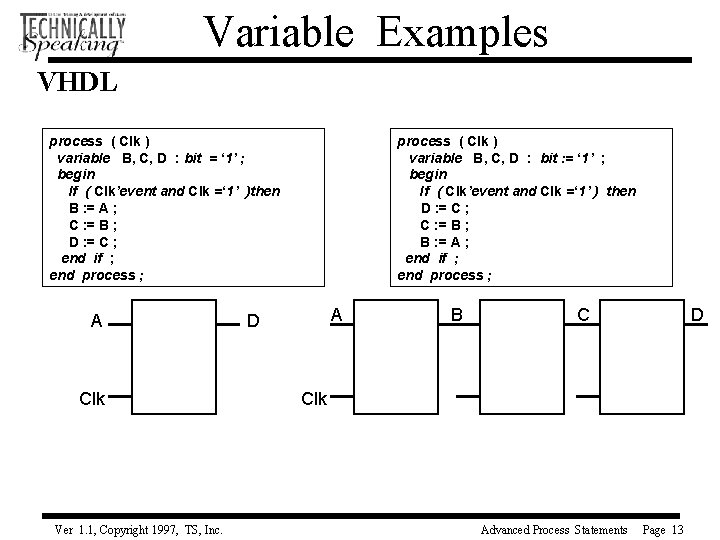

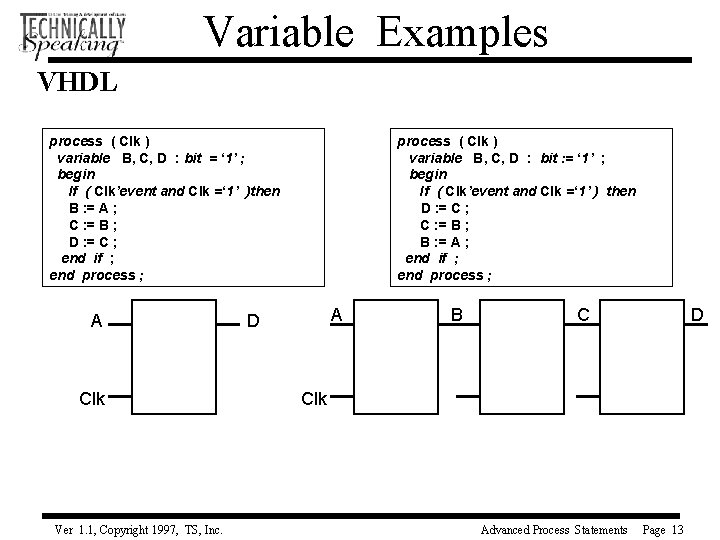

Variable Examples VHDL process ( Clk ) variable B, C, D : bit = ‘ 1’ ; begin If ( Clk’event and Clk =‘ 1’ )then B : = A ; C : = B ; D : = C ; end if ; end process ; A Clk Ver 1. 1, Copyright 1997, TS, Inc. process ( Clk ) variable B, C, D : bit : = ‘ 1’ ; begin If ( Clk’event and Clk =‘ 1’ ) then D : = C ; C : = B ; B : = A ; end if ; end process ; A D B C D Clk Advanced Process Statements Page 13

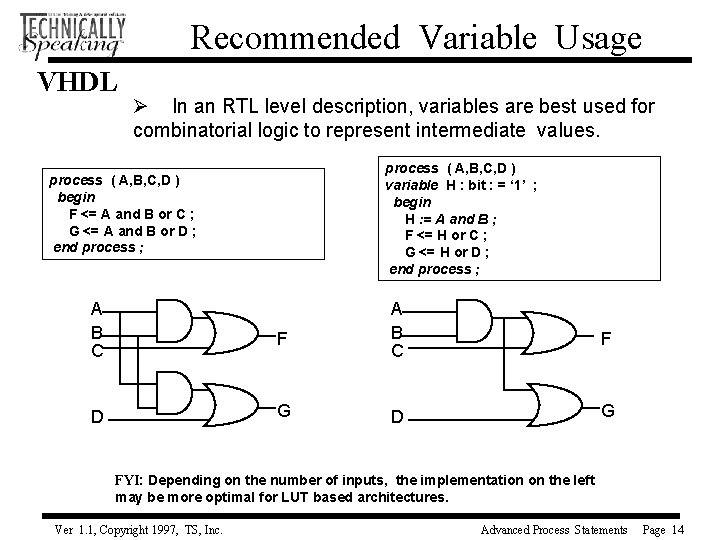

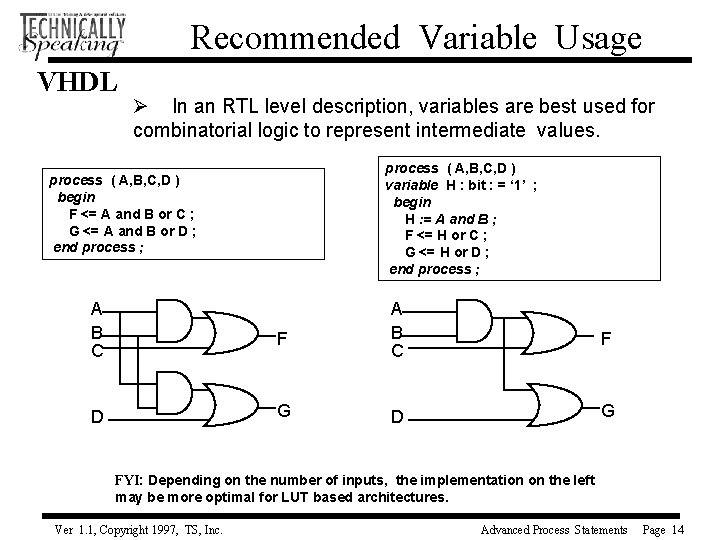

Recommended Variable Usage VHDL Ø In an RTL level description, variables are best used for combinatorial logic to represent intermediate values. process ( A, B, C, D ) variable H : bit : = ‘ 1’ ; begin H : = A and B ; F <= H or C ; G <= H or D ; end process ; process ( A, B, C, D ) begin F <= A and B or C ; G <= A and B or D ; end process ; A B C D F A B C F G D G FYI: Depending on the number of inputs, the implementation on the left may be more optimal for LUT based architectures. Ver 1. 1, Copyright 1997, TS, Inc. Advanced Process Statements Page 14

Summary VHDL Ø The process is the basic unit of operation in VHDL. Ø Within a process, the first condition found to be true will be executed. Ø A signal assignment will cause a transaction on that signal, but not necessarily an event. Ø Some form of the “wait” statement is used to control processes. Ø Variables are updated immediately, and retain their value within the process. Ver 1. 1, Copyright 1997, TS, Inc. Advanced Process Statements Page 15

Questions VHDL What is a “delta cycle” ? When is a signal updated as the result of an assignment ? What is the syntax for a variable assignment ? What is the scope of a variable ? What is the maximum number of delta cycles that can occur at any given point of simulation time ? What causes a suspended process to resume execution ? Ver 1. 1, Copyright 1997, TS, Inc. Advanced Process Statements Page 16