VHDL 2Sprachelemente und Concurrent Statements Nebenlufige Anweisungen Inhalt

VHDL 2_Sprachelemente und Concurrent Statements (Nebenläufige Anweisungen)

Inhalt n Sprachelemente und Objekte n Operatoren n Concurrent Statements (Nebenläufige Anweisungen)

Sprachelemente und Objekte

Kommentare -- Das ist eine Kommentarzeile -- auch eine zweite Zeile muss mit „--“ eingeleitet werden Entity nand 4 IS ( -- Kommentar bis zum Zeilenende -- VHDL ist unempfindlich hinsichtlich Klein- und Grossschreibung ! -- Jedoch ist es sinnvoll, wenn Sie in Ihrer Gruppe eine Konvention -- hinsichtlich der Namensgebung haben

![Daten Objekte CONSTANT name [, name. . . ]: Type : = wert; VARIABLE Daten Objekte CONSTANT name [, name. . . ]: Type : = wert; VARIABLE](http://slidetodoc.com/presentation_image_h/7ad96a69a11cf420a3bb3c71fae7e264/image-5.jpg)

Daten Objekte CONSTANT name [, name. . . ]: Type : = wert; VARIABLE name [, name. . . ]: Type [: = wert]; SIGNAL name [, name. . . ]: Type [: = wert]; Name CONSTANT a VARIABLE b SIGNAL c Datentyp deklaration Zuweisung eines Wertes : std_logic_vector (7 DOWNTO 0) : =“ 01001100“ ; : std_logic_vector (7 DOWNTO 0) ; : std_logic ; -- std_logic Datentypen sind definiert in Package ieee. std_logic_1164

n. Vordefinierte Typen Deklarationen

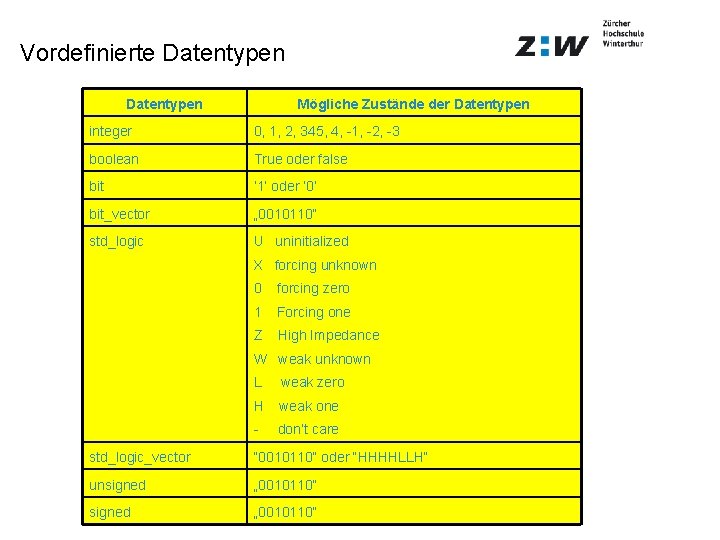

Vordefinierte Datentypen Mögliche Zustände der Datentypen integer 0, 1, 2, 345, 4, -1, -2, -3 boolean True oder false bit ‘ 1‘ oder ‘ 0‘ bit_vector „ 0010110“ std_logic U uninitialized X forcing unknown 0 forcing zero 1 Forcing one Z High Impedance W weak unknown L weak zero H weak one - don‘t care std_logic_vector “ 0010110“ oder “HHHHLLH“ unsigned „ 0010110“

Beispiel zur Verwendung von vordefinierten Datentypen Deklaration von Signalen: SIGNAL a, b SIGNAL c SIGNAL zaehler : std_logic ; : std_logic_vector (7 DOWNTO 0) ; : unsigned (6 DOWNTO 0) ; Zuweisung von Werten: a b c(7 DOWNTO 2) c(1) c(0) <= <= <= ‘ 1‘; ‘ 0‘; “ 100110“ ‘ 1‘; ‘ 0‘;

Operatoren

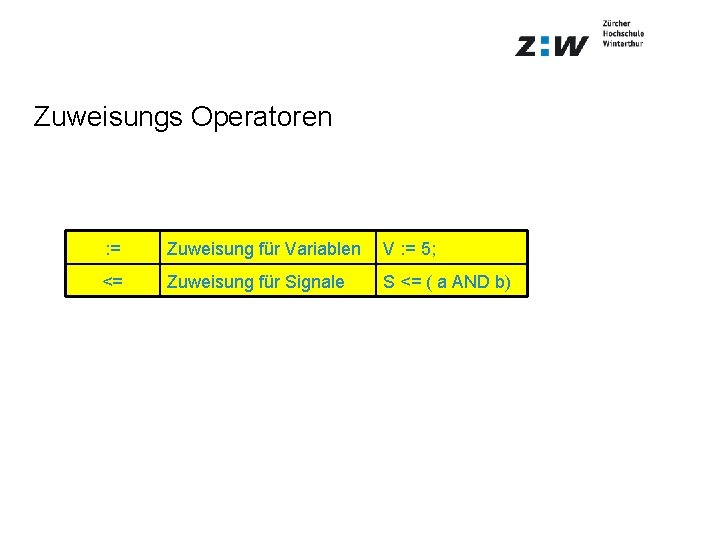

Zuweisungs Operatoren : = Zuweisung für Variablen V : = 5; <= Zuweisung für Signale S <= ( a AND b)

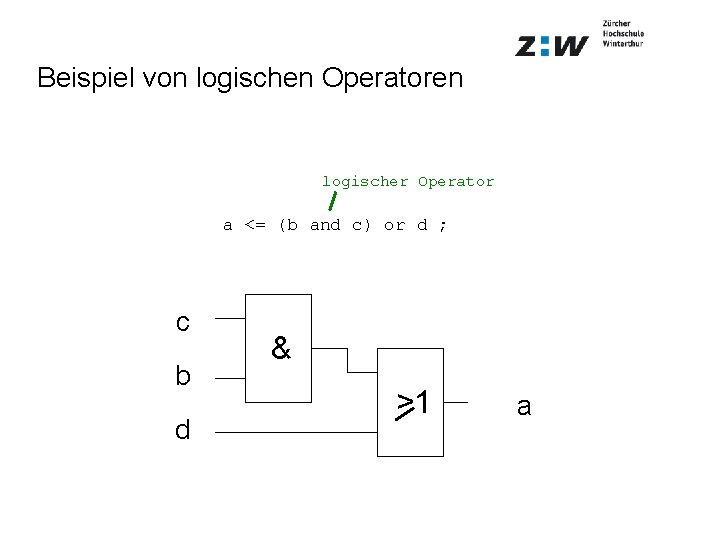

Beispiel von logischen Operatoren logischer Operator a <= (b and c) or d ; c b d & >1 a

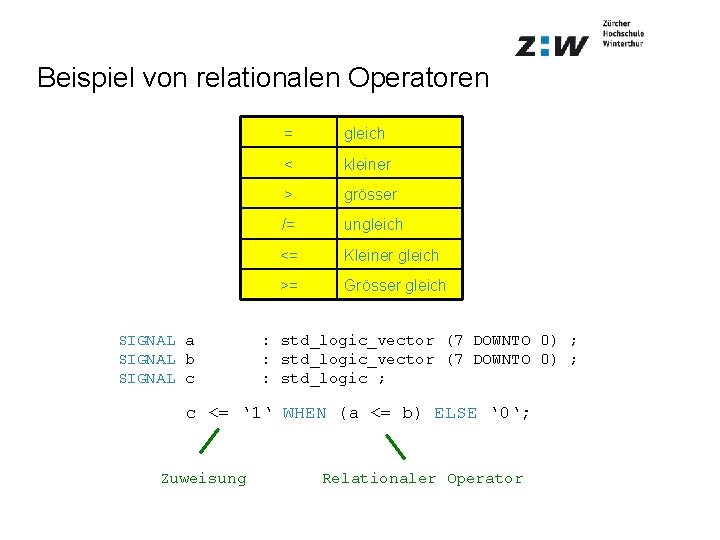

Beispiel von relationalen Operatoren SIGNAL a SIGNAL b SIGNAL c = gleich < kleiner > grösser /= ungleich <= Kleiner gleich >= Grösser gleich : std_logic_vector (7 DOWNTO 0) ; : std_logic ; c <= ‘ 1‘ WHEN (a <= b) ELSE ‘ 0‘; Zuweisung Relationaler Operator

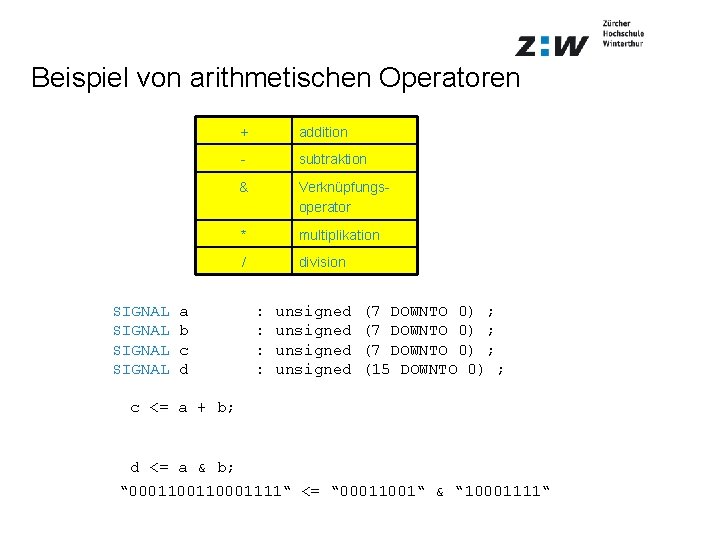

Beispiel von arithmetischen Operatoren SIGNAL a b c d + addition - subtraktion & Verknüpfungsoperator * multiplikation / division : : unsigned (7 DOWNTO 0) ; (15 DOWNTO 0) ; c <= a + b; d <= a & b; “ 000110001111“ <= “ 00011001“ & “ 10001111“

Concurrent Statements

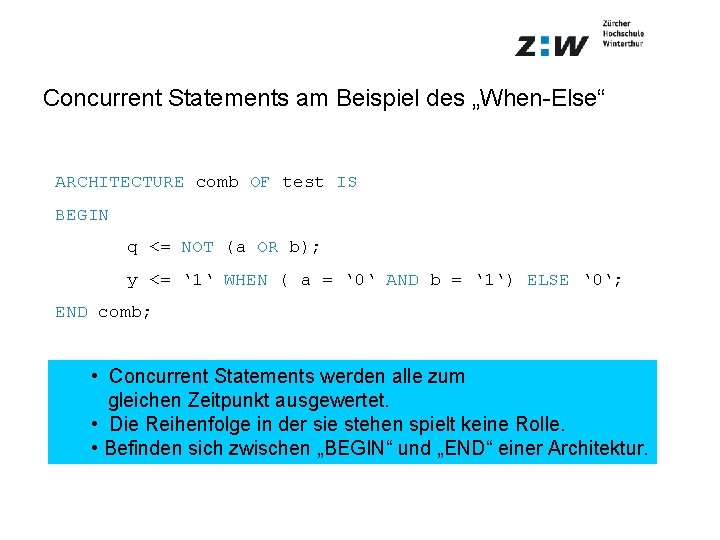

Concurrent Statements am Beispiel des „When-Else“ ARCHITECTURE comb OF test IS BEGIN q <= NOT (a OR b); y <= ‘ 1‘ WHEN ( a = ‘ 0‘ AND b = ‘ 1‘) ELSE ‘ 0‘; END comb; • Concurrent Statements werden alle zum gleichen Zeitpunkt ausgewertet. • Die Reihenfolge in der sie stehen spielt keine Rolle. • Befinden sich zwischen „BEGIN“ und „END“ einer Architektur.

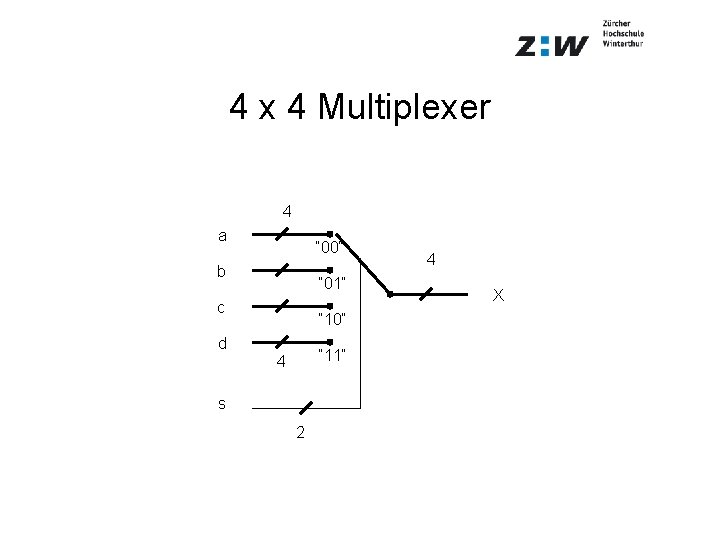

4 x 4 Multiplexer 4 a “ 00“ b “ 01“ c “ 10“ d “ 11“ 4 s 2 4 X

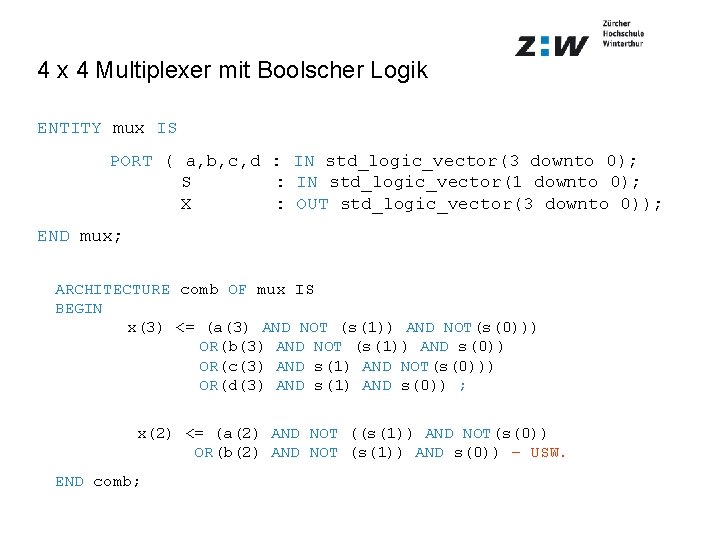

4 x 4 Multiplexer mit Boolscher Logik ENTITY mux IS PORT ( a, b, c, d : IN std_logic_vector(3 downto 0); S : IN std_logic_vector(1 downto 0); X : OUT std_logic_vector(3 downto 0)); END mux; ARCHITECTURE comb OF mux IS BEGIN x(3) <= (a(3) AND NOT (s(1)) AND NOT(s(0))) OR(b(3) AND NOT (s(1)) AND s(0)) OR(c(3) AND s(1) AND NOT(s(0))) OR(d(3) AND s(1) AND s(0)) ; x(2) <= (a(2) AND NOT ((s(1)) AND NOT(s(0)) OR(b(2) AND NOT (s(1)) AND s(0)) – USW. END comb;

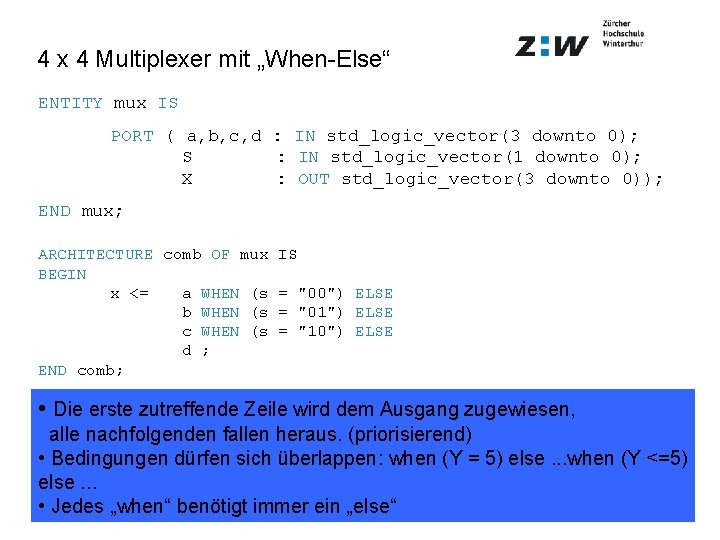

4 x 4 Multiplexer mit „When-Else“ ENTITY mux IS PORT ( a, b, c, d : IN std_logic_vector(3 downto 0); S : IN std_logic_vector(1 downto 0); X : OUT std_logic_vector(3 downto 0)); END mux; ARCHITECTURE comb OF mux BEGIN x <= a WHEN (s b WHEN (s c WHEN (s d ; END comb; IS = "00") ELSE = "01") ELSE = "10") ELSE • Die erste zutreffende Zeile wird dem Ausgang zugewiesen, alle nachfolgenden fallen heraus. (priorisierend) • Bedingungen dürfen sich überlappen: when (Y = 5) else. . . when (Y <=5) else. . . • Jedes „when“ benötigt immer ein „else“

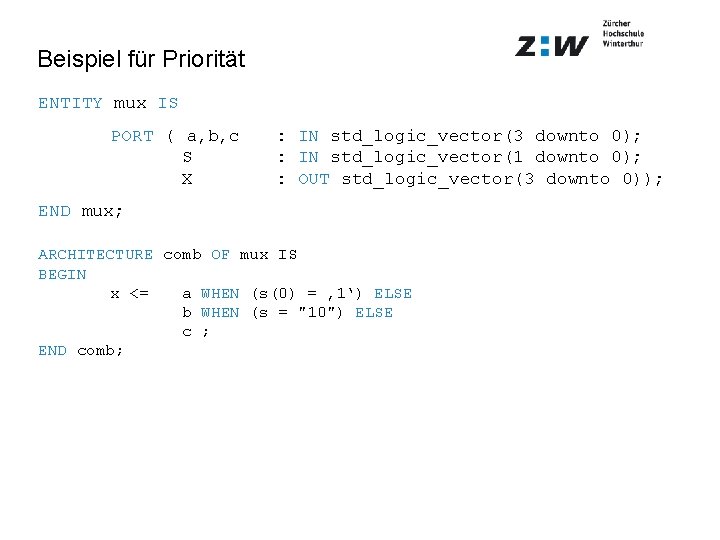

Beispiel für Priorität ENTITY mux IS PORT ( a, b, c S X : IN std_logic_vector(3 downto 0); : IN std_logic_vector(1 downto 0); : OUT std_logic_vector(3 downto 0)); END mux; ARCHITECTURE comb OF mux IS BEGIN x <= a WHEN (s(0) = ‚ 1‘) ELSE b WHEN (s = "10") ELSE c ; END comb;

- Slides: 19