VHDL 2 Identifiers data objects and data types

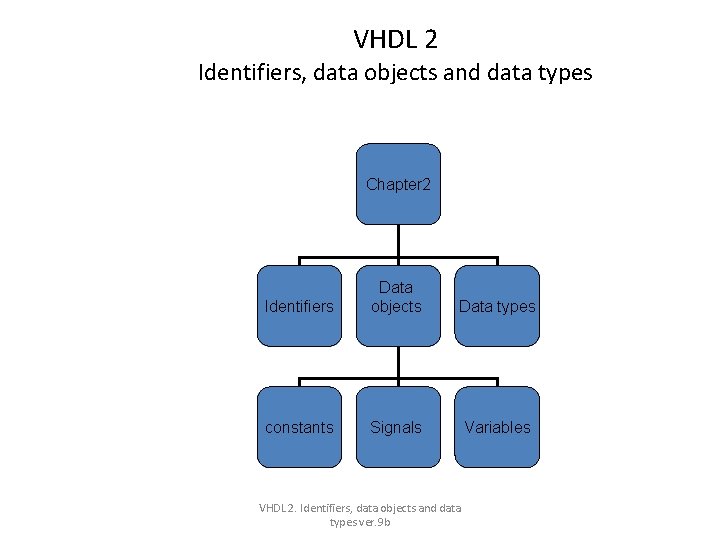

VHDL 2 Identifiers, data objects and data types Chapter 2 Identifiers Data objects Data types constants Signals Variables VHDL 2. Identifiers, data objects and data types ver. 9 b

Identifiers • How to create names? VHDL 2. Identifiers, data objects and data types ver. 9 b

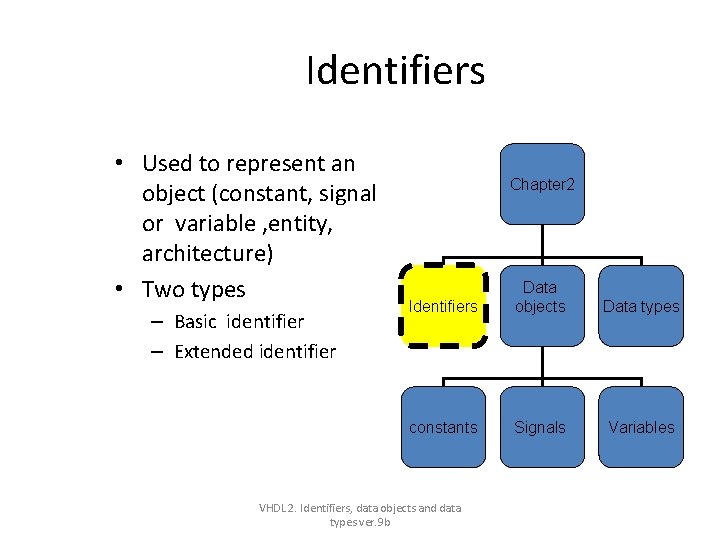

Identifiers • Used to represent an object (constant, signal or variable , entity, architecture) • Two types – Basic identifier – Extended identifier Chapter 2 Identifiers Data objects Data types constants Signals Variables VHDL 2. Identifiers, data objects and data types ver. 9 b

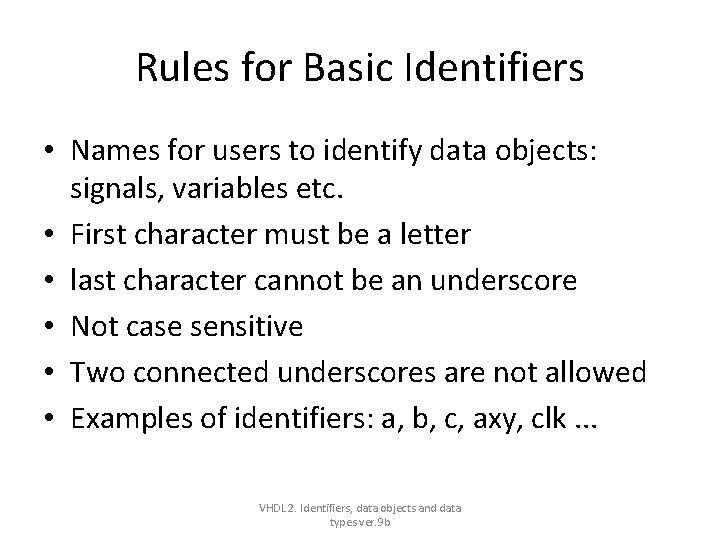

Rules for Basic Identifiers • Names for users to identify data objects: signals, variables etc. • First character must be a letter • last character cannot be an underscore • Not case sensitive • Two connected underscores are not allowed • Examples of identifiers: a, b, c, axy, clk. . . VHDL 2. Identifiers, data objects and data types ver. 9 b

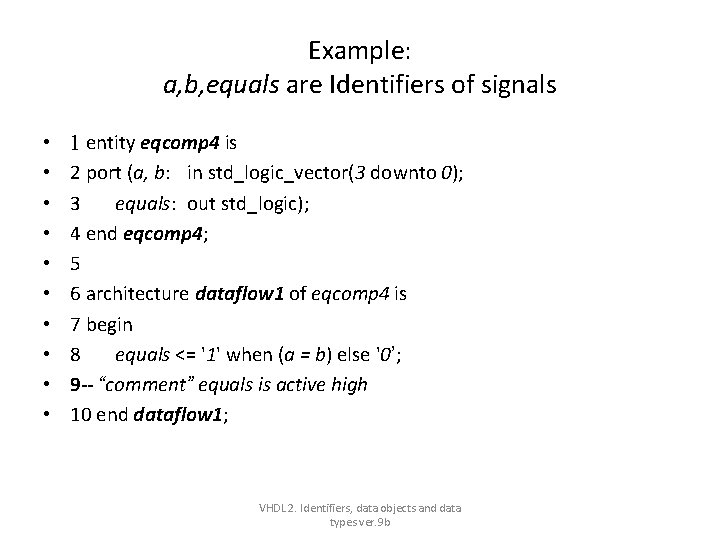

Example: a, b, equals are Identifiers of signals • • • 1 entity eqcomp 4 is 2 port (a, b: in std_logic_vector(3 downto 0); 3 equals: out std_logic); 4 end eqcomp 4; 5 6 architecture dataflow 1 of eqcomp 4 is 7 begin 8 equals <= '1' when (a = b) else '0’; 9 -- “comment” equals is active high 10 end dataflow 1; VHDL 2. Identifiers, data objects and data types ver. 9 b

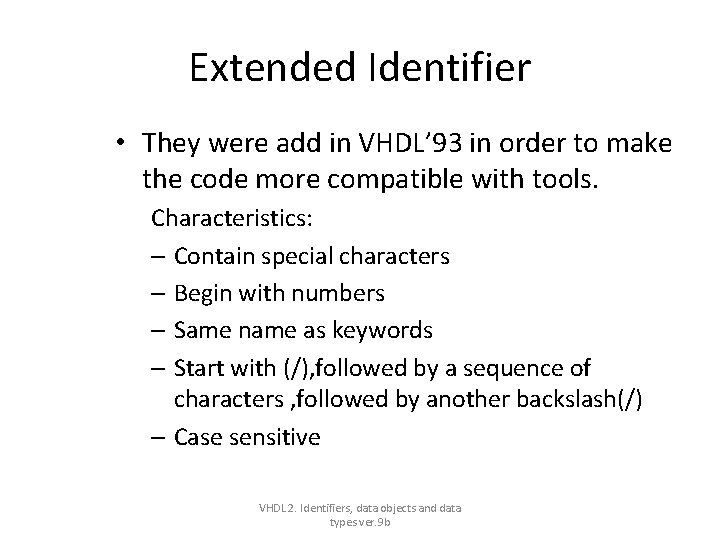

Extended Identifier • They were add in VHDL’ 93 in order to make the code more compatible with tools. Characteristics: – Contain special characters – Begin with numbers – Same name as keywords – Start with (/), followed by a sequence of characters , followed by another backslash(/) – Case sensitive VHDL 2. Identifiers, data objects and data types ver. 9 b

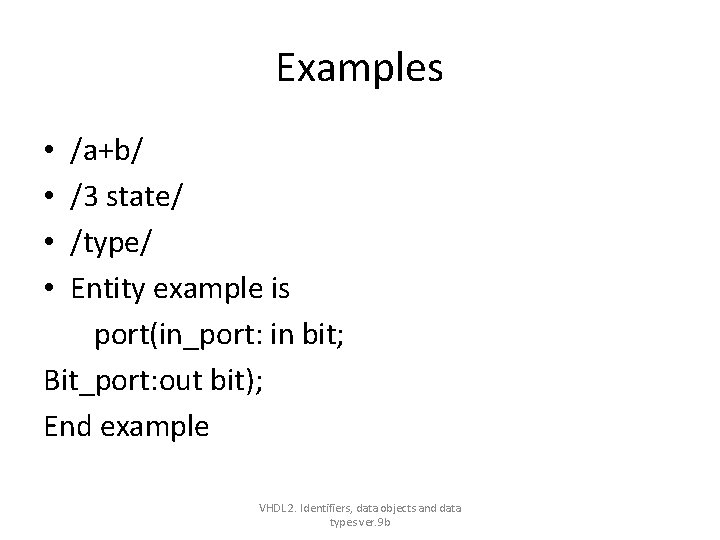

Examples /a+b/ /3 state/ /type/ Entity example is port(in_port: in bit; Bit_port: out bit); End example • • VHDL 2. Identifiers, data objects and data types ver. 9 b

Data objects VHDL 2. Identifiers, data objects and data types ver. 9 b

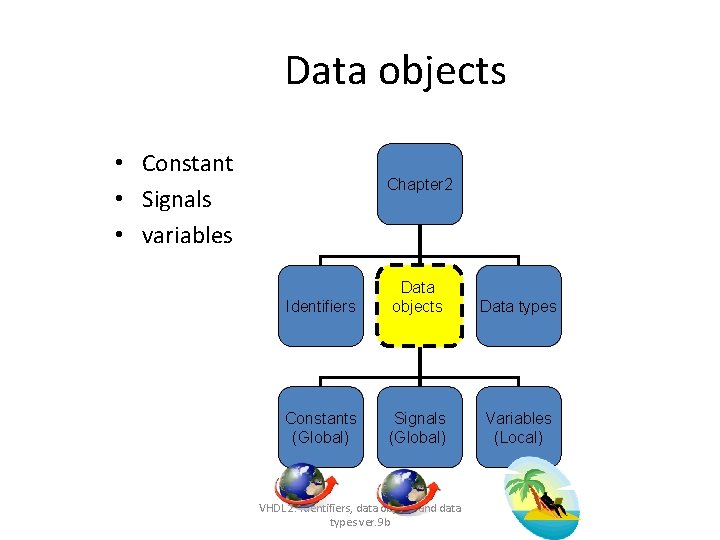

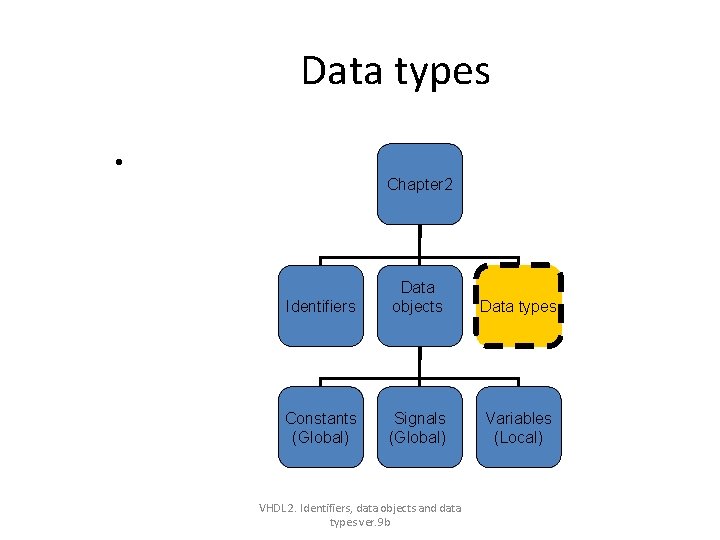

Data objects • Constant • Signals • variables Chapter 2 Identifiers Data objects Data types Constants (Global) Signals (Global) Variables (Local) VHDL 2. Identifiers, data objects and data types ver. 9 b

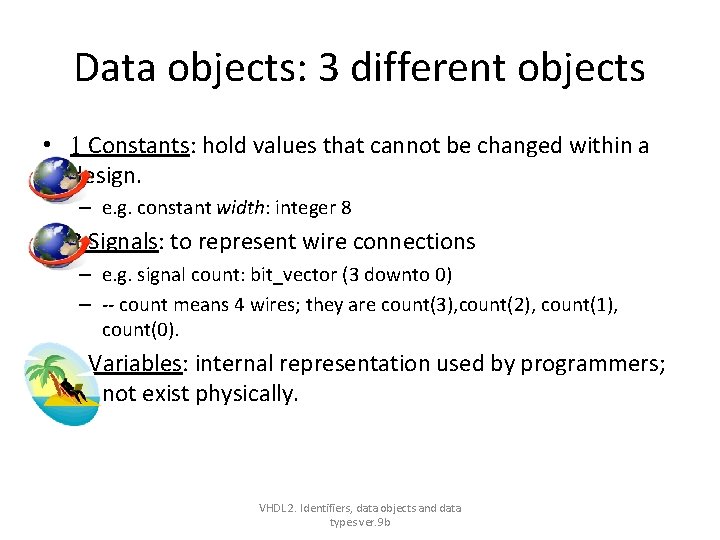

Data objects: 3 different objects • 1 Constants: hold values that cannot be changed within a design. – e. g. constant width: integer 8 • 2 Signals: to represent wire connections – e. g. signal count: bit_vector (3 downto 0) – -- count means 4 wires; they are count(3), count(2), count(1), count(0). • 3 Variables: internal representation used by programmers; do not exist physically. VHDL 2. Identifiers, data objects and data types ver. 9 b

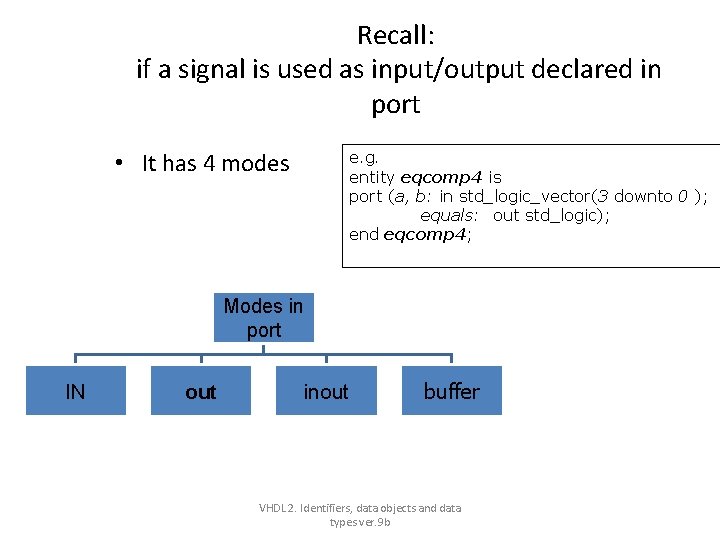

Recall: if a signal is used as input/output declared in port • It has 4 modes e. g. entity eqcomp 4 is port (a, b: in std_logic_vector(3 downto 0 ); equals: out std_logic); end eqcomp 4; Modes in port IN out inout buffer VHDL 2. Identifiers, data objects and data types ver. 9 b

Syntax to create data objects In entity declarations VHDL 2. Identifiers, data objects and data types ver. 9 b

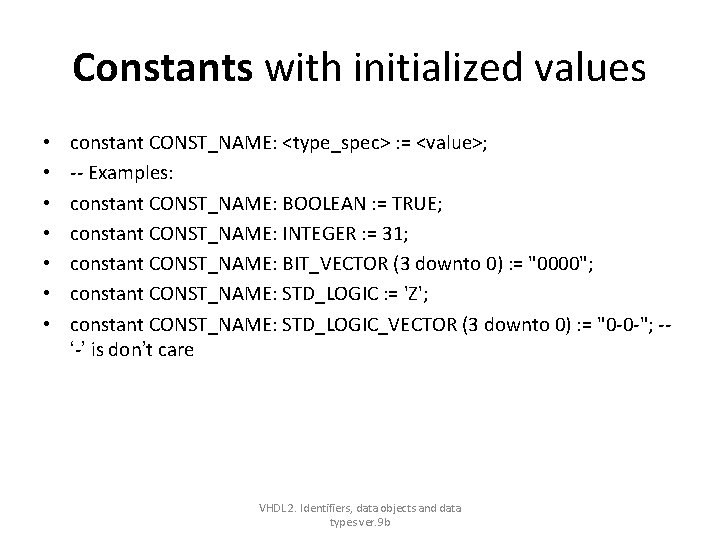

Constants with initialized values • • constant CONST_NAME: <type_spec> : = <value>; -- Examples: constant CONST_NAME: BOOLEAN : = TRUE; constant CONST_NAME: INTEGER : = 31; constant CONST_NAME: BIT_VECTOR (3 downto 0) : = "0000"; constant CONST_NAME: STD_LOGIC : = 'Z'; constant CONST_NAME: STD_LOGIC_VECTOR (3 downto 0) : = "0 -0 -"; -‘-’ is don’t care VHDL 2. Identifiers, data objects and data types ver. 9 b

![Signals with initialized values • signal sig_NAME: type_name [: init. Value]; • -- examples Signals with initialized values • signal sig_NAME: type_name [: init. Value]; • -- examples](http://slidetodoc.com/presentation_image_h2/10bd3435b6bbf9f38f2ec1836ee33e73/image-14.jpg)

Signals with initialized values • signal sig_NAME: type_name [: init. Value]; • -- examples – – signal s 1_bool : BOOLEAN; -- no initialized value signal xsl_int 1: INTEGER : =175; signal su 2_bit: BIT : =‘ 1’; BY DEFAULT value T’LEFT (leftmost value i. e false) VHDL 2. Identifiers, data objects and data types ver. 9 b

![Variables with initialized values • variable V_NAME: type_name [: init. Value]; • -- examples Variables with initialized values • variable V_NAME: type_name [: init. Value]; • -- examples](http://slidetodoc.com/presentation_image_h2/10bd3435b6bbf9f38f2ec1836ee33e73/image-15.jpg)

Variables with initialized values • variable V_NAME: type_name [: init. Value]; • -- examples – variable v 1_bool : BOOLEAN: = TRUE; – variable val_int 1: INTEGER: =135; – variable vv 2_bit: BIT; -- no initialized value VHDL 2. Identifiers, data objects and data types ver. 9 b

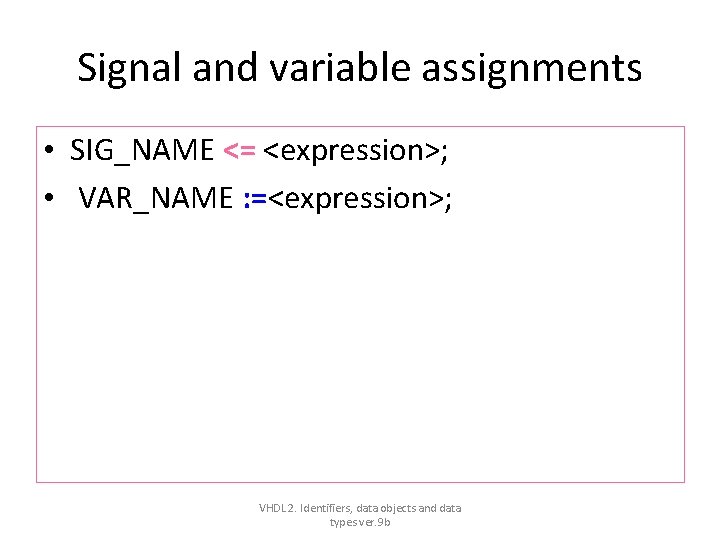

Signal and variable assignments • SIG_NAME <= <expression>; • VAR_NAME : =<expression>; VHDL 2. Identifiers, data objects and data types ver. 9 b

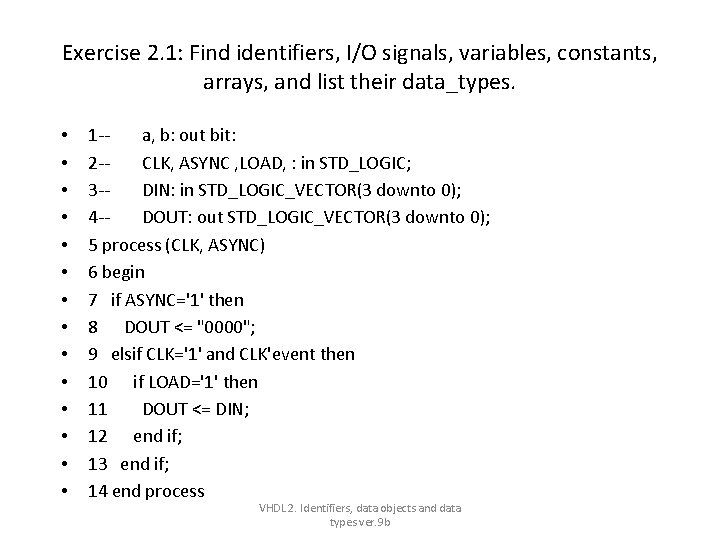

Exercise 2. 1: Find identifiers, I/O signals, variables, constants, arrays, and list their data_types. • • • • 1 -a, b: out bit: 2 -CLK, ASYNC , LOAD, : in STD_LOGIC; 3 -DIN: in STD_LOGIC_VECTOR(3 downto 0); 4 -DOUT: out STD_LOGIC_VECTOR(3 downto 0); 5 process (CLK, ASYNC) 6 begin 7 if ASYNC='1' then 8 DOUT <= "0000"; 9 elsif CLK='1' and CLK'event then 10 if LOAD='1' then 11 DOUT <= DIN; 12 end if; 13 end if; 14 end process VHDL 2. Identifiers, data objects and data types ver. 9 b

Data types • Chapter 2 Identifiers Data objects Data types Constants (Global) Signals (Global) Variables (Local) VHDL 2. Identifiers, data objects and data types ver. 9 b

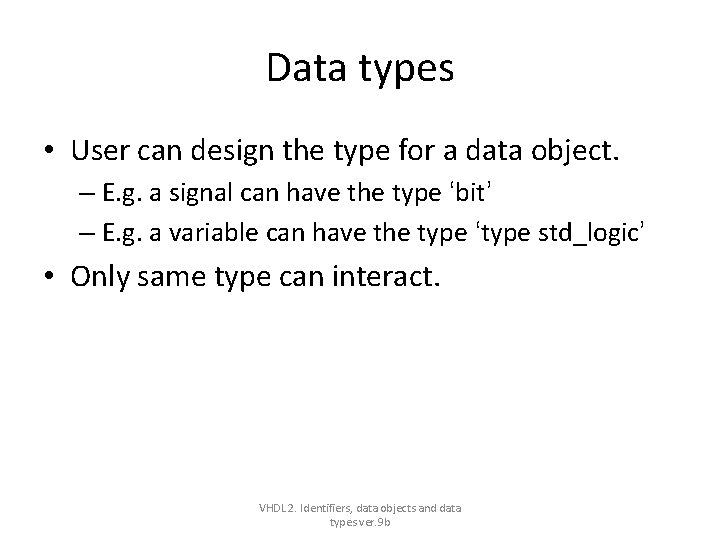

Data types • User can design the type for a data object. – E. g. a signal can have the type ‘bit’ – E. g. a variable can have the type ‘type std_logic’ • Only same type can interact. VHDL 2. Identifiers, data objects and data types ver. 9 b

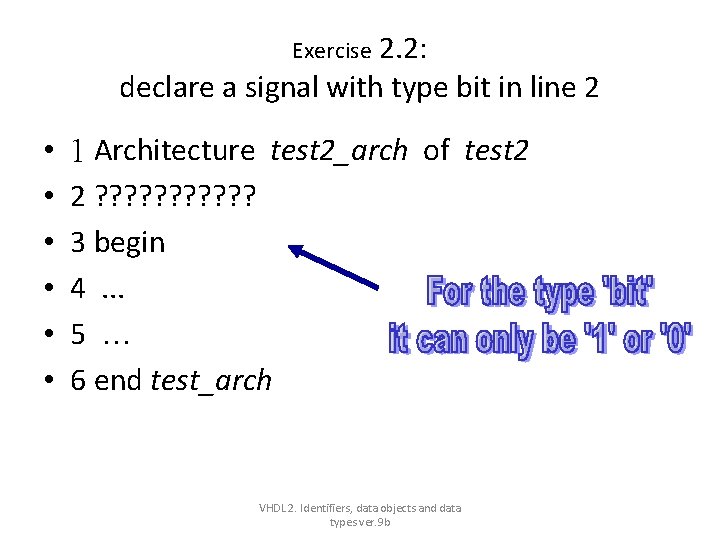

2. 2: declare a signal with type bit in line 2 Exercise • • • 1 Architecture test 2_arch of test 2 2 ? ? ? 3 begin 4. . . 5 … 6 end test_arch VHDL 2. Identifiers, data objects and data types ver. 9 b

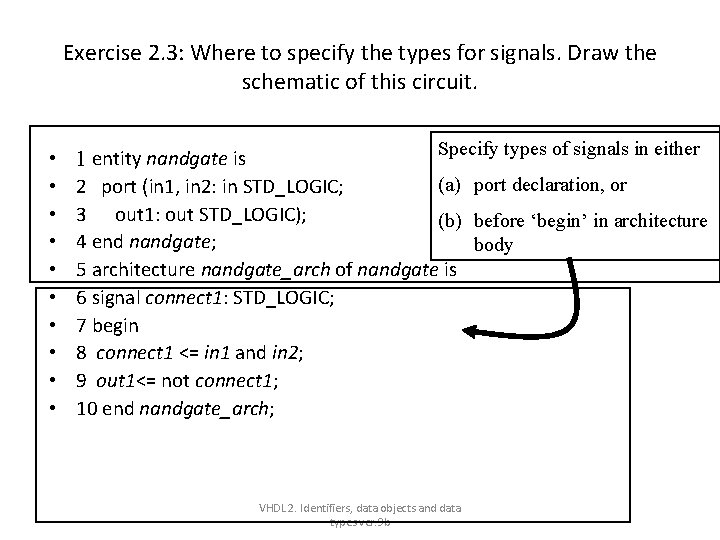

Exercise 2. 3: Where to specify the types for signals. Draw the schematic of this circuit. • • • Specify types of signals in either 1 entity nandgate is (a) port declaration, or 2 port (in 1, in 2: in STD_LOGIC; 3 out 1: out STD_LOGIC); (b) before ‘begin’ in architecture 4 end nandgate; body 5 architecture nandgate_arch of nandgate is 6 signal connect 1: STD_LOGIC; 7 begin 8 connect 1 <= in 1 and in 2; 9 out 1<= not connect 1; 10 end nandgate_arch; VHDL 2. Identifiers, data objects and data types ver. 9 b

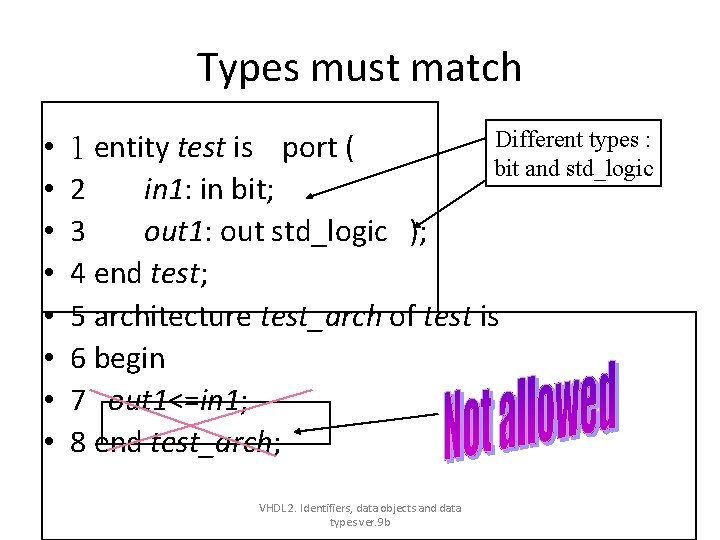

Types must match • • Different types : 1 entity test is port ( bit and std_logic 2 in 1: in bit; 3 out 1: out std_logic ); 4 end test; 5 architecture test_arch of test is 6 begin 7 out 1<=in 1; 8 end test_arch; VHDL 2. Identifiers, data objects and data types ver. 9 b

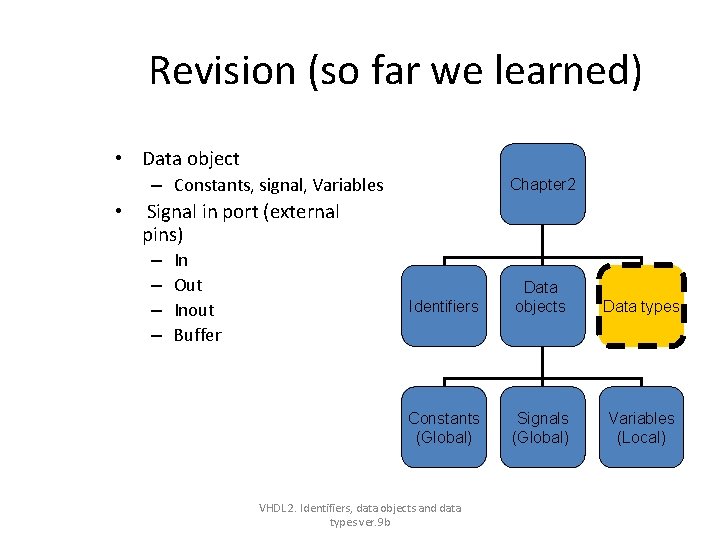

Revision (so far we learned) • Data object – Constants, signal, Variables • Chapter 2 Signal in port (external pins) – – In Out Inout Buffer Identifiers Data objects Data types Constants (Global) Signals (Global) Variables (Local) VHDL 2. Identifiers, data objects and data types ver. 9 b

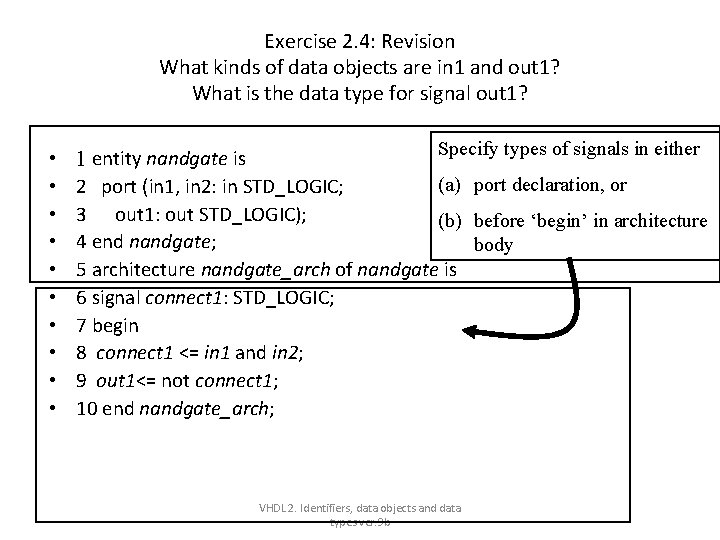

Exercise 2. 4: Revision What kinds of data objects are in 1 and out 1? What is the data type for signal out 1? • • • Specify types of signals in either 1 entity nandgate is (a) port declaration, or 2 port (in 1, in 2: in STD_LOGIC; 3 out 1: out STD_LOGIC); (b) before ‘begin’ in architecture 4 end nandgate; body 5 architecture nandgate_arch of nandgate is 6 signal connect 1: STD_LOGIC; 7 begin 8 connect 1 <= in 1 and in 2; 9 out 1<= not connect 1; 10 end nandgate_arch; VHDL 2. Identifiers, data objects and data types ver. 9 b

Different data types VHDL 2. Identifiers, data objects and data types ver. 9 b

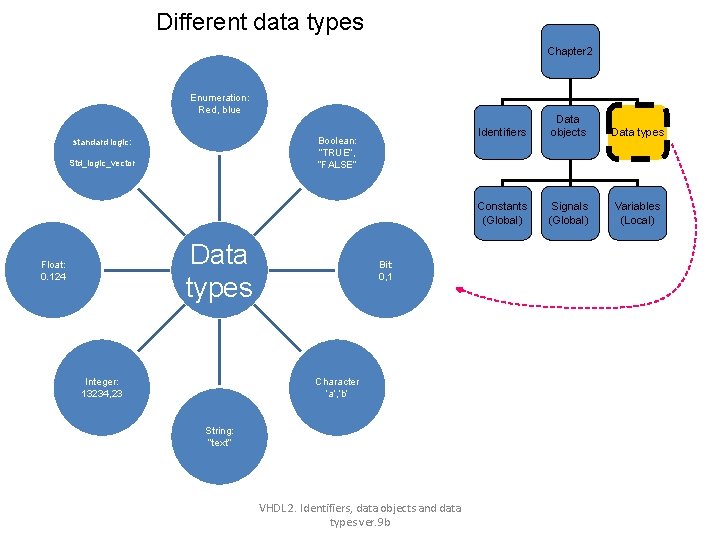

Different data types Chapter 2 Enumeration: Red, blue Boolean: “TRUE”, ”FALSE” standard logic: • Std_logic_vector Data types Float: 0. 124 Integer: 13234, 23 Bit: 0, 1 Character ‘a’, ’b’ String: “text” VHDL 2. Identifiers, data objects and data types ver. 9 b Identifiers Data objects Data types Constants (Global) Signals (Global) Variables (Local)

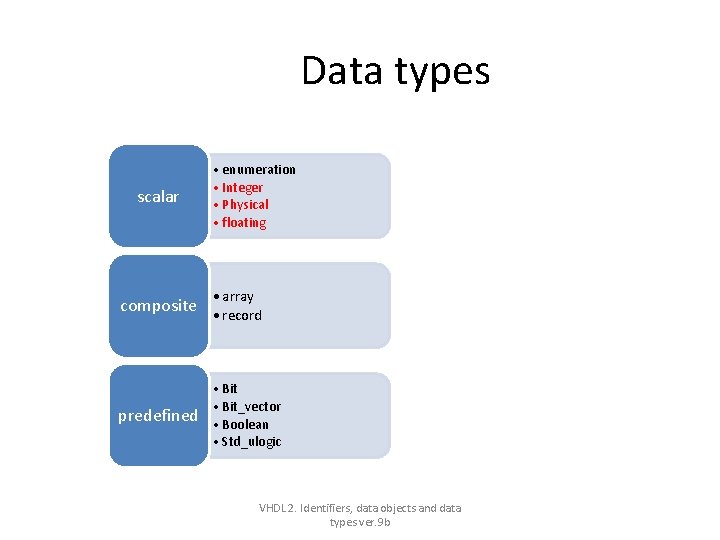

Data types scalar • enumeration • Integer • Physical • floating • array composite • record predefined • Bit_vector • Boolean • Std_ulogic VHDL 2. Identifiers, data objects and data types ver. 9 b

Scalar type • Is a type whose values have no elements. • Values cannot contain composite elements. • All values are in order. Each value of discrete or numeric have positional number associated with it. VHDL 2. Identifiers, data objects and data types ver. 9 b

Enumerated Types • An enumeration type is defined by listing (enumerating) all possible values explicitly. • Declaration Format: • TYPE type_name IS (enumeration_ident_list); type std_ulogic is (‘U’, ’ 0’, ’ 1’, ’Z’, ’W’, ’L’, ’H’, ’-’); • then we can declare signal carry : std_ulogic: =‘U’; • The definition explicitly enumerates all possible values that an object of this type can assume User defined values consisting of identifiers, character literals. VHDL 2. Identifiers, data objects and data types ver. 9 b

Predefined enumeration types • TYPE bit IS (`0', '1'); • TYPE boolean IS (false, true); • TYPE severity_level IS (note, warning, error, failure); • TYPE character IS (`a', 'b', 'c', . . . ); VHDL 2. Identifiers, data objects and data types ver. 9 b

More Examples • • TYPE Two_level_logic IS (`0', '1'); TYPE Three_level_logic IS (`0', '1', 'Z'); TYPE micro_op IS load, add, sub, mul); TYPE Opcode IS (Add, Add_with_carry, Sub_with_carr y, Complement); VHDL 2. Identifiers, data objects and data types ver. 9 b

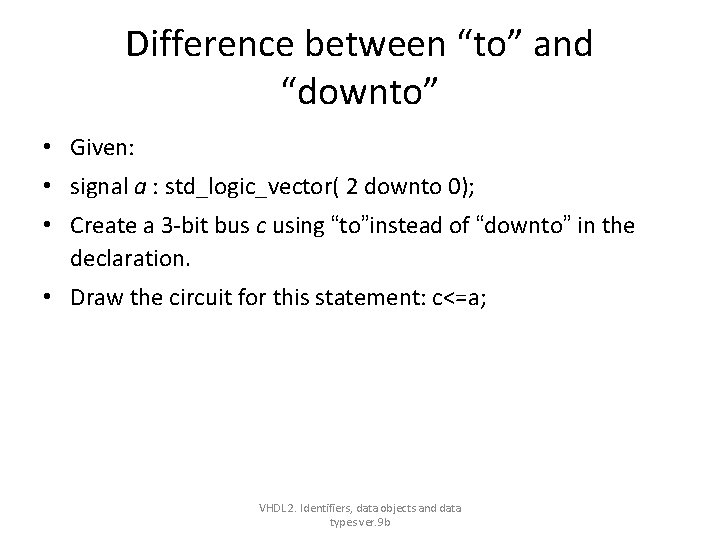

Difference between “to” and “downto” • Given: • signal a : std_logic_vector( 2 downto 0); • Create a 3 -bit bus c using “to”instead of “downto” in the declaration. • Draw the circuit for this statement: c<=a; VHDL 2. Identifiers, data objects and data types ver. 9 b

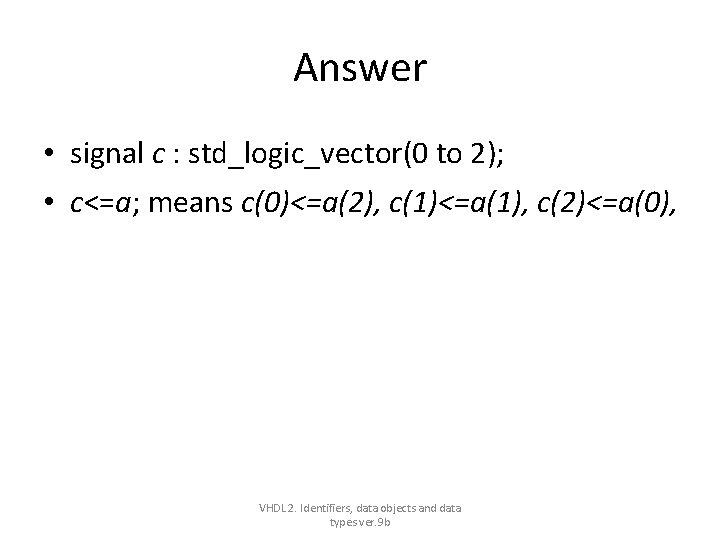

Answer • signal c : std_logic_vector(0 to 2); • c<=a; means c(0)<=a(2), c(1)<=a(1), c(2)<=a(0), VHDL 2. Identifiers, data objects and data types ver. 9 b

Exercises • Declare an emulation type of the traffic light. • Declare an emulation type of the outcome of rolling a dice. • Declare an emulation type of the 7 notes of music. • • Answer: type traffic_light is (yellow, green, red, yellow_green); signal tr 1: traffic_light; -- so tr 1 is a signal and can be one of the 4 cases. VHDL 2. Identifiers, data objects and data types ver. 9 b

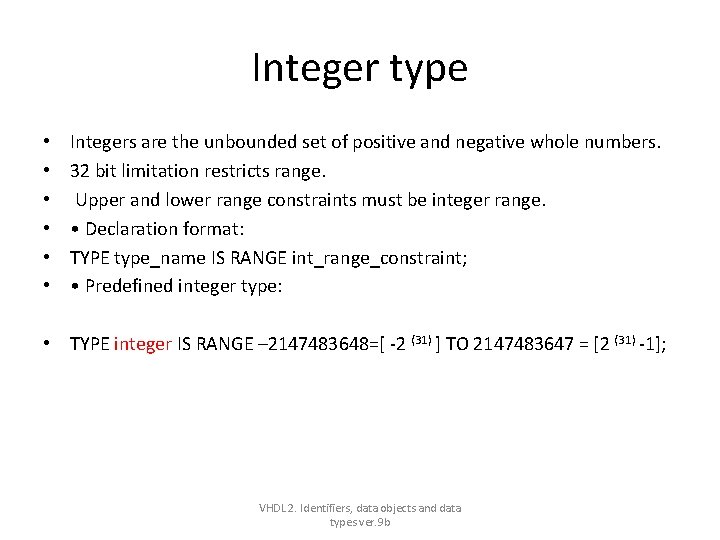

Integer type • • • Integers are the unbounded set of positive and negative whole numbers. 32 bit limitation restricts range. Upper and lower range constraints must be integer range. • Declaration format: TYPE type_name IS RANGE int_range_constraint; • Predefined integer type: • TYPE integer IS RANGE – 2147483648=[ -2 (31) ] TO 2147483647 = [2 (31) -1]; VHDL 2. Identifiers, data objects and data types ver. 9 b

Integer type (depends on your tool; it uses large amount of logic circuits for the implementation of integer/float operators) E. g. • Maximum range from -(2^31 -1) to (2^31 -1) • e. g. • variable a: integer range -255 to 255 VHDL 2. Identifiers, data objects and data types ver. 9 b

Floating type • Floating Points are the unbounded set of positive and negative numbers which contain a decimal point. • 32 bit limitation restricts range. • Upper and lower range constraints must contain a decimal point. • • Declaration format: • TYPE type_name IS RANGE range_constraint; • • Predefined floating point type: • TYPE real IS RANGE -1. 79769 E 308 TO 1. 79769 E 308; VHDL 2. Identifiers, data objects and data types ver. 9 b

Floating type • -1. 0 E 38 to 1. 0 E 38 • For encoding floating numbers, but usually not supported by synthesis tools of programmable logic because of its huge demand of resources. VHDL 2. Identifiers, data objects and data types ver. 9 b

Physical type • Describes objects in terms of a base unit, multiples of base unit, and a specified range. • Declaration format: • TYPE type_name IS RANGE range_constraints • UNITS • base_unit; • [ -- multiples; ] • END UNITS;

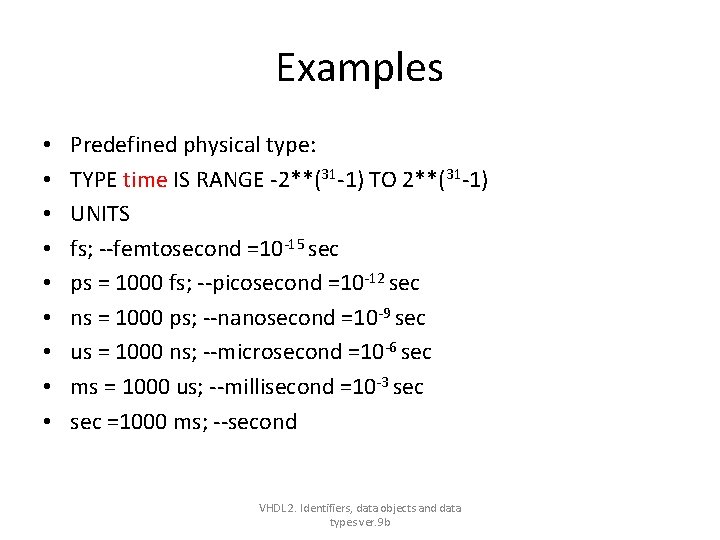

Examples • • • Predefined physical type: TYPE time IS RANGE -2**(31 -1) TO 2**(31 -1) UNITS fs; --femtosecond =10 -15 sec ps = 1000 fs; --picosecond =10 -12 sec ns = 1000 ps; --nanosecond =10 -9 sec us = 1000 ns; --microsecond =10 -6 sec ms = 1000 us; --millisecond =10 -3 sec =1000 ms; --second VHDL 2. Identifiers, data objects and data types ver. 9 b

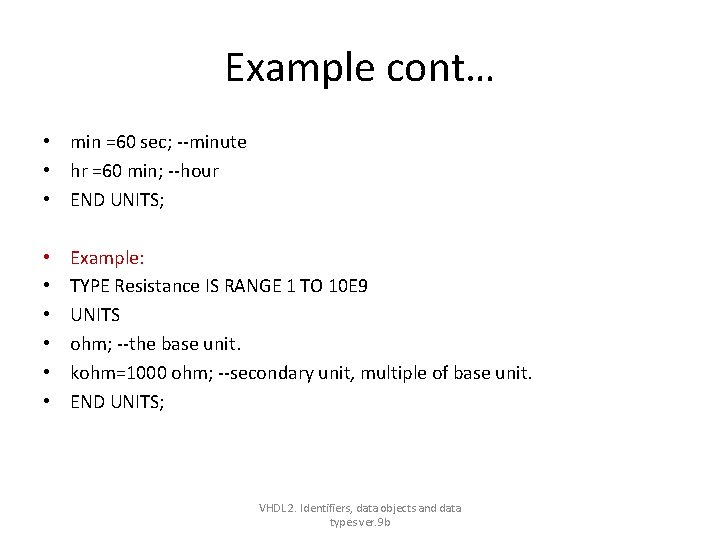

Example cont… • min =60 sec; --minute • hr =60 min; --hour • END UNITS; • • • Example: TYPE Resistance IS RANGE 1 TO 10 E 9 UNITS ohm; --the base unit. kohm=1000 ohm; --secondary unit, multiple of base unit. END UNITS; VHDL 2. Identifiers, data objects and data types ver. 9 b

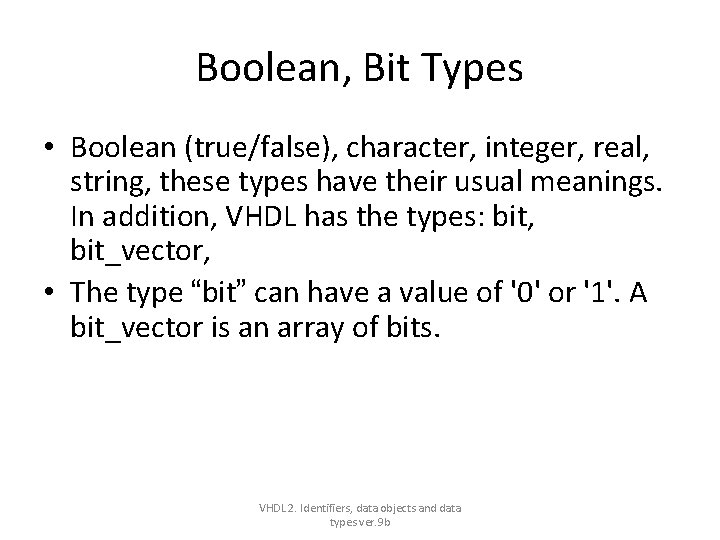

Boolean, Bit Types • Boolean (true/false), character, integer, real, string, these types have their usual meanings. In addition, VHDL has the types: bit, bit_vector, • The type “bit” can have a value of '0' or '1'. A bit_vector is an array of bits. VHDL 2. Identifiers, data objects and data types ver. 9 b

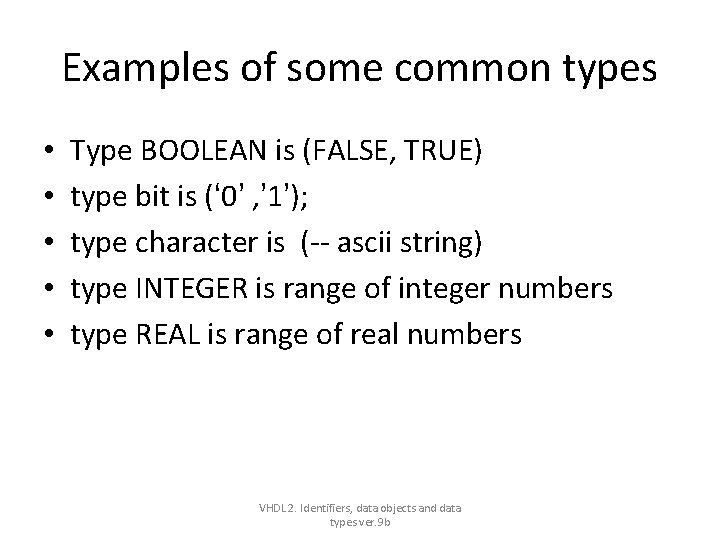

Examples of some common types • • • Type BOOLEAN is (FALSE, TRUE) type bit is (‘ 0’ , ’ 1’); type character is (-- ascii string) type INTEGER is range of integer numbers type REAL is range of real numbers VHDL 2. Identifiers, data objects and data types ver. 9 b

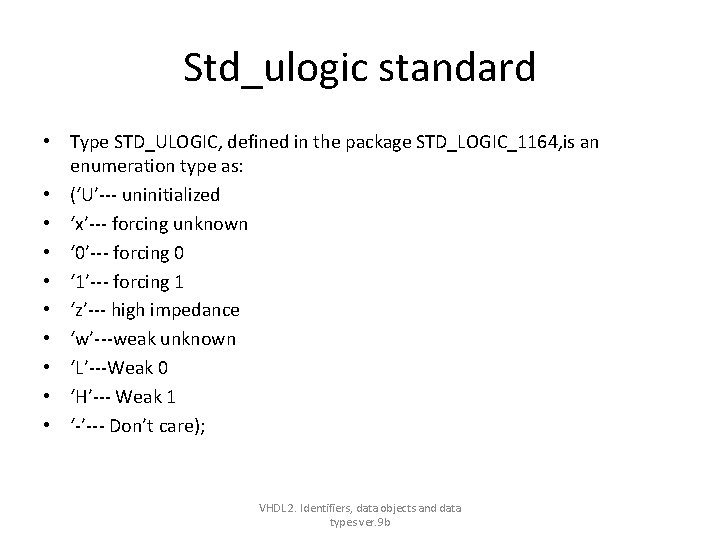

Std_ulogic standard • Type STD_ULOGIC, defined in the package STD_LOGIC_1164, is an enumeration type as: • (‘U’--- uninitialized • ‘x’--- forcing unknown • ‘ 0’--- forcing 0 • ‘ 1’--- forcing 1 • ‘z’--- high impedance • ‘w’---weak unknown • ‘L’---Weak 0 • ‘H’--- Weak 1 • ‘-’--- Don’t care); VHDL 2. Identifiers, data objects and data types ver. 9 b

Define Array or a bus VHDL 2. Identifiers, data objects and data types ver. 9 b

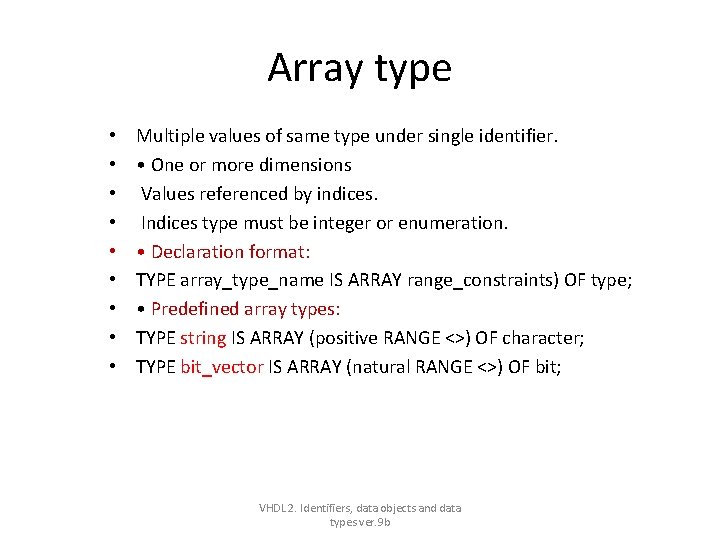

Array type • • • Multiple values of same type under single identifier. • One or more dimensions Values referenced by indices. Indices type must be integer or enumeration. • Declaration format: TYPE array_type_name IS ARRAY range_constraints) OF type; • Predefined array types: TYPE string IS ARRAY (positive RANGE <>) OF character; TYPE bit_vector IS ARRAY (natural RANGE <>) OF bit; VHDL 2. Identifiers, data objects and data types ver. 9 b

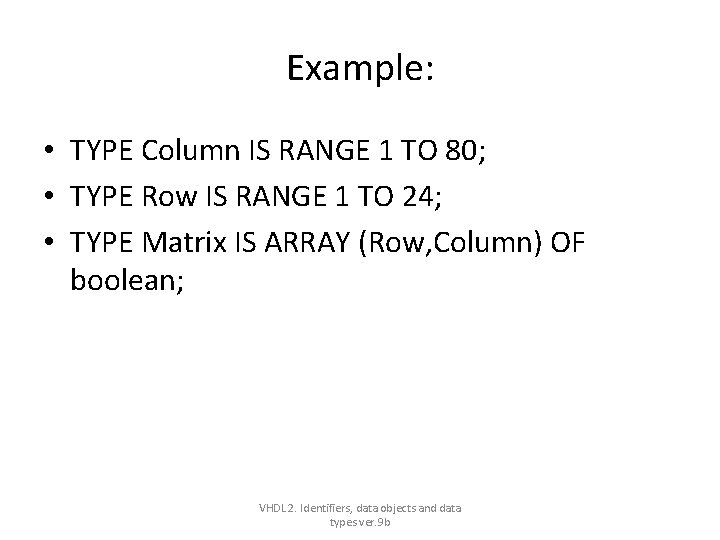

Example: • TYPE Column IS RANGE 1 TO 80; • TYPE Row IS RANGE 1 TO 24; • TYPE Matrix IS ARRAY (Row, Column) OF boolean; VHDL 2. Identifiers, data objects and data types ver. 9 b

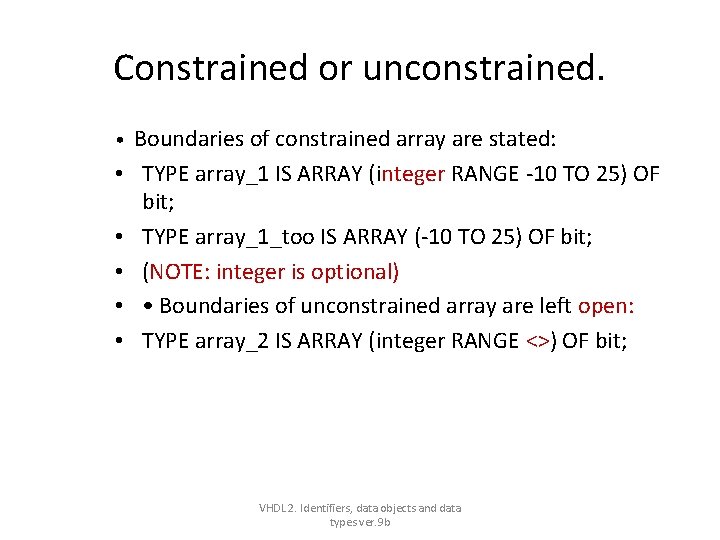

Constrained or unconstrained. • • • Boundaries of constrained array are stated: TYPE array_1 IS ARRAY (integer RANGE -10 TO 25) OF bit; TYPE array_1_too IS ARRAY (-10 TO 25) OF bit; (NOTE: integer is optional) • Boundaries of unconstrained array are left open: TYPE array_2 IS ARRAY (integer RANGE <>) OF bit; VHDL 2. Identifiers, data objects and data types ver. 9 b

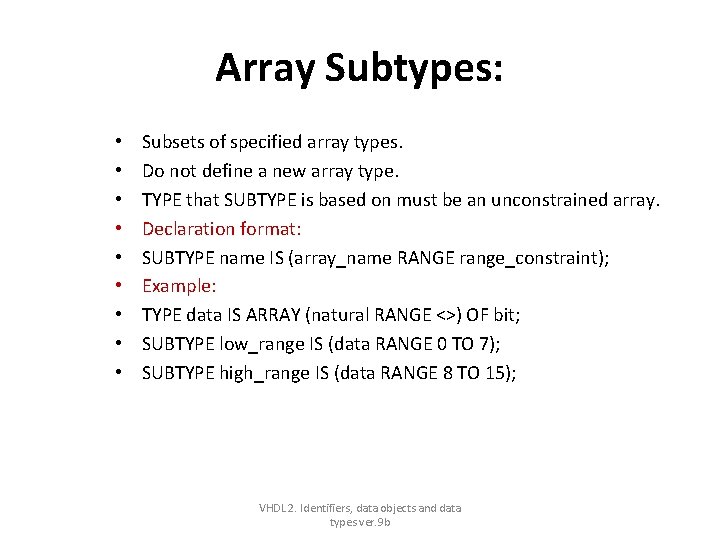

Array Subtypes: • • • Subsets of specified array types. Do not define a new array type. TYPE that SUBTYPE is based on must be an unconstrained array. Declaration format: SUBTYPE name IS (array_name RANGE range_constraint); Example: TYPE data IS ARRAY (natural RANGE <>) OF bit; SUBTYPE low_range IS (data RANGE 0 TO 7); SUBTYPE high_range IS (data RANGE 8 TO 15); VHDL 2. Identifiers, data objects and data types ver. 9 b

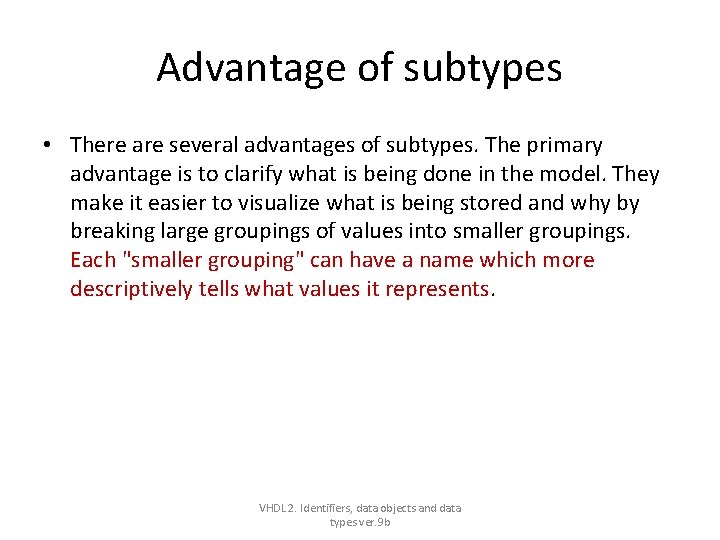

Advantage of subtypes • There are several advantages of subtypes. The primary advantage is to clarify what is being done in the model. They make it easier to visualize what is being stored and why by breaking large groupings of values into smaller groupings. Each "smaller grouping" can have a name which more descriptively tells what values it represents. VHDL 2. Identifiers, data objects and data types ver. 9 b

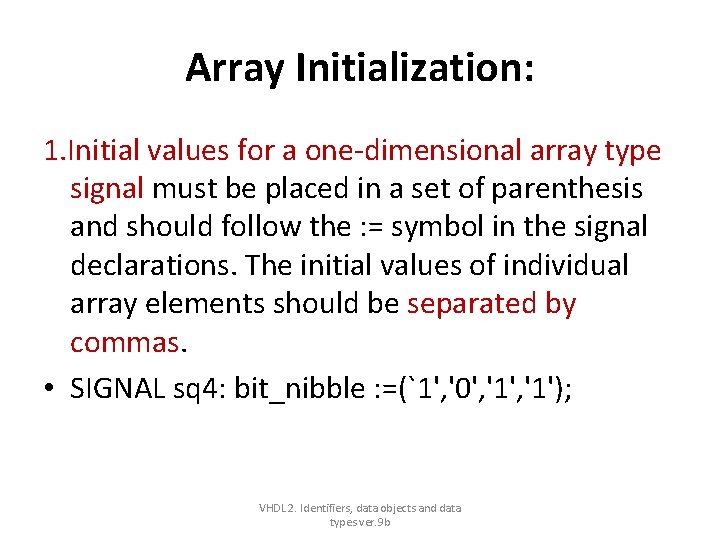

Array Initialization: 1. Initial values for a one-dimensional array type signal must be placed in a set of parenthesis and should follow the : = symbol in the signal declarations. The initial values of individual array elements should be separated by commas. • SIGNAL sq 4: bit_nibble : =(`1', '0', '1'); VHDL 2. Identifiers, data objects and data types ver. 9 b

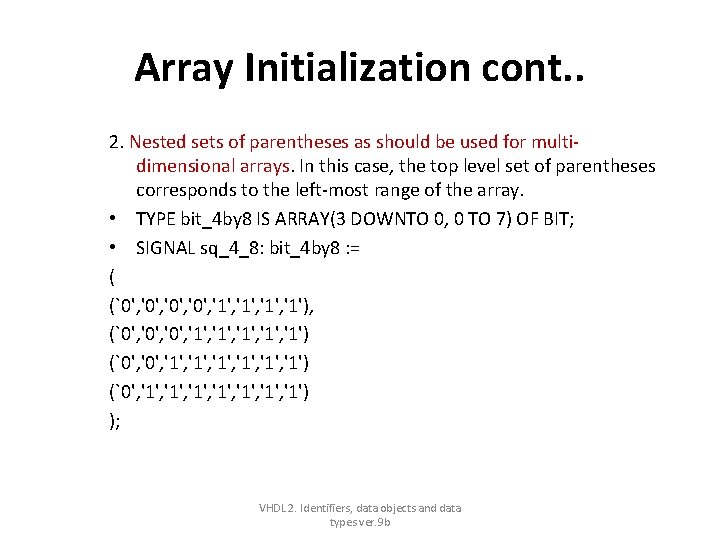

Array Initialization cont. . 2. Nested sets of parentheses as should be used for multidimensional arrays. In this case, the top level set of parentheses corresponds to the left-most range of the array. • TYPE bit_4 by 8 IS ARRAY(3 DOWNTO 0, 0 TO 7) OF BIT; • SIGNAL sq_4_8: bit_4 by 8 : = ( (`0', '0', '1', '1'), (`0', '0', '1', '1', '1') (`0', '1', '1', '1') ); VHDL 2. Identifiers, data objects and data types ver. 9 b

Exercise? ? ? • What are aggregates? • How an aggregate can be used to provide an initial value to an array object? • How aggregate specified in constant declaration? VHDL 2. Identifiers, data objects and data types ver. 9 b

Record type • A record type definition specifies one or more elements, each element having a different name and possibly a different type. • • Declaration format: • RECORD • element_declaration • {element_declaration} • END RECORD; VHDL 2. Identifiers, data objects and data types ver. 9 b

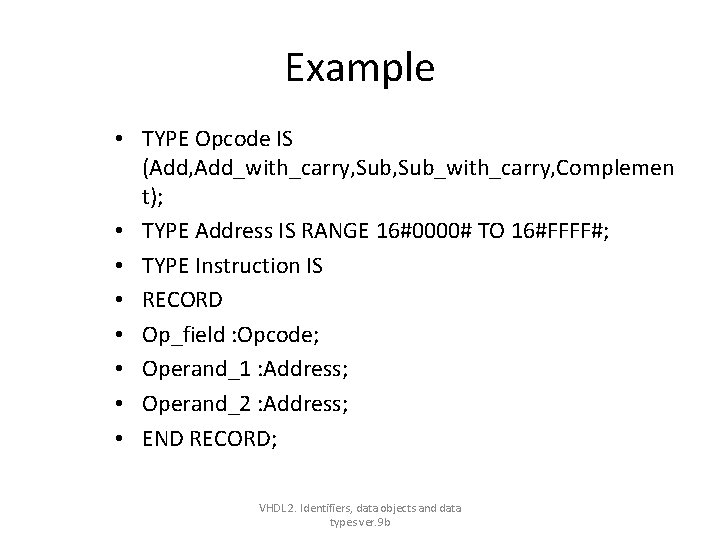

Example • TYPE Opcode IS (Add, Add_with_carry, Sub_with_carry, Complemen t); • TYPE Address IS RANGE 16#0000# TO 16#FFFF#; • TYPE Instruction IS • RECORD • Op_field : Opcode; • Operand_1 : Address; • Operand_2 : Address; • END RECORD; VHDL 2. Identifiers, data objects and data types ver. 9 b

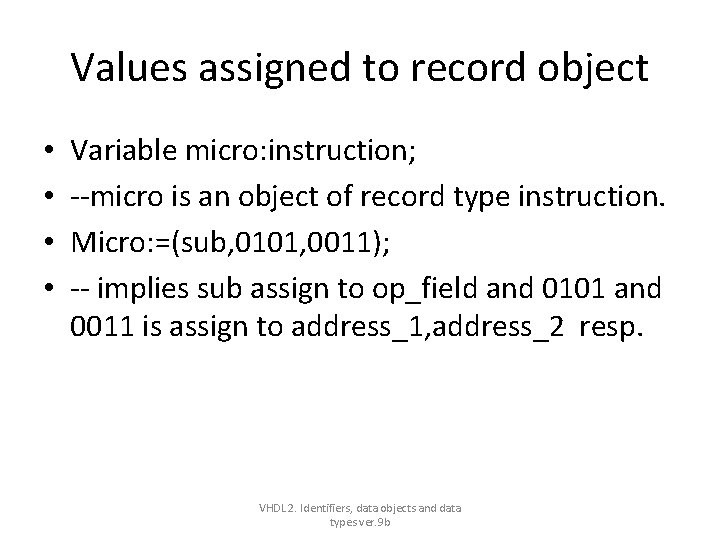

Values assigned to record object • • Variable micro: instruction; --micro is an object of record type instruction. Micro: =(sub, 0101, 0011); -- implies sub assign to op_field and 0101 and 0011 is assign to address_1, address_2 resp. VHDL 2. Identifiers, data objects and data types ver. 9 b

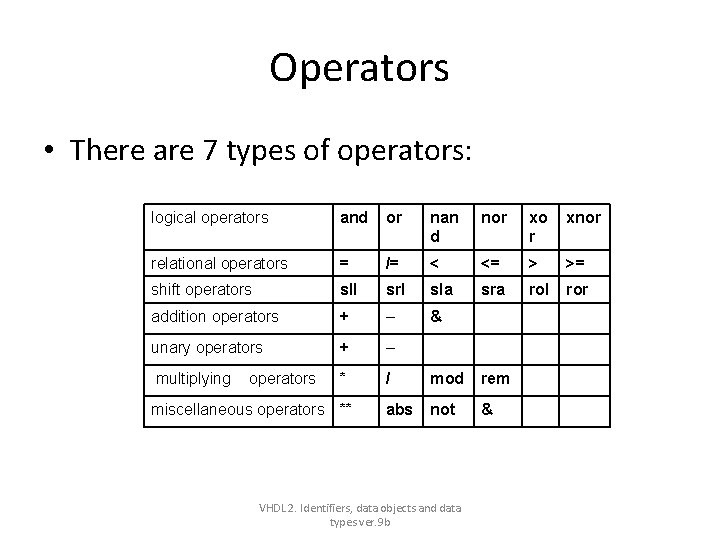

Operators • There are 7 types of operators: logical operators and or nan d nor xo r xnor relational operators = /= < <= > >= shift operators sll srl sla sra rol ror addition operators + – & unary operators + – multiplying * / mod rem abs not & operators miscellaneous operators ** VHDL 2. Identifiers, data objects and data types ver. 9 b

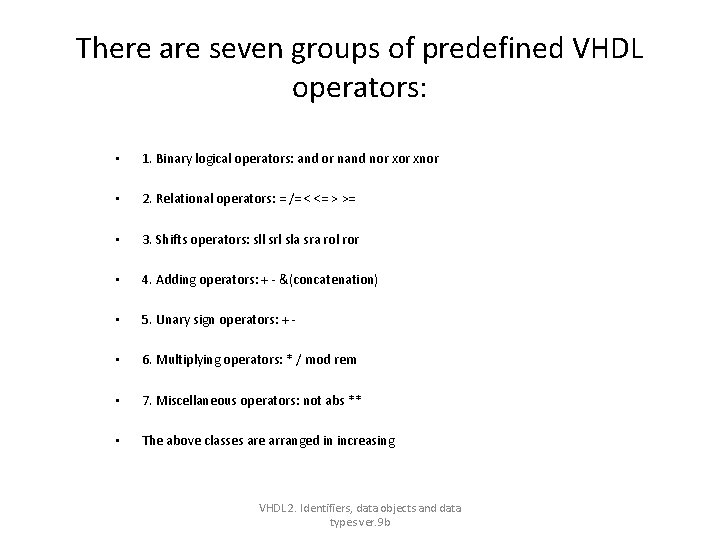

There are seven groups of predefined VHDL operators: • 1. Binary logical operators: and or nand nor xnor • 2. Relational operators: = /= < <= > >= • 3. Shifts operators: sll srl sla sra rol ror • 4. Adding operators: + - &(concatenation) • 5. Unary sign operators: + - • 6. Multiplying operators: * / mod rem • 7. Miscellaneous operators: not abs ** • The above classes are arranged in increasing VHDL 2. Identifiers, data objects and data types ver. 9 b

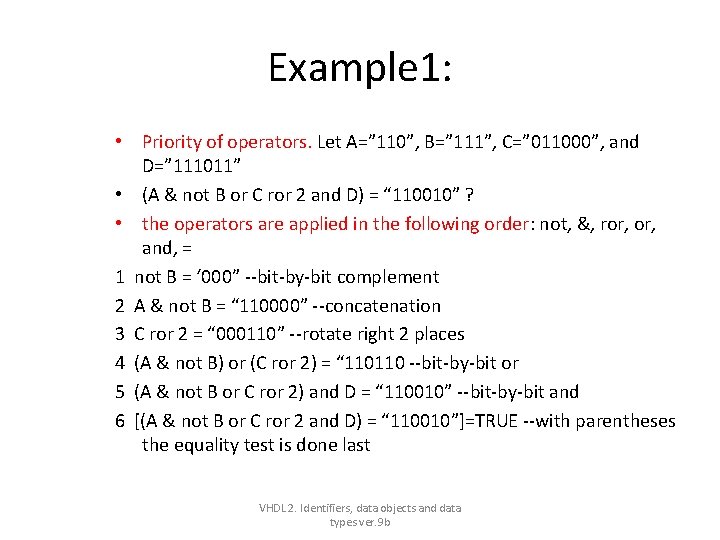

Example 1: • Priority of operators. Let A=” 110”, B=” 111”, C=” 011000”, and D=” 111011” • (A & not B or C ror 2 and D) = “ 110010” ? • the operators are applied in the following order: not, &, ror, and, = 1 not B = ‘ 000” --bit-by-bit complement 2 A & not B = “ 110000” --concatenation 3 C ror 2 = “ 000110” --rotate right 2 places 4 (A & not B) or (C ror 2) = “ 110110 --bit-by-bit or 5 (A & not B or C ror 2) and D = “ 110010” --bit-by-bit and 6 [(A & not B or C ror 2 and D) = “ 110010”]=TRUE --with parentheses the equality test is done last VHDL 2. Identifiers, data objects and data types ver. 9 b

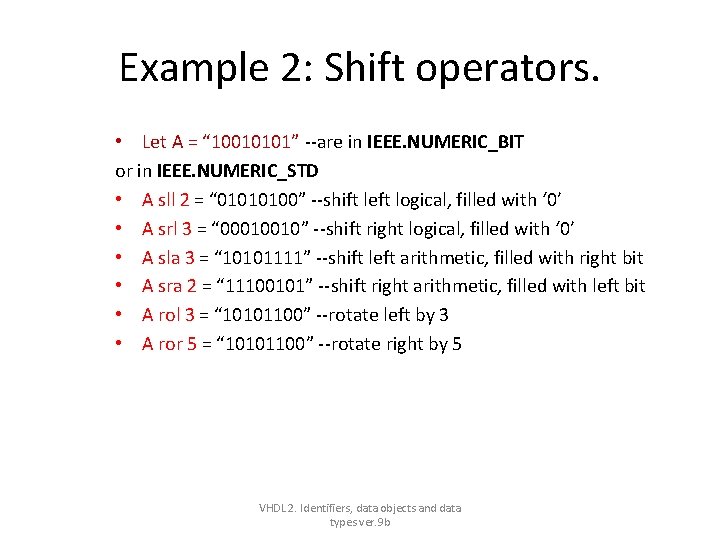

Example 2: Shift operators. • Let A = “ 10010101” --are in IEEE. NUMERIC_BIT or in IEEE. NUMERIC_STD • A sll 2 = “ 01010100” --shift left logical, filled with ‘ 0’ • A srl 3 = “ 00010010” --shift right logical, filled with ‘ 0’ • A sla 3 = “ 10101111” --shift left arithmetic, filled with right bit • A sra 2 = “ 11100101” --shift right arithmetic, filled with left bit • A rol 3 = “ 10101100” --rotate left by 3 • A ror 5 = “ 10101100” --rotate right by 5 VHDL 2. Identifiers, data objects and data types ver. 9 b

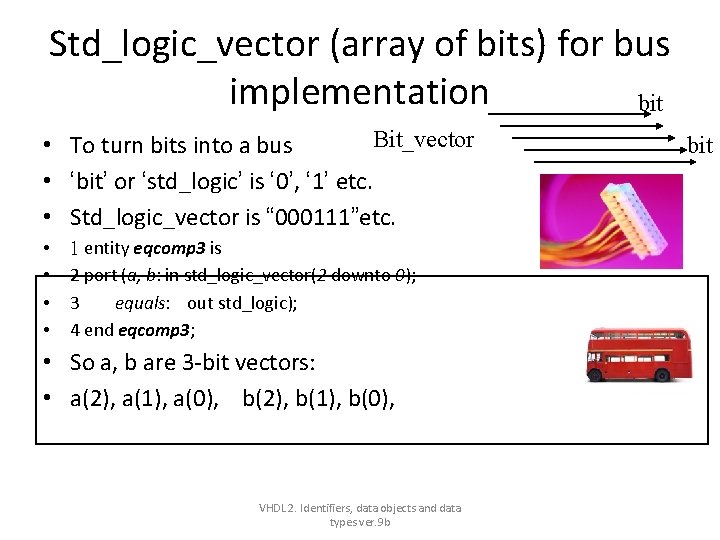

Std_logic_vector (array of bits) for bus implementation bit Bit_vector • To turn bits into a bus • ‘bit’ or ‘std_logic’ is ‘ 0’, ‘ 1’ etc. • Std_logic_vector is “ 000111”etc. • • 1 entity eqcomp 3 is 2 port (a, b: in std_logic_vector(2 downto 0); 3 equals: out std_logic); 4 end eqcomp 3; • So a, b are 3 -bit vectors: • a(2), a(1), a(0), b(2), b(1), b(0), VHDL 2. Identifiers, data objects and data types ver. 9 b bit

Entity • • Basic part of a VHDL model • • Entity describes the inputs and outputs of a component • • The port describes the pins of the block VHDL 2. Identifiers, data objects and data types ver. 9 b

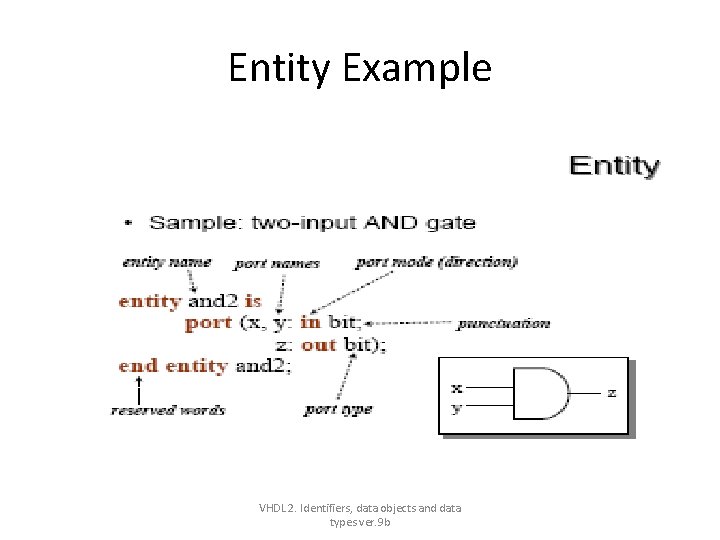

Entity Example VHDL 2. Identifiers, data objects and data types ver. 9 b

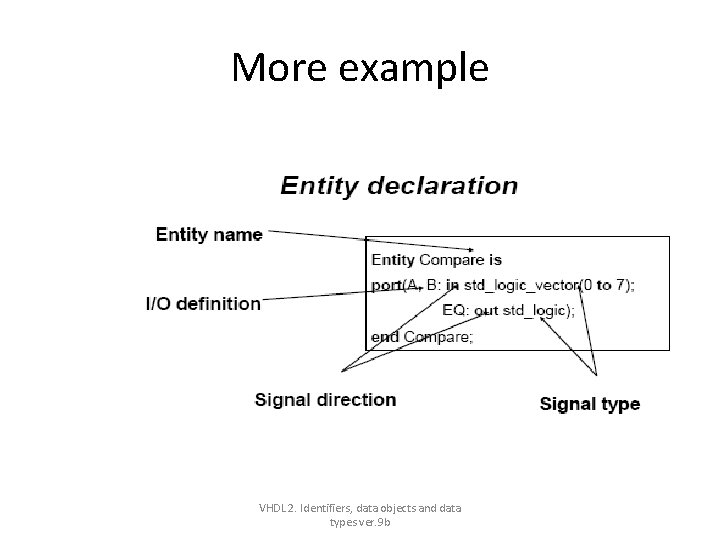

More example VHDL 2. Identifiers, data objects and data types ver. 9 b

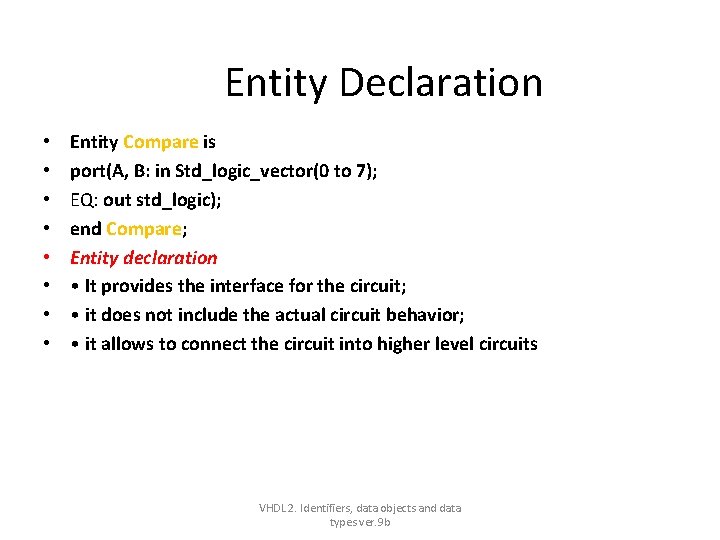

Entity Declaration • • Entity Compare is port(A, B: in Std_logic_vector(0 to 7); EQ: out std_logic); end Compare; Entity declaration • It provides the interface for the circuit; • it does not include the actual circuit behavior; • it allows to connect the circuit into higher level circuits VHDL 2. Identifiers, data objects and data types ver. 9 b

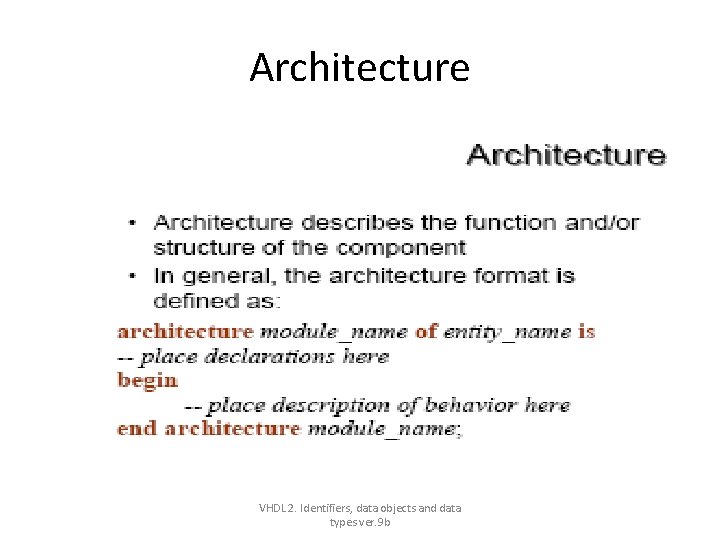

Architecture VHDL 2. Identifiers, data objects and data types ver. 9 b

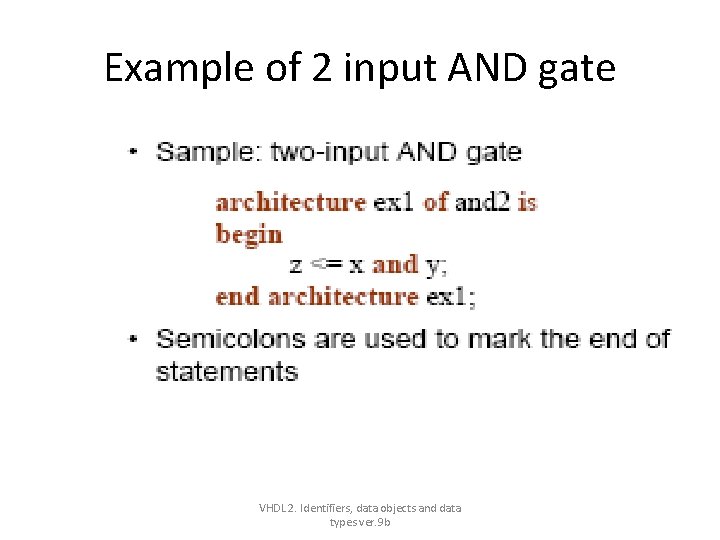

Example of 2 input AND gate VHDL 2. Identifiers, data objects and data types ver. 9 b

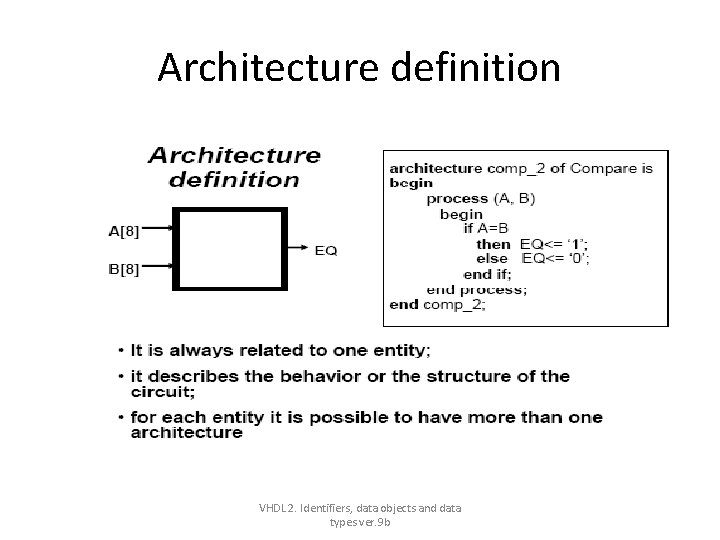

Architecture definition VHDL 2. Identifiers, data objects and data types ver. 9 b

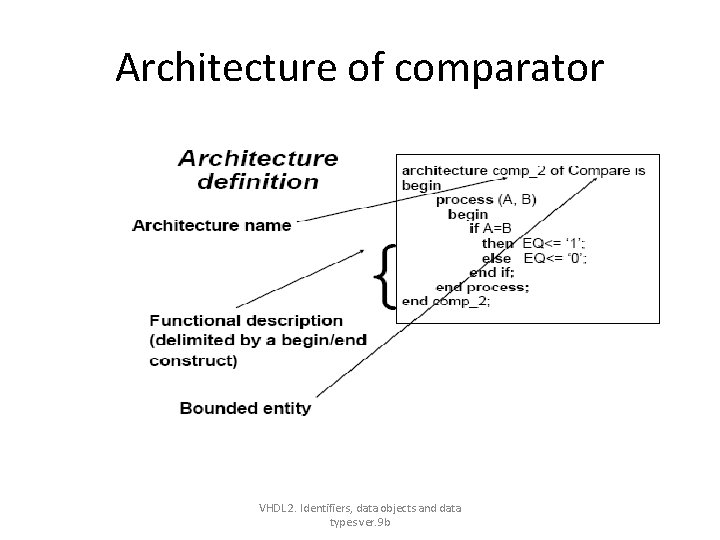

Architecture of comparator VHDL 2. Identifiers, data objects and data types ver. 9 b

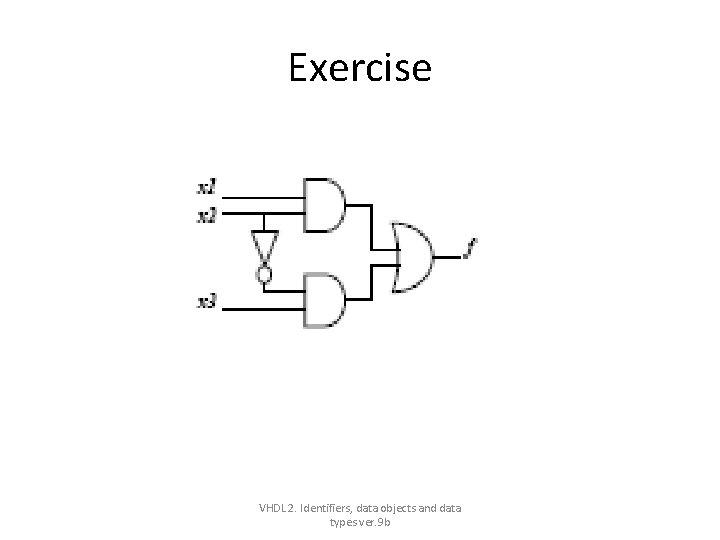

Exercise VHDL 2. Identifiers, data objects and data types ver. 9 b

Entity and architecture • The minimum VHDL design description must include at least one entity and its bounded architecture. But … VHDL 2. Identifiers, data objects and data types ver. 9 b

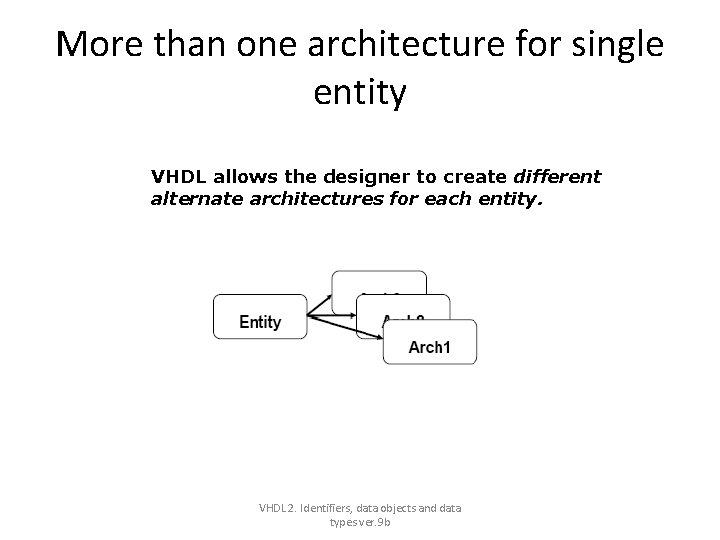

More than one architecture for single entity VHDL allows the designer to create different alternate architectures for each entity. VHDL 2. Identifiers, data objects and data types ver. 9 b

Define a circuit with two integer inputs A and B The output EQ is equal to ‘ 1’ if A=B+1. • • Entity Compare_int is port(A, B: in integer; EQ: out std_logic); end Compare_int; architecture comp of Compare_int is begin EQ<= ‘ 1’ when (A=B+1) else ‘ 0’; end comp; VHDL 2. Identifiers, data objects and data types ver. 9 b

Delays • Inertial • Transport • Delta delay VHDL 2. Identifiers, data objects and data types ver. 9 b

An advanced topic Resolved, Unresolved logic (Concept of Multi-value logic) VHDL 2. Identifiers, data objects and data types ver. 9 b

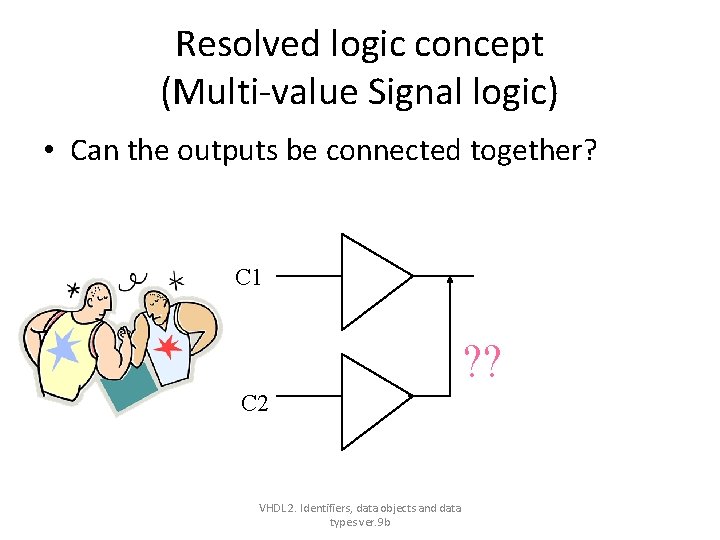

Resolved logic concept (Multi-value Signal logic) • Can the outputs be connected together? C 1 ? ? C 2 VHDL 2. Identifiers, data objects and data types ver. 9 b

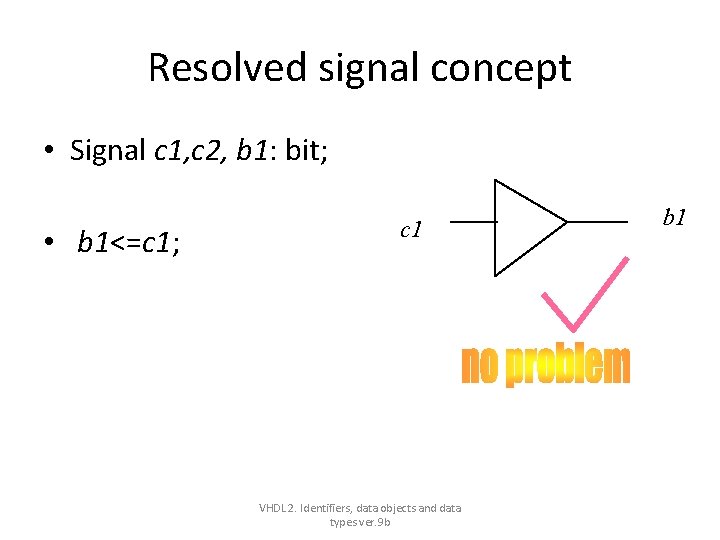

Resolved signal concept • Signal c 1, c 2, b 1: bit; • b 1<=c 1; c 1 VHDL 2. Identifiers, data objects and data types ver. 9 b b 1

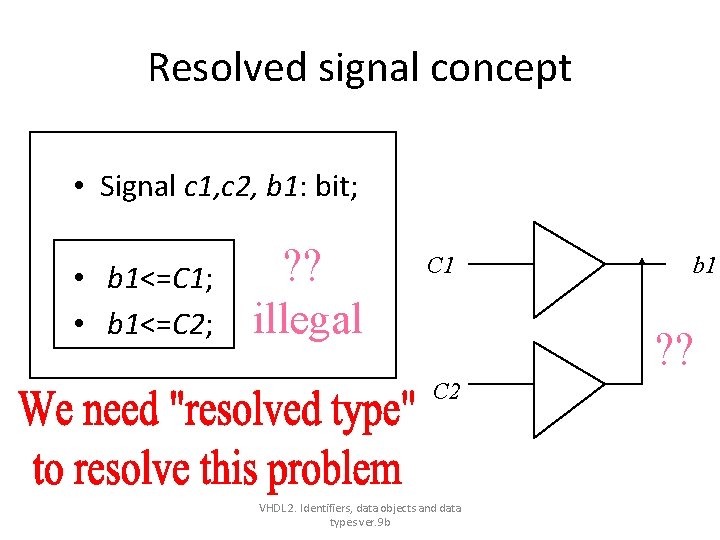

Resolved signal concept • Signal c 1, c 2, b 1: bit; • b 1<=C 1; • b 1<=C 2; ? ? illegal C 1 b 1 ? ? C 2 VHDL 2. Identifiers, data objects and data types ver. 9 b

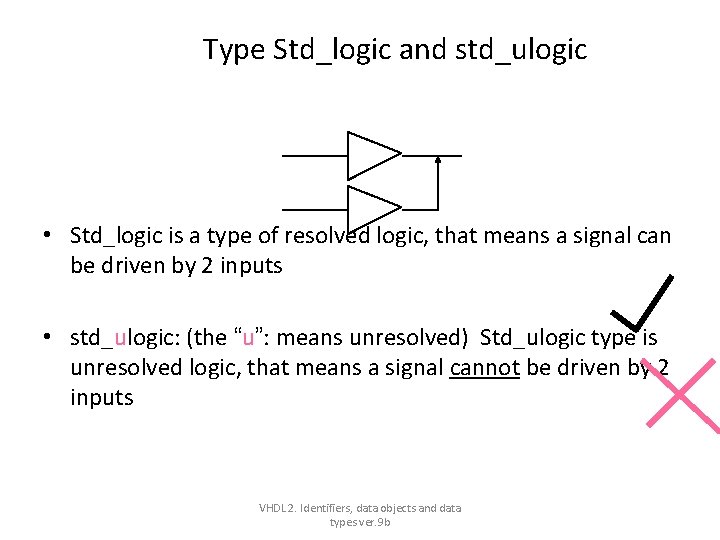

Type Std_logic and std_ulogic • Std_logic is a type of resolved logic, that means a signal can be driven by 2 inputs • std_ulogic: (the “u”: means unresolved) Std_ulogic type is unresolved logic, that means a signal cannot be driven by 2 inputs VHDL 2. Identifiers, data objects and data types ver. 9 b

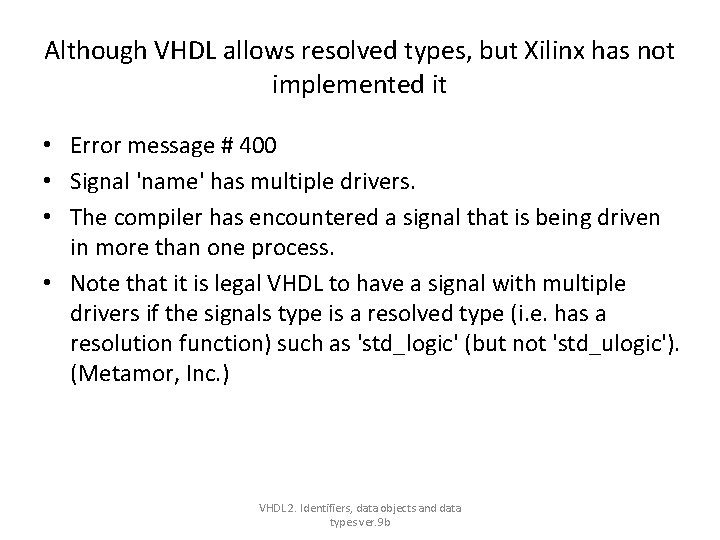

Although VHDL allows resolved types, but Xilinx has not implemented it • Error message # 400 • Signal 'name' has multiple drivers. • The compiler has encountered a signal that is being driven in more than one process. • Note that it is legal VHDL to have a signal with multiple drivers if the signals type is a resolved type (i. e. has a resolution function) such as 'std_logic' (but not 'std_ulogic'). (Metamor, Inc. ) VHDL 2. Identifiers, data objects and data types ver. 9 b

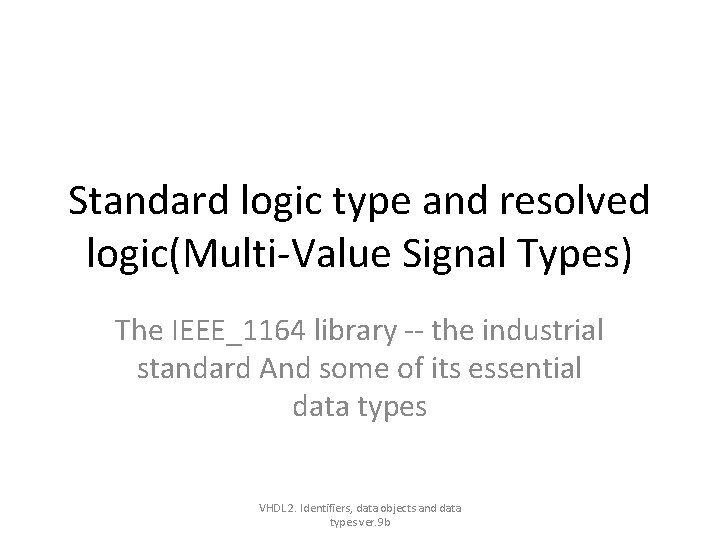

Standard logic type and resolved logic(Multi-Value Signal Types) The IEEE_1164 library -- the industrial standard And some of its essential data types VHDL 2. Identifiers, data objects and data types ver. 9 b

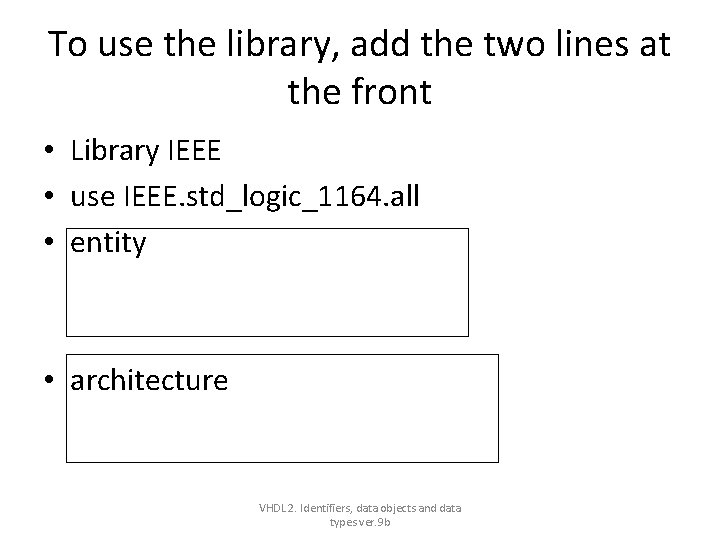

To use the library, add the two lines at the front • Library IEEE • use IEEE. std_logic_1164. all • entity • architecture VHDL 2. Identifiers, data objects and data types ver. 9 b

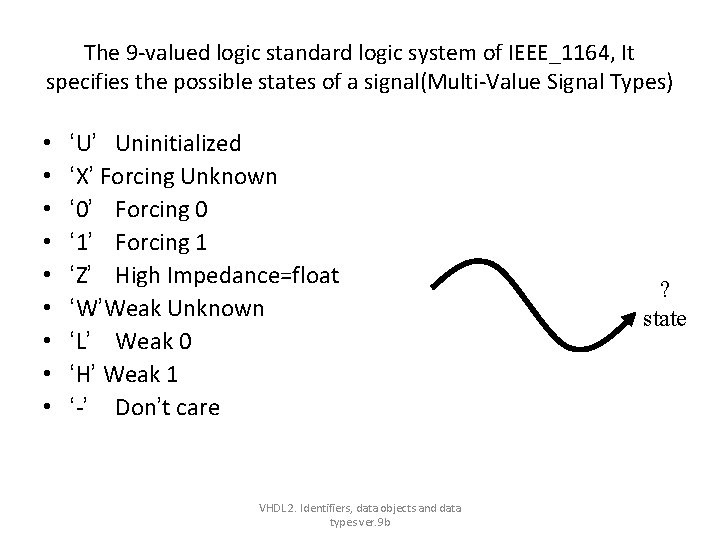

The 9 -valued logic standard logic system of IEEE_1164, It specifies the possible states of a signal(Multi-Value Signal Types) • • • ‘U’ Uninitialized ‘X’ Forcing Unknown ‘ 0’ Forcing 0 ‘ 1’ Forcing 1 ‘Z’ High Impedance=float ‘W’Weak Unknown ‘L’ Weak 0 ‘H’ Weak 1 ‘-’ Don’t care VHDL 2. Identifiers, data objects and data types ver. 9 b ? state

Resolved rules of the 9 -level logic • There are weak unknown, weak 0, weak 1 and force unknown, force 0, force 1 • when 2 signals tight together, the forcing signal dominates. • It is used to model the internal of a device. • In our applications here, the subset of the IEEE forcing values ‘X’ ‘ 0’ ‘ 1’ ‘Z’ are used. VHDL 2. Identifiers, data objects and data types ver. 9 b

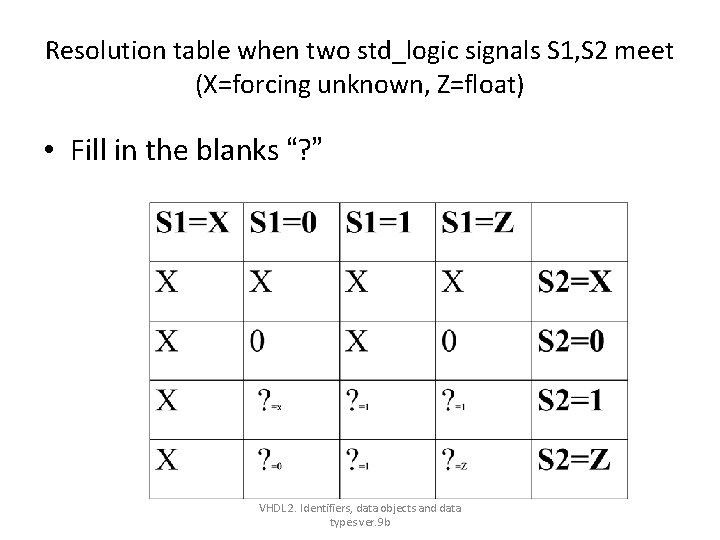

Resolution table when two std_logic signals S 1, S 2 meet (X=forcing unknown, Z=float) • Fill in the blanks “? ” VHDL 2. Identifiers, data objects and data types ver. 9 b

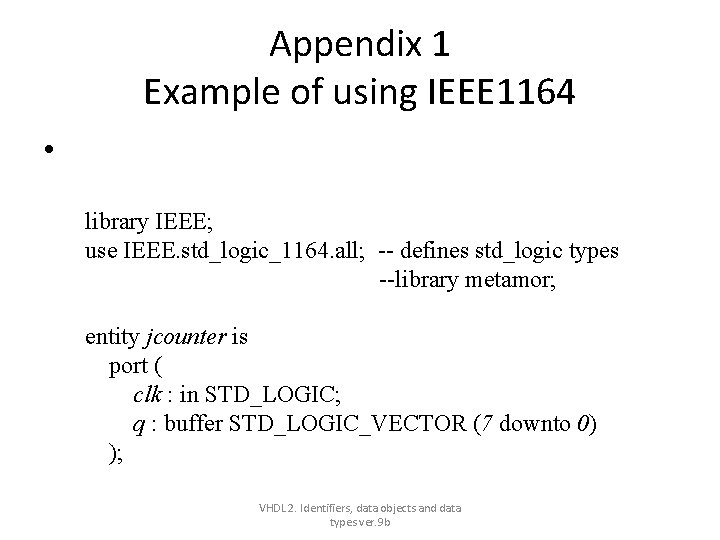

Appendix 1 Example of using IEEE 1164 • library IEEE; use IEEE. std_logic_1164. all; -- defines std_logic types --library metamor; entity jcounter is port ( clk : in STD_LOGIC; q : buffer STD_LOGIC_VECTOR (7 downto 0) ); VHDL 2. Identifiers, data objects and data types ver. 9 b

Quick Revision • You should learned – Identifier and usage – Different data objects (constant, signals, variables) – Different data types (Boolean , integer etc) – Resolved logic VHDL 2. Identifiers, data objects and data types ver. 9 b

- Slides: 87