Very Large Scale Integration II VLSI II Digital

- Slides: 29

Very Large Scale Integration II - VLSI II Digital Design Methodology Hayri Uğur UYANIK Devrim Yılmaz AKSIN ITU VLSI Laboratories Istanbul Technical University 1 www. vlsi. itu. edu. tr 10/3/2020

Outline l l Properties of Digital Circuits Implementation Methods – – – l l Programmable Logic Semi Custom Full Custom Project Constraints Digital Circuit Representations Digital Design Considerations Digital Design Flow 2 www. vlsi. itu. edu. tr 10/3/2020

Properties of Digital Circuits l Most general form – l For most cases, only 1 and 0 – l Inputs + Present State → Output + Next State No 0. 5 or Z Less specifications – – Delay Transition Power Area 3 www. vlsi. itu. edu. tr 10/3/2020

Properties of Digital Circuits l Combinational – l Inputs → Output Sequential – Moore Type l l – Inputs → Next State Present State → Output Mealy Type l Inputs + Present State → Output + Next State 4 www. vlsi. itu. edu. tr 10/3/2020

Properties of Digital Circuits l For most cases, only 1 and 0 – No 0. 5 or Z 5 www. vlsi. itu. edu. tr 10/3/2020

Properties of Digital Circuits l Delay = Gate Delay + Interconnect Delay 6 www. vlsi. itu. edu. tr 10/3/2020

Properties of Digital Circuits l Gate Delay 7 www. vlsi. itu. edu. tr 10/3/2020

Properties of Digital Circuits l Interconnect Delay 8 www. vlsi. itu. edu. tr 10/3/2020

Properties of Digital Circuits l Transition 9 www. vlsi. itu. edu. tr 10/3/2020

Implementation Methods l l l Programmable Logic (FPGA, CPLD, PLA, PAL) Semi Custom (ASIC, Standard Cell) Full Custom 10 www. vlsi. itu. edu. tr 10/3/2020

Programmable Logic l PLA and PAL 11 www. vlsi. itu. edu. tr 10/3/2020

Programmable Logic l CPLD 12 www. vlsi. itu. edu. tr 10/3/2020

Programmable Logic l FPGA – – CLB (LUT) Interconnect PLL, DCM I/O 13 www. vlsi. itu. edu. tr 10/3/2020

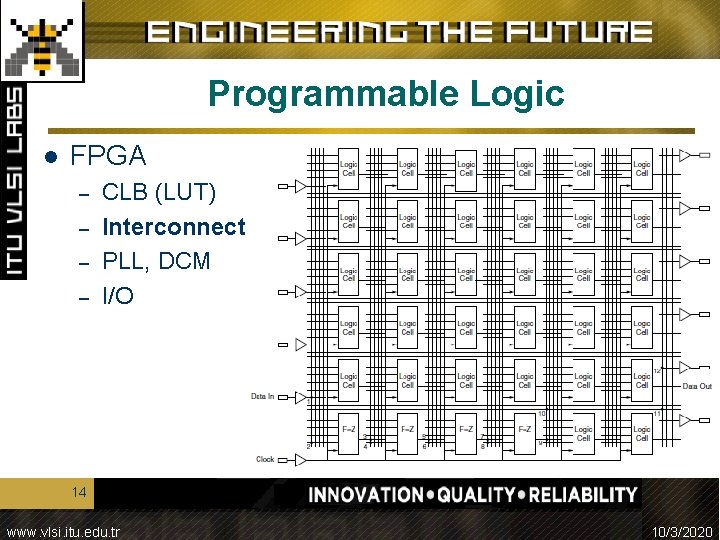

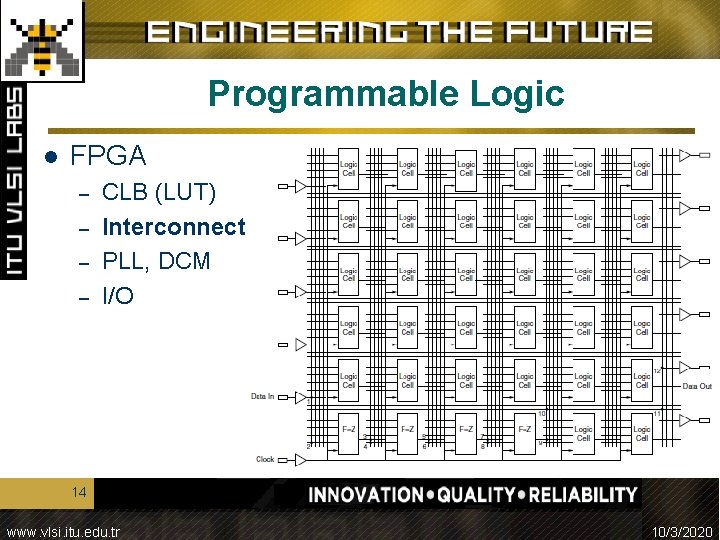

Programmable Logic l FPGA – – CLB (LUT) Interconnect PLL, DCM I/O 14 www. vlsi. itu. edu. tr 10/3/2020

Programmable Logic l FPGA – – CLB (LUT) Interconnect PLL, DCM I/O 15 www. vlsi. itu. edu. tr 10/3/2020

Programmable Logic l FPGA – – CLB (LUT) Interconnect PLL, DCM I/O 16 www. vlsi. itu. edu. tr 10/3/2020

Programmable Logic l FPGA Design – Architecture Driven l l l – No Area Control l – Dedicated Multipliers FFT CPU %1 utilization cost = %100 utilization cost Limited Power Control 17 www. vlsi. itu. edu. tr 10/3/2020

Semi Custom l l l Logic Cells from Process Technology Specific Generic Gates – – l Well Characterized Delay & Transition – – l Function Driving Capacity Supply Temperature Process Corner Load Systematic Layout (LEGO Parts) 18 www. vlsi. itu. edu. tr 10/3/2020

Full Custom l l Analog/RF design methods Design from scratch Custom schematic Custom layout 19 www. vlsi. itu. edu. tr 10/3/2020

Project Constraints Time to market Volume FPGA Semi Custom Full Custom Performance 20 www. vlsi. itu. edu. tr 10/3/2020

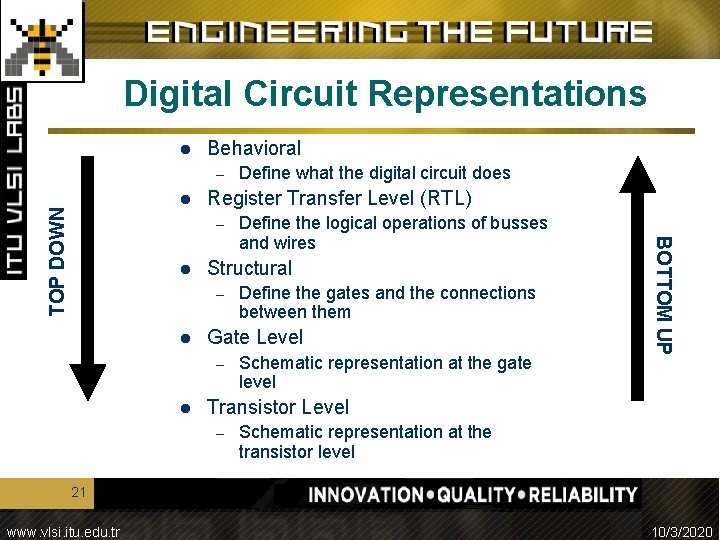

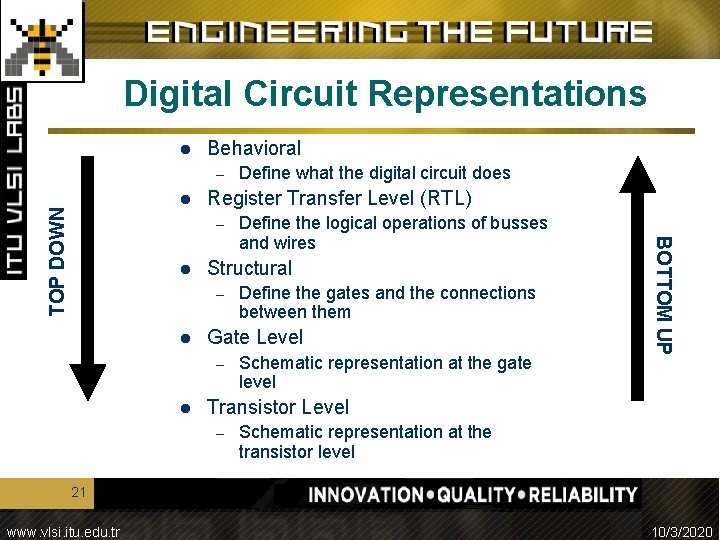

Digital Circuit Representations l Behavioral – Register Transfer Level (RTL) – l Structural – l Define the gates and the connections between them Gate Level – l Define the logical operations of busses and wires Schematic representation at the gate level BOTTOM UP TOP DOWN l Define what the digital circuit does Transistor Level – Schematic representation at the transistor level 21 www. vlsi. itu. edu. tr 10/3/2020

Digital Circuit Representations l Behavioral module FA_behavioral(a, b, carry_in, carry_out, sum); input a, b, carry_in; output carry_out, sum; reg [1: 0] tmp; reg carry_out, sum; always@(a or b or carry_in) begin tmp = a + b + carry_in; sum = tmp[0]; carry_out = tmp[1]; endmodule 22 www. vlsi. itu. edu. tr 10/3/2020

Digital Circuit Representations l Register Transfer Level (RTL) module FA_RTL(a, b, carry_in, carry_out, sum); input a, b, carry_in; output carry_out, sum; wire x 1, x 2, x 3; assign x 1 = a ^ b; assign sum = x 1 ^ carry_in; assign x 2 = x 1 & carry_in; assign x 3 = a & b; assign carry_out = x 2 | x 3; endmodule 23 www. vlsi. itu. edu. tr 10/3/2020

Digital Circuit Representations l Structural module FA_structural(a, b, carry_in, carry_out, sum); input a, b, carry_in; output carry_out, sum; wire x 1, x 2, x 3; XOR U 1(a, b, x 1); XOR U 2(x 1, carry_in, sum); AND U 3(x 1, carry_in, x 2); AND U 4(a, b, x 3); OR U 5(x 2, x 3, carry_out); endmodule 24 www. vlsi. itu. edu. tr 10/3/2020

Digital Circuit Representations l Gate Level 25 www. vlsi. itu. edu. tr 10/3/2020

Digital Circuit Representations l Transistor Level 26 www. vlsi. itu. edu. tr 10/3/2020

Digital Design Considerations l l l Digital Design ≠ “Let do and let pass, the world goes on by itself!” Vincent de Gournay Digital Design ≠ Do-it-all tools One should: – – Consider code style Consider coding for an architecture Investigate the tool outputs Know how synthesizer thinks 27 www. vlsi. itu. edu. tr 10/3/2020

Digital Design Flow 28 www. vlsi. itu. edu. tr 10/3/2020

References l l l l http: //ocw. mit. edu/NR/rdonlyres/Electrical-Engineering-and. Computer-Science/6 -111 Spring 2004/F 19 D 2 F 2 D-5 FE 9 -4 C 59 -AA 67 D 2113639 B 022/0/l 6_fsm_to. CMS_080904. pdf http: //asic-soc. blogspot. com/2008/12/transition-delay-andpropagation-delay. html http: //asic-soc. blogspot. com/2008/10/net-delay. html http: //people. bu. edu/rknepper/sc 571/chapter 4_b. ppt http: //www. xilinx. com/publications/products/cpld/logic_handbook. pdf http: //en. wikipedia. org/wiki/Adder_(electronics) http: //www. askkia. com/articles/how-to-create-a-single-bit-fulladder. html 29 www. vlsi. itu. edu. tr 10/3/2020