VerilogHDL for Synchronous Sequential Circuit 2152022 Department of

![Verilog Examples Tabular Results GROUP CREATE state = state[1] state[0] ; INPUTS A clk Verilog Examples Tabular Results GROUP CREATE state = state[1] state[0] ; INPUTS A clk](https://slidetodoc.com/presentation_image_h2/b7c85be6a7e095bb07dab0e9ef167026/image-17.jpg)

![Verilog Examples Tabular Results GROUP CREATE state = state[1] state[0] ; INPUTS clock reset; Verilog Examples Tabular Results GROUP CREATE state = state[1] state[0] ; INPUTS clock reset;](https://slidetodoc.com/presentation_image_h2/b7c85be6a7e095bb07dab0e9ef167026/image-21.jpg)

- Slides: 22

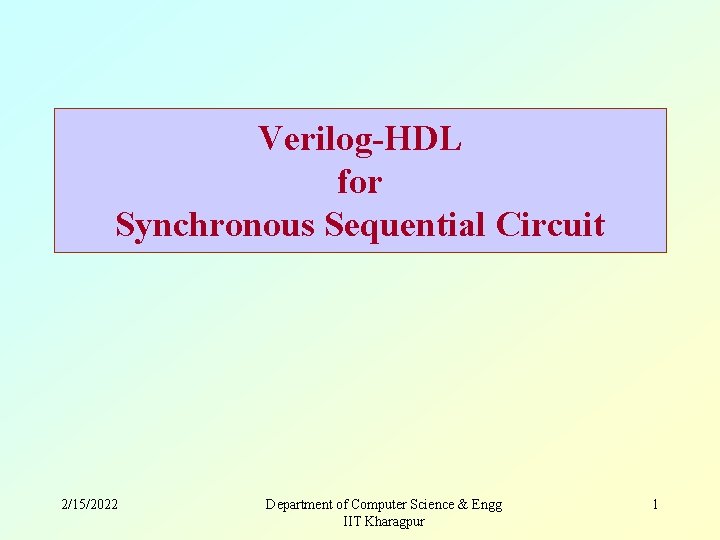

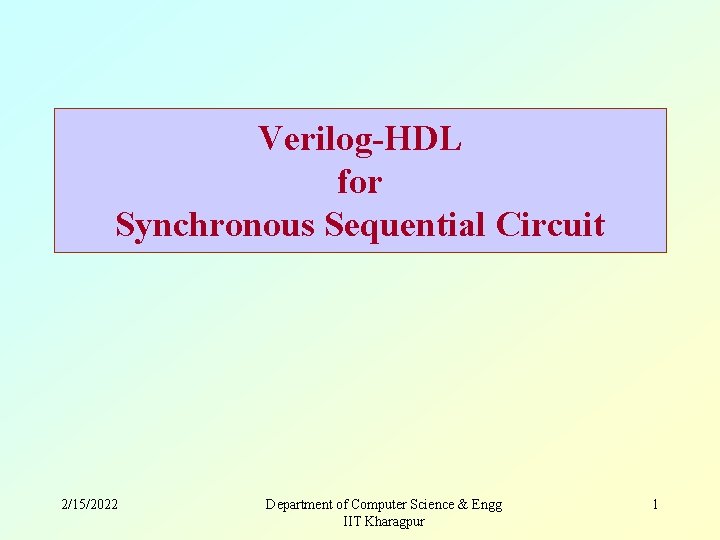

Verilog-HDL for Synchronous Sequential Circuit 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 1

Verilog Examples Write a Verilog description for a D flip-flop with a positive edge reset and a negative edge triggered clock. Use if-else statement. // D Flip-Flop (Behaviorally), Module DFF with synchronous reset, file name: dfflop. v module dfflop(q, d, clk, reset); input d, clk, reset; output q; reg q; // Always do this when the reset is positive edge or clock is negative edge always @(posedge reset or negedge clk) // If it is reset, q will equal to zero if (reset) q = 1'b 0; // If it is clock, q will equal to d else q = d; endmodule 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 2

Verilog Examples Tabular Results INPUTS reset clk d; OUTPUTS q; UNIT ns; RADIX HEX; PATTERN 0. 0> 1 0 0 = 0 2. 5> 0 1 0 = 0 5. 0> 0 0 1 = 1 7. 5> 0 1 1 = 1 10. 0> 0 0 1 = 1 12. 5> 0 1 0 = 1 15. 0> 0 0 0 = 0 17. 5> 1 1 1 = 0 20. 0> 0 0 0 = 0 22. 5> 0 1 0 = 0 25. 0> X X X = X 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 3

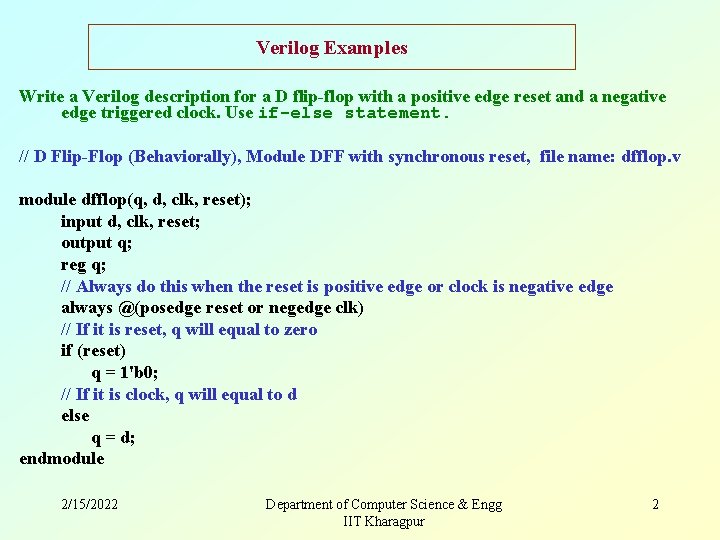

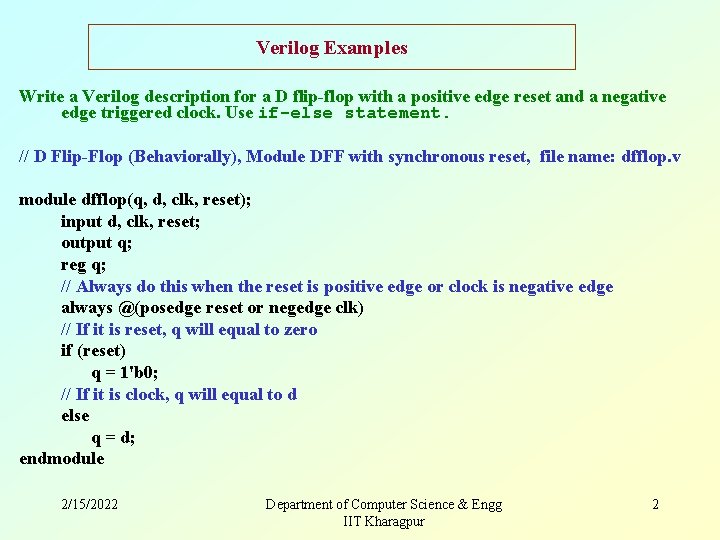

Verilog Examples Write a Verilog description for a D flip-flop with a positive edge triggered clock and a negative edge clear input. Use if-else statement. // Description D Flip Flop, file name: D. v module D_ff(Q, Q_bar, CLR, CLK, D); input CLR, CLK, D; output Q, Q_bar; reg Q, Q_bar; always @(posedge CLK or negedge CLR) begin if (!CLR) begin Q <= 1'b 0; Q_bar <= 1'b 1; end else begin Q <= D; Q_bar <= !D; end endmodule 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 4

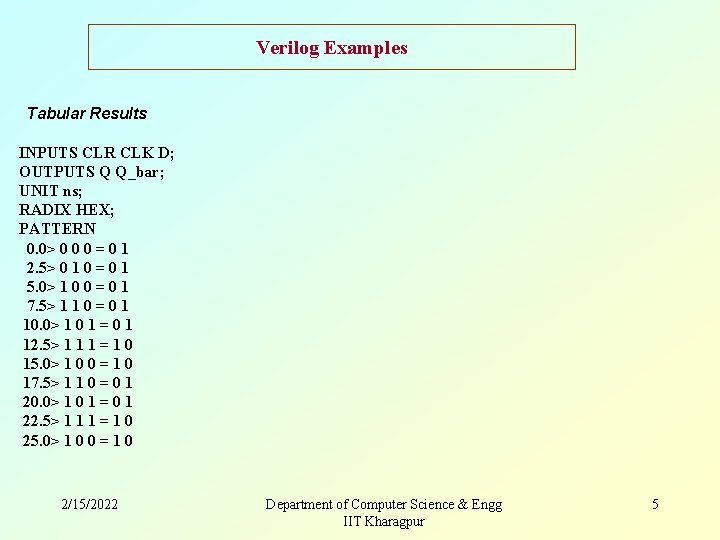

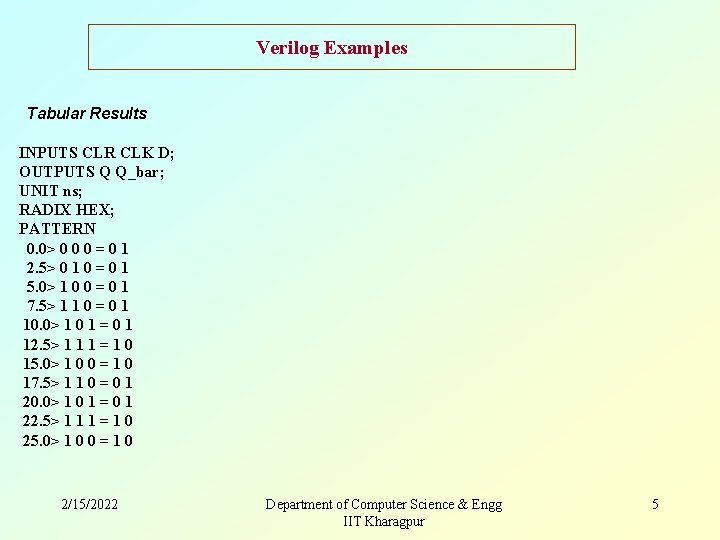

Verilog Examples Tabular Results INPUTS CLR CLK D; OUTPUTS Q Q_bar; UNIT ns; RADIX HEX; PATTERN 0. 0> 0 0 0 = 0 1 2. 5> 0 1 0 = 0 1 5. 0> 1 0 0 = 0 1 7. 5> 1 1 0 = 0 1 10. 0> 1 0 1 = 0 1 12. 5> 1 1 1 = 1 0 15. 0> 1 0 0 = 1 0 17. 5> 1 1 0 = 0 1 20. 0> 1 0 1 = 0 1 22. 5> 1 1 1 = 1 0 25. 0> 1 0 0 = 1 0 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 5

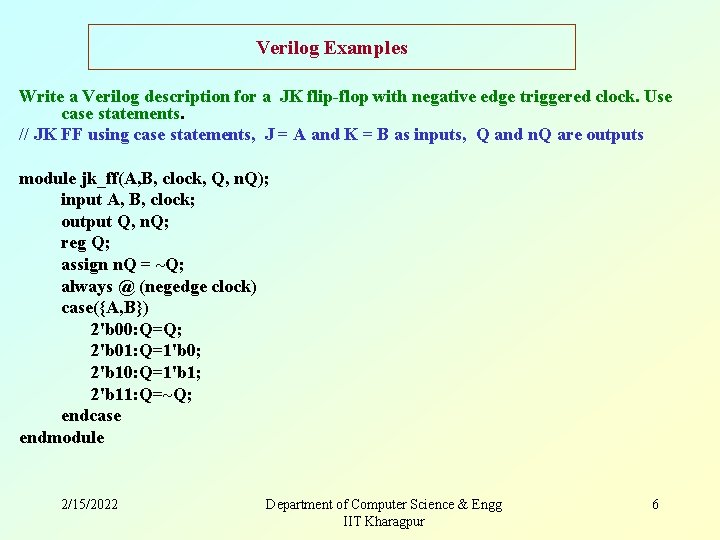

Verilog Examples Write a Verilog description for a JK flip-flop with negative edge triggered clock. Use case statements. // JK FF using case statements, J = A and K = B as inputs, Q and n. Q are outputs module jk_ff(A, B, clock, Q, n. Q); input A, B, clock; output Q, n. Q; reg Q; assign n. Q = ~Q; always @ (negedge clock) case({A, B}) 2'b 00: Q=Q; 2'b 01: Q=1'b 0; 2'b 10: Q=1'b 1; 2'b 11: Q=~Q; endcase endmodule 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 6

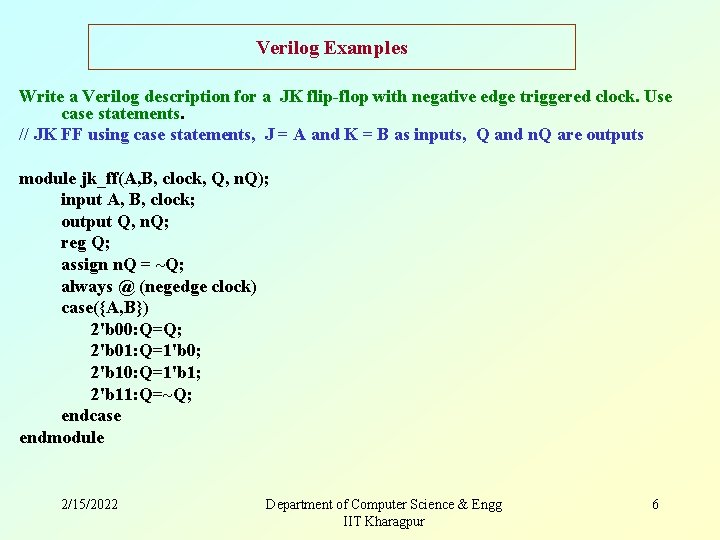

Verilog Examples Tabular Results INPUTS clock A B; OUTPUTS Q n. Q; UNIT ns; RADIX HEX; PATTERN 0. 0> 0 0 0 = 0 1 2. 5> 1 0 0 = 0 1 5. 0> 0 0 0 = 0 1 7. 5> 1 0 1 = 0 1 10. 0> 0 0 1 = 0 1 12. 5> 1 1 0 = 0 1 15. 0> 0 1 0 = 1 0 17. 5> 1 1 1 = 1 0 20. 0> 0 1 1 = 0 1 22. 5> 1 0 0 = 0 1 25. 0> 0 0 0 = 0 1 27. 5> 1 0 0 = 0 1 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 7

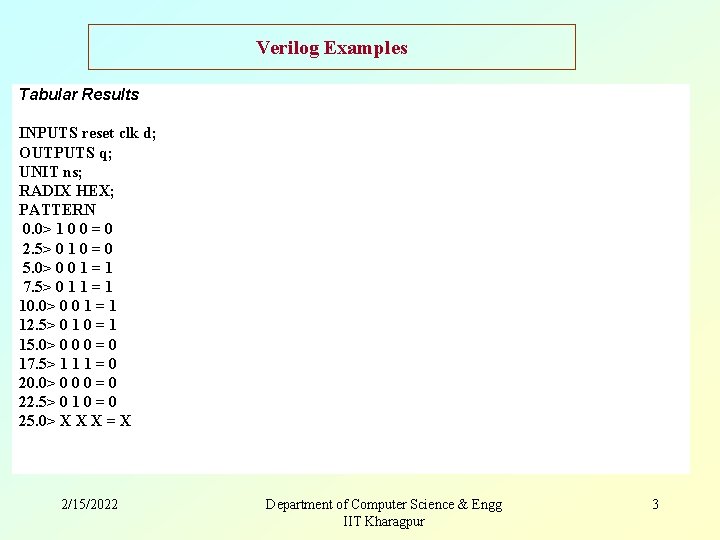

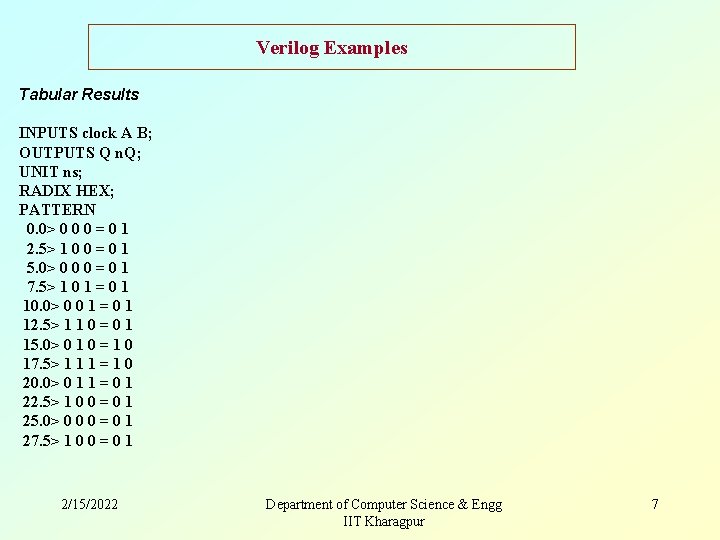

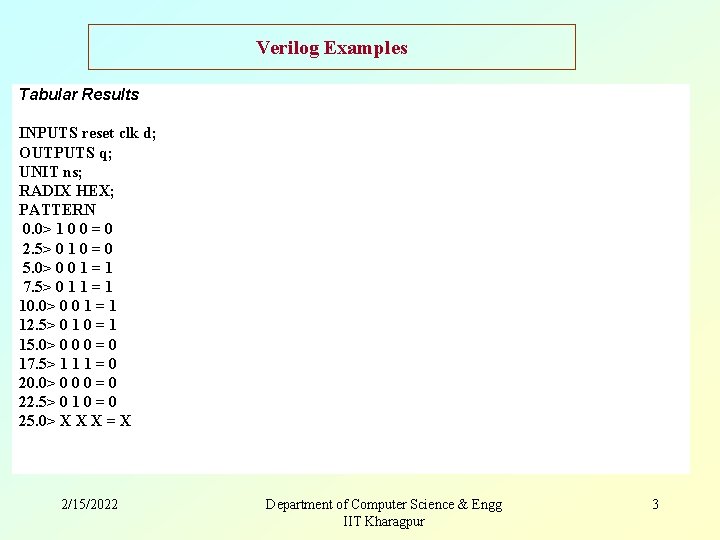

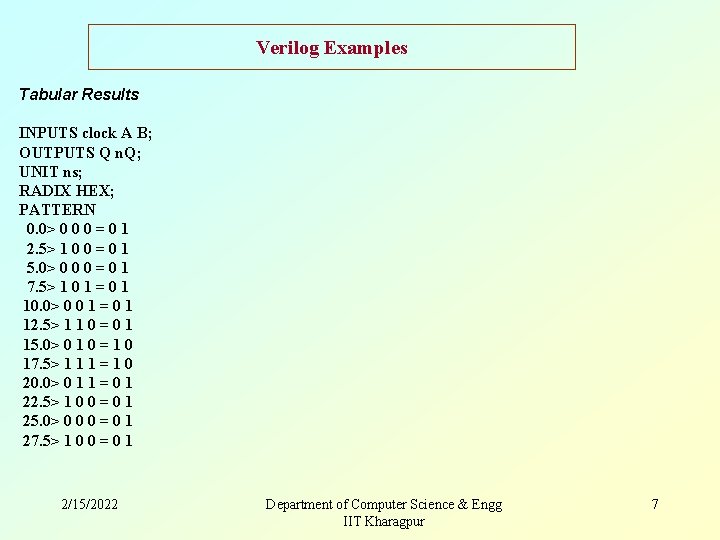

Verilog Examples Write a Verilog description for the state diagram of Figure 5. 21. Use a reset input so that the hardware can be initialized. Figure 5. 21 is redrawn below: 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 8

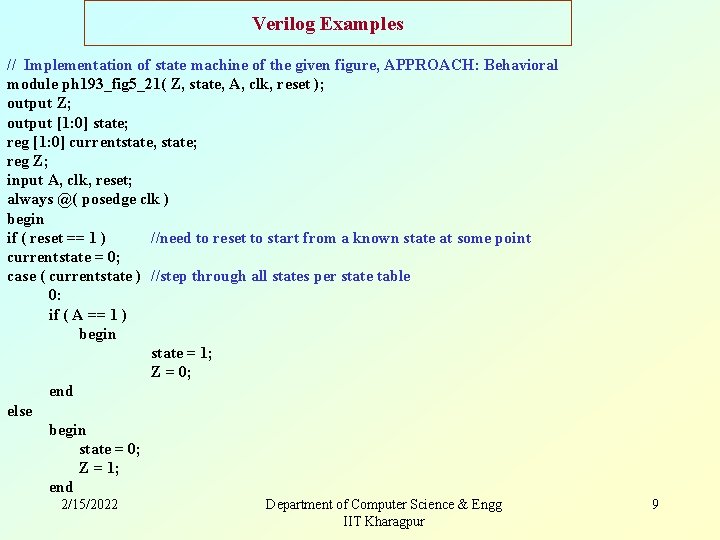

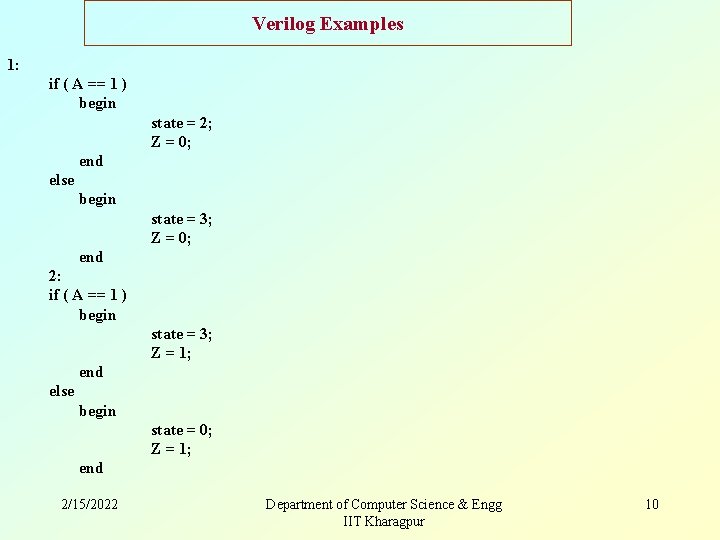

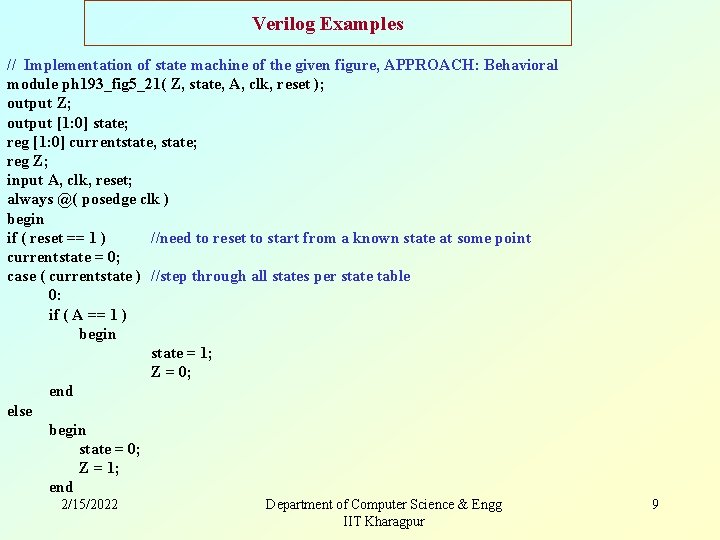

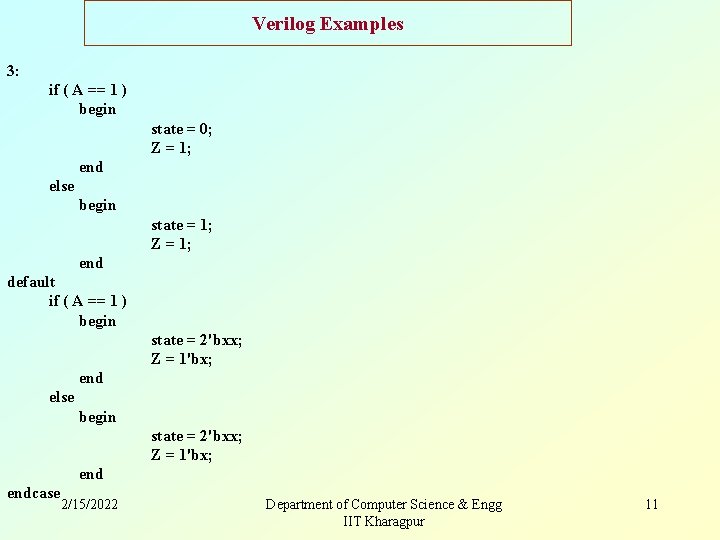

Verilog Examples // Implementation of state machine of the given figure, APPROACH: Behavioral module ph 193_fig 5_21( Z, state, A, clk, reset ); output Z; output [1: 0] state; reg [1: 0] currentstate, state; reg Z; input A, clk, reset; always @( posedge clk ) begin if ( reset == 1 ) //need to reset to start from a known state at some point currentstate = 0; case ( currentstate ) //step through all states per state table 0: if ( A == 1 ) begin state = 1; Z = 0; end else begin state = 0; Z = 1; end 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 9

Verilog Examples 1: if ( A == 1 ) begin state = 2; Z = 0; end else begin state = 3; Z = 0; end 2: if ( A == 1 ) begin state = 3; Z = 1; end else begin state = 0; Z = 1; end 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 10

Verilog Examples 3: if ( A == 1 ) begin state = 0; Z = 1; end else begin state = 1; Z = 1; end default if ( A == 1 ) begin state = 2'bxx; Z = 1'bx; end else begin state = 2'bxx; Z = 1'bx; endcase 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 11

Verilog Examples currentstate = state; endmodule //update state for next time pass module test; reg A, clk, reset; wire [1: 0] state; wire Z; pg 193_fig_5_21 pg 193_5_21_0 ( Z, state, A, clk, reset ); initial $monitor( "Time=%0 d, state=%0 b, A=%0 b, Z=%0 b, reset=%0 b", $time, state, A, Z, reset ); 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 12

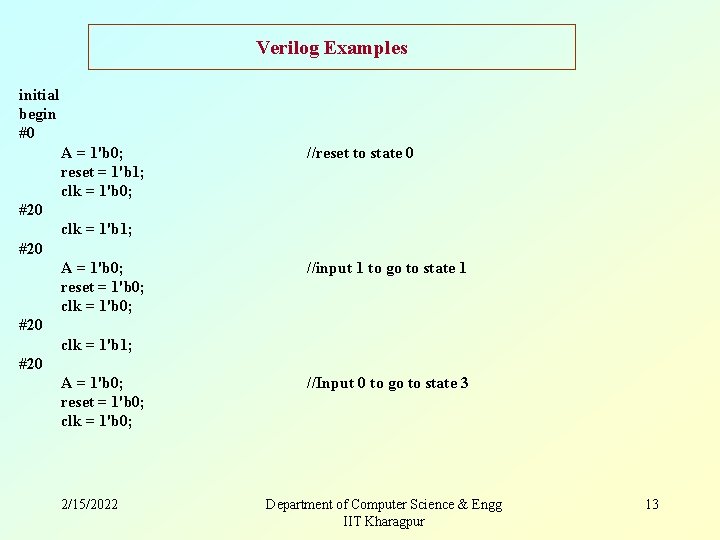

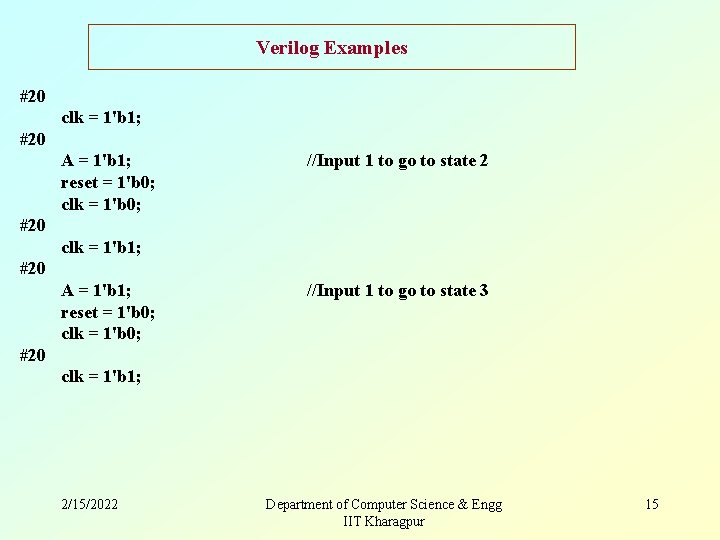

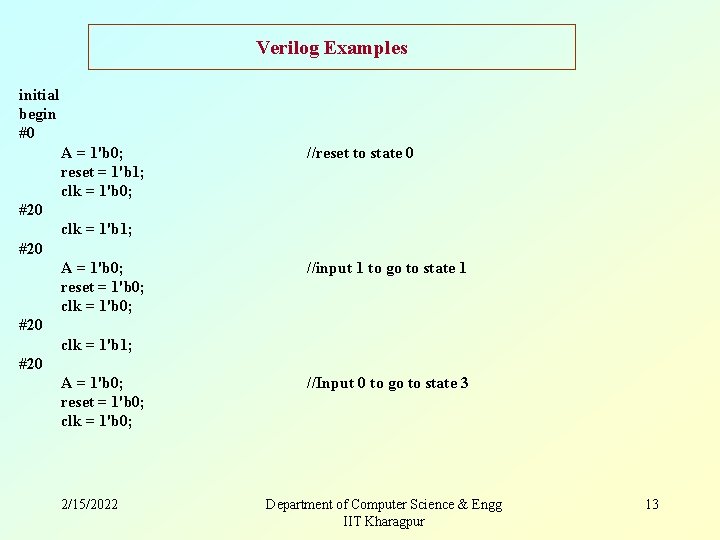

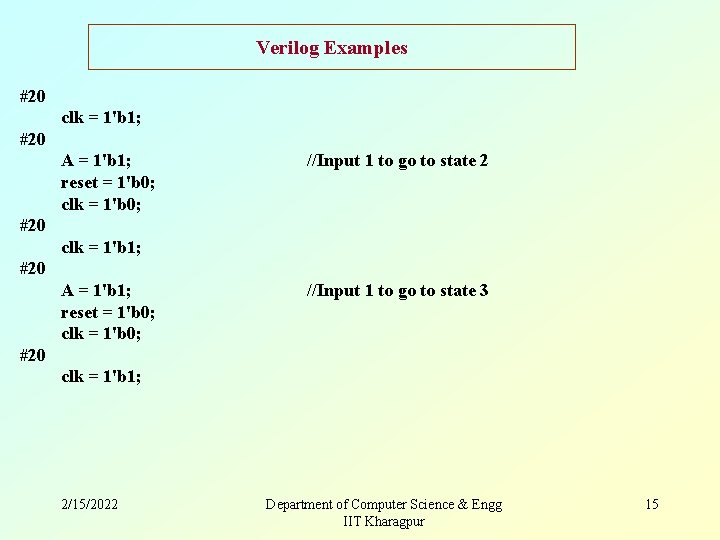

Verilog Examples initial begin #0 A = 1'b 0; reset = 1'b 1; clk = 1'b 0; //reset to state 0 #20 clk = 1'b 1; #20 A = 1'b 0; reset = 1'b 0; clk = 1'b 0; //input 1 to go to state 1 #20 clk = 1'b 1; #20 A = 1'b 0; reset = 1'b 0; clk = 1'b 0; 2/15/2022 //Input 0 to go to state 3 Department of Computer Science & Engg IIT Kharagpur 13

Verilog Examples #20 clk = 1'b 1; #20 A = 1'b 1; reset = 1'b 0; clk = 1'b 0; //Input 1 to go to state 0 #20 clk = 1'b 1; #20 A = 1'b 0; reset = 1'b 0; clk = 1'b 0; //Input 0 to stay at state 0 A = 1'b 0; reset = 1'b 0; clk = 1'b 0; //Input 1 to go to state 1 #20 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 14

Verilog Examples #20 clk = 1'b 1; #20 A = 1'b 1; reset = 1'b 0; clk = 1'b 0; //Input 1 to go to state 2 #20 clk = 1'b 1; #20 A = 1'b 1; reset = 1'b 0; clk = 1'b 0; //Input 1 to go to state 3 #20 clk = 1'b 1; 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 15

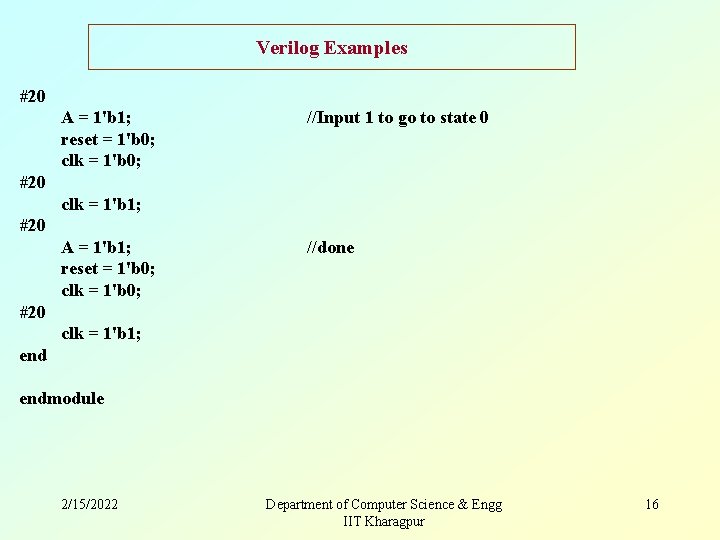

Verilog Examples #20 A = 1'b 1; reset = 1'b 0; clk = 1'b 0; //Input 1 to go to state 0 #20 clk = 1'b 1; #20 A = 1'b 1; reset = 1'b 0; clk = 1'b 0; //done #20 clk = 1'b 1; endmodule 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 16

![Verilog Examples Tabular Results GROUP CREATE state state1 state0 INPUTS A clk Verilog Examples Tabular Results GROUP CREATE state = state[1] state[0] ; INPUTS A clk](https://slidetodoc.com/presentation_image_h2/b7c85be6a7e095bb07dab0e9ef167026/image-17.jpg)

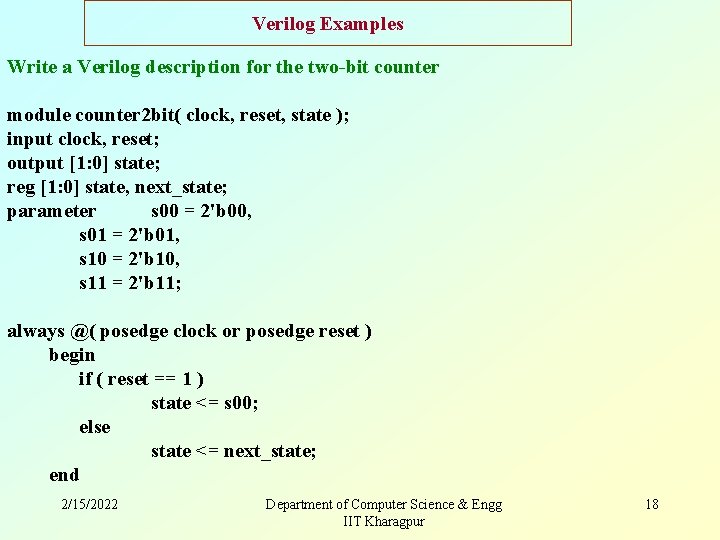

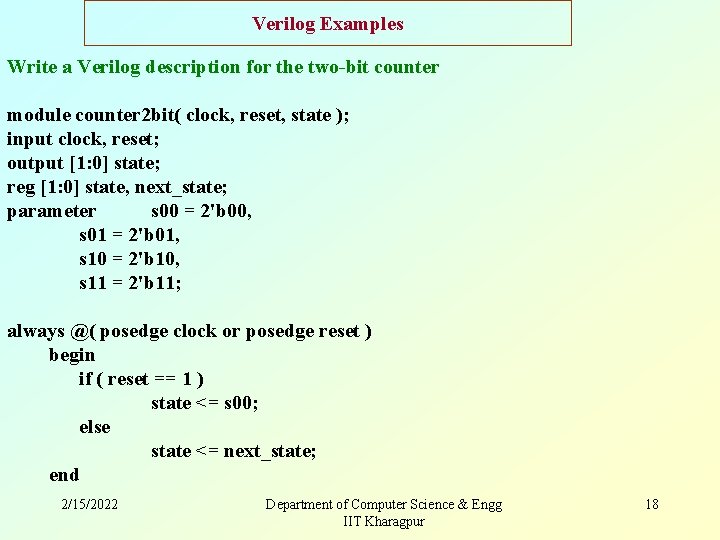

Verilog Examples Tabular Results GROUP CREATE state = state[1] state[0] ; INPUTS A clk reset; OUTPUTS state Z; UNIT ns; RADIX HEX; PATTERN 0. 0> 0 0 1 = 0 0 2. 5> 0 1 1 = 0 1 5. 0> 1 0 0 = 0 1 7. 5> 1 1 0 = 1 0 10. 0> 0 0 0 = 1 0 12. 5> 0 1 0 = 3 0 15. 0> 1 0 0 = 3 0 17. 5> 1 1 0 = 0 1 20. 0> 0 0 0 = 0 1 22. 5> 0 1 0 = 0 1 25. 0> 1 0 0 = 0 1 27. 5> 1 1 0 = 1 0 30. 0> 0 0 0 = 1 0 32. 5> 0 1 0 = 3 0 35. 0> 1 0 0 = 3 0 37. 5> 0 0 0 = 3 0 40. 0> 0 0 0 = X X 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 17

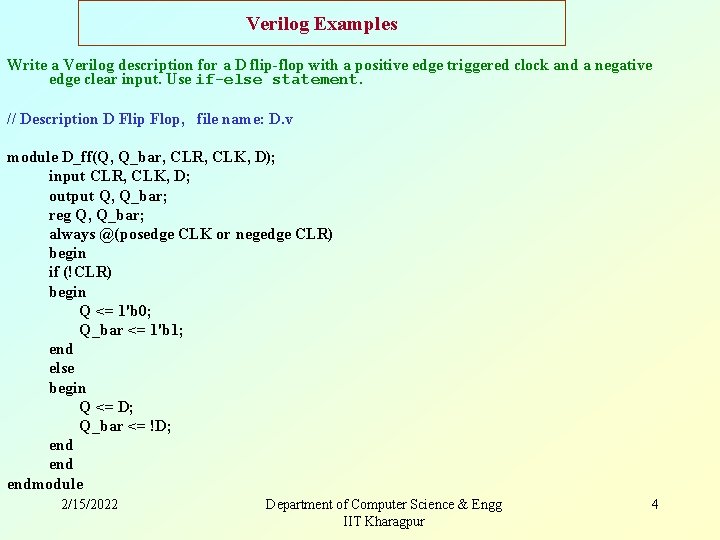

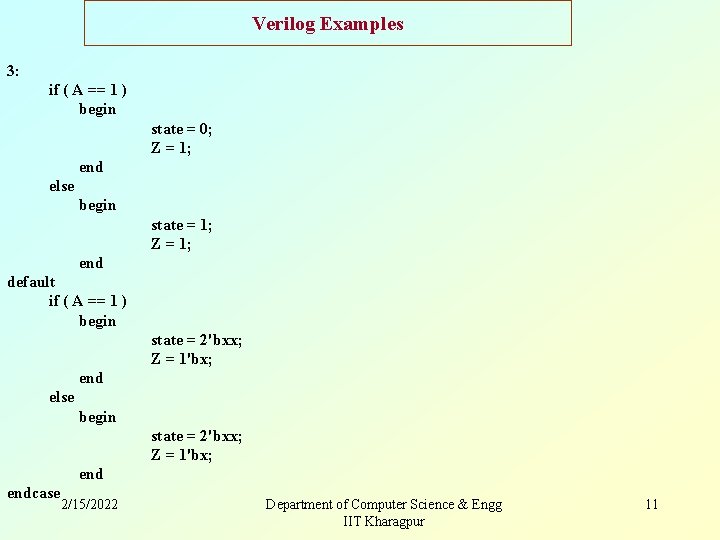

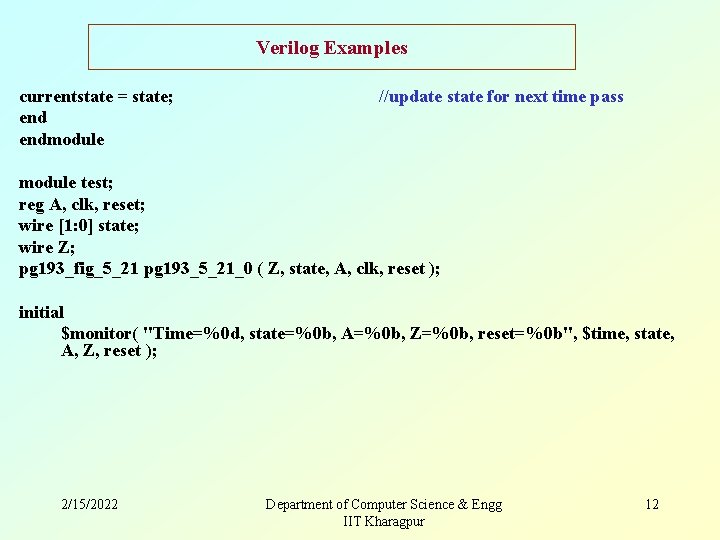

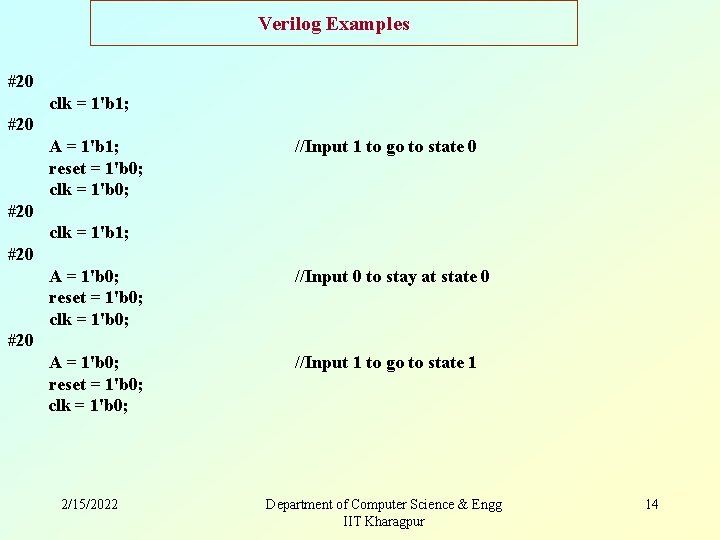

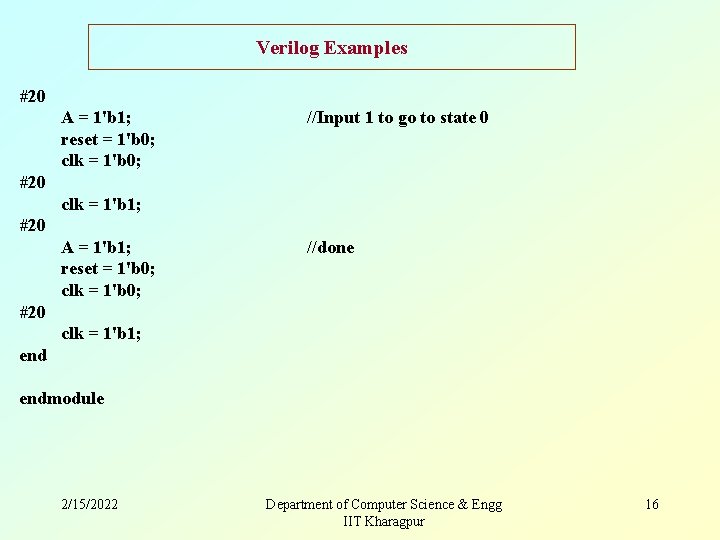

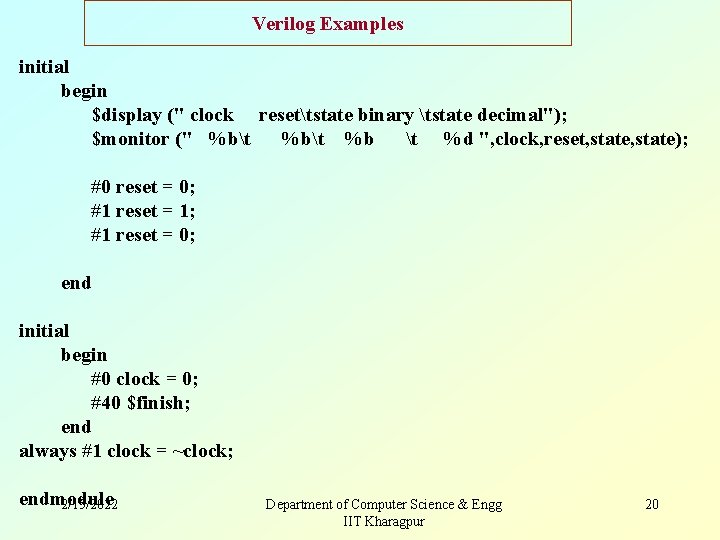

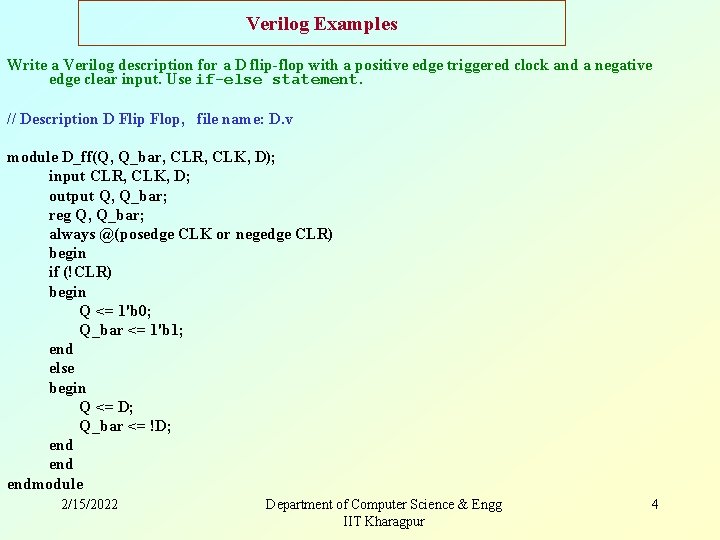

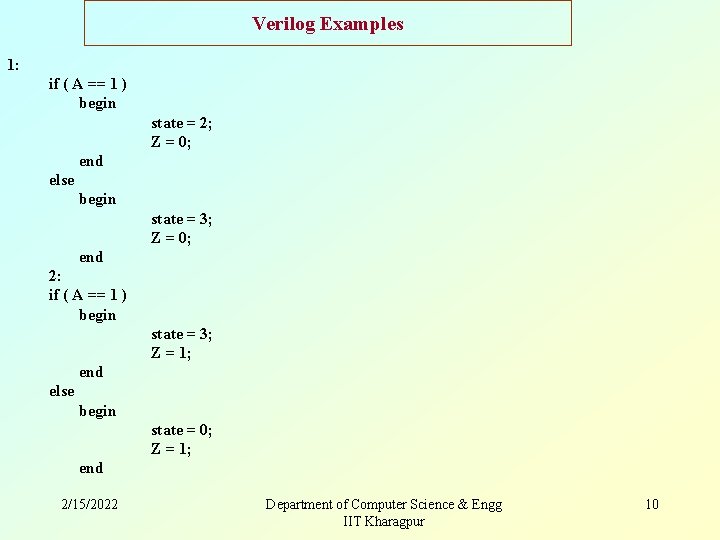

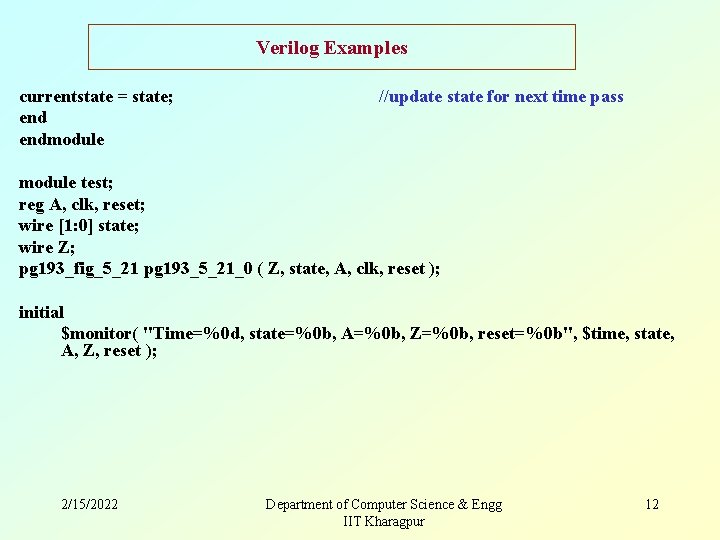

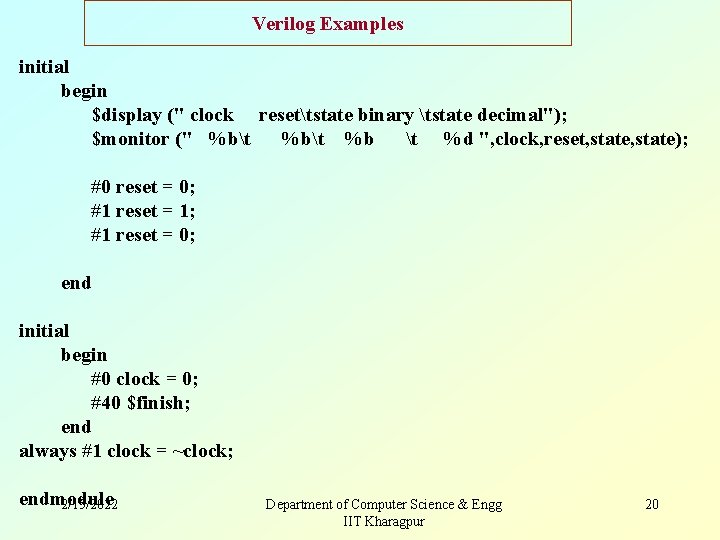

Verilog Examples Write a Verilog description for the two-bit counter module counter 2 bit( clock, reset, state ); input clock, reset; output [1: 0] state; reg [1: 0] state, next_state; parameter s 00 = 2'b 00, s 01 = 2'b 01, s 10 = 2'b 10, s 11 = 2'b 11; always @( posedge clock or posedge reset ) begin if ( reset == 1 ) state <= s 00; else state <= next_state; end 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 18

Verilog Examples always @( state ) begin case ( state ) s 00 : next_state <= s 01; s 01 : next_state <= s 10; s 10 : next_state <= s 11; s 11 : next_state <= s 00; endcase endmodule test; reg clock, reset; wire [1: 0] state; counter 2 bit c 2 bit( clock, reset, state ); 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 19

Verilog Examples initial begin $display (" clock resettstate binary tstate decimal"); $monitor (" %bt %b t %d ", clock, reset, state); #0 reset = 0; #1 reset = 1; #1 reset = 0; end initial begin #0 clock = 0; #40 $finish; end always #1 clock = ~clock; endmodule 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 20

![Verilog Examples Tabular Results GROUP CREATE state state1 state0 INPUTS clock reset Verilog Examples Tabular Results GROUP CREATE state = state[1] state[0] ; INPUTS clock reset;](https://slidetodoc.com/presentation_image_h2/b7c85be6a7e095bb07dab0e9ef167026/image-21.jpg)

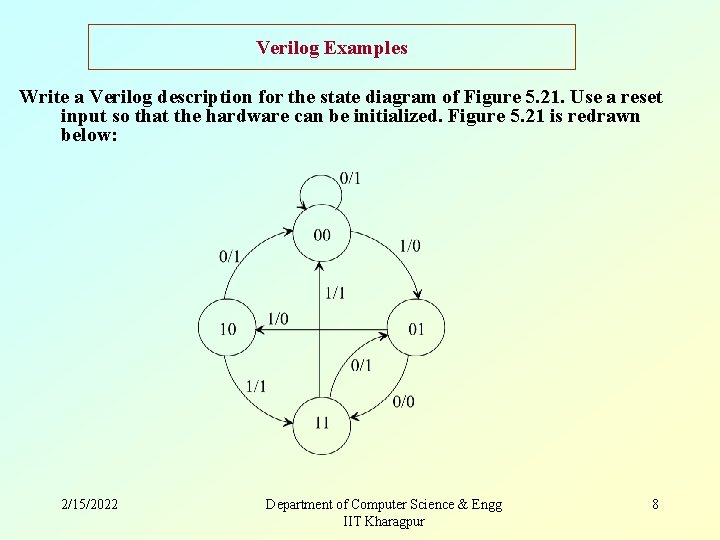

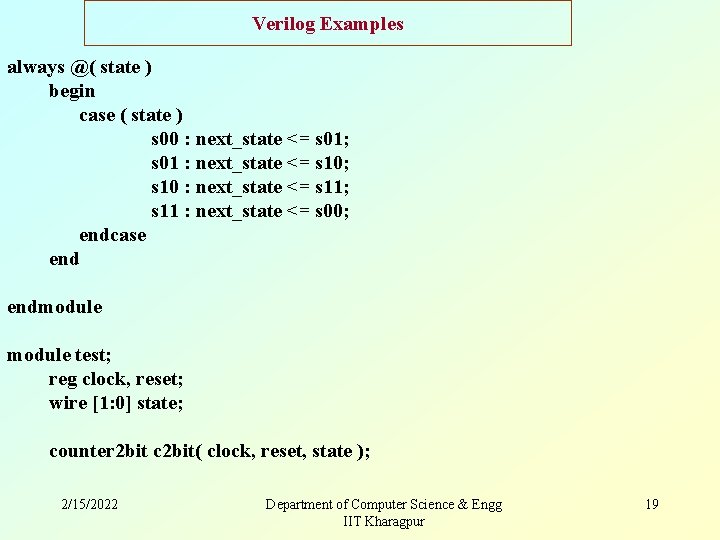

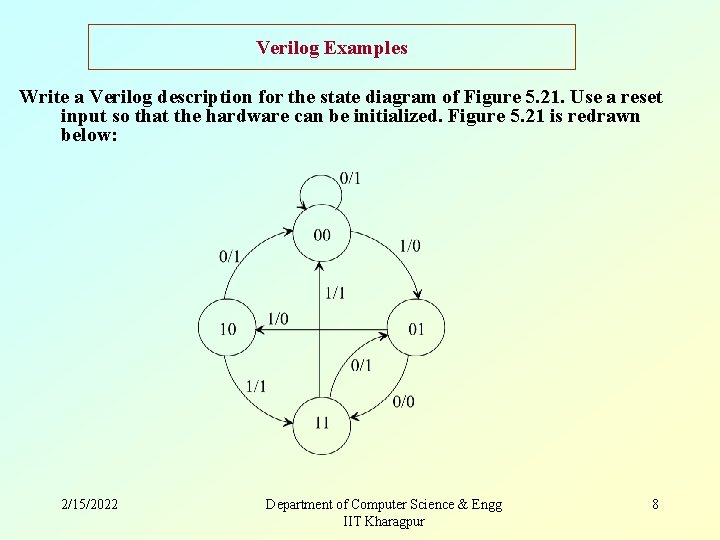

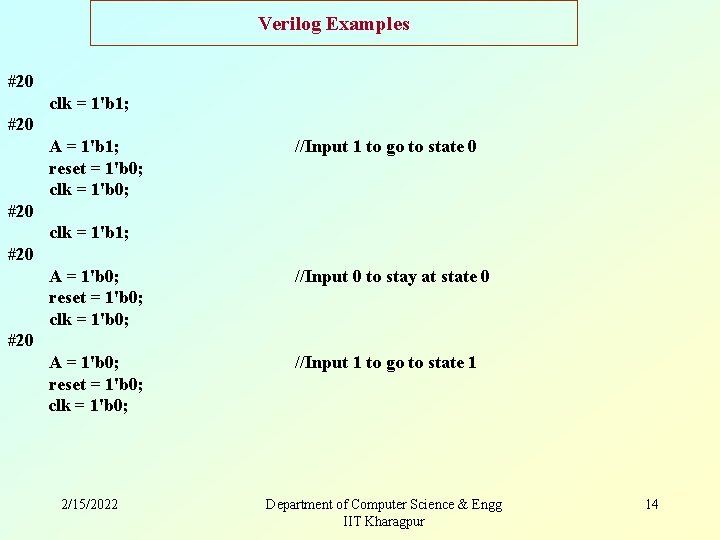

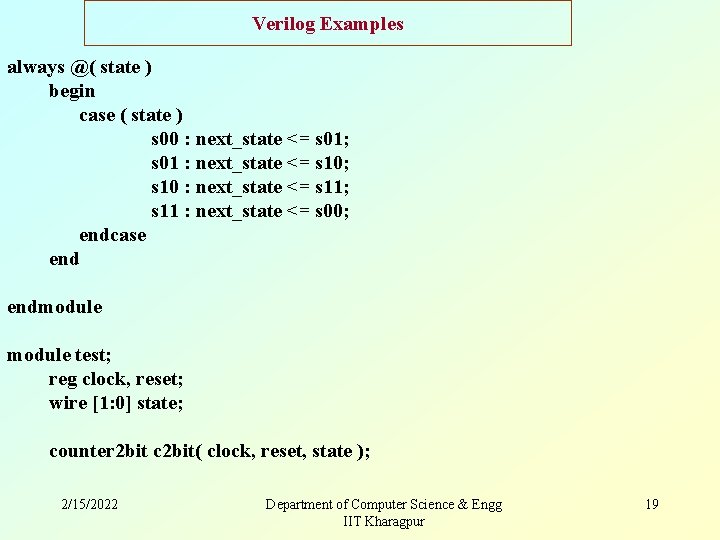

Verilog Examples Tabular Results GROUP CREATE state = state[1] state[0] ; INPUTS clock reset; OUTPUTS state; UNIT ns; RADIX HEX; PATTERN 0. 0> 0 0 = 0 5. 0> 0 0 = 0 7. 5> 1 0 = 1 12. 5> 1 0 = 2 15. 0> 0 0 = 2 20. 0> 0 0 = 3 22. 5> 1 0 = 0 27. 5> 1 0 = 1 30. 0> 0 0 = 1 35. 0> 0 0 = 2 37. 5> 1 0 = 3 42. 5> 1 0 = X 2/15/2022 2. 5> 1 1 = 0 10. 0> 0 0 = 1 17. 5> 1 0 = 3 25. 0> 0 0 = 0 32. 5> 1 0 = 2 40. 0> 0 0 = 3 Department of Computer Science & Engg IIT Kharagpur 21

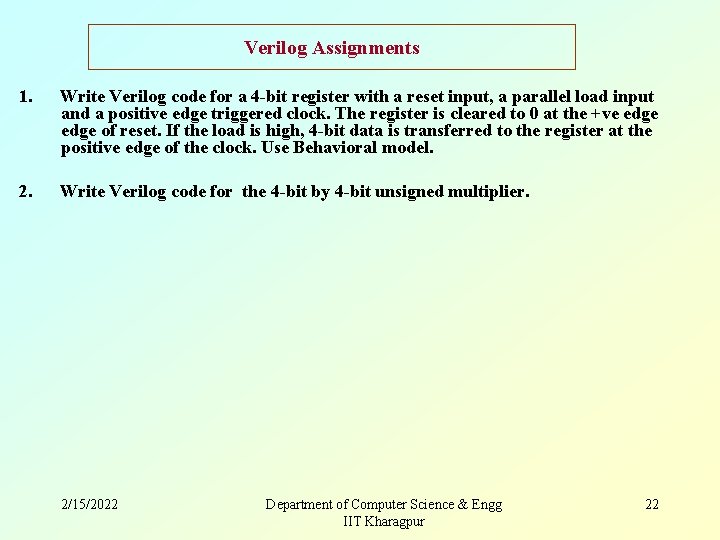

Verilog Assignments 1. Write Verilog code for a 4 -bit register with a reset input, a parallel load input and a positive edge triggered clock. The register is cleared to 0 at the +ve edge of reset. If the load is high, 4 -bit data is transferred to the register at the positive edge of the clock. Use Behavioral model. 2. Write Verilog code for the 4 -bit by 4 -bit unsigned multiplier. 2/15/2022 Department of Computer Science & Engg IIT Kharagpur 22