Verilog Static Loop Unrolling Support in Odin II

- Slides: 1

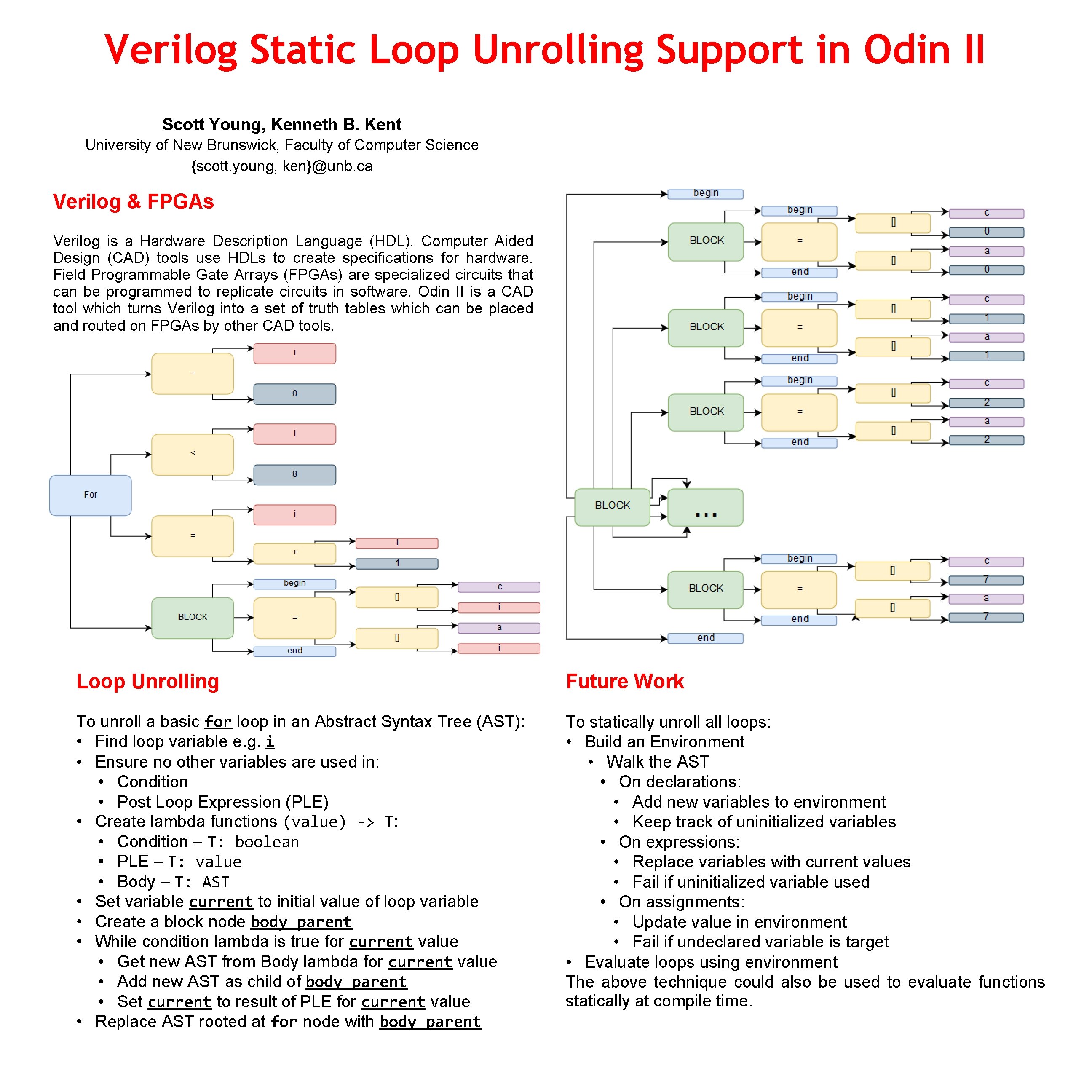

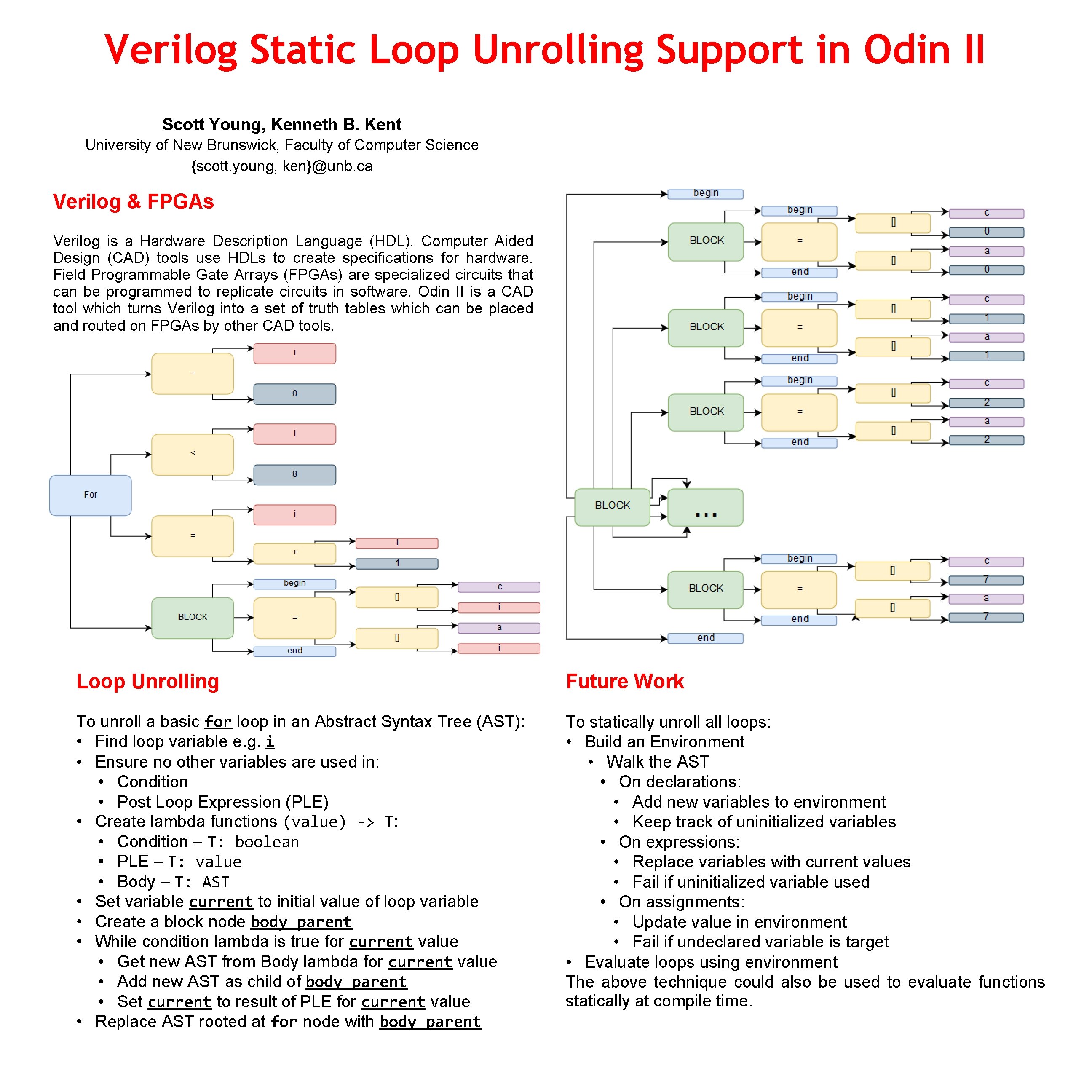

Verilog Static Loop Unrolling Support in Odin II Scott Young, Kenneth B. Kent University of New Brunswick, Faculty of Computer Science {scott. young, ken}@unb. ca Verilog & FPGAs Verilog is a Hardware Description Language (HDL). Computer Aided Design (CAD) tools use HDLs to create specifications for hardware. Field Programmable Gate Arrays (FPGAs) are specialized circuits that can be programmed to replicate circuits in software. Odin II is a CAD tool which turns Verilog into a set of truth tables which can be placed and routed on FPGAs by other CAD tools. Loop Unrolling Future Work To unroll a basic for loop in an Abstract Syntax Tree (AST): • Find loop variable e. g. i • Ensure no other variables are used in: • Condition • Post Loop Expression (PLE) • Create lambda functions (value) -> T: • Condition – T: boolean • PLE – T: value • Body – T: AST • Set variable current to initial value of loop variable • Create a block node body parent • While condition lambda is true for current value • Get new AST from Body lambda for current value • Add new AST as child of body parent • Set current to result of PLE for current value • Replace AST rooted at for node with body parent To statically unroll all loops: • Build an Environment • Walk the AST • On declarations: • Add new variables to environment • Keep track of uninitialized variables • On expressions: • Replace variables with current values • Fail if uninitialized variable used • On assignments: • Update value in environment • Fail if undeclared variable is target • Evaluate loops using environment The above technique could also be used to evaluate functions statically at compile time.