VERILOG Sntese de Lgica combinatria Funo lgica combinatria

VERILOG: Síntese de Lógica combinatória Função lógica combinatória pode ser representada como: logic_output(t) = f(logic_inputs(t)) Regras Evite modelamento dependente de tecnologia, ou seja, implemente a função, não o timing. Lógica combinatória não pode ter realimentação. Especifique a saída de uma função combinatória para todos os possíveis combinações de entrada. Lógica que não é combinatória será sintetizado como sequencial.

Estilos para Lógica Combinatória Sintetizável Os seguintes estilos são possíveis: Netlist de instâncias de portas e de primitivas Verilog (completamente estrutural). UDP (User Defined Primitive) combinatória (somente algumas ferramentas) Funções Atribuições permanentes Instruções comportamentais Tasks sem controle de atraso ou de eventos Interconexões dos elementos acima

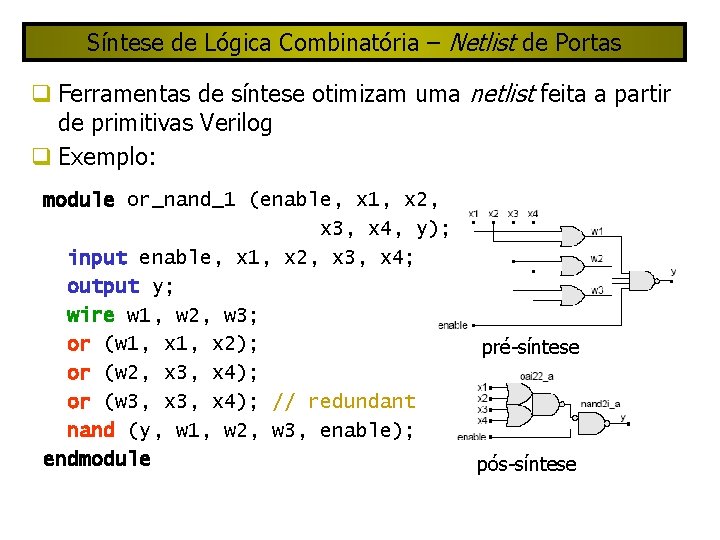

Síntese de Lógica Combinatória – Netlist de Portas Ferramentas de síntese otimizam uma netlist feita a partir de primitivas Verilog Exemplo: module or_nand_1 (enable, x 1, x 2, x 3, x 4, y); input enable, x 1, x 2, x 3, x 4; output y; wire w 1, w 2, w 3; or (w 1, x 2); or (w 2, x 3, x 4); or (w 3, x 4); // redundant nand (y, w 1, w 2, w 3, enable); endmodule pré-síntese pós-síntese

Síntese de Lógica combinatória – Netlist de Portas (cont. ) Passos gerais da síntese: 1) Portas lógicas são traduzidas em equações booleanas. 2) As equações booleanas são otimizadas. 3) Equações booleanas são mapeadas para células de biblioteca. Funções complexas que são modeladas portas primitivas não podem ser mapeadas para células de biblioteca mais complexas (p. ex. somador, multiplicador). Diretivas de síntese permitam a preservação da estrutura caso células equivalentes existem na biblioteca.

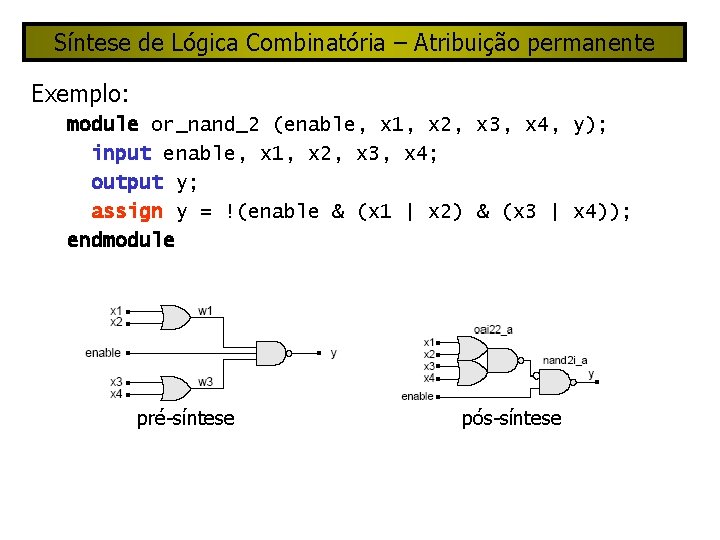

Síntese de Lógica Combinatória – Atribuição permanente Exemplo: module or_nand_2 (enable, x 1, x 2, x 3, x 4, y); input enable, x 1, x 2, x 3, x 4; output y; assign y = !(enable & (x 1 | x 2) & (x 3 | x 4)); endmodule pré-síntese pós-síntese

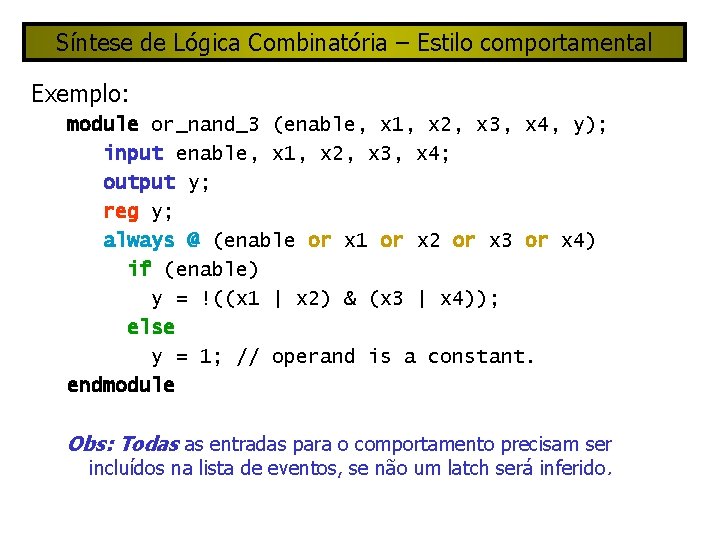

Síntese de Lógica Combinatória – Estilo comportamental Exemplo: module or_nand_3 (enable, x 1, x 2, x 3, x 4, y); input enable, x 1, x 2, x 3, x 4; output y; reg y; always @ (enable or x 1 or x 2 or x 3 or x 4) if (enable) y = !((x 1 | x 2) & (x 3 | x 4)); else y = 1; // operand is a constant. endmodule Obs: Todas as entradas para o comportamento precisam ser incluídos na lista de eventos, se não um latch será inferido.

Síntese de Lógica Combinatória – Funções Exemplo: module or_nand_4 (enable, x 1, x 2, x 3, x 4, y); input enable, x 1, x 2, x 3, x 4; output y; assign y = or_nand(enable, x 1, x 2, x 3, x 4); function or_nand; input enable, x 1, x 2, x 3, x 4; begin or_nand = ~(enable & (x 1 | x 2) & (x 3 | x 4)); endfunction endmodule

Síntese de Lógica Combinatória – Tarefas Example: module or_nand_5 (enable, x 1, x 2, x 3, x 4, y); input enable, x 1, x 2, x 3, x 4; output y; reg y; always @ (enable or x 1 or x 2 or x 3 or x 4) or_nand (enable, x 1, x 2, x 3 c, x 4); task or_nand; input enable, x 1, x 2, x 3, x 4; output y; begin y = !(enable & (x 1 | x 2) & (x 3 | x 4)); endtask endmodule

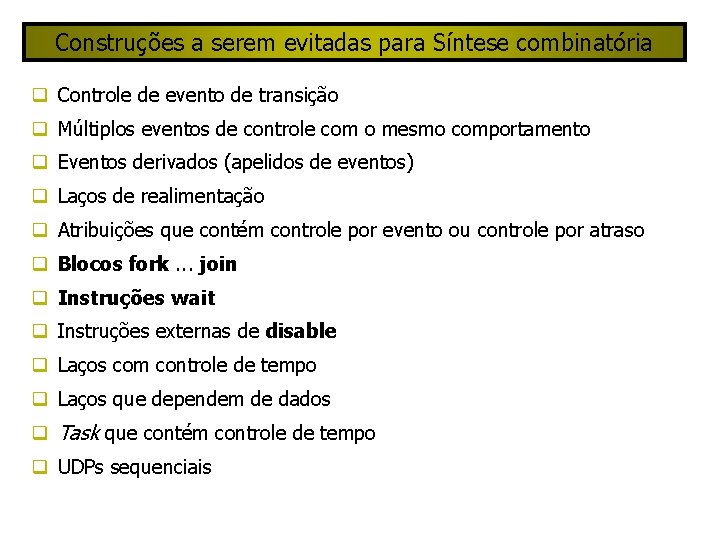

Construções a serem evitadas para Síntese combinatória Controle de evento de transição Múltiplos eventos de controle com o mesmo comportamento Eventos derivados (apelidos de eventos) Laços de realimentação Atribuições que contém controle por evento ou controle por atraso Blocos fork. . . join Instruções wait Instruções externas de disable Laços com controle de tempo Laços que dependem de dados Task que contém controle de tempo UDPs sequenciais

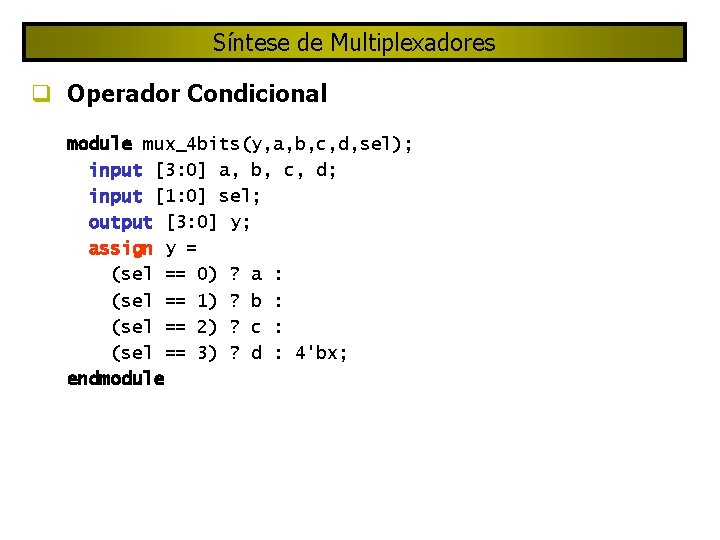

Síntese de Multiplexadores Operador Condicional module mux_4 bits(y, a, b, c, d, sel); input [3: 0] a, b, c, d; input [1: 0] sel; output [3: 0] y; assign y = (sel == 0) ? a : (sel == 1) ? b : (sel == 2) ? c : (sel == 3) ? d : 4'bx; endmodule

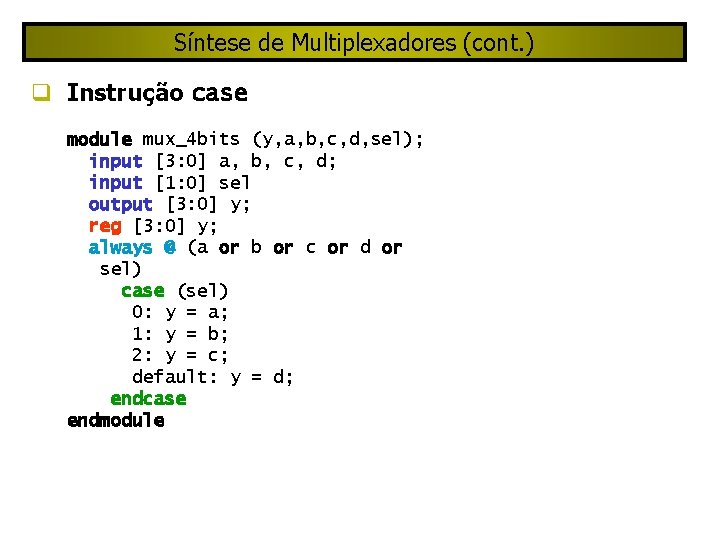

Síntese de Multiplexadores (cont. ) Instrução case module mux_4 bits (y, a, b, c, d, sel); input [3: 0] a, b, c, d; input [1: 0] sel output [3: 0] y; reg [3: 0] y; always @ (a or b or c or d or sel) case (sel) 0: y = a; 1: y = b; 2: y = c; default: y = d; endcase endmodule

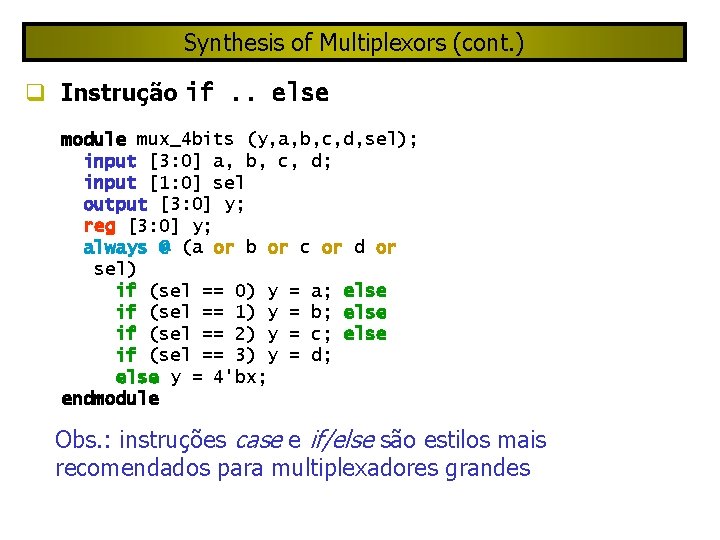

Synthesis of Multiplexors (cont. ) Instrução if. . else module mux_4 bits (y, a, b, c, d, sel); input [3: 0] a, b, c, d; input [1: 0] sel output [3: 0] y; reg [3: 0] y; always @ (a or b or c or d or sel) if (sel == 0) y = a; else if (sel == 1) y = b; else if (sel == 2) y = c; else if (sel == 3) y = d; else y = 4'bx; endmodule Obs. : instruções case e if/else são estilos mais recomendados para multiplexadores grandes

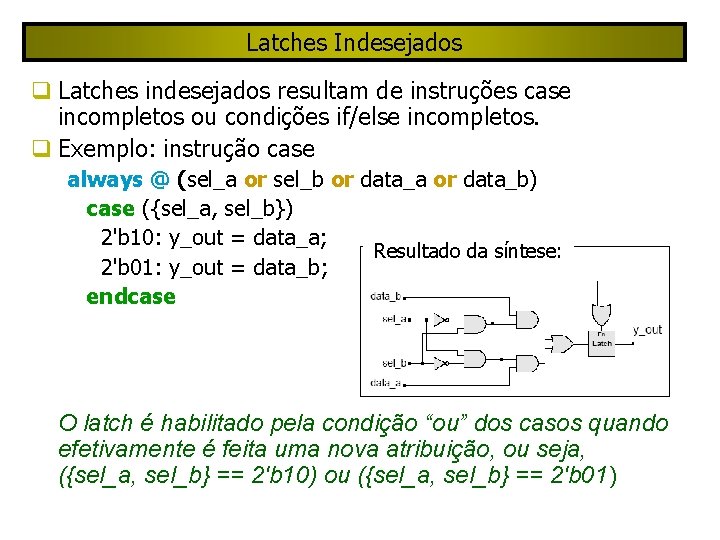

Latches Indesejados Latches indesejados resultam de instruções case incompletos ou condições if/else incompletos. Exemplo: instrução case always @ (sel_a or sel_b or data_a or data_b) case ({sel_a, sel_b}) 2'b 10: y_out = data_a; Resultado da síntese: 2'b 01: y_out = data_b; endcase O latch é habilitado pela condição “ou” dos casos quando efetivamente é feita uma nova atribuição, ou seja, ({sel_a, sel_b} == 2'b 10) ou ({sel_a, sel_b} == 2'b 01)

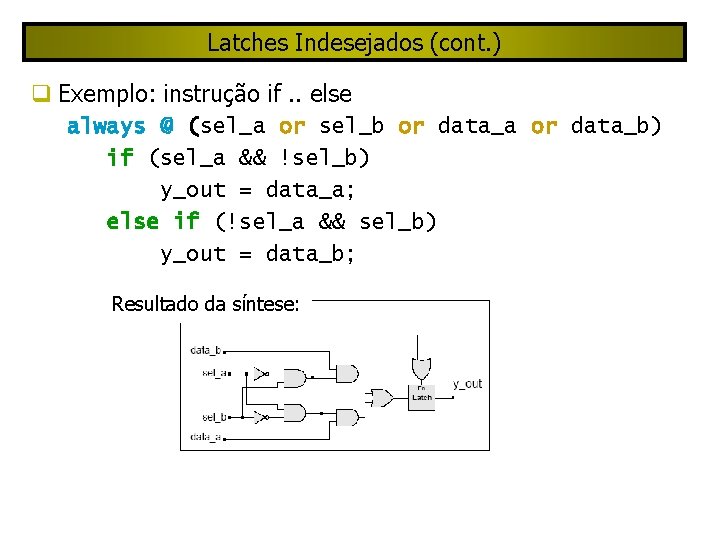

Latches Indesejados (cont. ) Exemplo: instrução if. . else always @ (sel_a or sel_b or data_a or data_b) if (sel_a && !sel_b) y_out = data_a; else if (!sel_a && sel_b) y_out = data_b; Resultado da síntese:

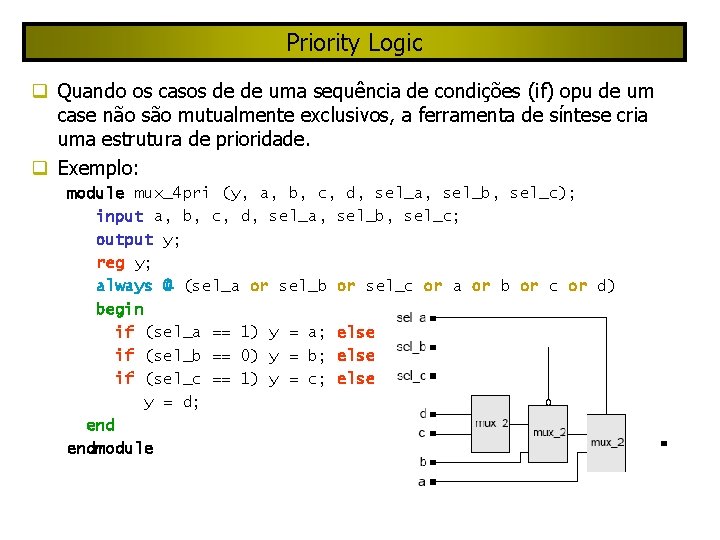

Priority Logic Quando os casos de de uma sequência de condições (if) opu de um case não são mutualmente exclusivos, a ferramenta de síntese cria uma estrutura de prioridade. Exemplo: module mux_4 pri (y, a, b, c, d, sel_a, sel_b, sel_c); input a, b, c, d, sel_a, sel_b, sel_c; output y; reg y; always @ (sel_a or sel_b or sel_c or a or b or c or d) begin if (sel_a == 1) y = a; else if (sel_b == 0) y = b; else if (sel_c == 1) y = c; else y = d; endmodule

VERILOG: Síntese – Lógica Sequencial Regra Geral: Uma variável será sintetizada como flip-flop se o seu valor á atribuída só no momento da transição de um sinal. Exemplo: module D_reg 4 a (Data_in, clock, reset, Data_out); input [3: 0] Data_in; input clock, reset; output [3: 0] Data_out; reg [3: 0] Data_out; always @ (posedge reset or posedge clock) if (reset == 1'b 1) Data_out <= 4'b 0; else Data_out <= Data_in; endmodule

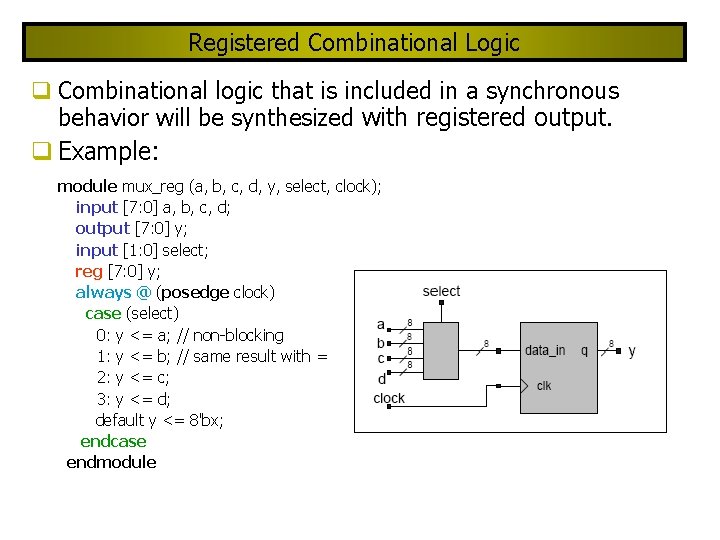

Registered Combinational Logic Combinational logic that is included in a synchronous behavior will be synthesized with registered output. Example: module mux_reg (a, b, c, d, y, select, clock); input [7: 0] a, b, c, d; output [7: 0] y; input [1: 0] select; reg [7: 0] y; always @ (posedge clock) case (select) 0: y <= a; // non-blocking 1: y <= b; // same result with = 2: y <= c; 3: y <= d; default y <= 8'bx; endcase endmodule

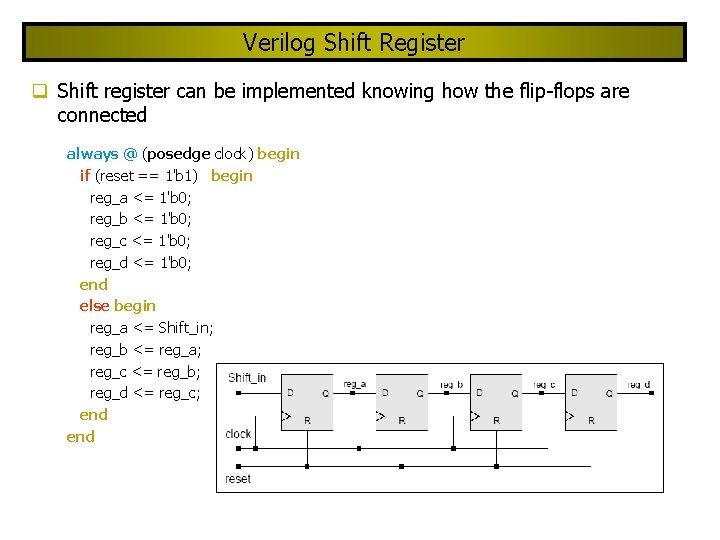

Verilog Shift Register Shift register can be implemented knowing how the flip-flops are connected always @ (posedge clock) begin if (reset == 1'b 1) begin reg_a <= 1'b 0; reg_b <= 1'b 0; reg_c <= 1'b 0; reg_d <= 1'b 0; end else begin reg_a <= Shift_in; reg_b <= reg_a; reg_c <= reg_b; reg_d <= reg_c; end

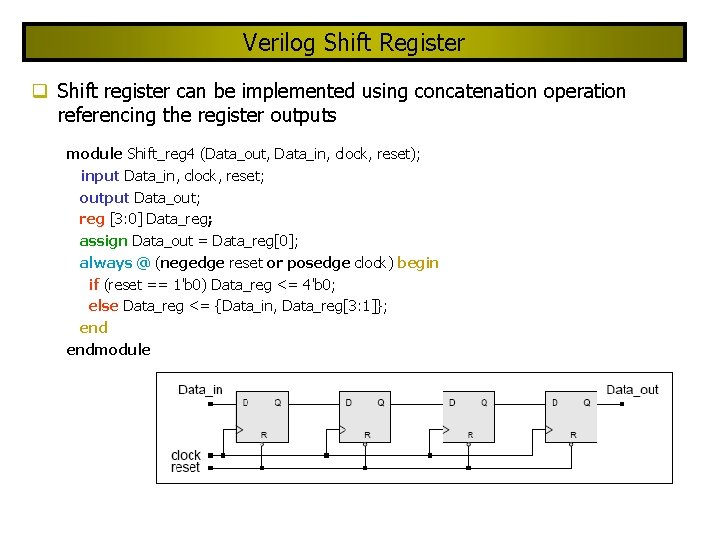

Verilog Shift Register Shift register can be implemented using concatenation operation referencing the register outputs module Shift_reg 4 (Data_out, Data_in, clock, reset); input Data_in, clock, reset; output Data_out; reg [3: 0] Data_reg; assign Data_out = Data_reg[0]; always @ (negedge reset or posedge clock) begin if (reset == 1'b 0) Data_reg <= 4'b 0; else Data_reg <= {Data_in, Data_reg[3: 1]}; endmodule

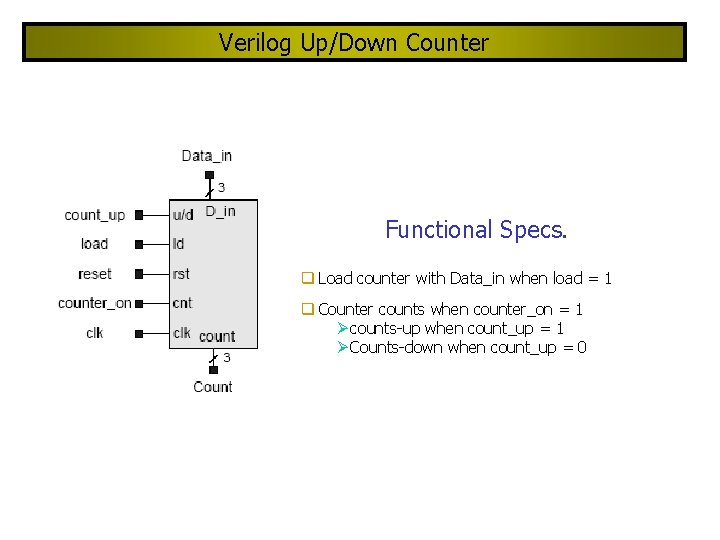

Verilog Up/Down Counter Functional Specs. Load counter with Data_in when load = 1 Counter counts when counter_on = 1 counts-up when count_up = 1 Counts-down when count_up = 0

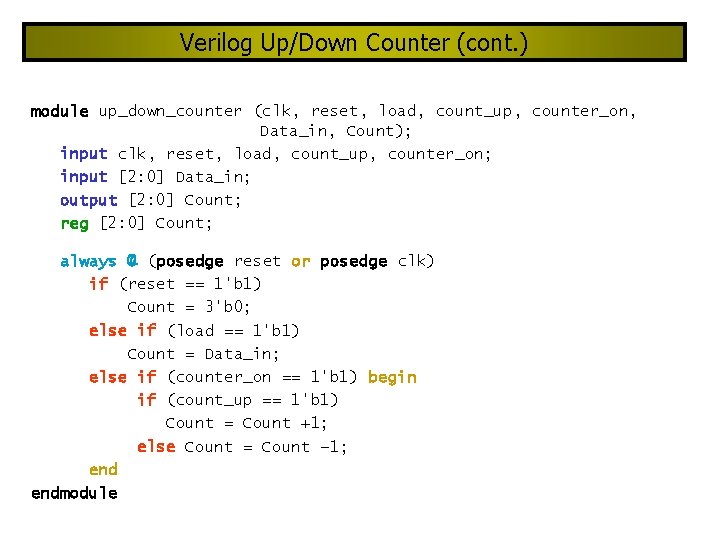

Verilog Up/Down Counter (cont. ) module up_down_counter (clk, reset, load, count_up, counter_on, Data_in, Count); input clk, reset, load, count_up, counter_on; input [2: 0] Data_in; output [2: 0] Count; reg [2: 0] Count; always @ (posedge reset or posedge clk) if (reset == 1'b 1) Count = 3'b 0; else if (load == 1'b 1) Count = Data_in; else if (counter_on == 1'b 1) begin if (count_up == 1'b 1) Count = Count +1; else Count = Count – 1; endmodule

- Slides: 21