Verilog Simulation Tools Verification YiMin Chih Outline One

![Expect(Slave) for i in range(golden_len): test. Expect((golden[i]. reshape(1, 1, 1) Check data every time Expect(Slave) for i in range(golden_len): test. Expect((golden[i]. reshape(1, 1, 1) Check data every time](https://slidetodoc.com/presentation_image_h2/824da20f6bfa9d32e1ed638b32b1ad21/image-17.jpg)

![Constant value (x, ) = Create. Buses([((“dut”, “x”), ), ]) x. values[0][0] = x_data Constant value (x, ) = Create. Buses([((“dut”, “x”), ), ]) x. values[0][0] = x_data](https://slidetodoc.com/presentation_image_h2/824da20f6bfa9d32e1ed638b32b1ad21/image-18.jpg)

- Slides: 21

Verilog Simulation Tools &Verification 池翊忞(Yi-Min Chih)

Outline � One wire/ Two wire � Verilog Procedural Interface/ nicotb 2

One wire/ Two wire 3

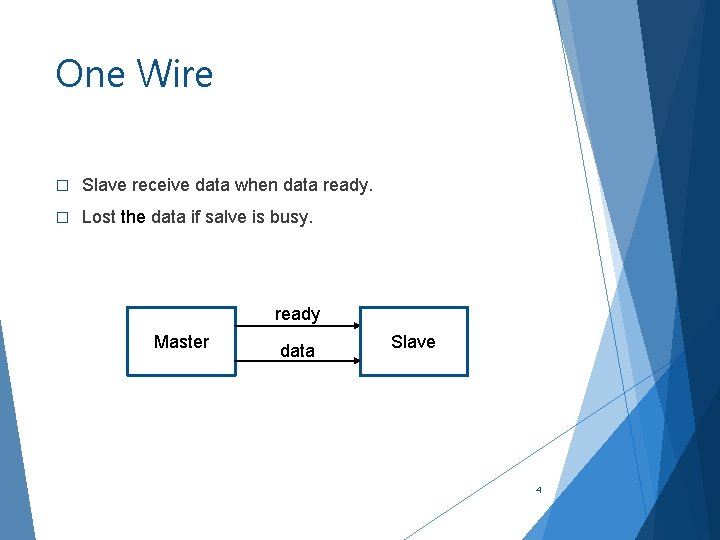

One Wire � Slave receive data when data ready. � Lost the data if salve is busy. ready Master data Slave 4

Two Wire � Master will hold the data when slave is not ack. Master ready ack data Slave 5

Nicotb 6

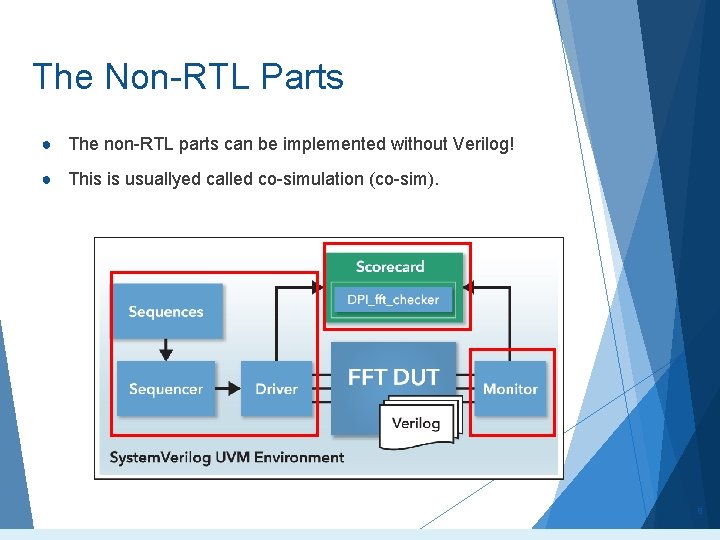

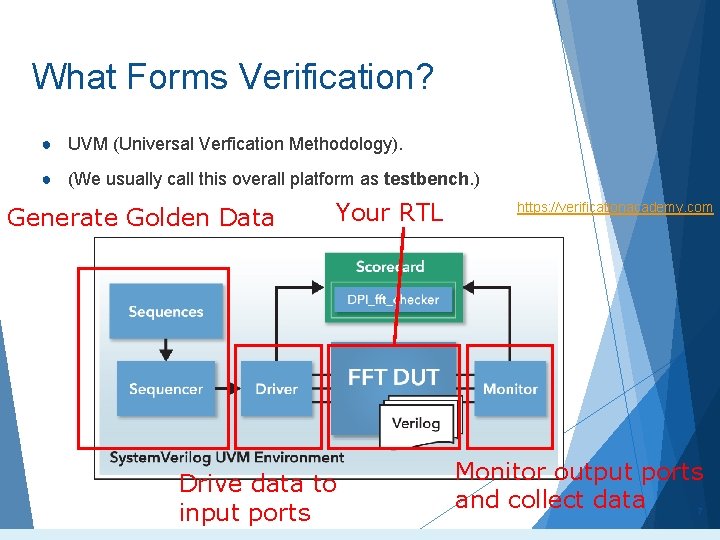

What Forms Verification? ● UVM (Universal Verfication Methodology). ● (We usually call this overall platform as testbench. ) Generate Golden Data Your RTL Drive data to input ports https: //verificationacademy. com Monitor output ports and collect data 7

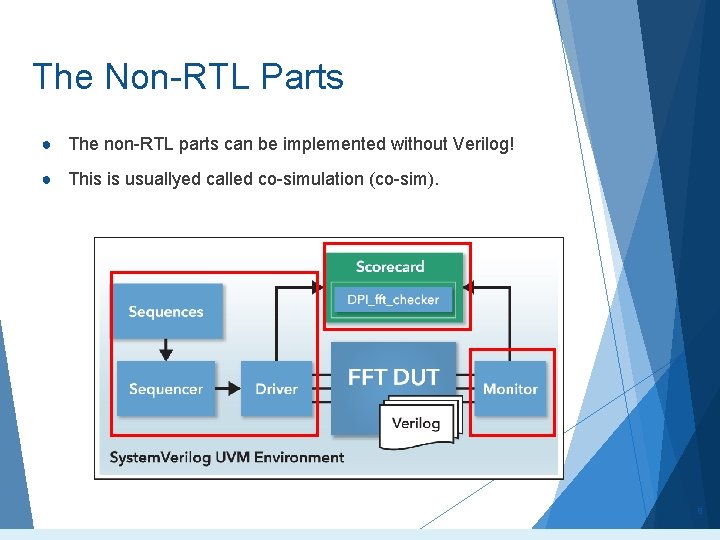

The Non-RTL Parts ● The non-RTL parts can be implemented without Verilog! ● This is usuallyed called co-simulation (co-sim). 8

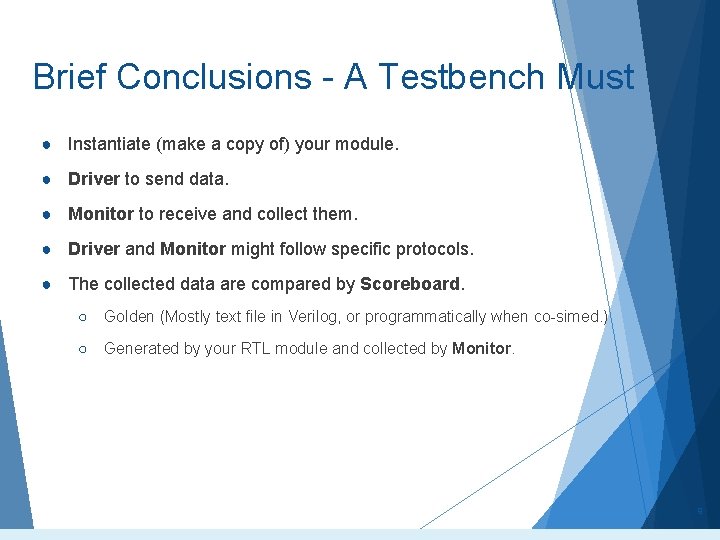

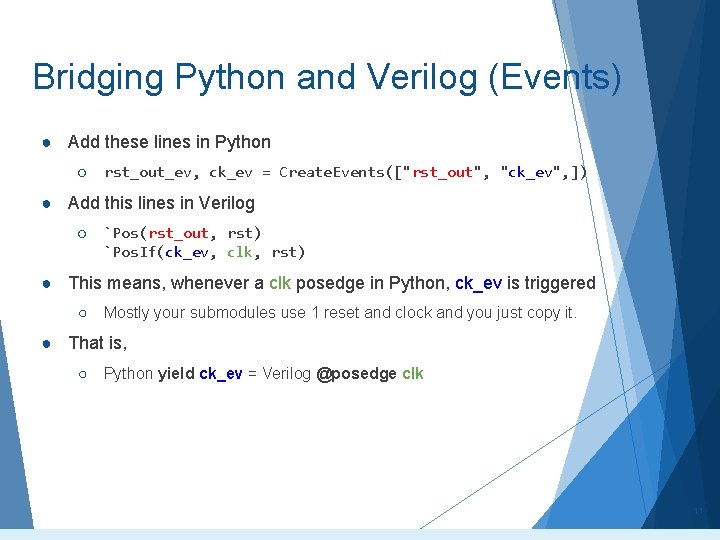

Brief Conclusions - A Testbench Must ● Instantiate (make a copy of) your module. ● Driver to send data. ● Monitor to receive and collect them. ● Driver and Monitor might follow specific protocols. ● The collected data are compared by Scoreboard. ○ Golden (Mostly text file in Verilog, or programmatically when co-simed. ) ○ Generated by your RTL module and collected by Monitor. 9

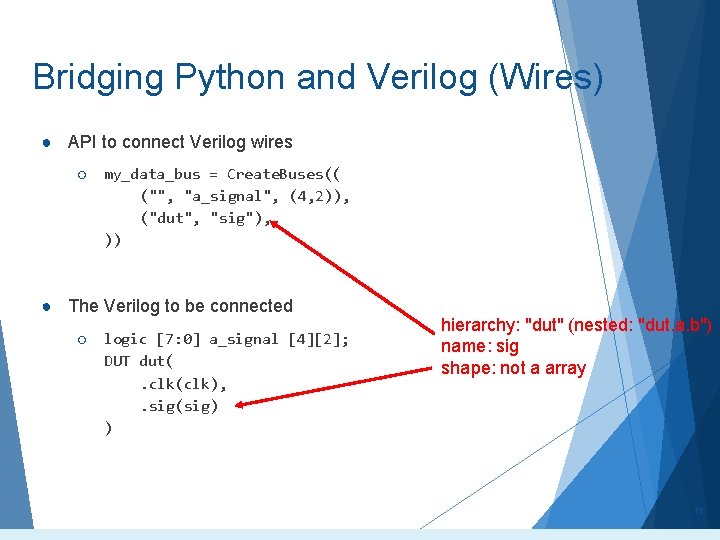

No Need for Verify RTL with Verilog ● Verilog provide external C accesses through VPI. ○ https: //en. wikipedia. org/wiki/Verilog_Procedural_Interface ● Based on C, people develops Java, Python. . . versions. ● AFAIK, there are quite a lot Python based frameworks. ○ myhdl: https: //github. com/myhdl ○ cocotb: https: //github. com/potentialventures/cocotb ○ nicotb: https: //github. com/johnlin/nicotb We focus on this today. 10

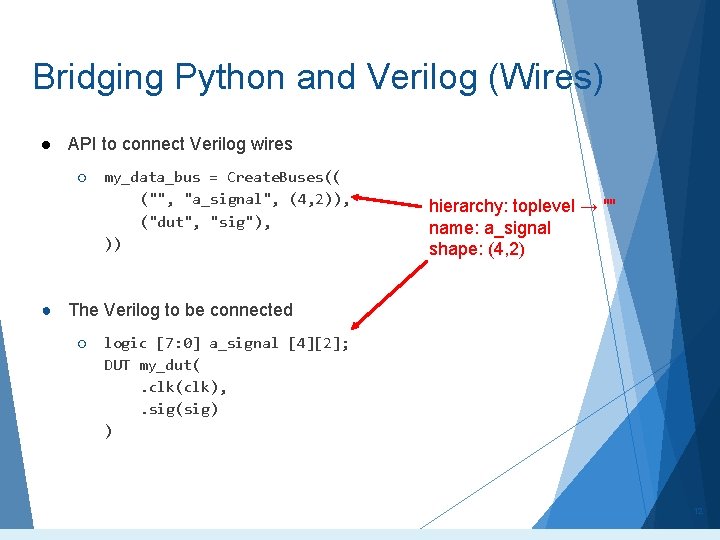

Bridging Python and Verilog (Events) ● Add these lines in Python ○ rst_out_ev, ck_ev = Create. Events(["rst_out", "ck_ev", ]) ● Add this lines in Verilog ○ `Pos(rst_out, rst) `Pos. If(ck_ev, clk, rst) ● This means, whenever a clk posedge in Python, ck_ev is triggered ○ Mostly your submodules use 1 reset and clock and you just copy it. ● That is, ○ Python yield ck_ev = Verilog @posedge clk 11

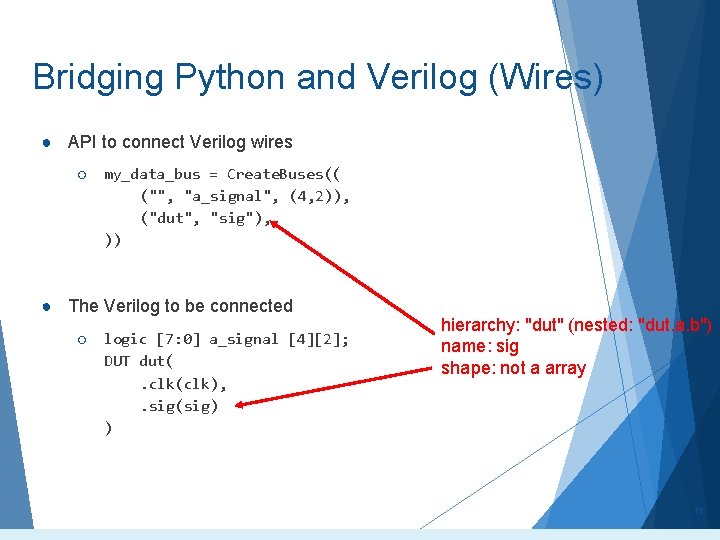

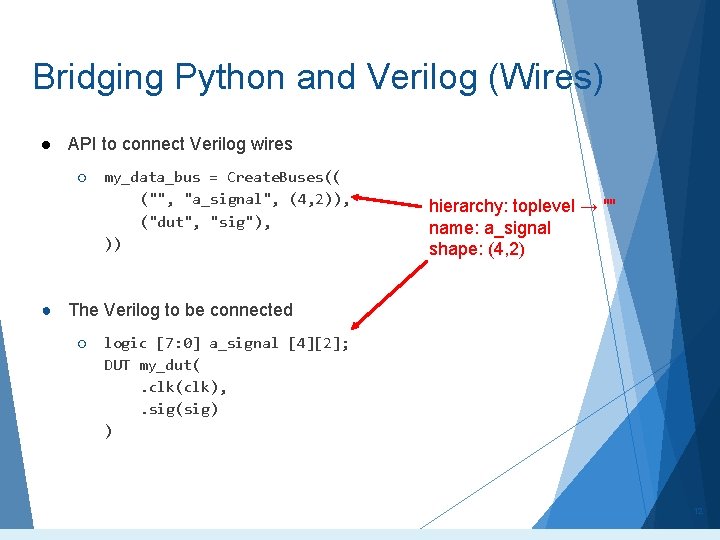

Bridging Python and Verilog (Wires) ● API to connect Verilog wires ○ my_data_bus = Create. Buses(( ("", "a_signal", (4, 2)), ("dut", "sig"), )) hierarchy: toplevel → "" name: a_signal shape: (4, 2) ● The Verilog to be connected ○ logic [7: 0] a_signal [4][2]; DUT my_dut(. clk(clk), . sig(sig) ) 12

Bridging Python and Verilog (Wires) ● API to connect Verilog wires ○ my_data_bus = Create. Buses(( ("", "a_signal", (4, 2)), ("dut", "sig"), )) ● The Verilog to be connected ○ logic [7: 0] a_signal [4][2]; DUT dut(. clk(clk), . sig(sig) ) hierarchy: "dut" (nested: "dut. a. b") name: sig shape: not a array 13

Convert Bus into Protocol(Master) ● First, you need to create the buses ○ (irdy, iack, iint) = Create. Buses([ (("dut", "irdy"), ), (("dut", "iack"), ), (("dut", "iint "), ), ]) ● Then, construct the classes in Python master = Two. Wire. Master(irdy, iack, iint, ck_ev, A=1, B=5) master_data = master. values 14

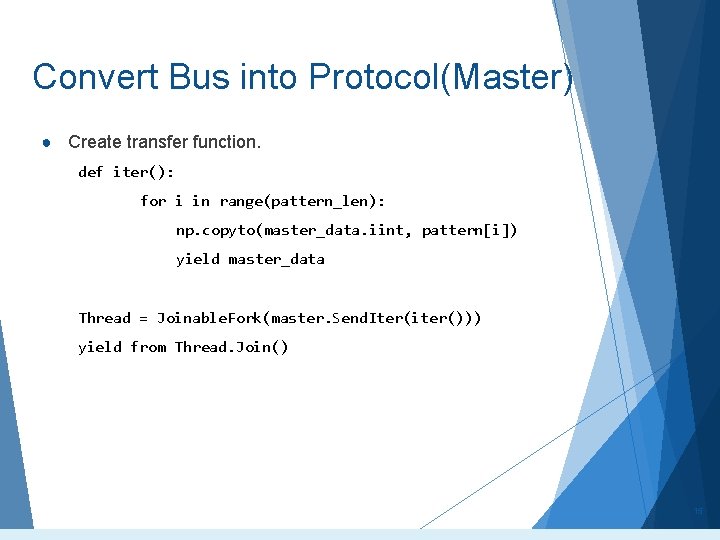

Convert Bus into Protocol(Master) ● Create transfer function. def iter(): for i in range(pattern_len): np. copyto(master_data. iint, pattern[i]) yield master_data Thread = Joinable. Fork(master. Send. Iter(iter())) yield from Thread. Join() 15

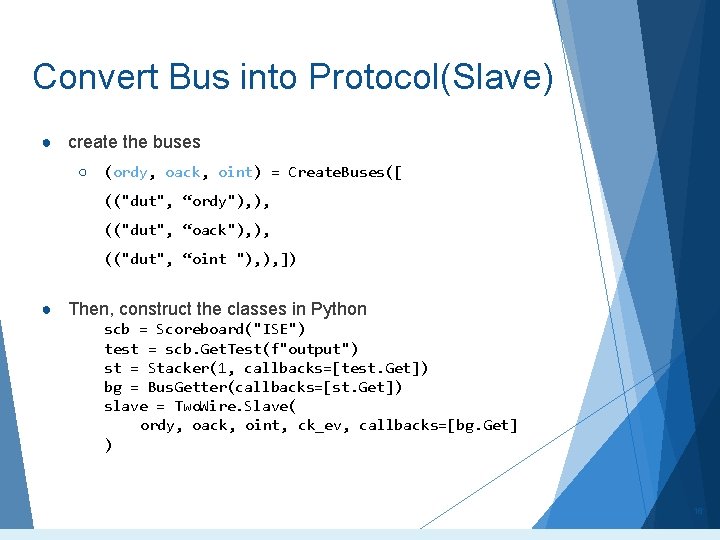

Convert Bus into Protocol(Slave) ● create the buses ○ (ordy, oack, oint) = Create. Buses([ (("dut", “ordy"), ), (("dut", “oack"), ), (("dut", “oint "), ), ]) ● Then, construct the classes in Python scb = Scoreboard("ISE") test = scb. Get. Test(f"output") st = Stacker(1, callbacks=[test. Get]) bg = Bus. Getter(callbacks=[st. Get]) slave = Two. Wire. Slave( ordy, oack, oint, ck_ev, callbacks=[bg. Get] ) 16

![ExpectSlave for i in rangegoldenlen test Expectgoldeni reshape1 1 1 Check data every time Expect(Slave) for i in range(golden_len): test. Expect((golden[i]. reshape(1, 1, 1) Check data every time](https://slidetodoc.com/presentation_image_h2/824da20f6bfa9d32e1ed638b32b1ad21/image-17.jpg)

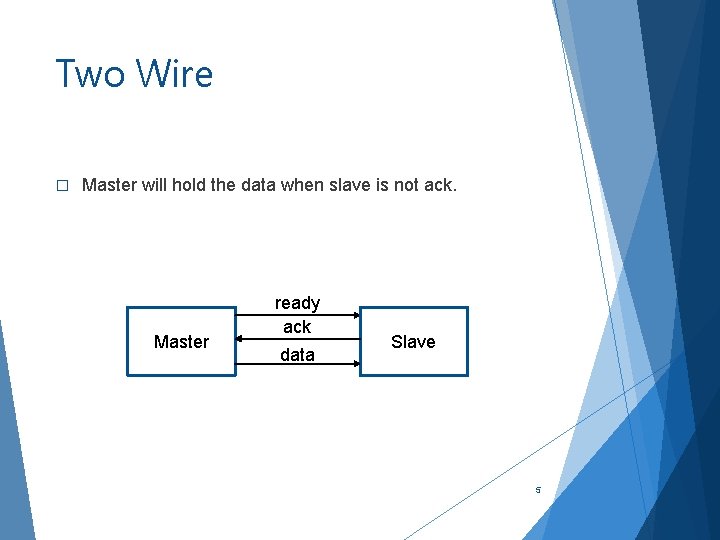

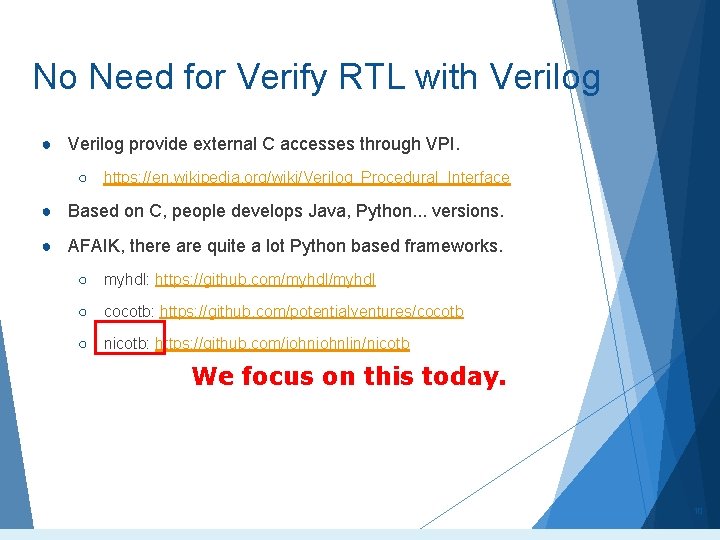

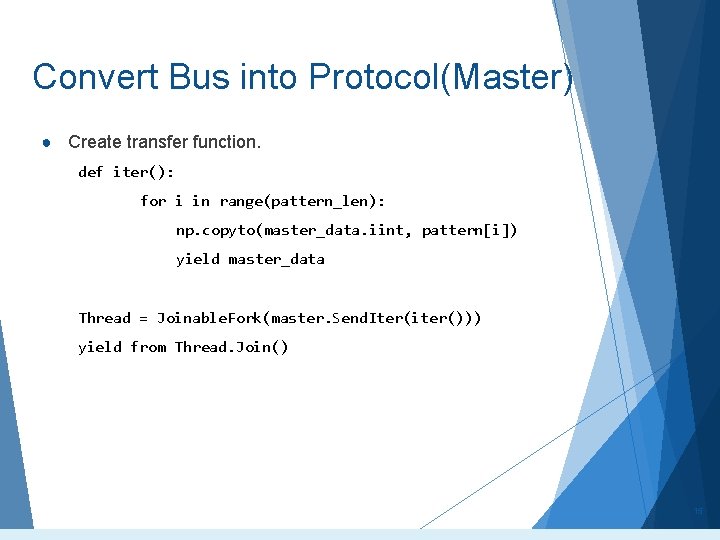

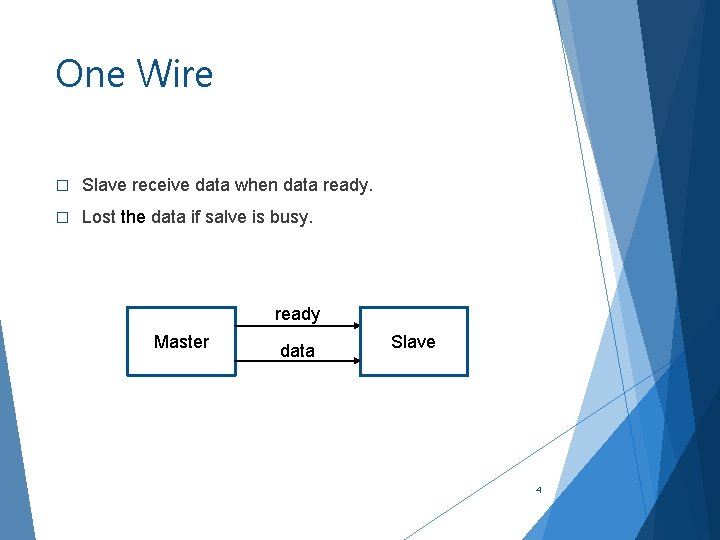

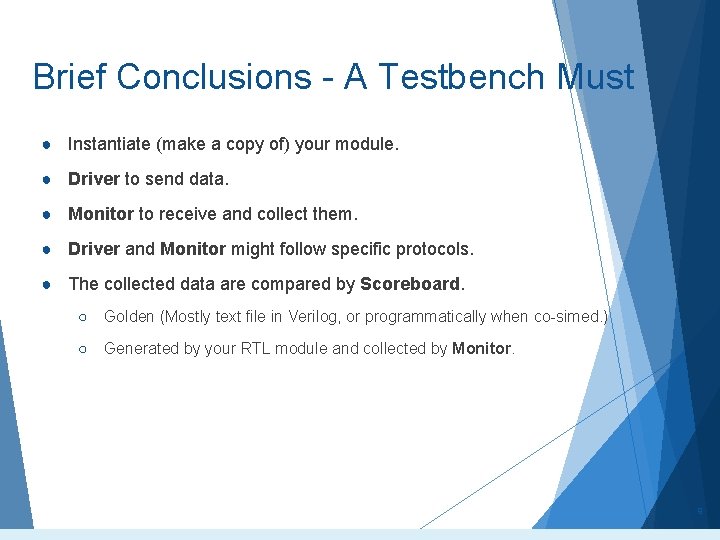

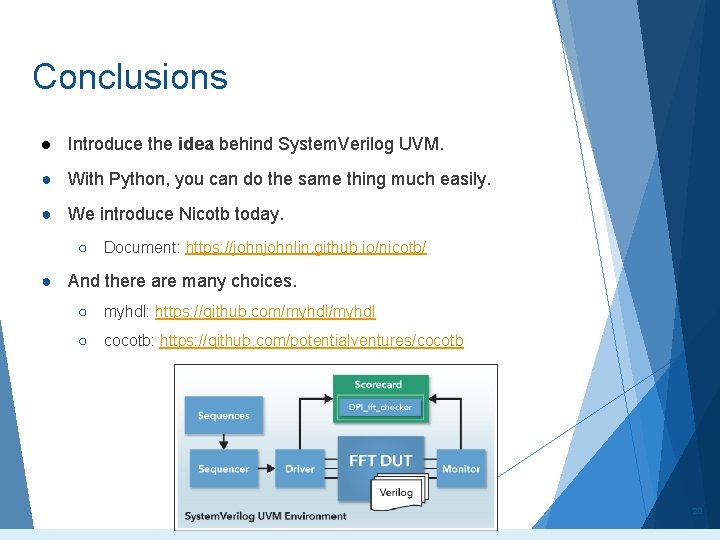

Expect(Slave) for i in range(golden_len): test. Expect((golden[i]. reshape(1, 1, 1) Check data every time dimension of data 17

![Constant value x Create Busesdut x x values00 xdata Constant value (x, ) = Create. Buses([((“dut”, “x”), ), ]) x. values[0][0] = x_data](https://slidetodoc.com/presentation_image_h2/824da20f6bfa9d32e1ed638b32b1ad21/image-18.jpg)

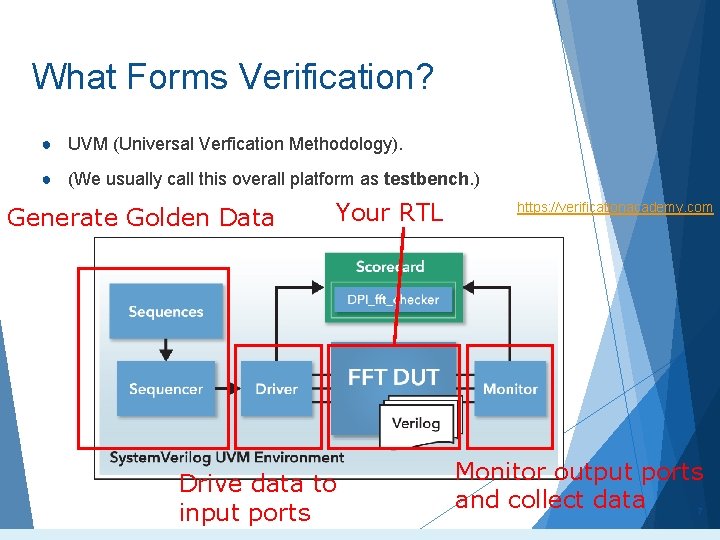

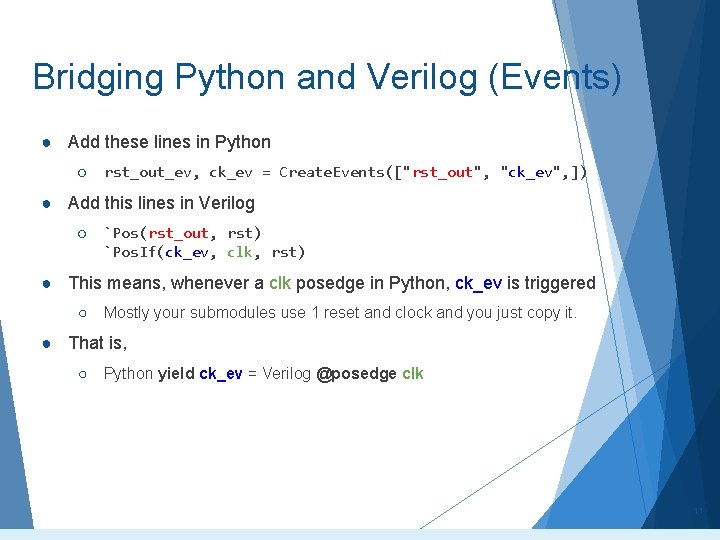

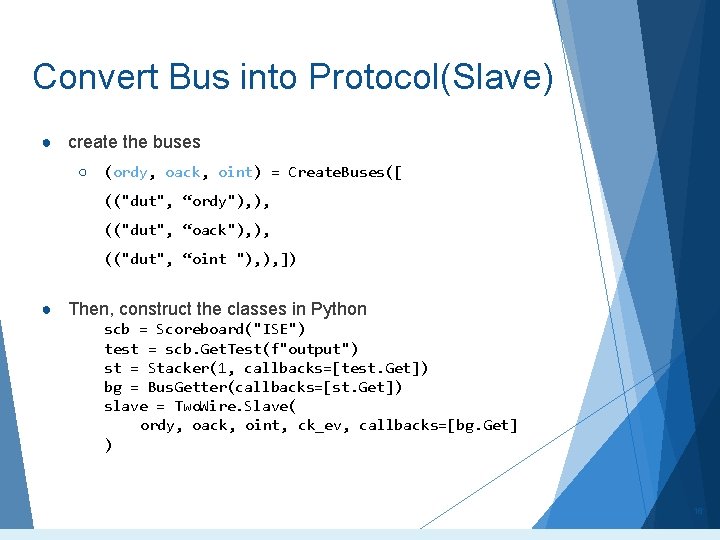

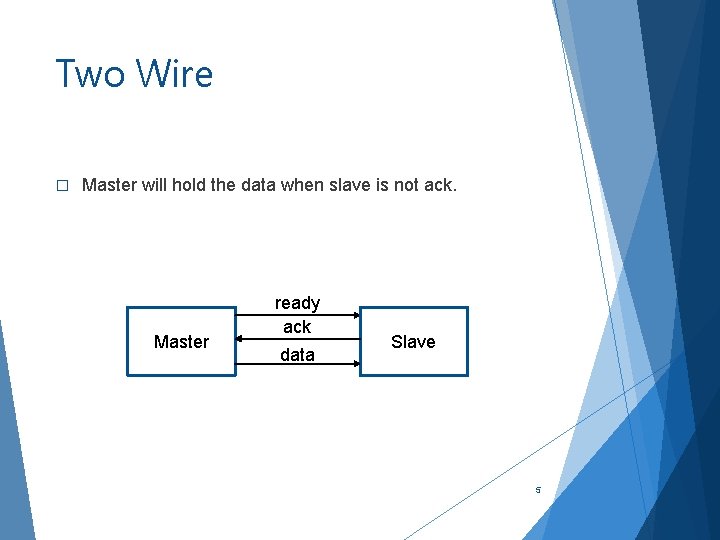

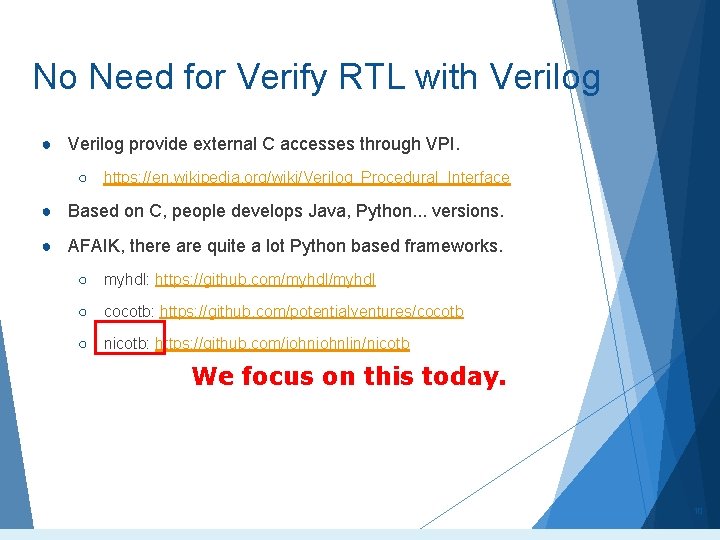

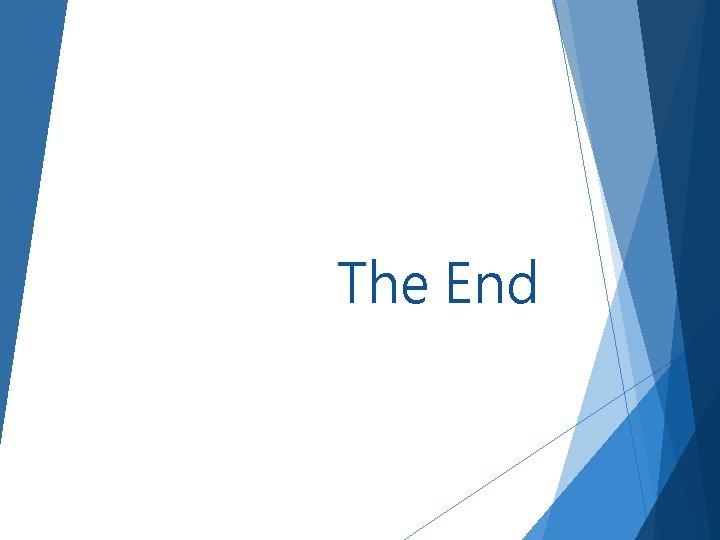

Constant value (x, ) = Create. Buses([((“dut”, “x”), ), ]) x. values[0][0] = x_data x. Write() 18

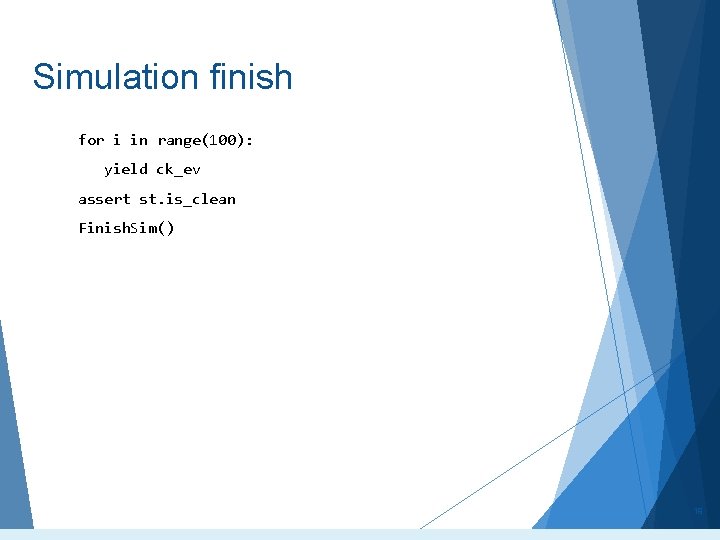

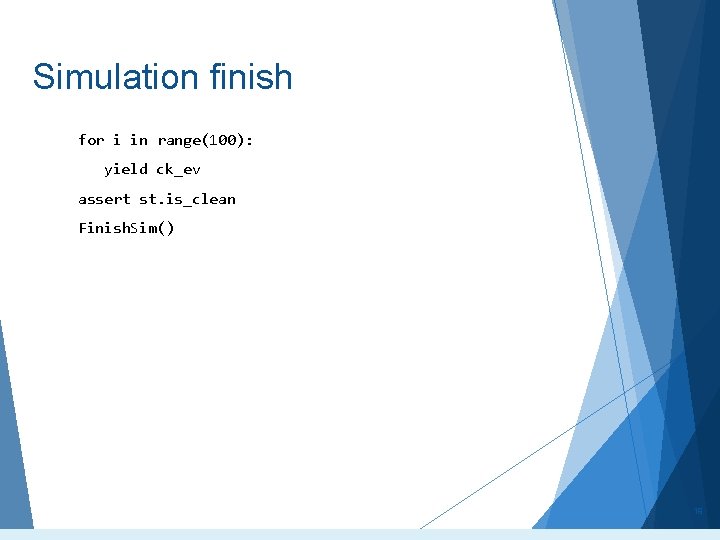

Simulation finish for i in range(100): yield ck_ev assert st. is_clean Finish. Sim() 19

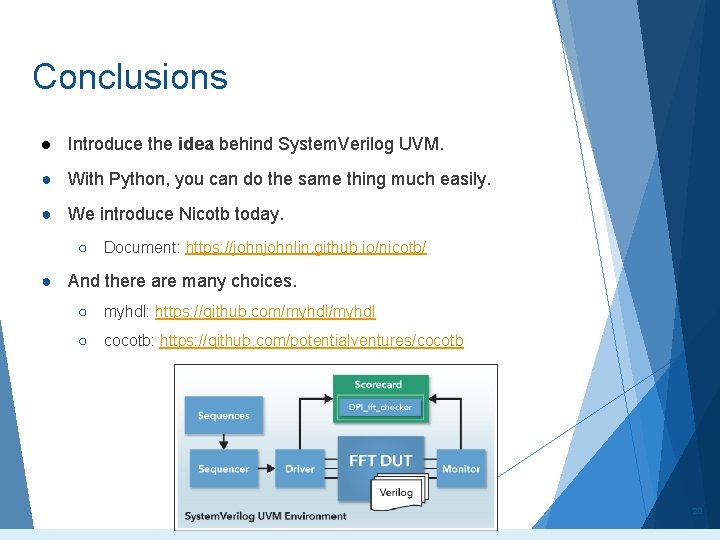

Conclusions ● Introduce the idea behind System. Verilog UVM. ● With Python, you can do the same thing much easily. ● We introduce Nicotb today. ○ Document: https: //johnlin. github. io/nicotb/ ● And there are many choices. ○ myhdl: https: //github. com/myhdl ○ cocotb: https: //github. com/potentialventures/cocotb 20

The End