Verilog Onebit Full Adder module fulladder A B

Verilog

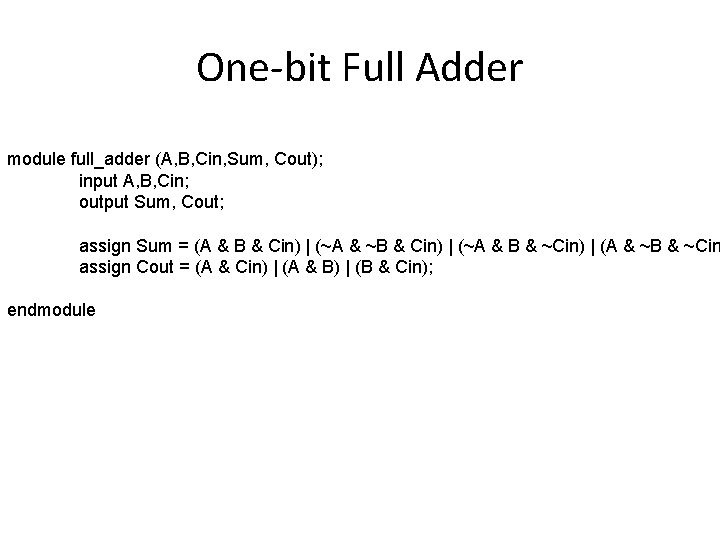

One-bit Full Adder module full_adder (A, B, Cin, Sum, Cout); input A, B, Cin; output Sum, Cout; assign Sum = (A & B & Cin) | (~A & ~B & Cin) | (~A & B & ~Cin) | (A & ~B & ~Cin assign Cout = (A & Cin) | (A & B) | (B & Cin); endmodule

![Four-bit Adder module four_bit_adder (A, B, Cin, Sum, Cout); input [3: 0] A; input Four-bit Adder module four_bit_adder (A, B, Cin, Sum, Cout); input [3: 0] A; input](http://slidetodoc.com/presentation_image_h2/a361f9006dffdfe9600e62cf194dc1d2/image-3.jpg)

Four-bit Adder module four_bit_adder (A, B, Cin, Sum, Cout); input [3: 0] A; input [3: 0] B; input Cin; output [3: 0] Sum; output Cout; wire C 0, C 1, C 2; full_adder FA 1(A[0], B[0], Cin, Sum[0], C 0); full_adder FA 2(A[1], B[1], C 0, Sum[1], C 1); full_adder FA 3(A[2], B[2], C 1, Sum[2], C 2); full_adder FA 4(A[3], B[3], C 2, Sum[3], Cout); endmodule

![MIPS ALU module MIPSALU (ALUctl, A, B, ALUOut, Zero); input [3: 0] ALUctl; input MIPS ALU module MIPSALU (ALUctl, A, B, ALUOut, Zero); input [3: 0] ALUctl; input](http://slidetodoc.com/presentation_image_h2/a361f9006dffdfe9600e62cf194dc1d2/image-4.jpg)

MIPS ALU module MIPSALU (ALUctl, A, B, ALUOut, Zero); input [3: 0] ALUctl; input [31: 0] A, B; output reg [31: 0] ALUOut; output Zero; assign Zero = (ALUOut==0); //Zero is true if ALUOut is 0; goes anywhere always @(ALUctl, A, B) //reevaluate if these change case (ALUctl) 0: ALUOut <= A & B; 1: ALUOut <= A | B; 2: ALUOut <= A + B; 6: ALUOut <= A - B; 7: ALUOut <= A < B ? 1: 0; 12: ALUOut <= ~(A | B); // result is nor default: ALUOut <= 0; //default to 0, should not happen; endcase

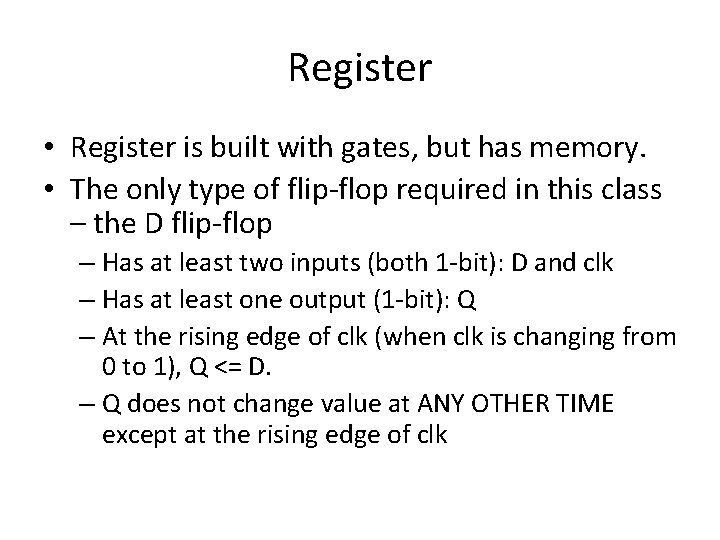

Register • Register is built with gates, but has memory. • The only type of flip-flop required in this class – the D flip-flop – Has at least two inputs (both 1 -bit): D and clk – Has at least one output (1 -bit): Q – At the rising edge of clk (when clk is changing from 0 to 1), Q <= D. – Q does not change value at ANY OTHER TIME except at the rising edge of clk

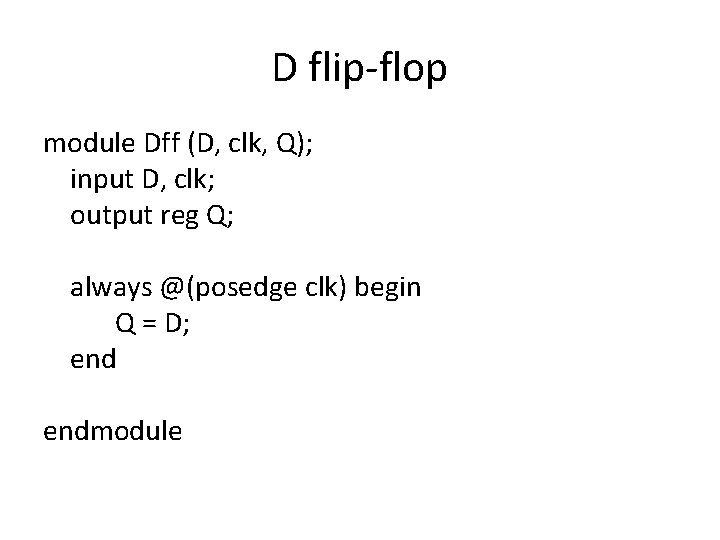

D flip-flop module Dff (D, clk, Q); input D, clk; output reg Q; always @(posedge clk) begin Q = D; endmodule

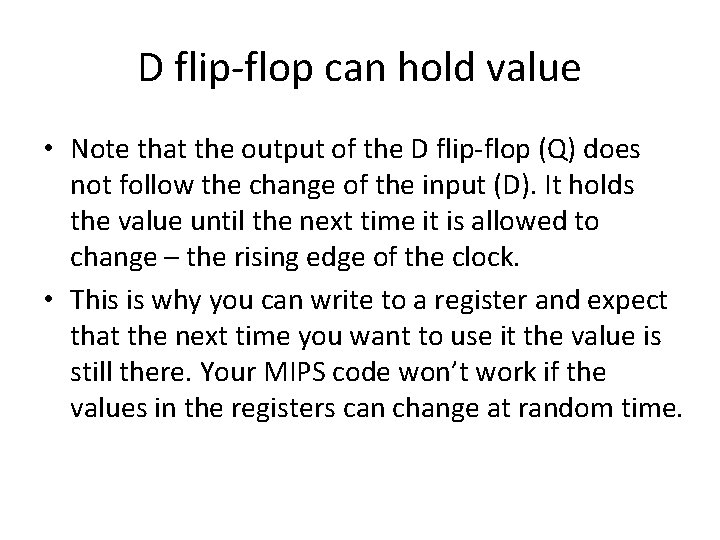

D flip-flop can hold value • Note that the output of the D flip-flop (Q) does not follow the change of the input (D). It holds the value until the next time it is allowed to change – the rising edge of the clock. • This is why you can write to a register and expect that the next time you want to use it the value is still there. Your MIPS code won’t work if the values in the registers can change at random time.

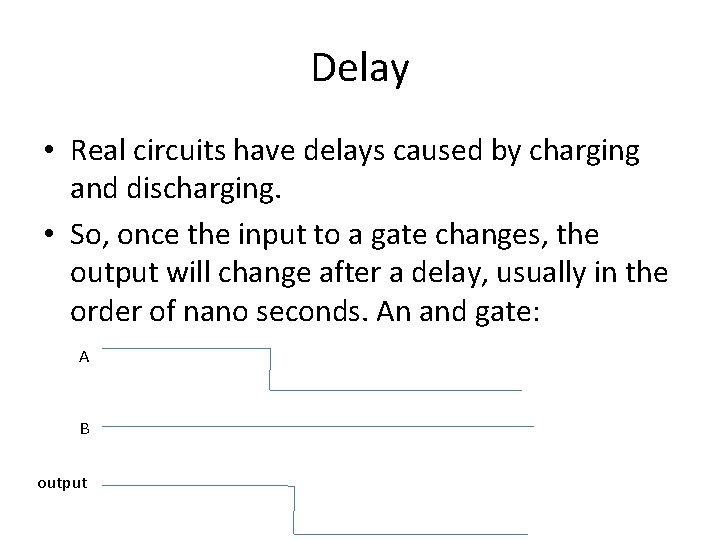

Delay • Real circuits have delays caused by charging and discharging. • So, once the input to a gate changes, the output will change after a delay, usually in the order of nano seconds. An and gate: A B output

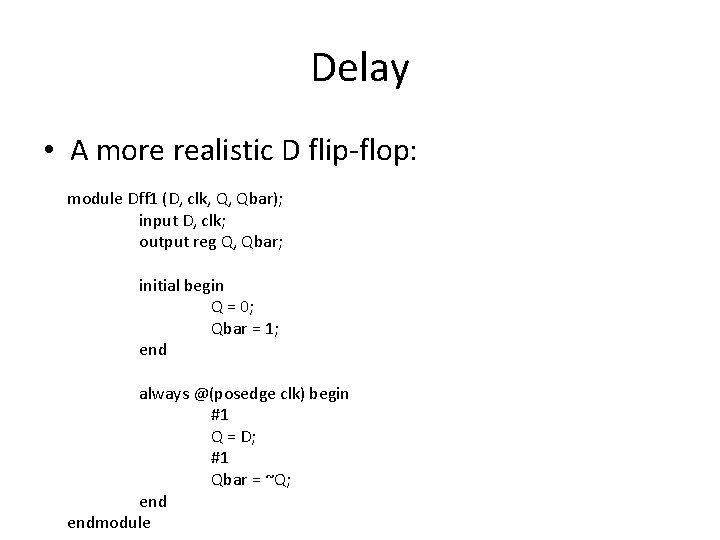

Delay • A more realistic D flip-flop: module Dff 1 (D, clk, Q, Qbar); input D, clk; output reg Q, Qbar; initial begin Q = 0; Qbar = 1; end always @(posedge clk) begin #1 Q = D; #1 Qbar = ~Q; endmodule

What happens if… What happens if I connect a Dff like this? wire Q 2, Qbar 2; Dff 1 D 2 (Qbar 2, clk, Q 2, Qbar 2);

The verilog code used in the class • http: //www. cs. fsu. edu/~zzhang/CDA 3100_Spring_2009_files/week 11_1. v

- Slides: 11