Verilog HDL Sun HyeSeung Hanbat National University Prof

Verilog HDL 개요 한밭대학교 반도체설계실 Sun, Hye-Seung Hanbat National University Prof. Lee Jaeheung

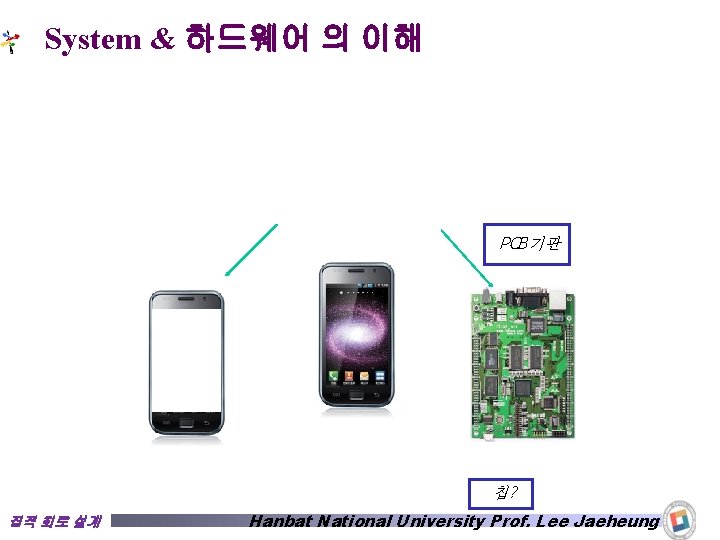

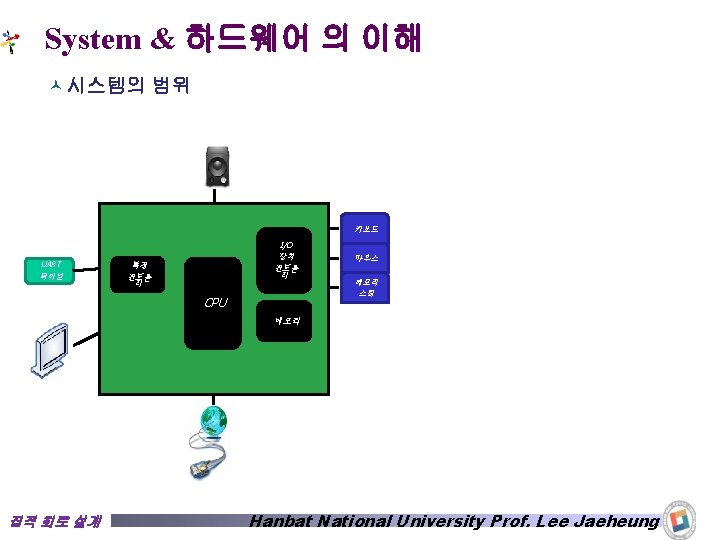

System & 하드웨어 의 이해 PCB기판 칩? 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

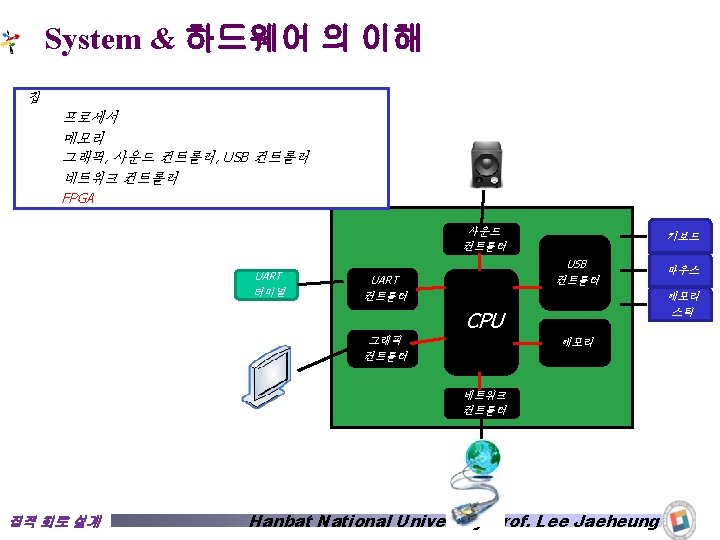

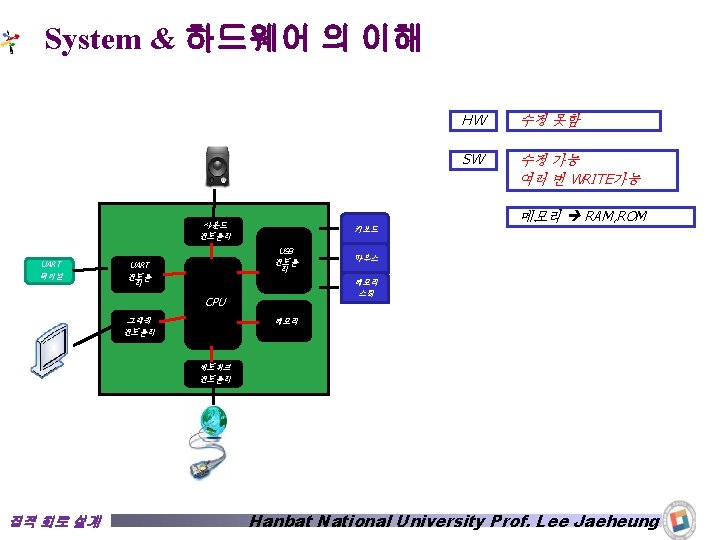

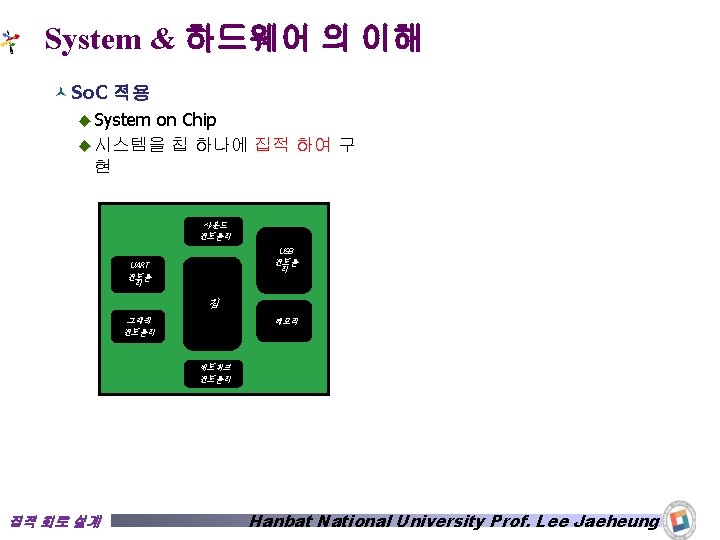

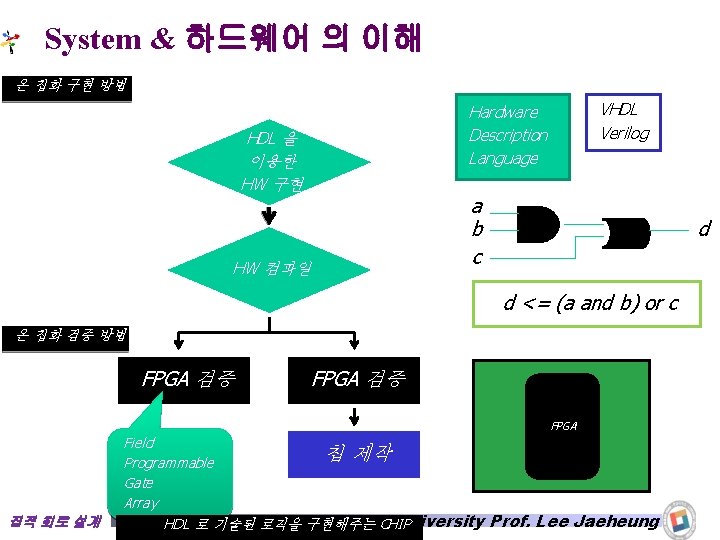

System & 하드웨어 의 이해 온 칩화 구현 방법 VHDL Verilog Hardware Description Language HDL 을 이용한 HW 구현 a b c HW 컴파일 d d <= (a and b) or c 온 칩화 검증 방법 FPGA 검증 사운드 컨트롤러 UART 컨트롤 러 CPU FPGA CPU 메모리 Field 칩 제작 Programmable 네트워크 컨트롤러 Gate Array National University Prof. Lee Jaeheung HDL 로 기술된Hanbat 로직을 구현해주는 CHIP 그래픽 컨트롤 러 집적 회로 설계 USB 컨트롤 러

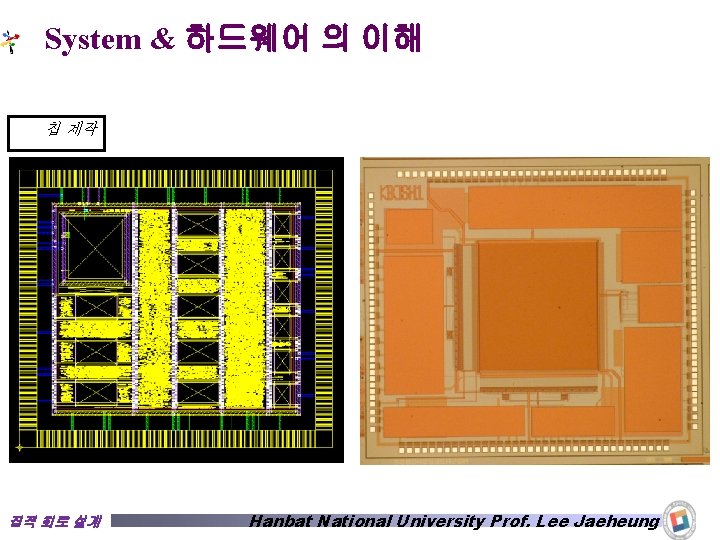

System & 하드웨어 의 이해 칩 제작 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

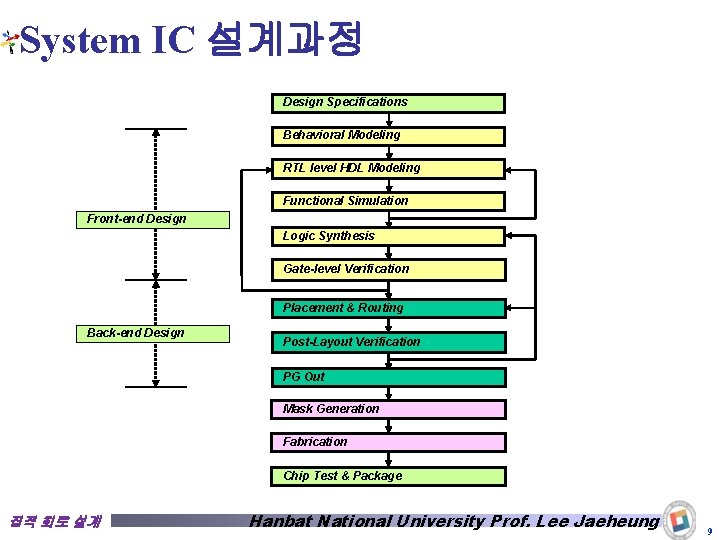

System IC 설계과정 Design Specifications Behavioral Modeling RTL level HDL Modeling Functional Simulation Front-end Design Logic Synthesis Gate-level Verification Placement & Routing Back-end Design Post-Layout Verification PG Out Mask Generation Fabrication Chip Test & Package 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 9

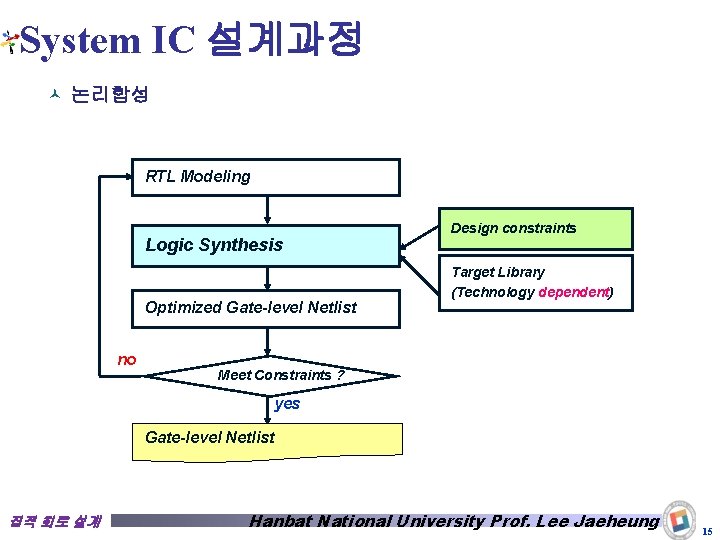

System IC 설계과정 © 논리합성 RTL Modeling Logic Synthesis Optimized Gate-level Netlist no Design constraints Target Library (Technology dependent) Meet Constraints ? yes Gate-level Netlist 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 15

System IC 설계과정 © 논리합성 과정 Synthesis = Translation + Logic Optimization + Mapping residue = 16’h 0000; if (high_bits == 2’b 10) residue = state_table[index]; Translate (read) else state_table[index] = 16’h 0000; Optimize + Map (compile) HDL Source Generic Boolean Target Technology 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 17

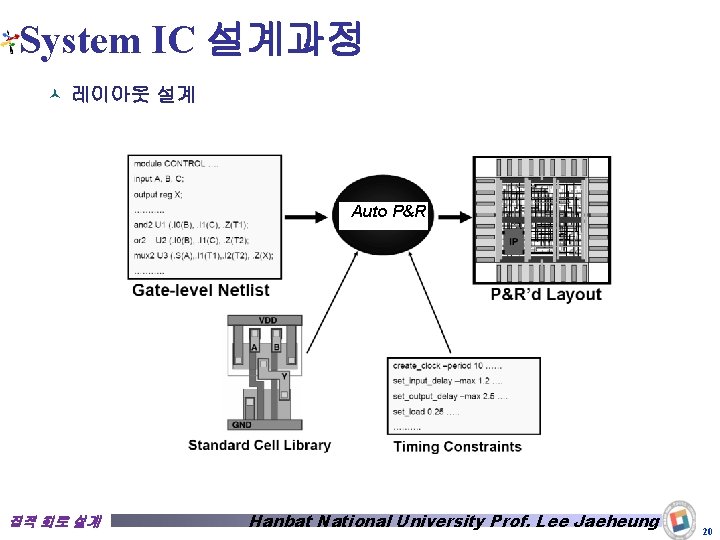

System IC 설계과정 © 레이아웃 설계 Auto P&R 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 20

Verilog HDL의 역사 © Verilog HDL ◆ 1983년 Gateway Design Automation사에서 하드웨어 기술언어인 Hi. Lo 와 C 언어의 특징을 기반으로 개발 ◆ 1991년 Cadence Design Systems가 Open Verilog International (OVI)라 는 조직을 구성하고 Verilog HDL을 공개 ◆ 1993년 IEEE Working Group이 구성되어 표준화 작업을 진행 ◆ 1995년 12월 IEEE Std. 1364 -1995로 표준화 ◆ 2001년에 IEEE Std. 1364 -2001로 개정 ◆ Verilog HDL의 확장 형태인 System. Verilog가 개발되어 IEEE 표준화를 추진 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 23

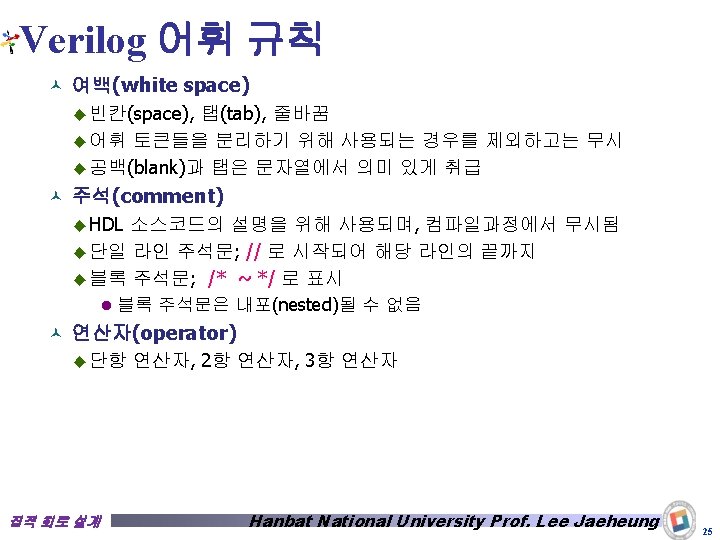

Verilog 어휘 규칙 © 어휘 토큰 (lexical tokens) ◆ 여백(white space) ◆ 주석(comment) ◆ 연산자(operator) ◆ 수(number) ◆ 문자열(string) ◆ 식별자(identifier) ◆ 키워드(keyword) 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 24

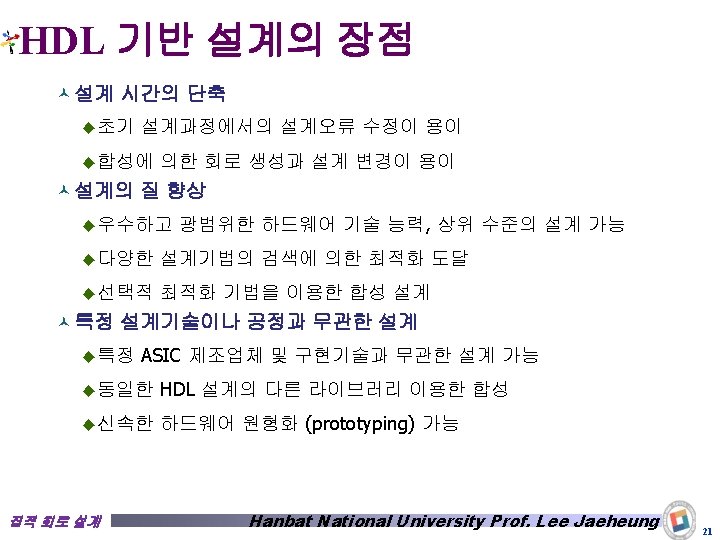

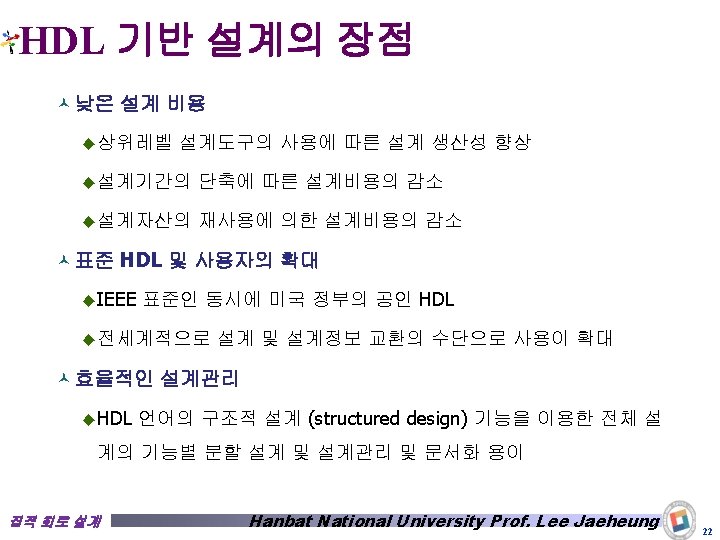

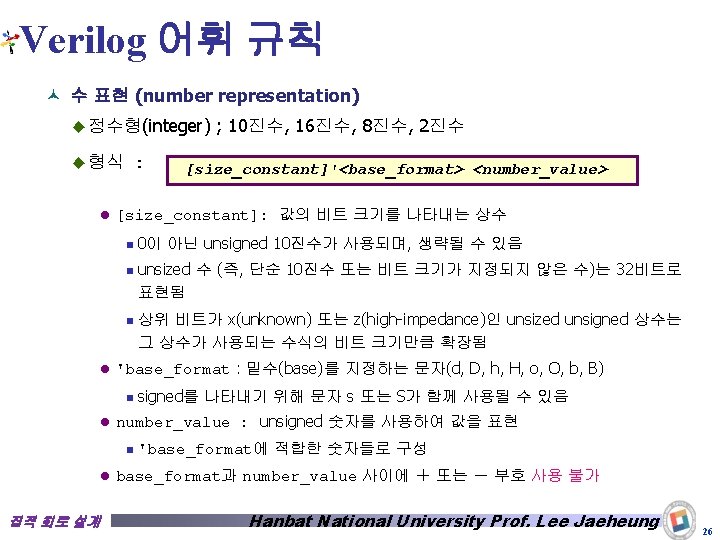

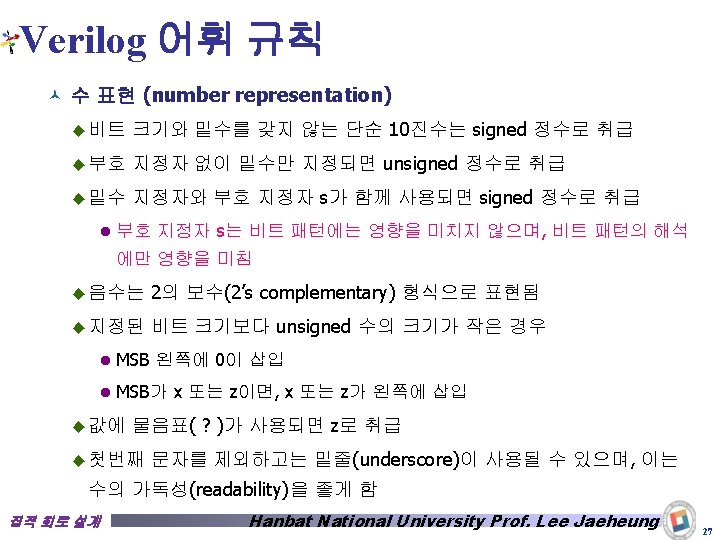

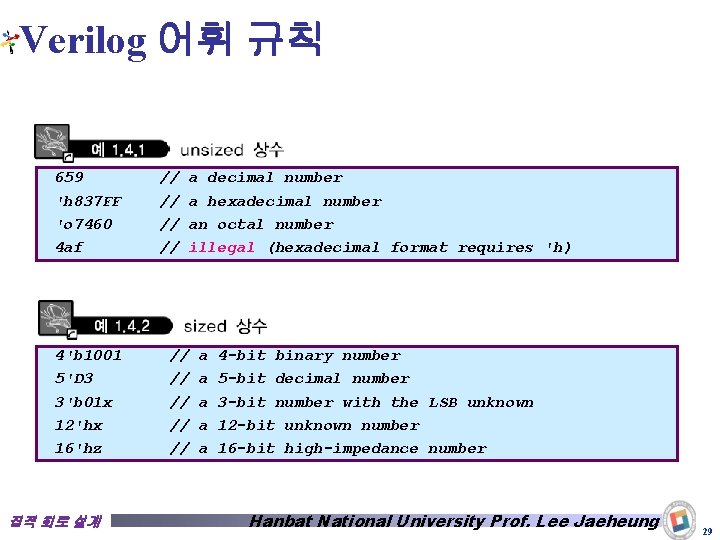

Verilog 어휘 규칙 Number # of Bits Base Dec. Equiv. Stored 10 32 Decimal 10 00. . 01010 2’b 10 2 Binary 2 10 3’d 5 3 Decimal 5 101 8’o 5 8 Octal 5 00000101 8’ha 8 Hex 10 00001010 3’b 5 Invalid! 3’b 01 x 3 Binary - 01 x 12’hx 12 Hex - xxxxxx 8’b 0000_0001 8 Binary 1 00000001 8’bx 01 8 Binary - xxxxxx 01 ’bz Unsized Binary - zz. . . zz(32 bits) 8’HAD 8 Hex 집적 회로 설계 173 10101101 Hanbat National University Prof. Lee Jaeheung 28

Verilog 어휘 규칙 659 // a decimal number 'h 837 FF // a hexadecimal number 'o 7460 // an octal number 4 af // illegal (hexadecimal format requires 'h) 4'b 1001 // a 4 -bit binary number 5'D 3 // a 5 -bit decimal number 3'b 01 x // a 3 -bit number with the LSB unknown 12'hx // a 12 -bit unknown number 16'hz // a 16 -bit high-impedance number 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 29

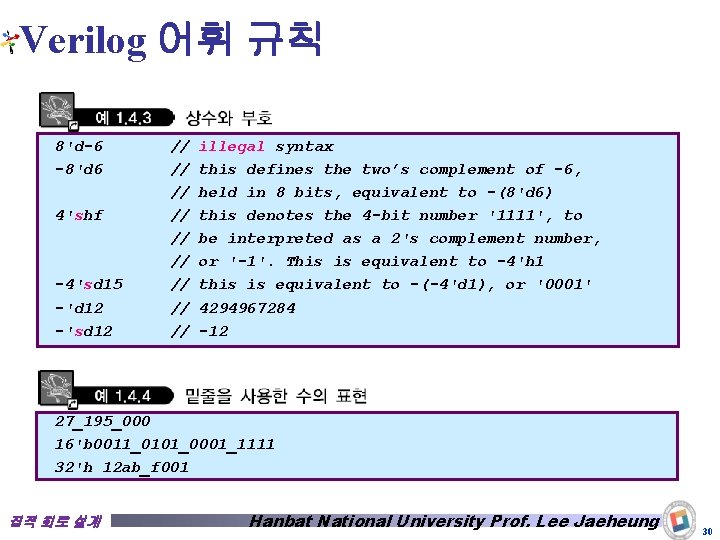

Verilog 어휘 규칙 8'd-6 // illegal syntax -8'd 6 // this defines the two’s complement of -6, // held in 8 bits, equivalent to -(8'd 6) 4'shf // this denotes the 4 -bit number '1111', to // be interpreted as a 2's complement number, // or '-1'. This is equivalent to -4'h 1 -4'sd 15 // this is equivalent to -(-4'd 1), or '0001' -'d 12 // 4294967284 -'sd 12 // -12 27_195_000 16'b 0011_0101_0001_1111 32'h 12 ab_f 001 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 30

![Verilog 어휘 규칙 reg [11: 0] a, b, c, d; initial begin a = Verilog 어휘 규칙 reg [11: 0] a, b, c, d; initial begin a =](http://slidetodoc.com/presentation_image_h/c0f7ad938d88b5ad0829fcff4e443255/image-32.jpg)

Verilog 어휘 규칙 reg [11: 0] a, b, c, d; initial begin a = 'hx; // yields xxx b = 'h 3 x; // yields 03 x c = 'hz 3; // yields zz 3 d = 'h 0 z 3; // yields 0 z 3 end 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 31

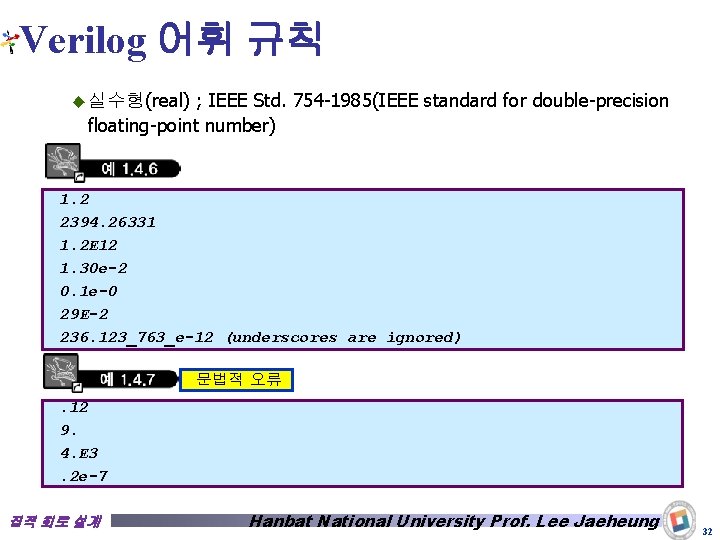

Verilog 어휘 규칙 ; IEEE Std. 754 -1985(IEEE standard for double-precision floating-point number) ◆ 실수형(real) 1. 2 2394. 26331 1. 2 E 12 1. 30 e-2 0. 1 e-0 29 E-2 236. 123_763_e-12 (underscores are ignored) 문법적 오류. 12 9. 4. E 3. 2 e-7 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 32

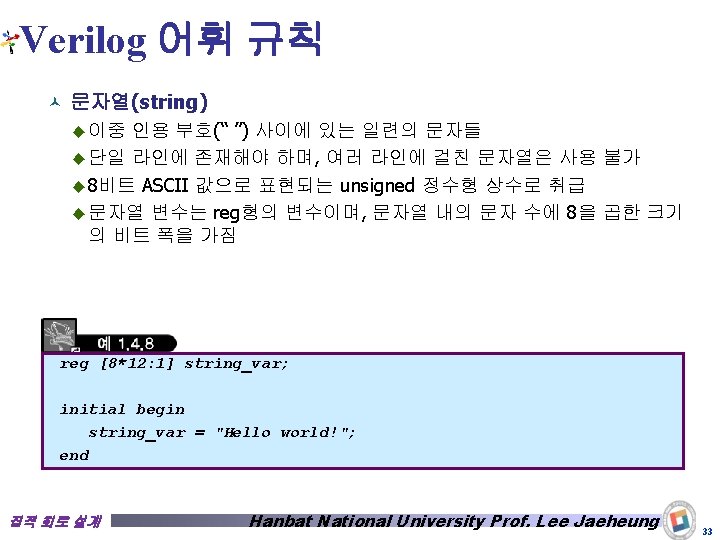

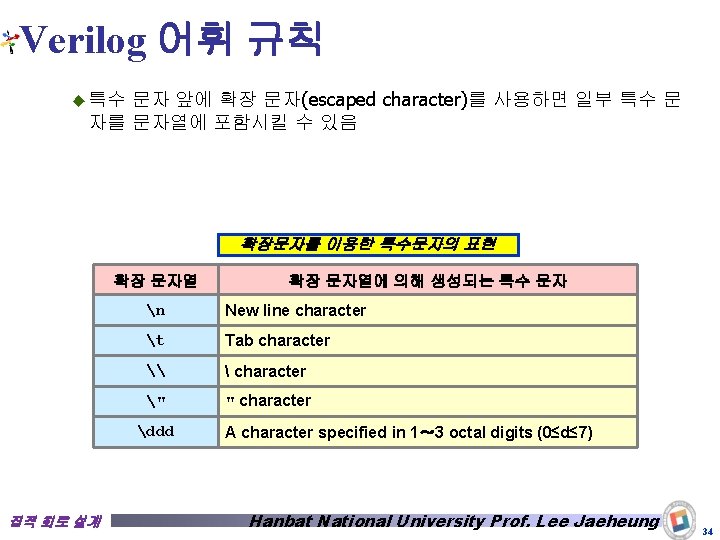

Verilog 어휘 규칙 문자 앞에 확장 문자(escaped character)를 사용하면 일부 특수 문 자를 문자열에 포함시킬 수 있음 ◆ 특수 확장문자를 이용한 특수문자의 표현 확장 문자열 n New line character t Tab character \ character " " character ddd 집적 회로 설계 확장 문자열에 의해 생성되는 특수 문자 A character specified in 1~ 3 octal digits (0≤d≤ 7) Hanbat National University Prof. Lee Jaeheung 34

![Verilog 어휘 규칙 module string_test; reg [8*14: 1] stringvar; initial begin stringvar = "Hello Verilog 어휘 규칙 module string_test; reg [8*14: 1] stringvar; initial begin stringvar = "Hello](http://slidetodoc.com/presentation_image_h/c0f7ad938d88b5ad0829fcff4e443255/image-36.jpg)

Verilog 어휘 규칙 module string_test; reg [8*14: 1] stringvar; initial begin stringvar = "Hello world"; $display("%s is stored as %h", stringvar); stringvar = {stringvar, "!!!"}; $display("%s is stored as %h", stringvar); endmodule Hello world is stored as 00000048656 c 6 c 6 f 20776 f 726 c 64 Hello world!!! is stored as 48656 c 6 c 6 f 20776 f 726 c 64212121 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 35

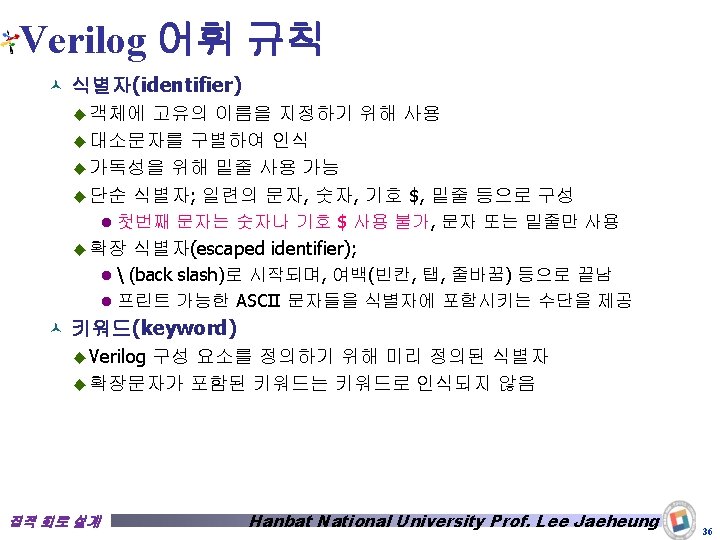

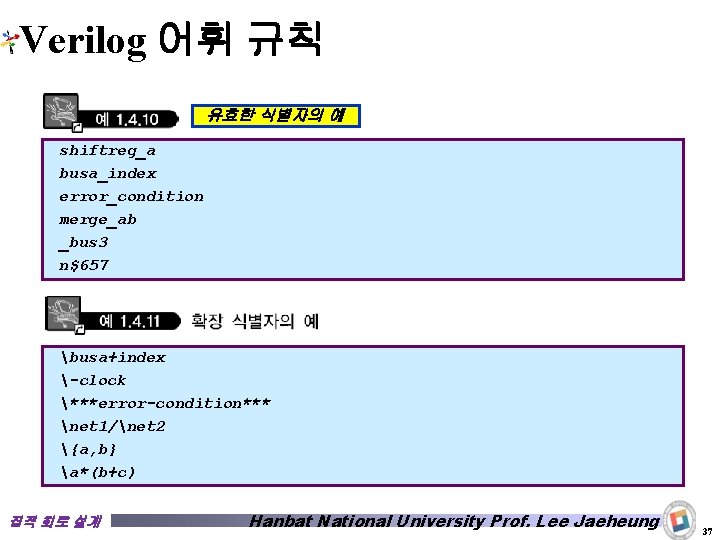

Verilog 어휘 규칙 유효한 식별자의 예 shiftreg_a busa_index error_condition merge_ab _bus 3 n$657 busa+index -clock ***error-condition*** net 1/net 2 {a, b} a*(b+c) 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 37

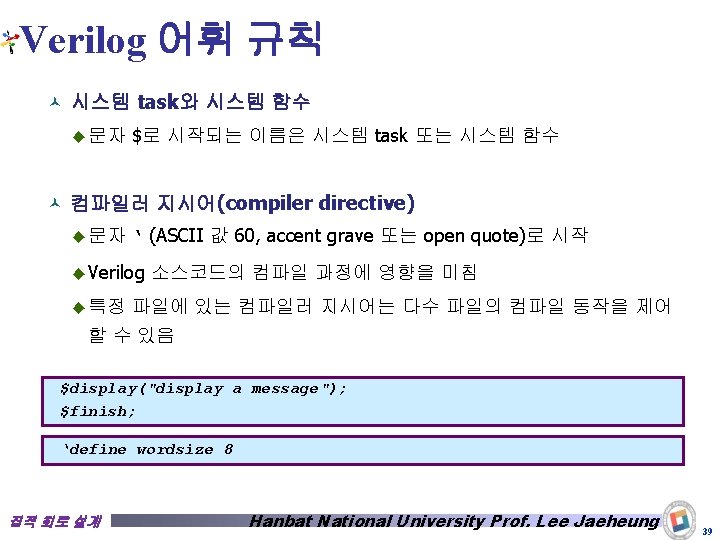

Verilog 어휘 규칙 © Verilog keyword (일부) 집적 회로 설계 always if release and ifnone repeat assign incdir rnmos automatic include rpmos begin initial rtran buf inout rtranif 0 bufif 0 input rtranif 1 bufif 1 instance scalared case integer showcancelled casex join signed casez large small cell liblist specify cmos library specparam config localparam strong 0 deassign macromodule strong 1 default medium supply 0 defparam module supply 1 design nand table disable negedge task edge nmos time else nor tran end not tranif 0 endcase notif 0 tranif 1 Hanbat National University Prof. Lee Jaeheung 38

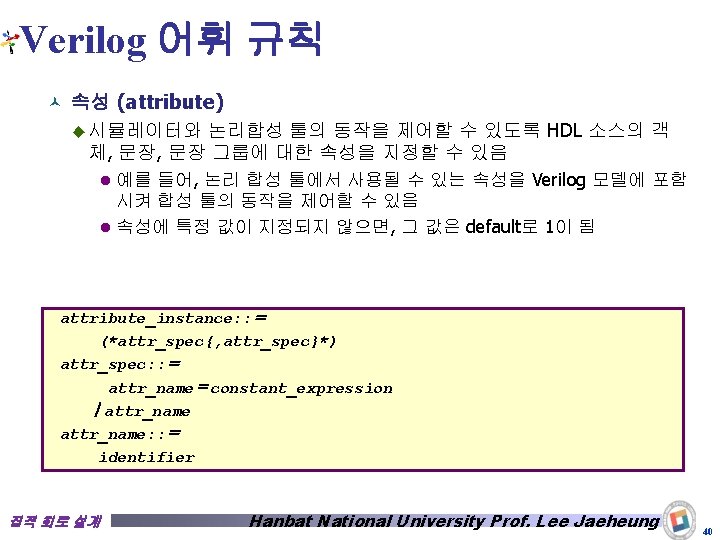

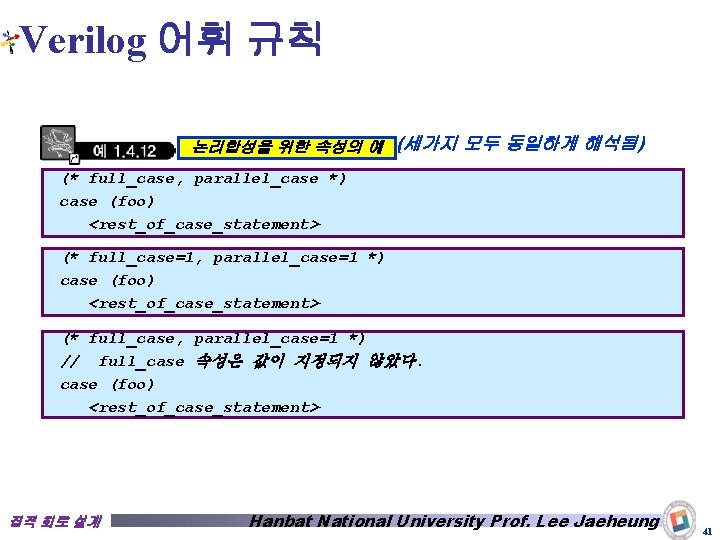

Verilog 어휘 규칙 논리합성을 위한 속성의 예 (세가지 모두 동일하게 해석됨) (* full_case, parallel_case *) case (foo) <rest_of_case_statement> (* full_case=1, parallel_case=1 *) case (foo) <rest_of_case_statement> (* full_case, parallel_case=1 *) // full_case 속성은 값이 지정되지 않았다. case (foo) <rest_of_case_statement> 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 41

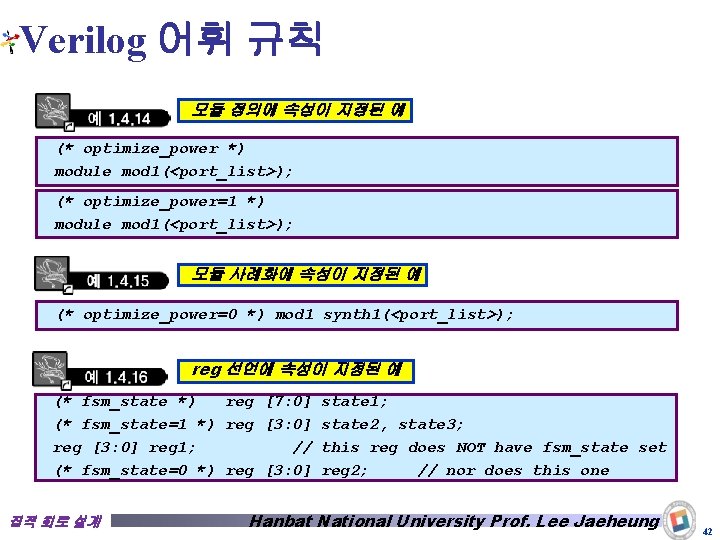

Verilog 어휘 규칙 모듈 정의에 속성이 지정된 예 (* optimize_power *) module mod 1(<port_list>); (* optimize_power=1 *) module mod 1(<port_list>); 모듈 사례화에 속성이 지정된 예 (* optimize_power=0 *) mod 1 synth 1(<port_list>); reg 선언에 속성이 지정된 예 (* fsm_state *) reg [7: 0] state 1; (* fsm_state=1 *) reg [3: 0] state 2, state 3; reg [3: 0] reg 1; // this reg does NOT have fsm_state set (* fsm_state=0 *) reg [3: 0] reg 2; // nor does this one 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 42

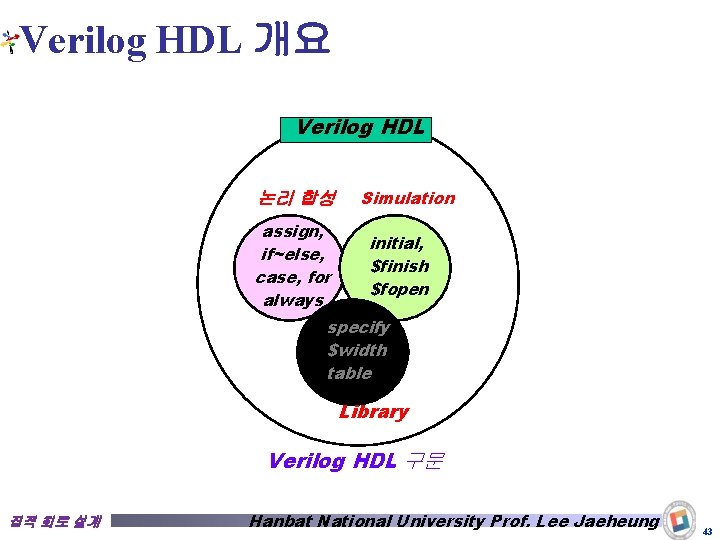

Verilog HDL 개요 Verilog HDL 논리 합성 assign, if~else, case, for always Simulation initial, $finish $fopen specify $width table Library Verilog HDL 구문 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 43

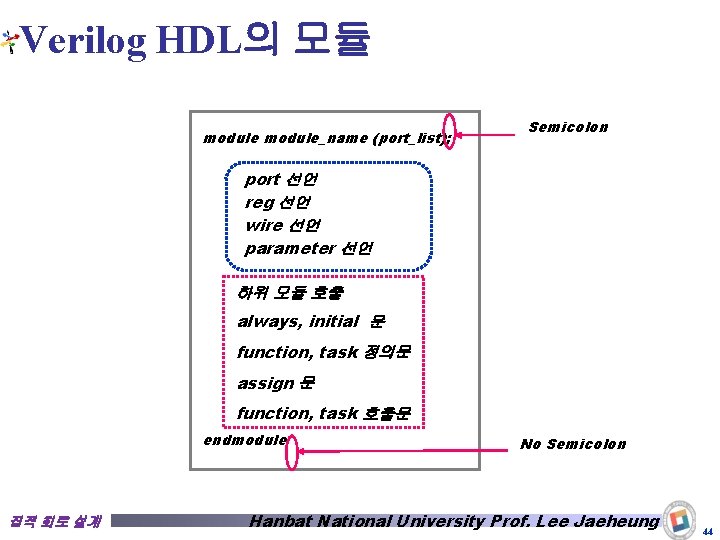

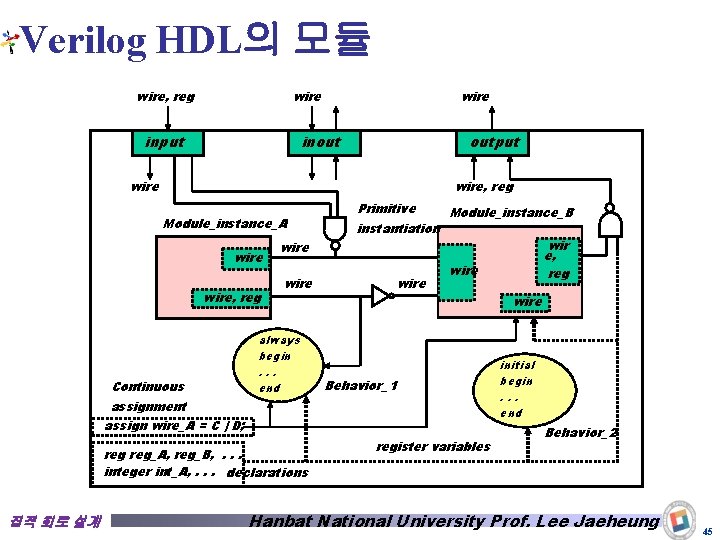

Verilog HDL의 모듈 module_name (port_list); Semicolon port 선언 reg 선언 wire 선언 parameter 선언 하위 모듈 호출 always, initial 문 function, task 정의문 assign 문 function, task 호출문 endmodule 집적 회로 설계 No Semicolon Hanbat National University Prof. Lee Jaeheung 44

Verilog HDL의 모듈 wire, reg wire input wire inout output wire, reg Module_instance_A wire, reg Continuous Primitive instantiation Module_instance_B wire always begin. . . end wire Behavior_1 assignment assign wire_A = C | D; reg_A, reg_B, . . . integer int_A, . . . declarations 집적 회로 설계 wir e, reg wire register variables initial begin. . . end Behavior_2 Hanbat National University Prof. Lee Jaeheung 45

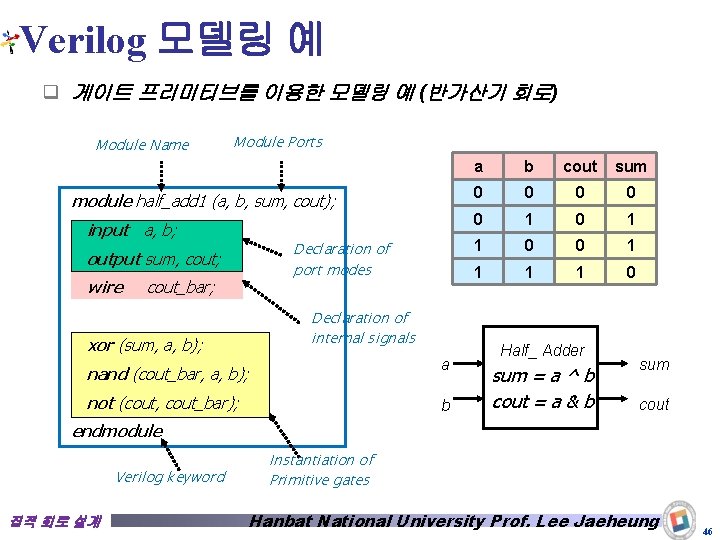

Verilog 모델링 예 q 게이트 프리미티브를 이용한 모델링 예 (반가산기 회로) Module Name Module Ports module half_add 1 (a, b, sum, cout); input a, b; Declaration of port modes output sum, cout; wire cout_bar; Declaration of internal signals xor (sum, a, b); nand (cout_bar, a, b); a not (cout, cout_bar); b a b cout sum 0 0 0 1 1 0 Half_ Adder sum = a ^ b cout = a & b sum cout endmodule Verilog keyword 집적 회로 설계 Instantiation of Primitive gates Hanbat National University Prof. Lee Jaeheung 46

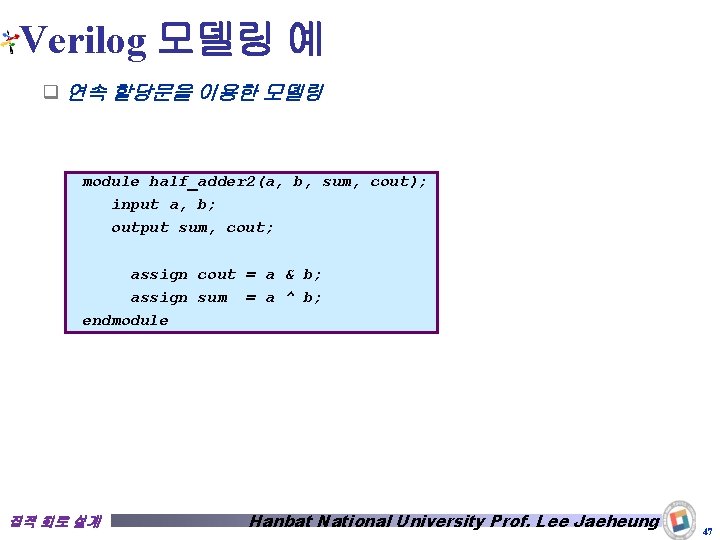

Verilog 모델링 예 q 연속 할당문을 이용한 모델링 module half_adder 2(a, b, sum, cout); input a, b; output sum, cout; assign cout = a & b; assign sum = a ^ b; endmodule 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 47

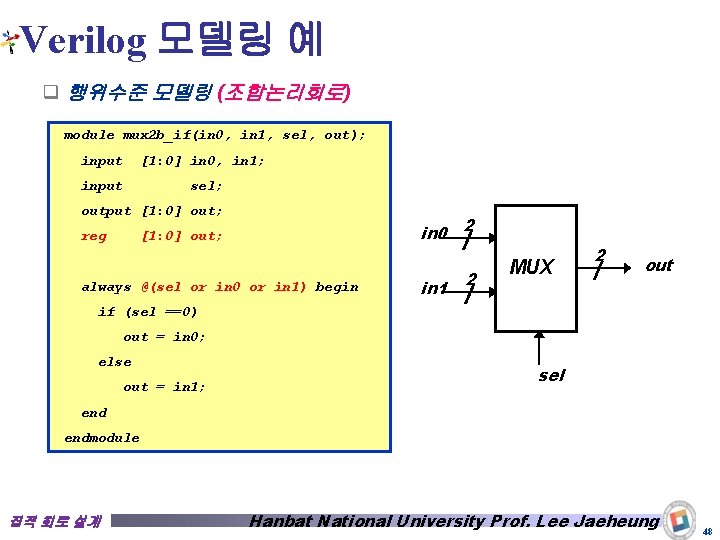

Verilog 모델링 예 q 행위수준 모델링 (조합논리회로) module mux 2 b_if(in 0, in 1, sel, out); input [1: 0] in 0, in 1; input sel; output [1: 0] out; in 0 2 reg [1: 0] out; always @(sel or in 0 or in 1) begin in 1 2 MUX 2 out if (sel ==0) out = in 0; else out = in 1; sel endmodule 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 48

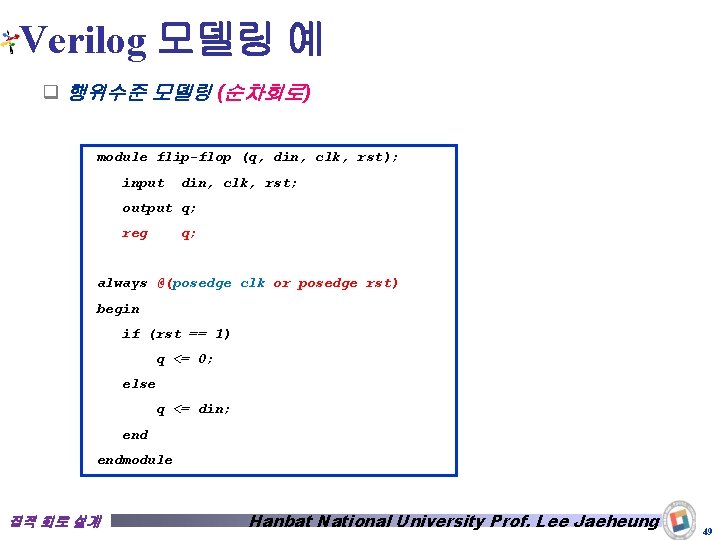

Verilog 모델링 예 q 행위수준 모델링 (순차회로) module flip-flop (q, din, clk, rst); input din, clk, rst; output q; reg q; always @(posedge clk or posedge rst) begin if (rst == 1) q <= 0; else q <= din; endmodule 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 49

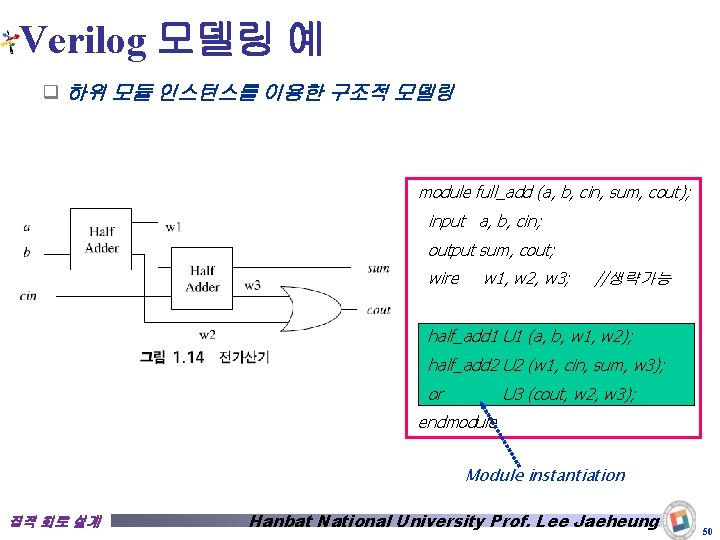

Verilog 모델링 예 q 하위 모듈 인스턴스를 이용한 구조적 모델링 module full_add (a, b, cin, sum, cout); input a, b, cin; output sum, cout; wire w 1, w 2, w 3; //생략가능 half_add 1 U 1 (a, b, w 1, w 2); half_add 2 U 2 (w 1, cin, sum, w 3); or U 3 (cout, w 2, w 3); endmodule Module instantiation 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 50

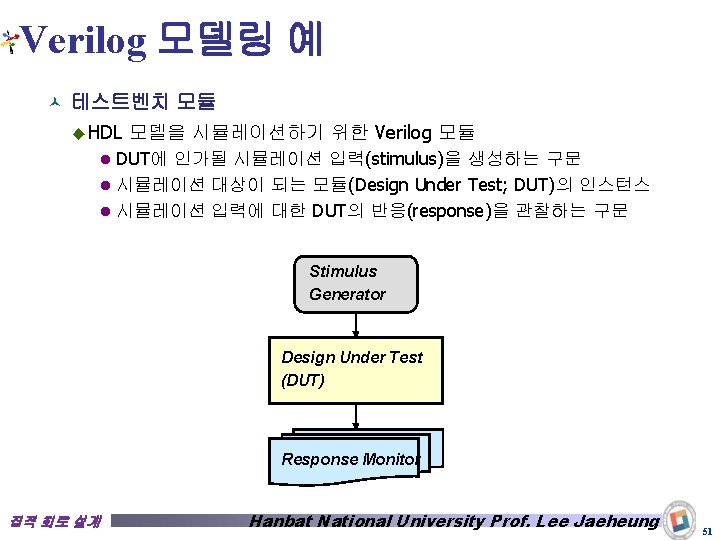

Verilog 모델링 예 © 테스트벤치 모듈 ◆ HDL 모델을 시뮬레이션하기 위한 Verilog 모듈 l DUT에 인가될 시뮬레이션 입력(stimulus)을 생성하는 구문 l 시뮬레이션 대상이 되는 모듈(Design Under Test; DUT)의 인스턴스 l 시뮬레이션 입력에 대한 DUT의 반응(response)을 관찰하는 구문 Stimulus Generator Design Under Test (DUT) Response Monitor 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 51

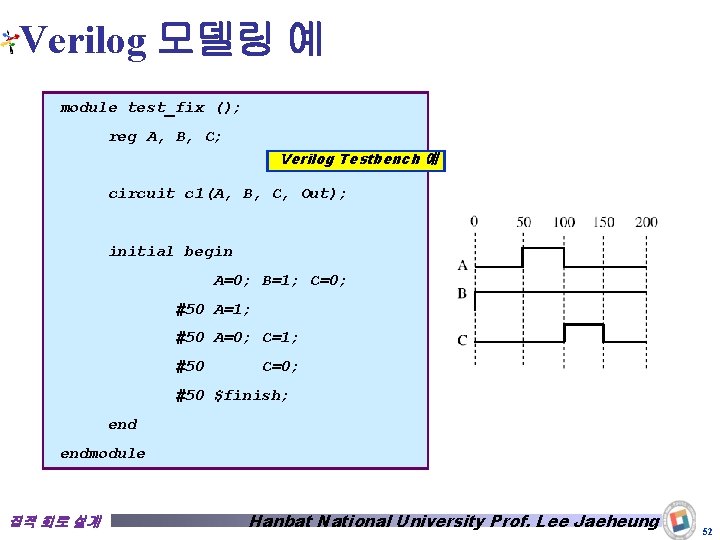

Verilog 모델링 예 module test_fix (); reg A, B, C; Verilog Testbench 예 circuit c 1(A, B, C, Out); initial begin A=0; B=1; C=0; #50 A=1; #50 A=0; C=1; #50 C=0; #50 $finish; endmodule 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 52

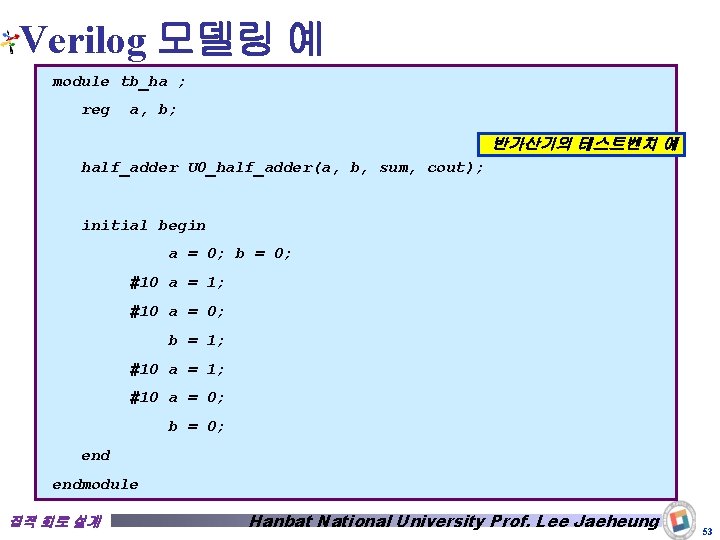

Verilog 모델링 예 module tb_ha ; reg a, b; 반가산기의 테스트벤치 예 half_adder U 0_half_adder(a, b, sum, cout); initial begin a = 0; b = 0; #10 a = 1; #10 a = 0; b = 0; endmodule 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 53

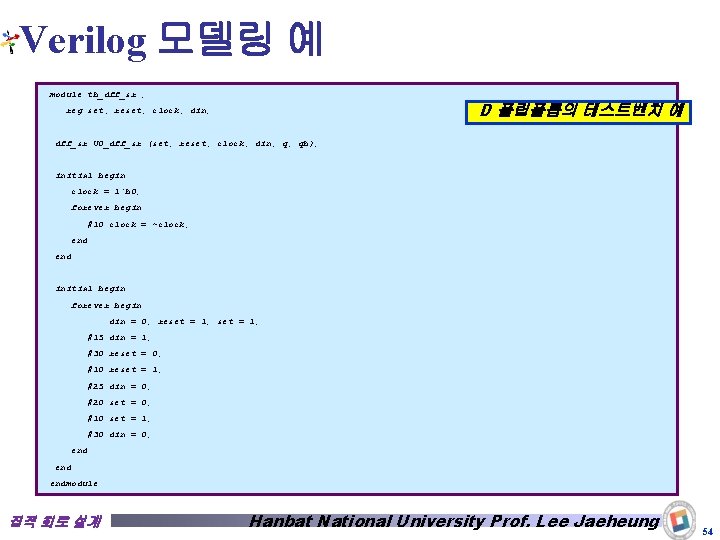

Verilog 모델링 예 module tb_dff_sr ; D 플립플롭의 테스트벤치 예 reg set, reset, clock, din; dff_sr U 0_dff_sr (set, reset, clock, din, q, qb); initial begin clock = 1'b 0; forever begin #10 clock = ~clock; end initial begin forever begin din = 0; reset = 1; #15 din = 1; #30 reset = 0; #10 reset = 1; #25 din = 0; #20 set = 0; #10 set = 1; #30 din = 0; end endmodule 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung 54

- Slides: 55