Verilog HDL Quick Reference Guide Author Nikola Jevtovi

![6. Module Port Declarations • Syntax: port_direction [port_size] port_name, . . . ; • 6. Module Port Declarations • Syntax: port_direction [port_size] port_name, . . . ; •](https://slidetodoc.com/presentation_image/2658c8bf9ee0f3634f82592612ae8980/image-17.jpg)

![7. Data Type Declarations • Syntax: register_type [size] variable_name , variable_name, . . . 7. Data Type Declarations • Syntax: register_type [size] variable_name , variable_name, . . .](https://slidetodoc.com/presentation_image/2658c8bf9ee0f3634f82592612ae8980/image-18.jpg)

![8. Module Instances • Syntax: - Port Order Connections module_name instance_name [instance_array_range] (signal, . 8. Module Instances • Syntax: - Port Order Connections module_name instance_name [instance_array_range] (signal, .](https://slidetodoc.com/presentation_image/2658c8bf9ee0f3634f82592612ae8980/image-23.jpg)

![9. Primitive Instances • Syntax - Gate Type gate_type (drive_strength) #(delay) instance_name [instance_array_range] (terminal, 9. Primitive Instances • Syntax - Gate Type gate_type (drive_strength) #(delay) instance_name [instance_array_range] (terminal,](https://slidetodoc.com/presentation_image/2658c8bf9ee0f3634f82592612ae8980/image-26.jpg)

![9. Primitive Instances • Syntax - Switch Type switch_type #(delay) instance_name [instance_array_range] (terminal, . 9. Primitive Instances • Syntax - Switch Type switch_type #(delay) instance_name [instance_array_range] (terminal, .](https://slidetodoc.com/presentation_image/2658c8bf9ee0f3634f82592612ae8980/image-27.jpg)

![12. Continuous Assignments • - Syntax Explicit Continuous Assignment net_type [size] net_name; assign #(delay) 12. Continuous Assignments • - Syntax Explicit Continuous Assignment net_type [size] net_name; assign #(delay)](https://slidetodoc.com/presentation_image/2658c8bf9ee0f3634f82592612ae8980/image-40.jpg)

![14. Function Definitions • Syntax function [size_or_type] function_name; input declarations local variable declarations procedural_statement 14. Function Definitions • Syntax function [size_or_type] function_name; input declarations local variable declarations procedural_statement](https://slidetodoc.com/presentation_image/2658c8bf9ee0f3634f82592612ae8980/image-42.jpg)

- Slides: 49

Verilog HDL Quick Reference Guide Author: Nikola Jevtović Computer Science Department School of Electrical Engineering University of Belgrade email: jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide

Reference On-line Verilog HDL Quick Reference Guide by Stuart Sutherland of Sutherland HDL, Inc. - Portland, Oregon, USA http: //www. sutherland-hdl. com/ jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 2

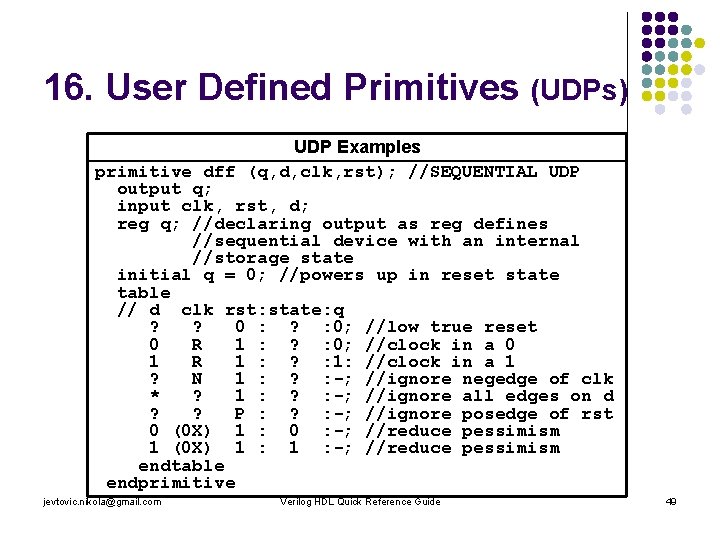

Verilog HDL Quick Reference Guide 1. Hierarchy Scopes 2. Concurrency 3. Reserved Keywords 4. Lexical Conventions 5. Module Definitions 6. Module Port Declarations 7. Data Type Declarations 8. Module Instances jevtovic. nikola@gmail. com 9. Primitive Instances 10. Procedural Blocks 11. Operators 12. Continuous Assignments 13. Task Definitions 14. Function Definitions 15. Specify Blocks 16. User Defined Primitives Verilog HDL Quick Reference Guide 3

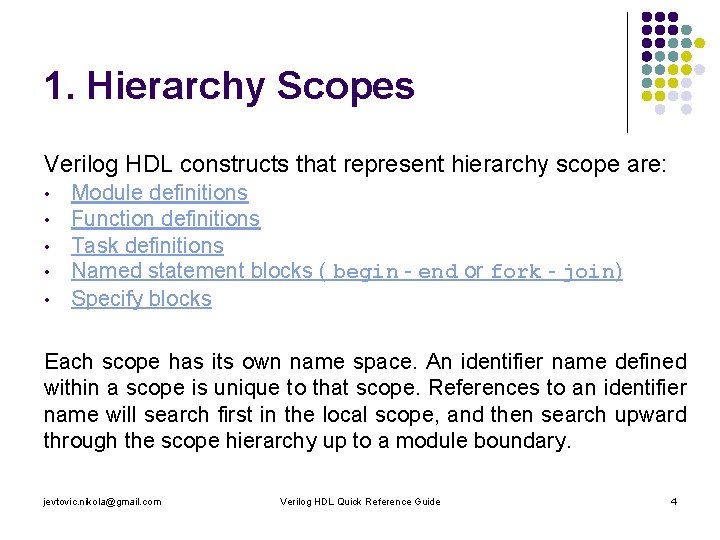

1. Hierarchy Scopes Verilog HDL constructs that represent hierarchy scope are: • • • Module definitions Function definitions Task definitions Named statement blocks ( begin - end or fork - join) Specify blocks Each scope has its own name space. An identifier name defined within a scope is unique to that scope. References to an identifier name will search first in the local scope, and then search upward through the scope hierarchy up to a module boundary. jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 4

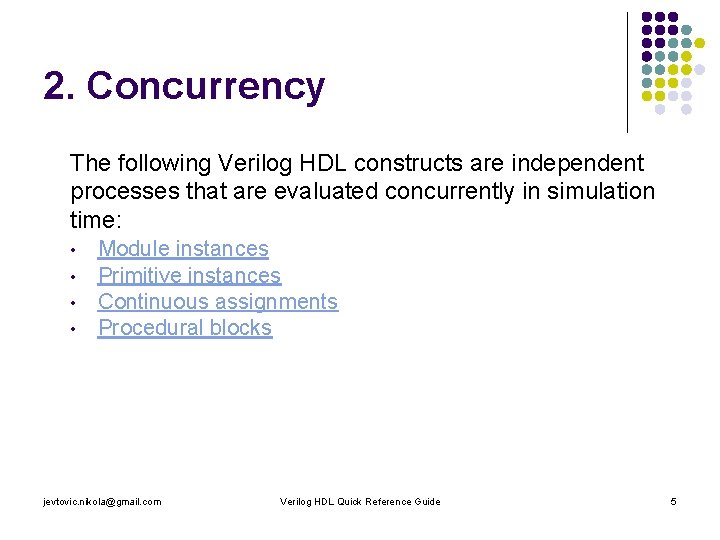

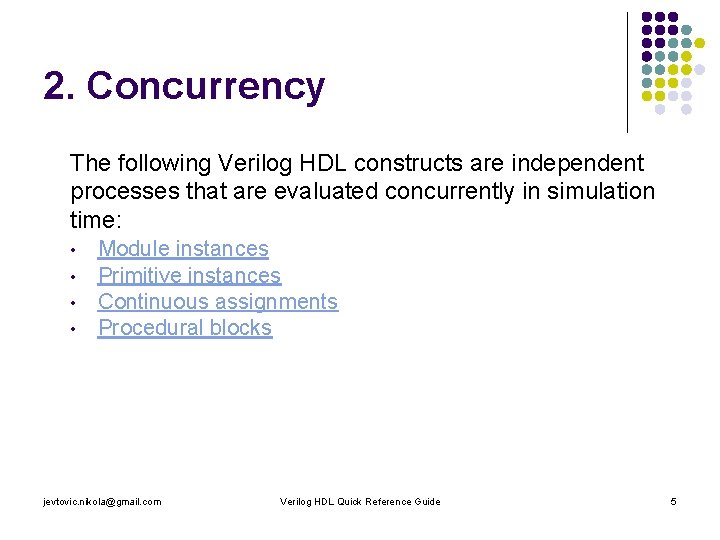

2. Concurrency The following Verilog HDL constructs are independent processes that are evaluated concurrently in simulation time: • • Module instances Primitive instances Continuous assignments Procedural blocks jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 5

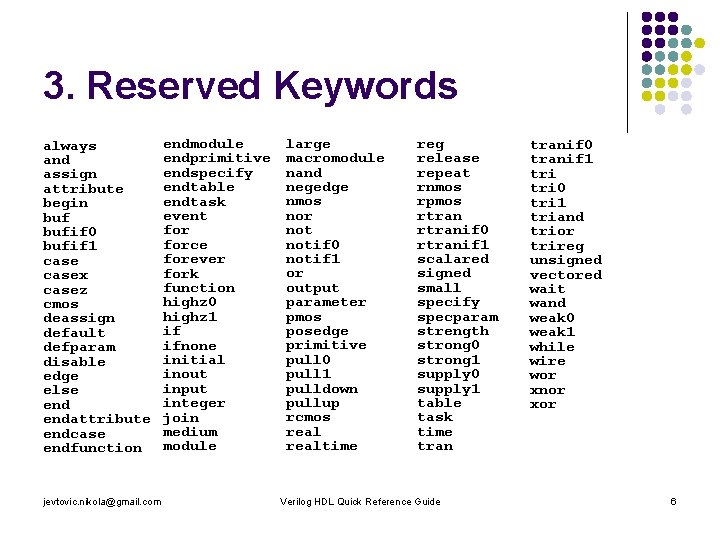

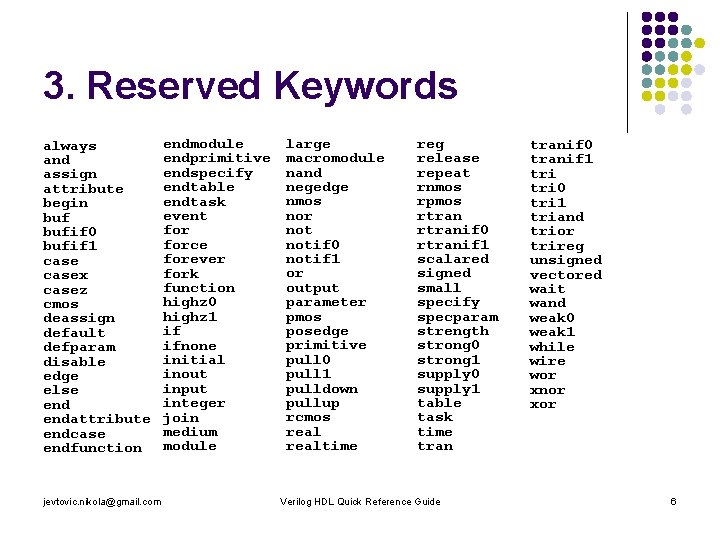

3. Reserved Keywords always and assign attribute begin bufif 0 bufif 1 casex casez cmos deassign default defparam disable edge else endattribute endcase endfunction jevtovic. nikola@gmail. com endmodule endprimitive endspecify endtable endtask event force forever fork function highz 0 highz 1 if ifnone initial inout input integer join medium module large macromodule nand negedge nmos nor notif 0 notif 1 or output parameter pmos posedge primitive pull 0 pull 1 pulldown pullup rcmos realtime reg release repeat rnmos rpmos rtranif 0 rtranif 1 scalared signed small specify specparam strength strong 0 strong 1 supply 0 supply 1 table task time tran Verilog HDL Quick Reference Guide tranif 0 tranif 1 tri 0 tri 1 triand trior trireg unsigned vectored wait wand weak 0 weak 1 while wire wor xnor xor 6

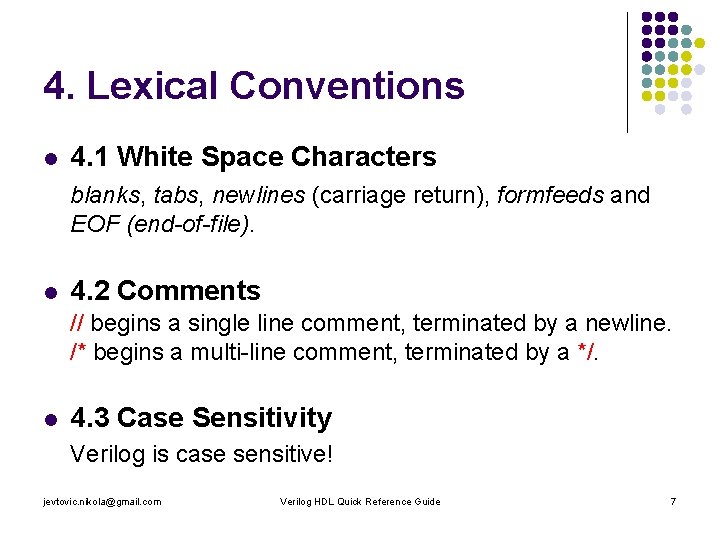

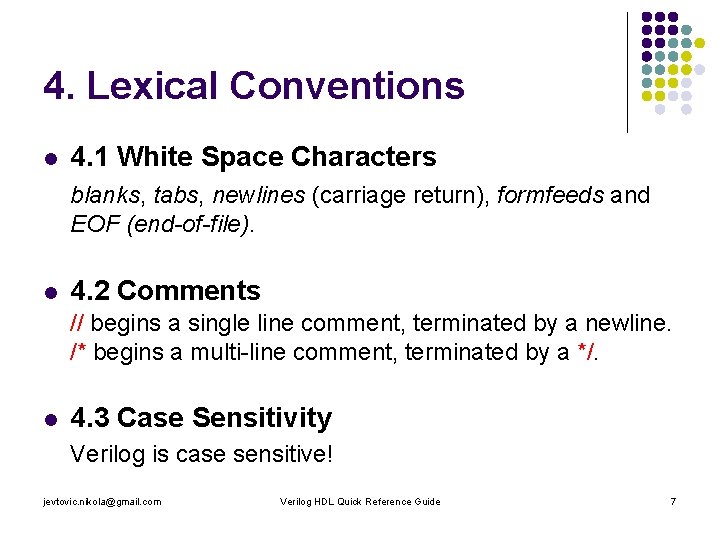

4. Lexical Conventions l 4. 1 White Space Characters blanks, tabs, newlines (carriage return), formfeeds and EOF (end-of-file). l 4. 2 Comments // begins a single line comment, terminated by a newline. /* begins a multi-line comment, terminated by a */. l 4. 3 Case Sensitivity Verilog is case sensitive! jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 7

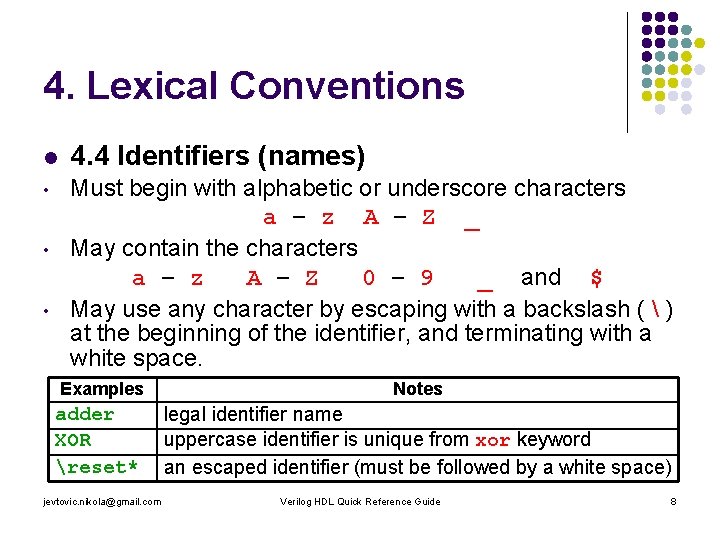

4. Lexical Conventions l 4. 4 Identifiers (names) • Must begin with alphabetic or underscore characters a – z A – Z _ May contain the characters a – z A – Z 0 – 9 _ and $ May use any character by escaping with a backslash ( ) at the beginning of the identifier, and terminating with a white space. • • Examples Notes adder XOR reset* legal identifier name uppercase identifier is unique from xor keyword an escaped identifier (must be followed by a white space) jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 8

4. Lexical Conventions l 4. 5 Logic Values • The Verilog HDL has 4 logic values: Logic Value Description 0 zero, low, or false 1 one, high, or true z or Z high impedance (tri-stated or floating) x or X unknown or uninitialized jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 9

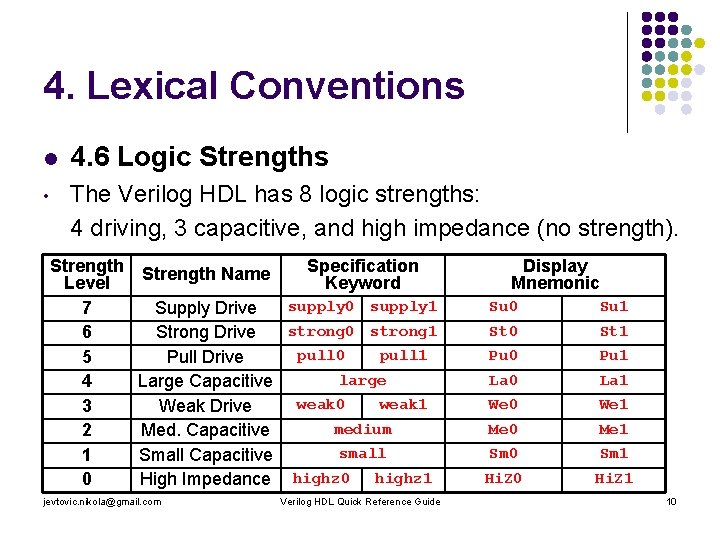

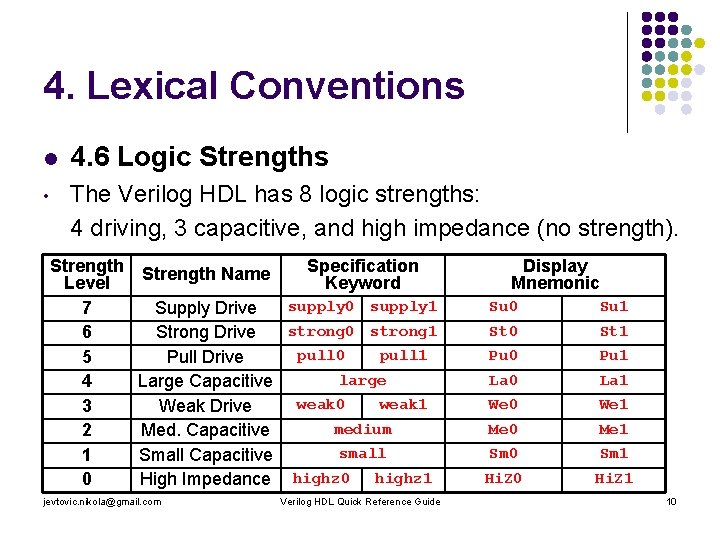

4. Lexical Conventions l 4. 6 Logic Strengths • The Verilog HDL has 8 logic strengths: 4 driving, 3 capacitive, and high impedance (no strength). Strength Level 7 6 5 4 3 2 1 0 Strength Name Specification Keyword supply 0 supply 1 Supply Drive strong 0 strong 1 Strong Drive pull 0 pull 1 Pull Drive large Large Capacitive weak 0 weak 1 Weak Drive medium Med. Capacitive small Small Capacitive High Impedance highz 0 highz 1 jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide Display Mnemonic Su 0 Su 1 St 0 St 1 Pu 0 Pu 1 La 0 La 1 We 0 We 1 Me 0 Me 1 Sm 0 Sm 1 Hi. Z 0 Hi. Z 1 10

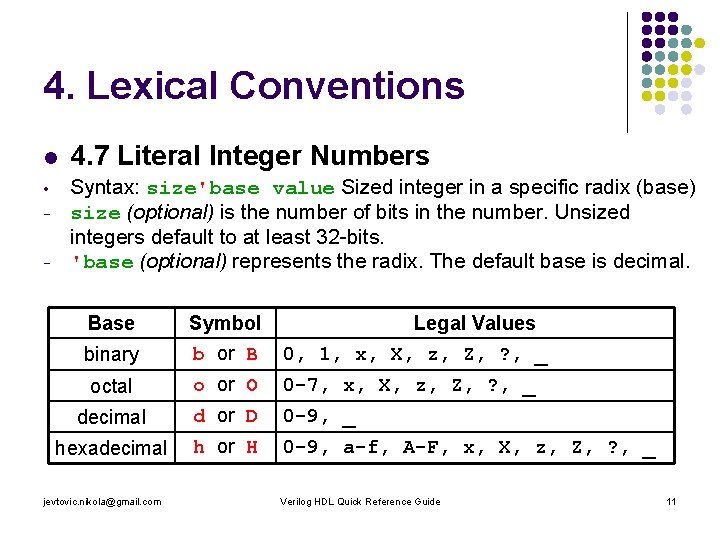

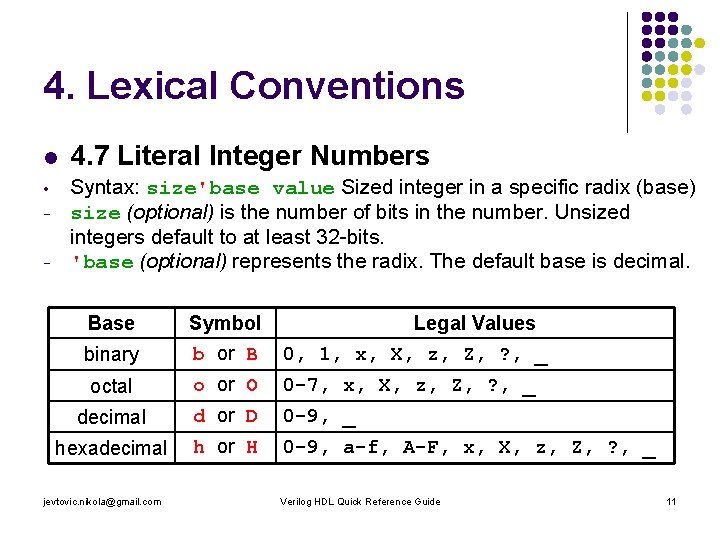

4. Lexical Conventions l 4. 7 Literal Integer Numbers • Syntax: size'base value Sized integer in a specific radix (base) size (optional) is the number of bits in the number. Unsized integers default to at least 32 -bits. 'base (optional) represents the radix. The default base is decimal. - Base binary Symbol b or B Legal Values 0, 1, x, X, z, Z, ? , _ octal o or O 0 -7, x, X, z, Z, ? , _ decimal d or D 0 -9, _ hexadecimal h or H 0 -9, a-f, A-F, x, X, z, Z, ? , _ jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 11

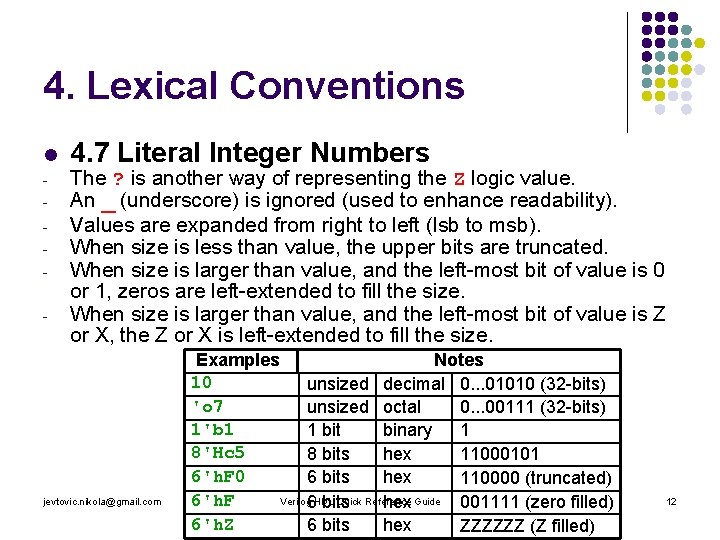

4. Lexical Conventions l - 4. 7 Literal Integer Numbers The ? is another way of representing the Z logic value. An _ (underscore) is ignored (used to enhance readability). Values are expanded from right to left (lsb to msb). When size is less than value, the upper bits are truncated. When size is larger than value, and the left-most bit of value is 0 or 1, zeros are left-extended to fill the size. When size is larger than value, and the left-most bit of value is Z or X, the Z or X is left-extended to fill the size. jevtovic. nikola@gmail. com Examples Notes 10 unsized decimal 0. . . 01010 (32 -bits) 'o 7 unsized octal 0. . . 00111 (32 -bits) 1'b 1 1 bit binary 1 8'Hc 5 8 bits hex 11000101 6'h. F 0 6 bits hex 110000 (truncated) Verilog 6 HDL Quick Reference 6'h. F bits hex Guide 001111 (zero filled) 6'h. Z 6 bits hex ZZZZZZ (Z filled) 12

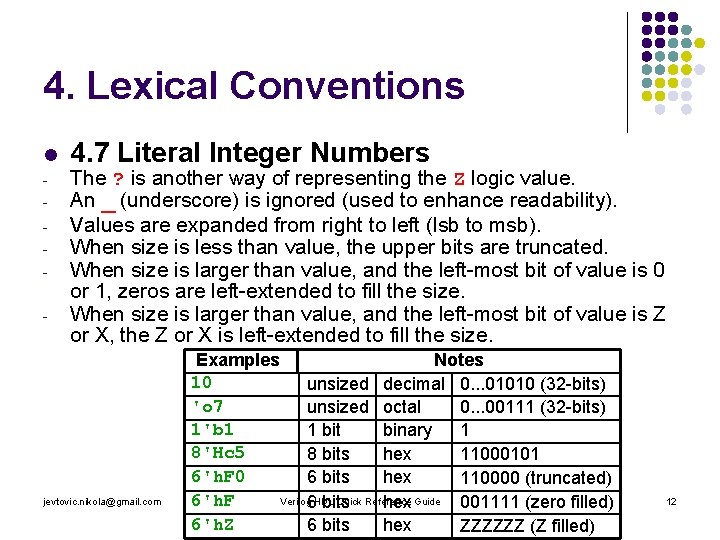

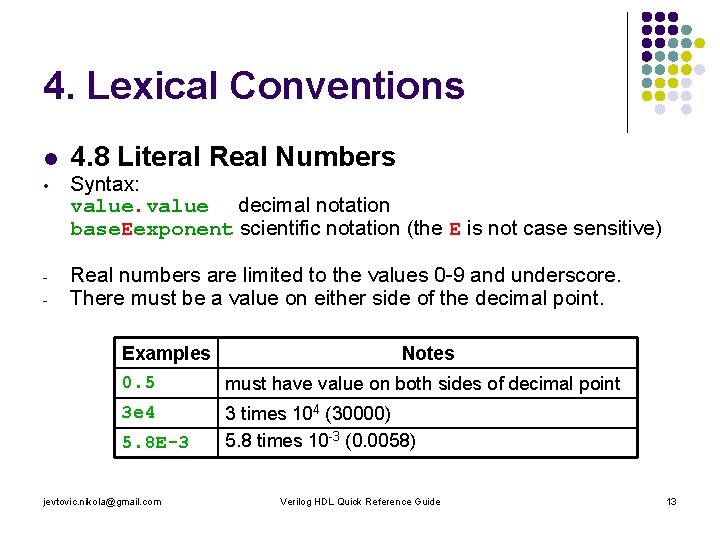

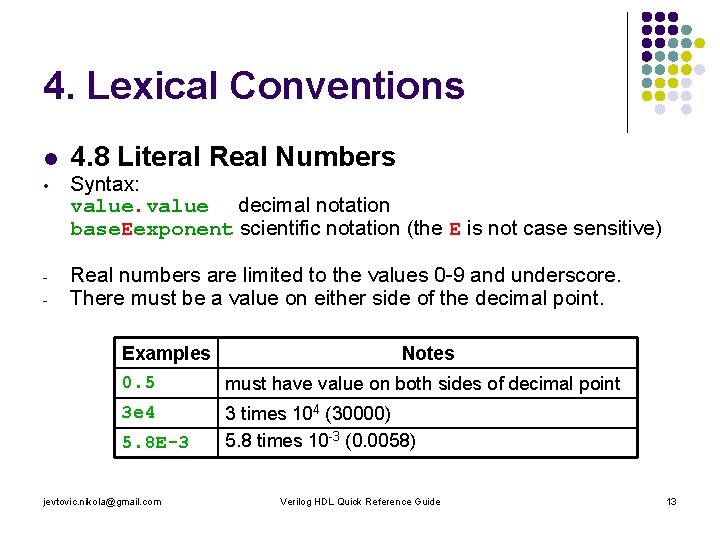

4. Lexical Conventions l 4. 8 Literal Real Numbers • Syntax: value decimal notation base. Eexponent scientific notation (the E is not case sensitive) - Real numbers are limited to the values 0 -9 and underscore. There must be a value on either side of the decimal point. Examples Notes 0. 5 must have value on both sides of decimal point 3 e 4 3 times 104 (30000) 5. 8 E-3 jevtovic. nikola@gmail. com 5. 8 times 10 -3 (0. 0058) Verilog HDL Quick Reference Guide 13

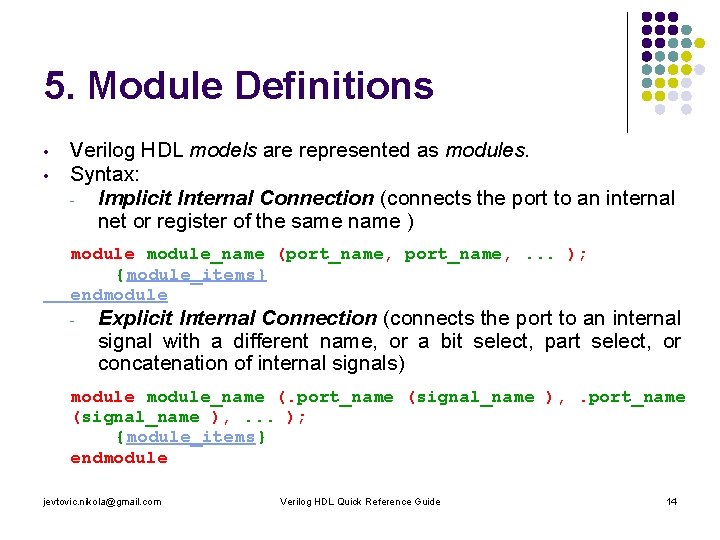

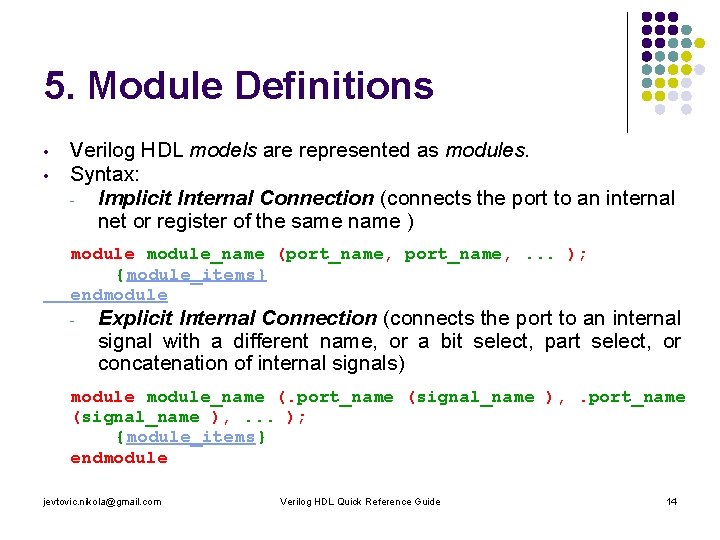

5. Module Definitions • • Verilog HDL models are represented as modules. Syntax: - Implicit Internal Connection (connects the port to an internal net or register of the same name ) module_name (port_name, . . . ); {module_items} endmodule - Explicit Internal Connection (connects the port to an internal signal with a different name, or a bit select, part select, or concatenation of internal signals) module_name (. port_name (signal_name ), . . . ); {module_items} endmodule jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 14

5. Module Definitions • - module_items are: module port declarations data type declarations module instances primitive instances procedural blocks continuous assignments task definitions function definitions specify blocks jevtovic. nikola@gmail. com • Module functionality may be: - Behavioral - modeled with procedural blocks or continuous assignment statements. - Structural - modeled as a netlist of module instances or primitive instances. - A combination of behavioral and structural. Verilog HDL Quick Reference Guide 15

5. Module Definitions l l l Module definitions may not be nested. Instead, modules instantiate other modules. Module definitions may be expressed using parameter constants. Each instance of a module may redefine the parameters to be unique to that instance. Module items may appear in any order, but port declarations and data type declarations should be listed before the ports or signals are referenced. jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 16

![6 Module Port Declarations Syntax portdirection portsize portname 6. Module Port Declarations • Syntax: port_direction [port_size] port_name, . . . ; •](https://slidetodoc.com/presentation_image/2658c8bf9ee0f3634f82592612ae8980/image-17.jpg)

6. Module Port Declarations • Syntax: port_direction [port_size] port_name, . . . ; • port_direction is declared as: - input for scalar or vector input ports. - output for scalar or vector output ports. - inout for scalar or vector bi-directional ports. • port_size is a range from [ msb : lsb ] Examples Notes input a, b, sel; output [7: 0] result; inout [0: 15] data_bus; input [15: 12] addr; parameter word = 32; input [word-1: 0] addr; 3 scalar ports little endian convention big endian convention msb: lsb may be any integer constant expressions may be used jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 17

![7 Data Type Declarations Syntax registertype size variablename variablename 7. Data Type Declarations • Syntax: register_type [size] variable_name , variable_name, . . .](https://slidetodoc.com/presentation_image/2658c8bf9ee0f3634f82592612ae8980/image-18.jpg)

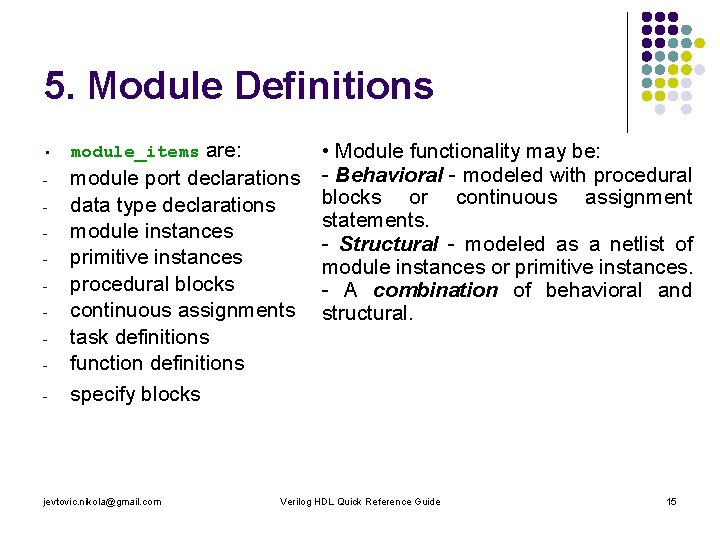

7. Data Type Declarations • Syntax: register_type [size] variable_name , variable_name, . . . ; register_type [size] memory_name [array_size]; net_type [size] #(delay) net_name , . . . ; net_type (drive_strength) [size] #(delay) net_name = continuous_assignment ; trireg (capacitance_strength) [size] #(delay, decay_time) net_name, . . . ; parameter constant_name = value, . . . ; specparam constant_name = value, . . . ; event_name, . . . ; • delay (optional) may only be specified on net data types. • size is a range from [msb : lsb]. • array_size is from [ first_address : last_address] • strength (opt. ) specified as (strength 1, strength 0) or _(strength 0, strength 1) • decay_time (opt. ) The syntax is (rise_delay, fall_delay, decay_time) jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 18

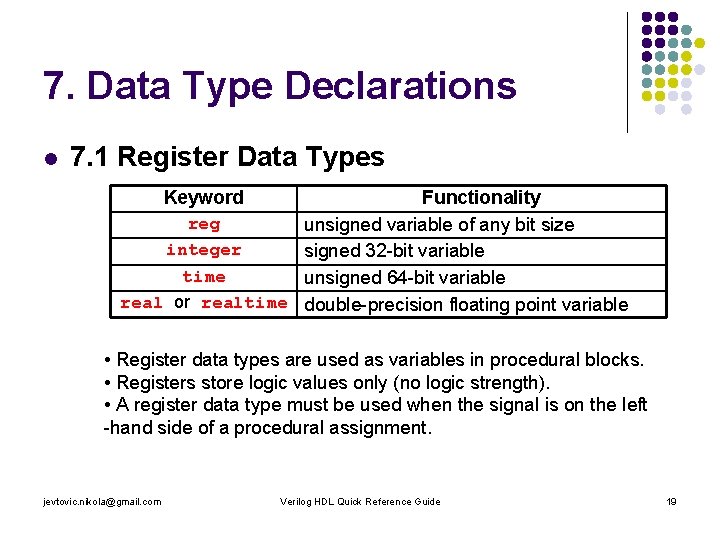

7. Data Type Declarations l 7. 1 Register Data Types Keyword Functionality reg unsigned variable of any bit size integer signed 32 -bit variable time unsigned 64 -bit variable real or realtime double-precision floating point variable • Register data types are used as variables in procedural blocks. • Registers store logic values only (no logic strength). • A register data type must be used when the signal is on the left -hand side of a procedural assignment. jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 19

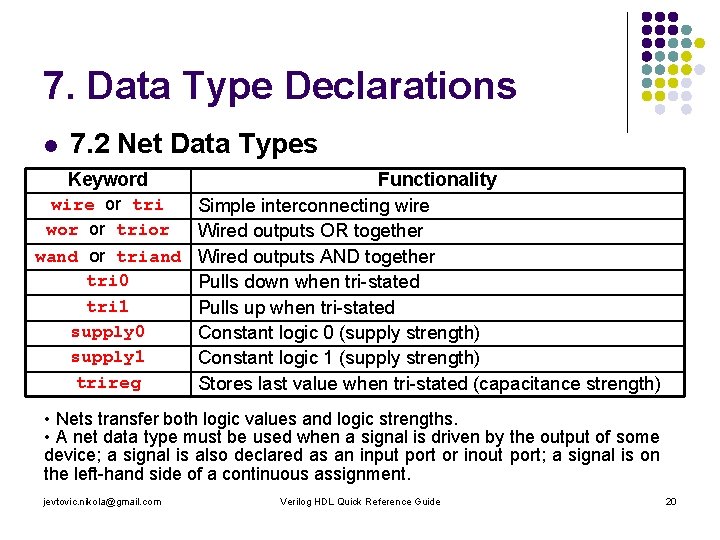

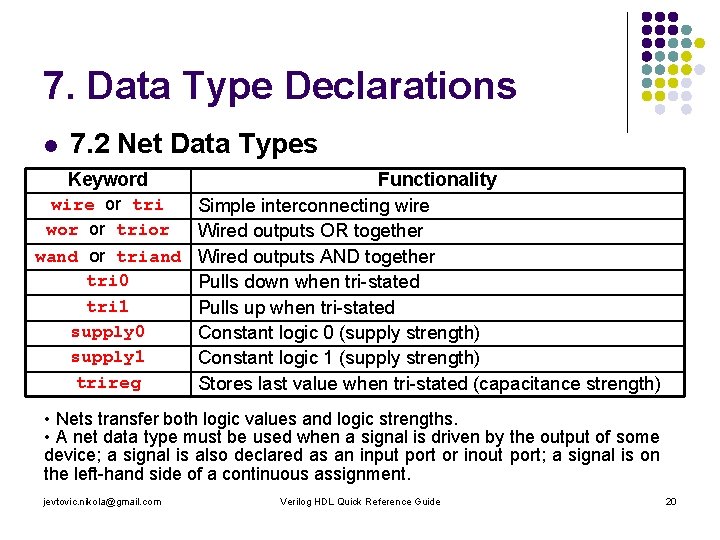

7. Data Type Declarations l 7. 2 Net Data Types Keyword Functionality wire or tri Simple interconnecting wire wor or trior Wired outputs OR together wand or triand Wired outputs AND together tri 0 Pulls down when tri-stated tri 1 Pulls up when tri-stated supply 0 Constant logic 0 (supply strength) supply 1 Constant logic 1 (supply strength) trireg Stores last value when tri-stated (capacitance strength) • Nets transfer both logic values and logic strengths. • A net data type must be used when a signal is driven by the output of some device; a signal is also declared as an input port or inout port; a signal is on the left-hand side of a continuous assignment. jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 20

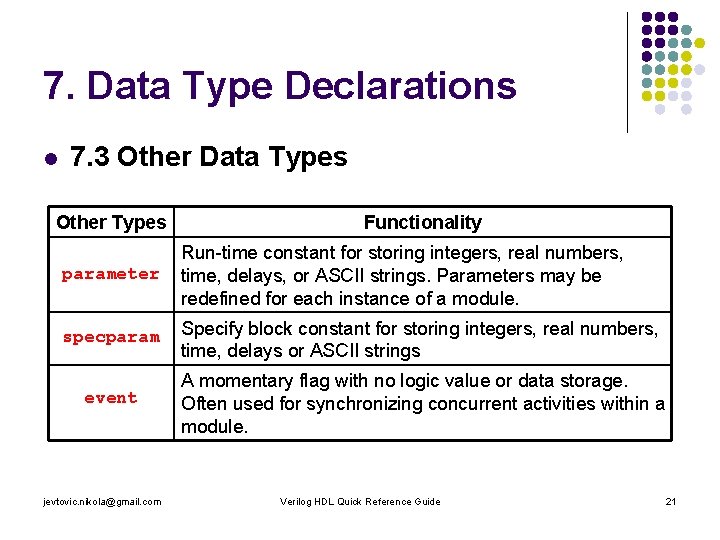

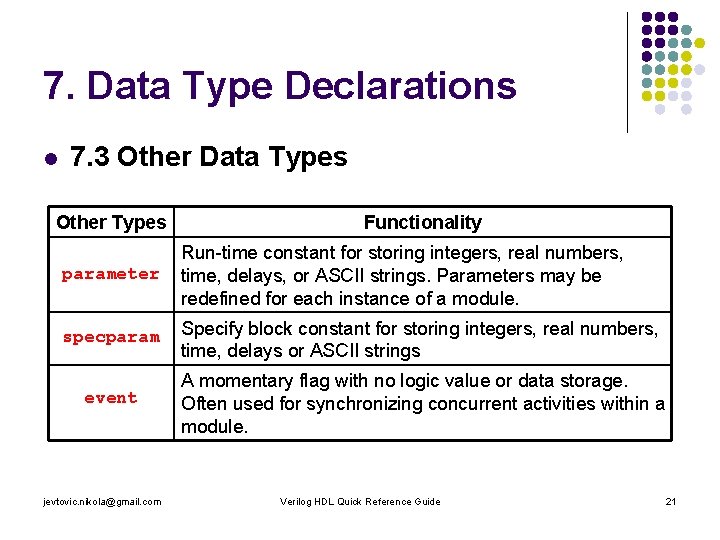

7. Data Type Declarations l 7. 3 Other Data Types Other Types Functionality parameter Run-time constant for storing integers, real numbers, time, delays, or ASCII strings. Parameters may be redefined for each instance of a module. specparam Specify block constant for storing integers, real numbers, time, delays or ASCII strings event A momentary flag with no logic value or data storage. Often used for synchronizing concurrent activities within a module. jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 21

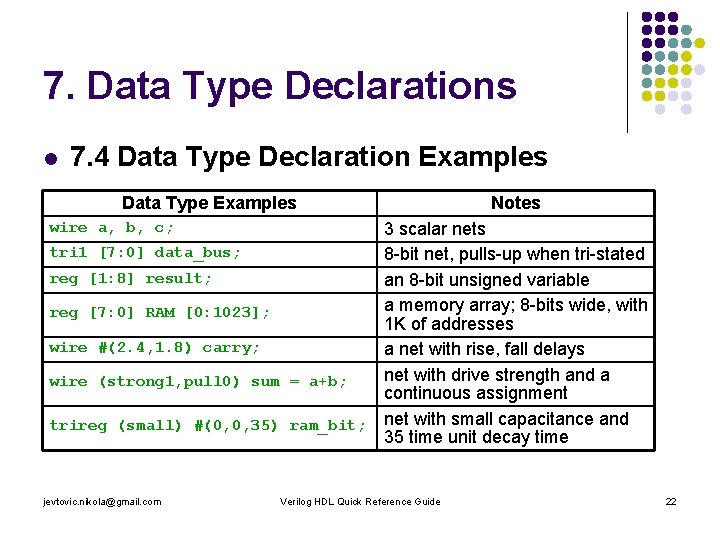

7. Data Type Declarations l 7. 4 Data Type Declaration Examples Data Type Examples Notes 3 scalar nets tri 1 [7: 0] data_bus; 8 -bit net, pulls-up when tri-stated reg [1: 8] result; an 8 -bit unsigned variable a memory array; 8 -bits wide, with reg [7: 0] RAM [0: 1023]; 1 K of addresses wire #(2. 4, 1. 8) carry; a net with rise, fall delays net with drive strength and a wire (strong 1, pull 0) sum = a+b; continuous assignment trireg (small) #(0, 0, 35) ram_bit; net with small capacitance and 35 time unit decay time wire a, b, c; jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 22

![8 Module Instances Syntax Port Order Connections modulename instancename instancearrayrange signal 8. Module Instances • Syntax: - Port Order Connections module_name instance_name [instance_array_range] (signal, .](https://slidetodoc.com/presentation_image/2658c8bf9ee0f3634f82592612ae8980/image-23.jpg)

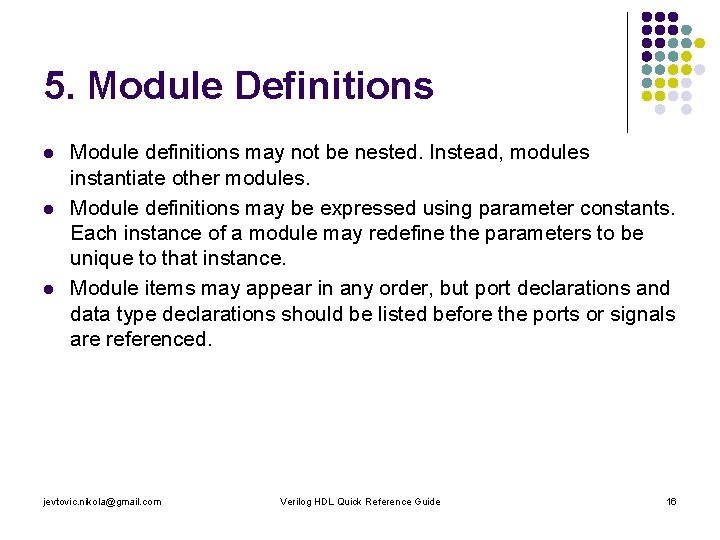

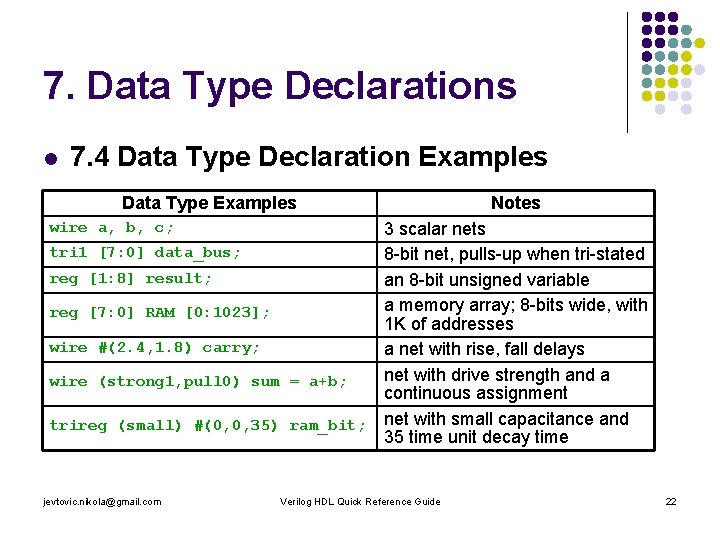

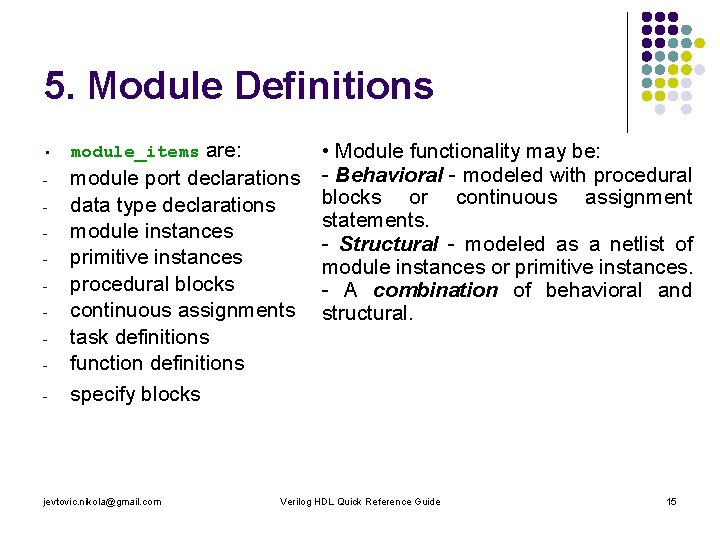

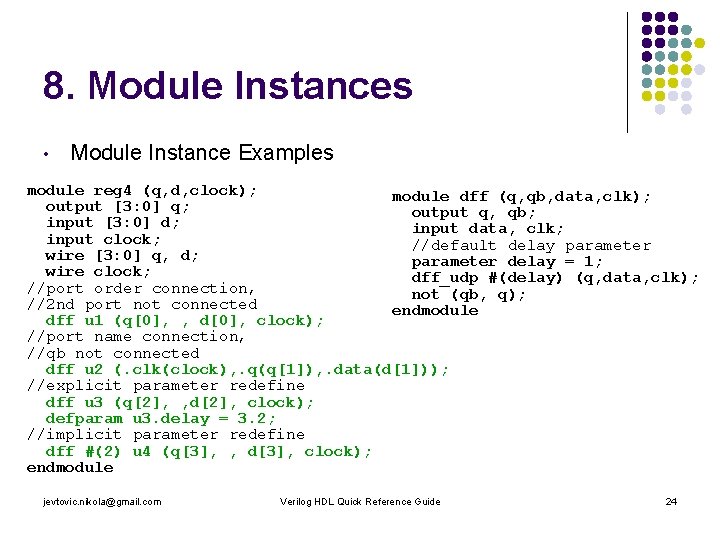

8. Module Instances • Syntax: - Port Order Connections module_name instance_name [instance_array_range] (signal, . . . ); - Port Name Connections module_name instance_name [instance_array_range] (. port_name(signal), . . . ); - Explicit Parameter Redefinition defparam heirarchy_path. parameter_name = value; - Implicit Parameter Redefinition module_name #(value) instance_name (signals); • instance_name (required) is used to make multiple instances of the same module unique from one another. • instance_array_range (optional) instantiates multiple modules, each instance connected to separate bits of a vector. jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 23

8. Module Instances • Module Instance Examples module reg 4 (q, d, clock); module dff (q, qb, data, clk); output [3: 0] q; output q, qb; input [3: 0] d; input data, clk; input clock; //default delay parameter wire [3: 0] q, d; parameter delay = 1; wire clock; dff_udp #(delay) (q, data, clk); //port order connection, not (qb, q); //2 nd port not connected endmodule dff u 1 (q[0], , d[0], clock); //port name connection, //qb not connected dff u 2 (. clk(clock), . q(q[1]), . data(d[1])); //explicit parameter redefine dff u 3 (q[2], , d[2], clock); defparam u 3. delay = 3. 2; //implicit parameter redefine dff #(2) u 4 (q[3], , d[3], clock); endmodule jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 24

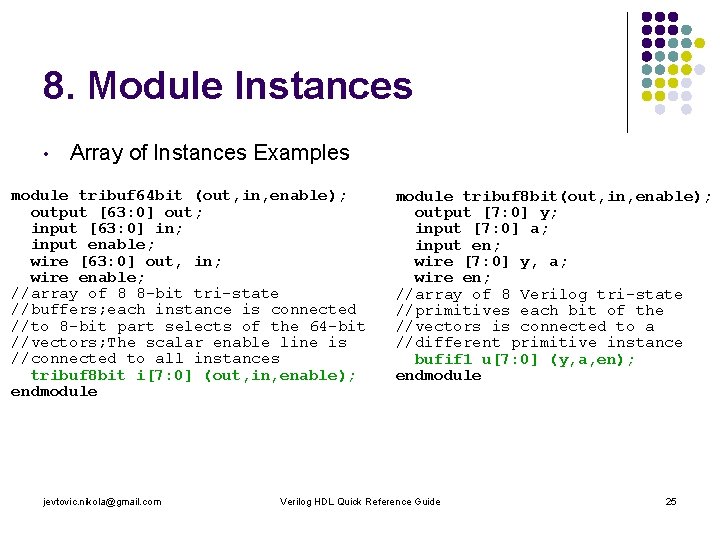

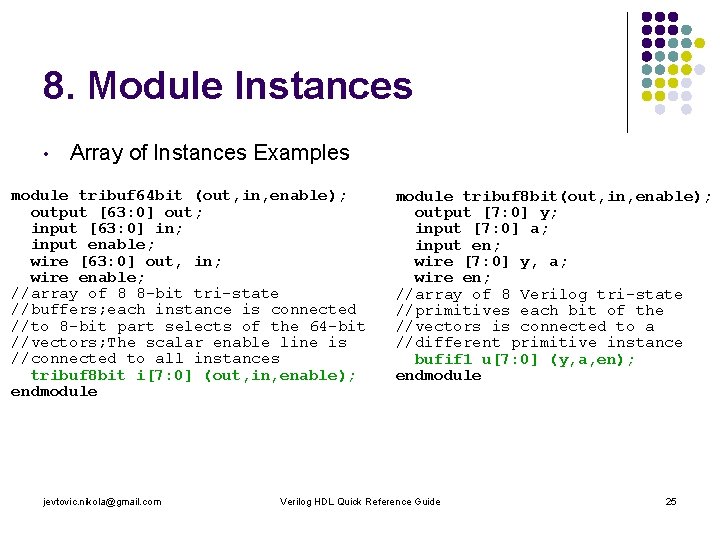

8. Module Instances • Array of Instances Examples module tribuf 64 bit (out, in, enable); output [63: 0] out; input [63: 0] in; input enable; wire [63: 0] out, in; wire enable; //array of 8 8 -bit tri-state //buffers; each instance is connected //to 8 -bit part selects of the 64 -bit //vectors; The scalar enable line is //connected to all instances tribuf 8 bit i[7: 0] (out, in, enable); endmodule jevtovic. nikola@gmail. com module tribuf 8 bit(out, in, enable); output [7: 0] y; input [7: 0] a; input en; wire [7: 0] y, a; wire en; //array of 8 Verilog tri-state //primitives each bit of the //vectors is connected to a //different primitive instance bufif 1 u[7: 0] (y, a, en); endmodule Verilog HDL Quick Reference Guide 25

![9 Primitive Instances Syntax Gate Type gatetype drivestrength delay instancename instancearrayrange terminal 9. Primitive Instances • Syntax - Gate Type gate_type (drive_strength) #(delay) instance_name [instance_array_range] (terminal,](https://slidetodoc.com/presentation_image/2658c8bf9ee0f3634f82592612ae8980/image-26.jpg)

9. Primitive Instances • Syntax - Gate Type gate_type (drive_strength) #(delay) instance_name [instance_array_range] (terminal, . . . ); Gate Type and or xor buf nand nor xnor not bufif 0 bufif 1 pullup notif 0 notif 1 pulldown Terminal Order (1_output, 1 -or-more_inputs) (1 -or-more_outputs, 1_input) (1_output, 1_input, 1_control) user-defined-primitives jevtovic. nikola@gmail. com (1_output) (1_output, 1 -or-more_inputs) Verilog HDL Quick Reference Guide 26

![9 Primitive Instances Syntax Switch Type switchtype delay instancename instancearrayrange terminal 9. Primitive Instances • Syntax - Switch Type switch_type #(delay) instance_name [instance_array_range] (terminal, .](https://slidetodoc.com/presentation_image/2658c8bf9ee0f3634f82592612ae8980/image-27.jpg)

9. Primitive Instances • Syntax - Switch Type switch_type #(delay) instance_name [instance_array_range] (terminal, . . . ); Switch Type Terminal Order pmos nmos cmos rpmos rnmos rcmos tran rtran (1_output, 1_input, n_control, p_control) (2_bidirectional-inouts) tranif 0 rtranif 1 (2_bidirectional-inouts, 1_control) jevtovic. nikola@gmail. com (1_output, 1_input, 1_control) Verilog HDL Quick Reference Guide 27

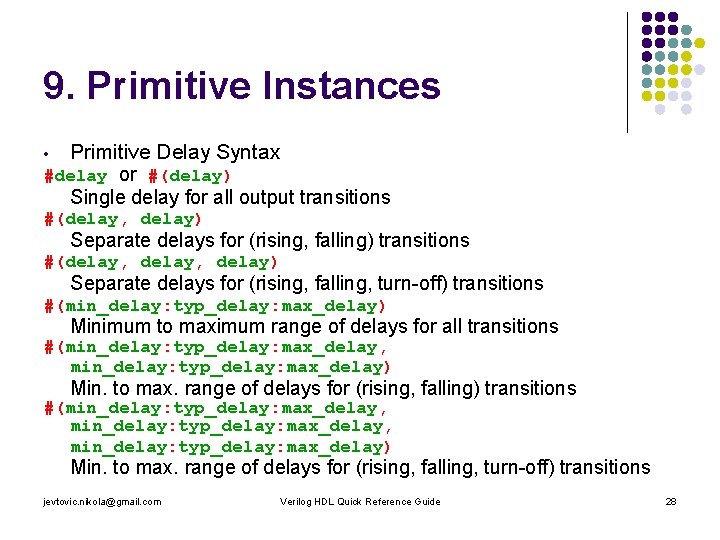

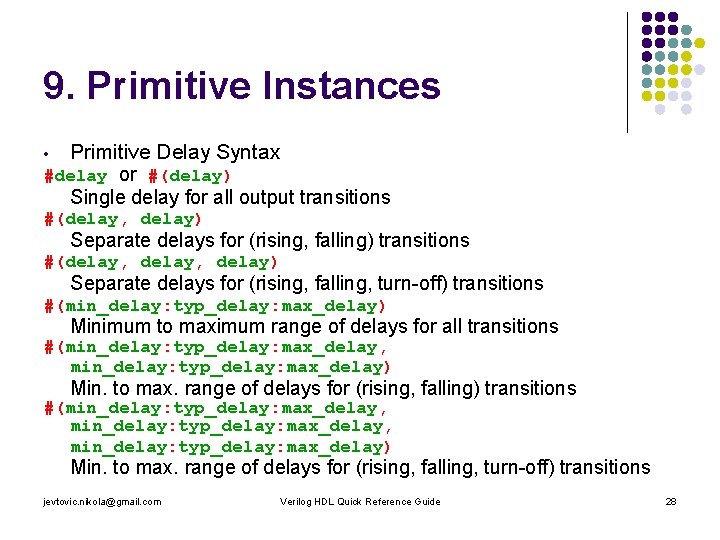

9. Primitive Instances Primitive Delay Syntax #delay or #(delay) Single delay for all output transitions • #(delay, delay) Separate delays for (rising, falling) transitions #(delay, delay) Separate delays for (rising, falling, turn-off) transitions #(min_delay: typ_delay: max_delay) Minimum to maximum range of delays for all transitions #(min_delay: typ_delay: max_delay, min_delay: typ_delay: max_delay) Min. to max. range of delays for (rising, falling) transitions #(min_delay: typ_delay: max_delay, min_delay: typ_delay: max_delay) Min. to max. range of delays for (rising, falling, turn-off) transitions jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 28

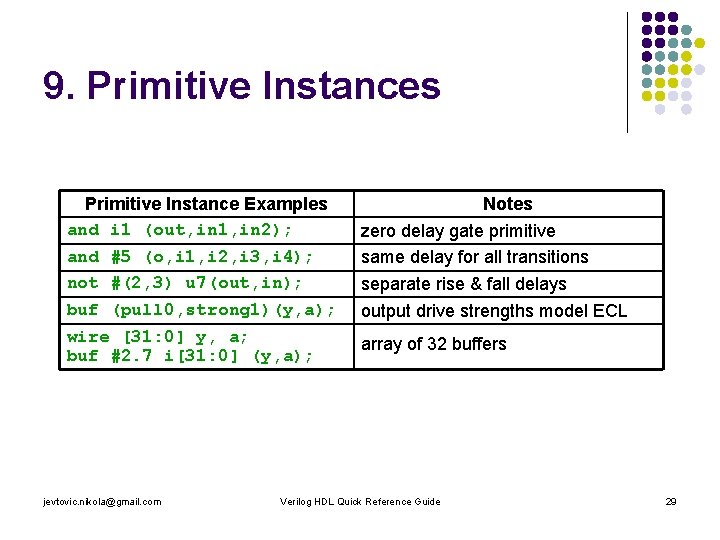

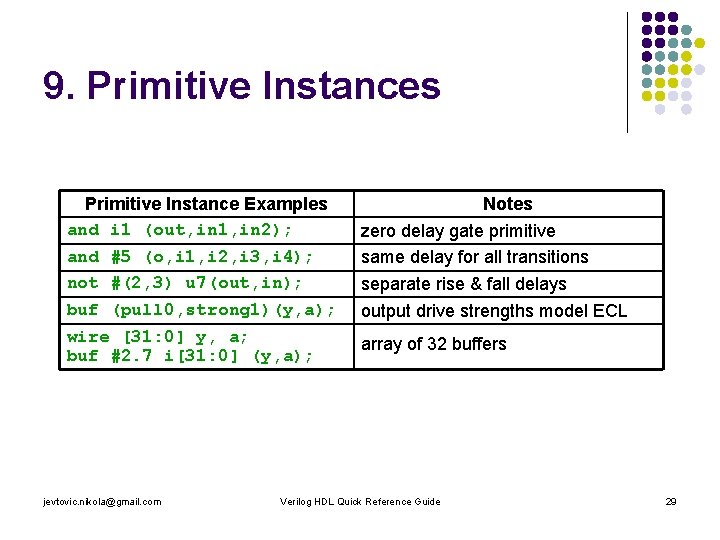

9. Primitive Instances Primitive Instance Examples and i 1 (out, in 1, in 2); and #5 (o, i 1, i 2, i 3, i 4); not #(2, 3) u 7(out, in); buf (pull 0, strong 1)(y, a); wire [31: 0] y, a; buf #2. 7 i[31: 0] (y, a); jevtovic. nikola@gmail. com Notes zero delay gate primitive same delay for all transitions separate rise & fall delays output drive strengths model ECL array of 32 buffers Verilog HDL Quick Reference Guide 29

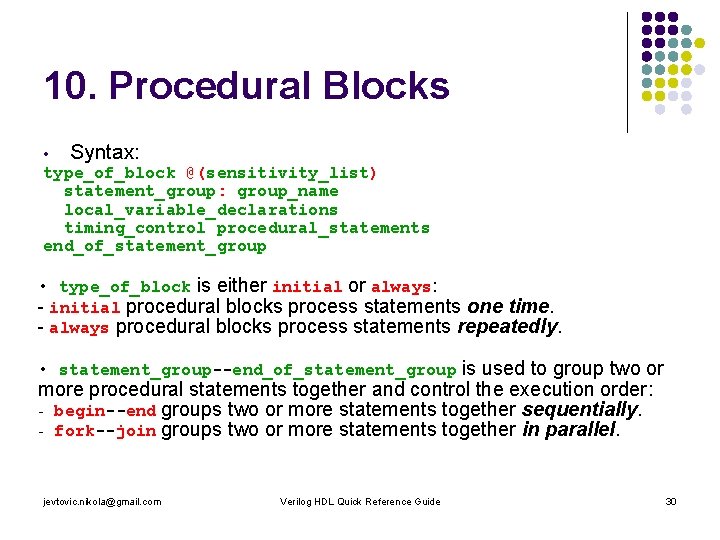

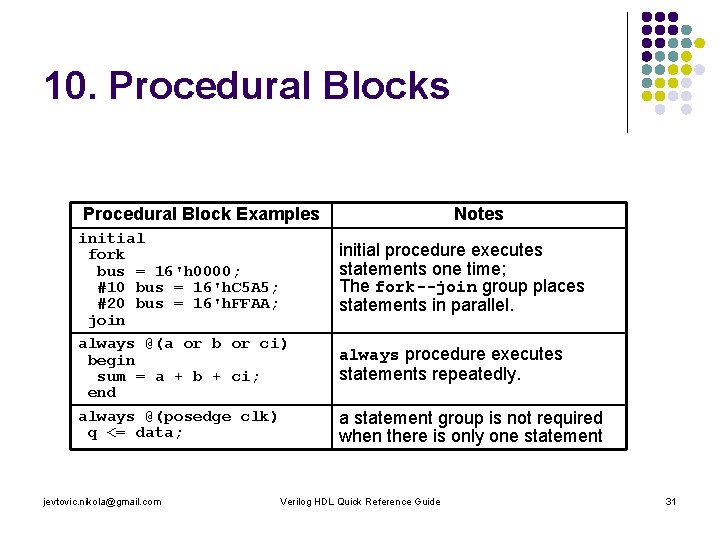

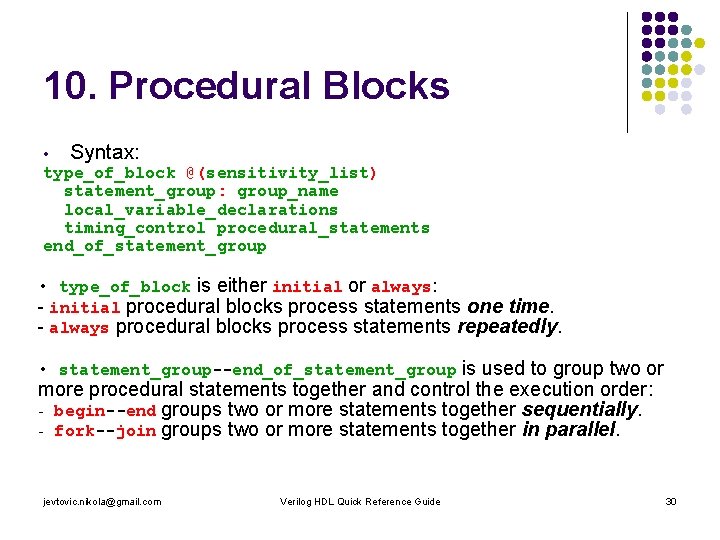

10. Procedural Blocks • Syntax: type_of_block @(sensitivity_list) statement_group: group_name local_variable_declarations timing_control procedural_statements end_of_statement_group • type_of_block is either initial or always: - initial procedural blocks process statements one time. - always procedural blocks process statements repeatedly. • statement_group--end_of_statement_group is used to group two or more procedural statements together and control the execution order: - begin--end groups two or more statements together sequentially. - fork--join groups two or more statements together in parallel. jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 30

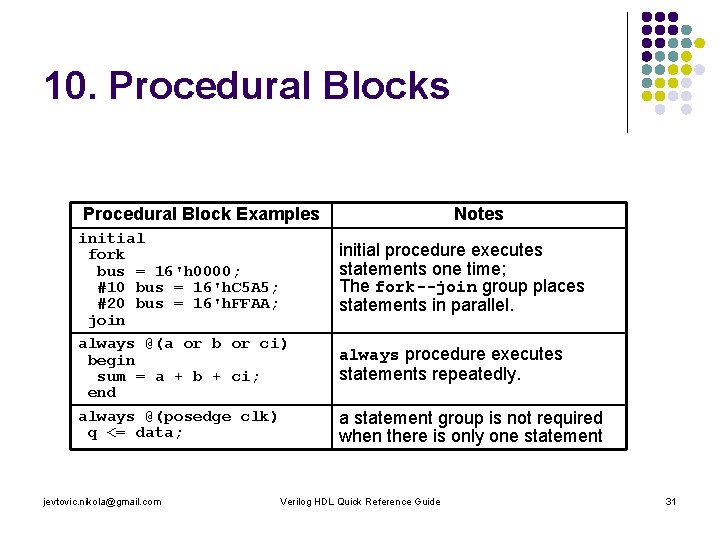

10. Procedural Blocks Procedural Block Examples initial fork bus = 16'h 0000; #10 bus = 16'h. C 5 A 5; #20 bus = 16'h. FFAA; join always @(a or b or ci) begin sum = a + b + ci; end always @(posedge clk) q <= data; jevtovic. nikola@gmail. com Notes initial procedure executes statements one time; The fork--join group places statements in parallel. always procedure executes statements repeatedly. a statement group is not required when there is only one statement Verilog HDL Quick Reference Guide 31

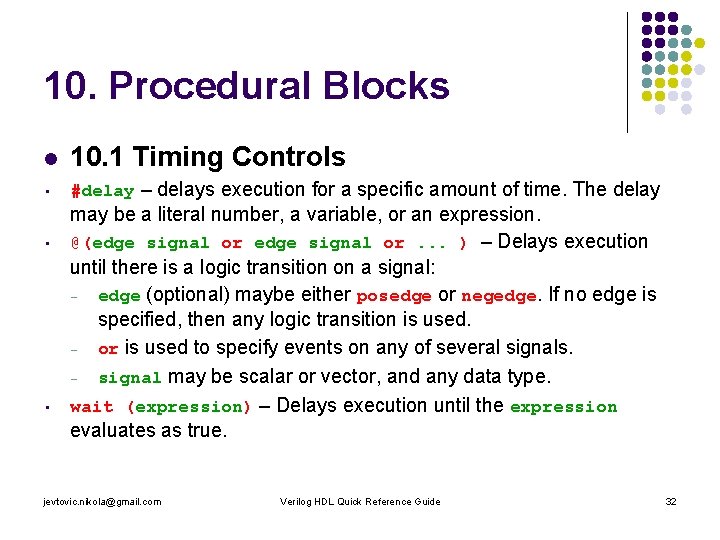

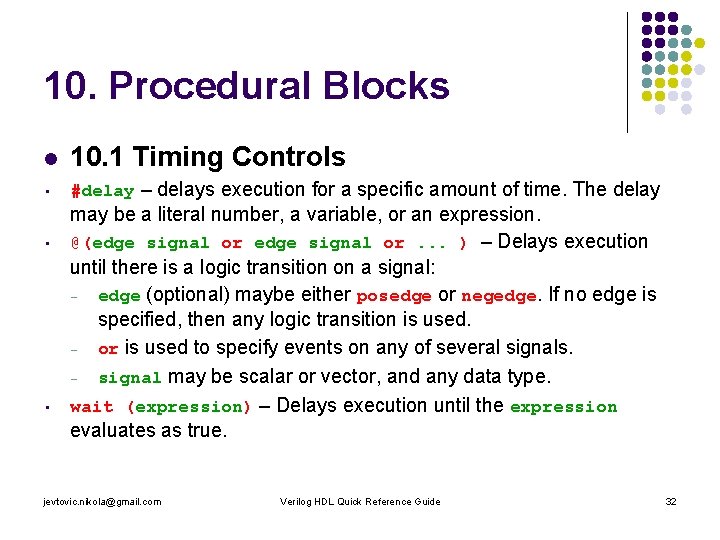

10. Procedural Blocks l 10. 1 Timing Controls • #delay – delays execution for a specific amount of time. The delay • • may be a literal number, a variable, or an expression. @(edge signal or. . . ) – Delays execution until there is a logic transition on a signal: - edge (optional) maybe either posedge or negedge. If no edge is specified, then any logic transition is used. - or is used to specify events on any of several signals. - signal may be scalar or vector, and any data type. wait (expression) – Delays execution until the expression evaluates as true. jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 32

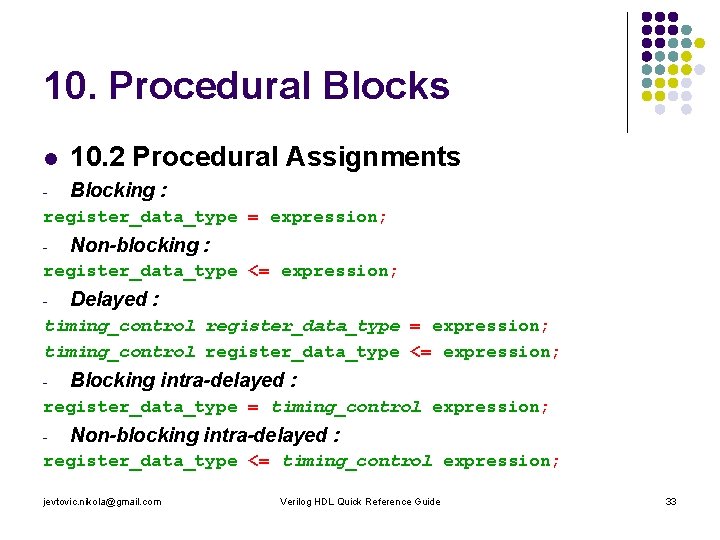

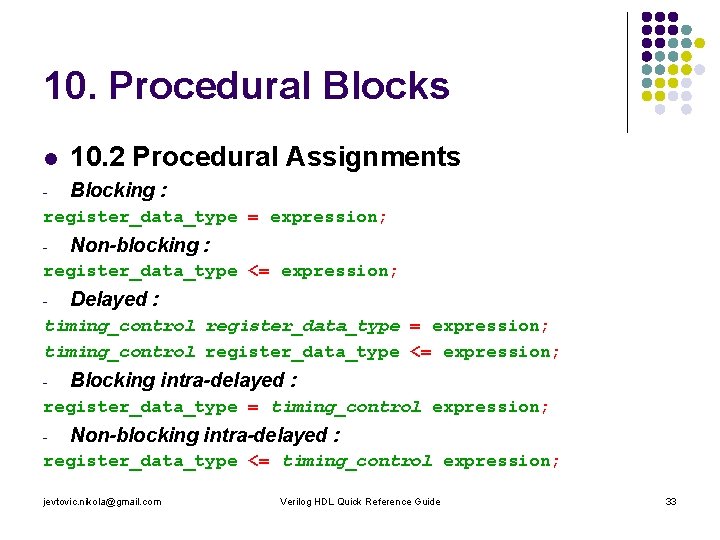

10. Procedural Blocks l 10. 2 Procedural Assignments - Blocking : register_data_type = expression; - Non-blocking : register_data_type <= expression; - Delayed : timing_control register_data_type = expression; timing_control register_data_type <= expression; - Blocking intra-delayed : register_data_type = timing_control expression; - Non-blocking intra-delayed : register_data_type <= timing_control expression; jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 33

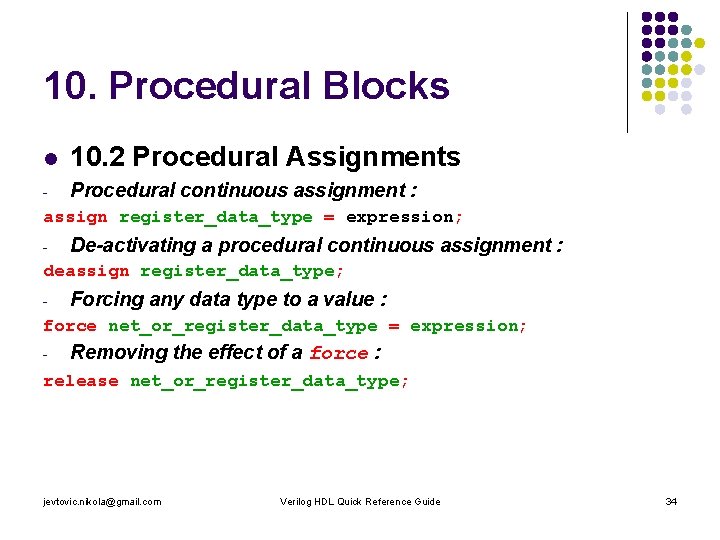

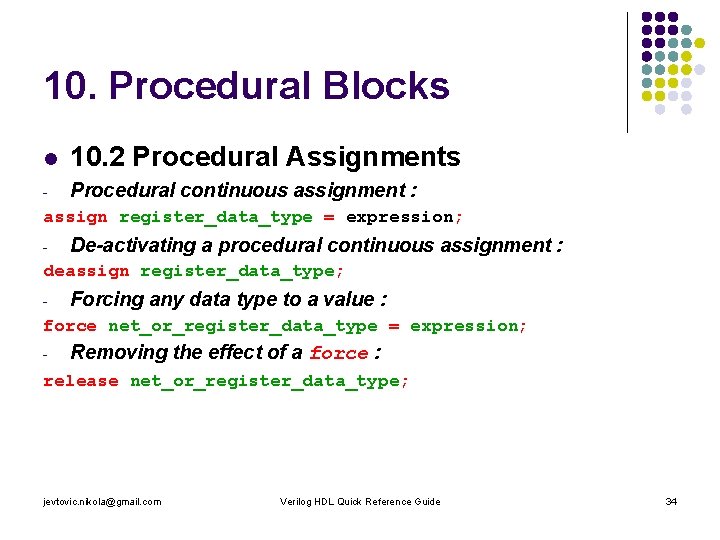

10. Procedural Blocks l 10. 2 Procedural Assignments - Procedural continuous assignment : assign register_data_type = expression; - De-activating a procedural continuous assignment : deassign register_data_type; - Forcing any data type to a value : force net_or_register_data_type = expression; - Removing the effect of a force : release net_or_register_data_type; jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 34

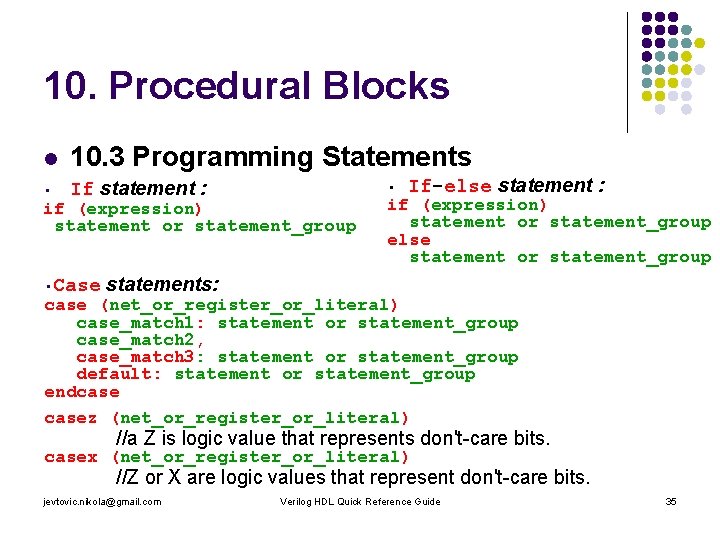

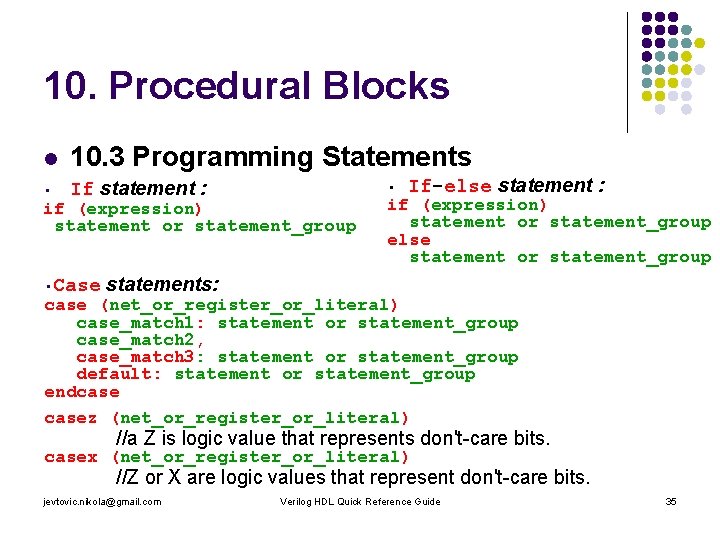

10. Procedural Blocks l 10. 3 Programming Statements • If statement : • if (expression) statement or statement_group • Case If-else statement : if (expression) statement or statement_group else statement or statement_group statements: case (net_or_register_or_literal) case_match 1: statement or statement_group case_match 2, case_match 3: statement or statement_group default: statement or statement_group endcasez (net_or_register_or_literal) //a Z is logic value that represents don't-care bits. casex (net_or_register_or_literal) //Z or X are logic values that represent don't-care bits. jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 35

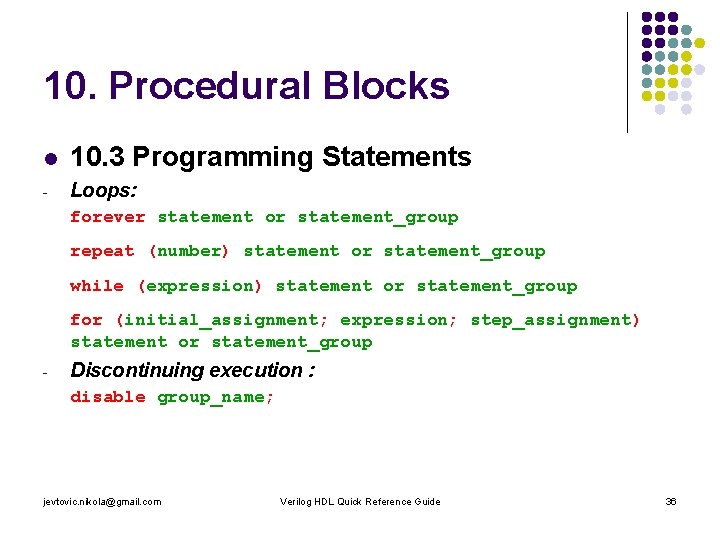

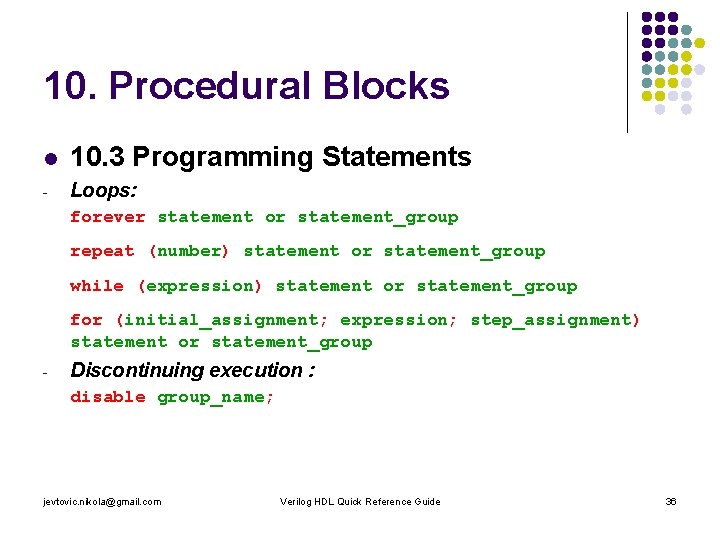

10. Procedural Blocks l 10. 3 Programming Statements - Loops: forever statement or statement_group repeat (number) statement or statement_group while (expression) statement or statement_group for (initial_assignment; expression; step_assignment) statement or statement_group - Discontinuing execution : disable group_name; jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 36

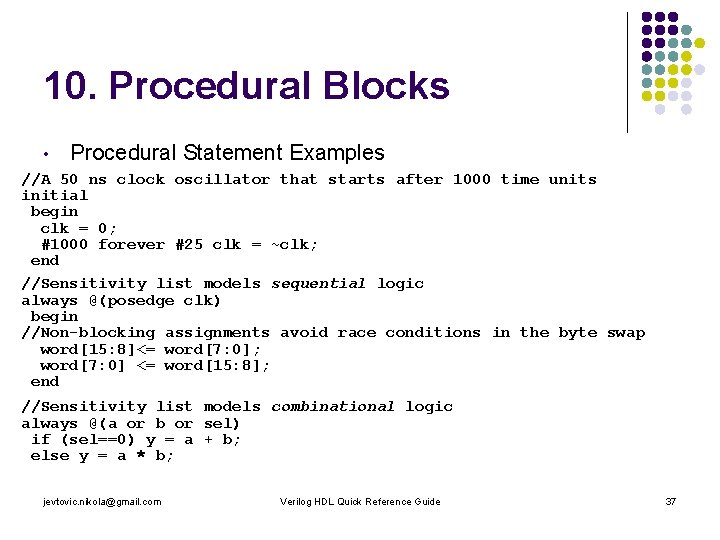

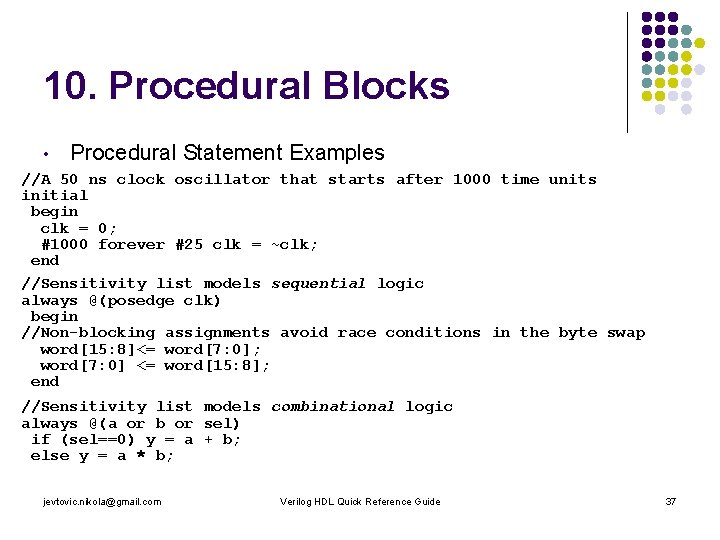

10. Procedural Blocks • Procedural Statement Examples //A 50 ns clock oscillator that starts after 1000 time units initial begin clk = 0; #1000 forever #25 clk = ~clk; end //Sensitivity list models sequential logic always @(posedge clk) begin //Non-blocking assignments avoid race conditions in the byte swap word[15: 8]<= word[7: 0]; word[7: 0] <= word[15: 8]; end //Sensitivity list models combinational logic always @(a or b or sel) if (sel==0) y = a + b; else y = a * b; jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 37

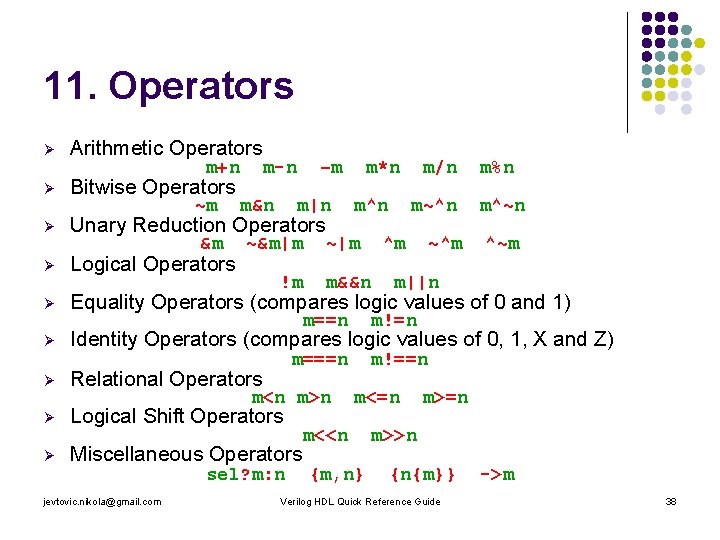

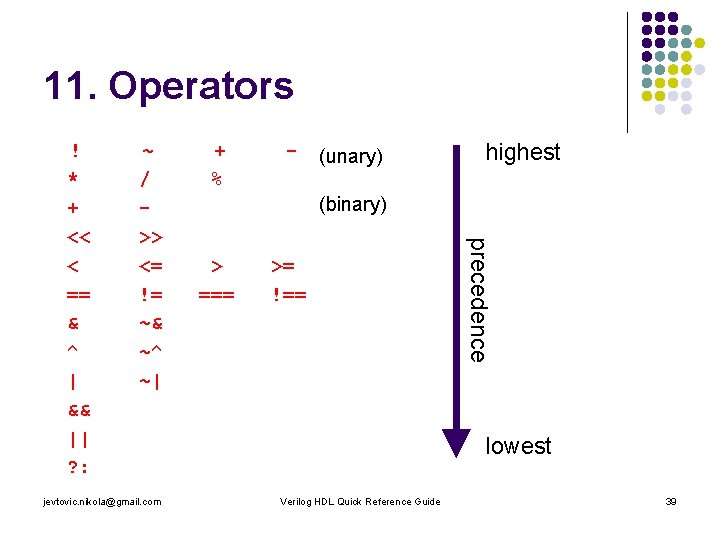

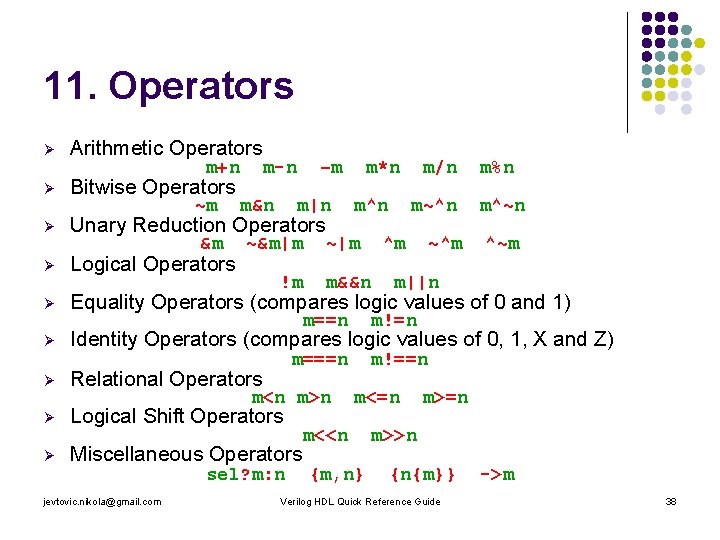

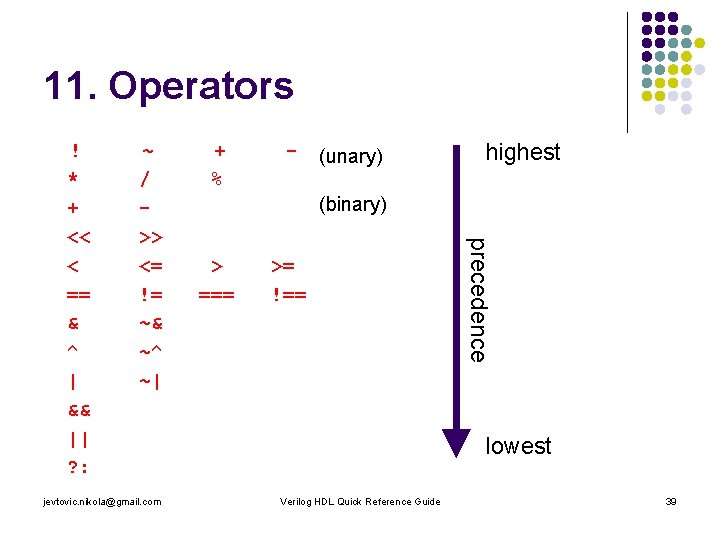

11. Operators Ø Arithmetic Operators Ø Bitwise Operators Ø Unary Reduction Operators Ø Logical Operators Ø Equality Operators (compares logic values of 0 and 1) Ø Identity Operators (compares logic values of 0, 1, X and Z) Ø Relational Operators Ø Logical Shift Operators Ø Miscellaneous Operators m+n ~m &m m-n m&n –m m|n ~&m|m !m m*n m^n ~|m m&&n m==n jevtovic. nikola@gmail. com sel? m: n m~^n ^m ~^m m%n m^~n ^~m m||n m!=n m===n m<n m>n m/n m!==n m<<n {m, n} m>=n m>>n {n{m}} Verilog HDL Quick Reference Guide ->m 38

11. Operators ~ / >> <= != ~& ~^ ~| jevtovic. nikola@gmail. com + % - (unary) highest (binary) > === >= !== precedence ! * + << < == & ^ | && || ? : lowest Verilog HDL Quick Reference Guide 39

![12 Continuous Assignments Syntax Explicit Continuous Assignment nettype size netname assign delay 12. Continuous Assignments • - Syntax Explicit Continuous Assignment net_type [size] net_name; assign #(delay)](https://slidetodoc.com/presentation_image/2658c8bf9ee0f3634f82592612ae8980/image-40.jpg)

12. Continuous Assignments • - Syntax Explicit Continuous Assignment net_type [size] net_name; assign #(delay) net_name = expression; - Implicit Continuous Assignment net_type (strength) [size] net_name = expression; Continuous Assignment Examples //A 32 -bit wide 2: 1 MUX wire [31: 0] mux_out; assign mux_out = sel? a : b; //A 16 -bit wide tri-state buffer with delay tri [0: 15] #2. 8 buf_out = en? in: 16'bz; //A 64 -bit ALU with ECL output strengths wire [63: 0] (strong 1, pull 0) alu_out= alu_function(opcode, a, b); jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 40

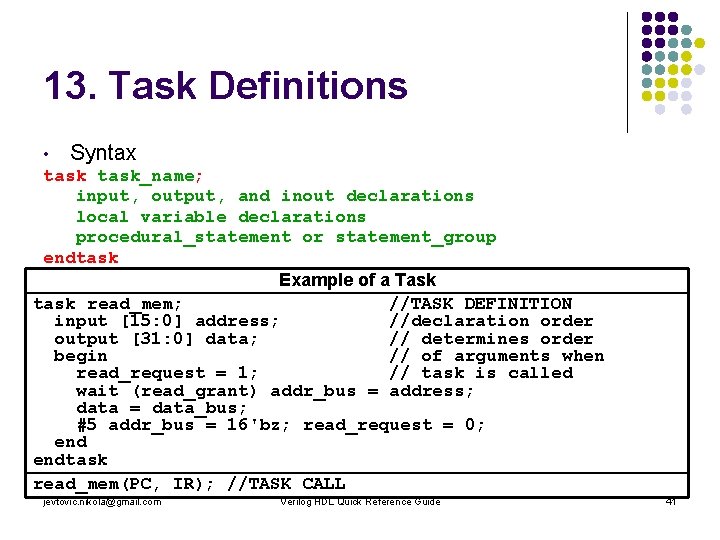

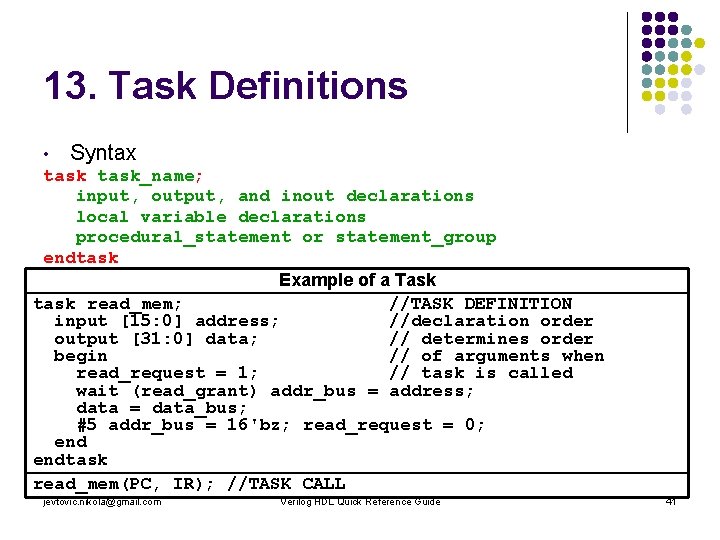

13. Task Definitions • Syntax task_name; input, output, and inout declarations local variable declarations procedural_statement or statement_group endtask Example of a Task task read_mem; //TASK DEFINITION input [15: 0] address; //declaration order output [31: 0] data; // determines order begin // of arguments when read_request = 1; // task is called wait (read_grant) addr_bus = address; data = data_bus; #5 addr_bus = 16'bz; read_request = 0; endtask read_mem(PC, IR); //TASK CALL jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 41

![14 Function Definitions Syntax function sizeortype functionname input declarations local variable declarations proceduralstatement 14. Function Definitions • Syntax function [size_or_type] function_name; input declarations local variable declarations procedural_statement](https://slidetodoc.com/presentation_image/2658c8bf9ee0f3634f82592612ae8980/image-42.jpg)

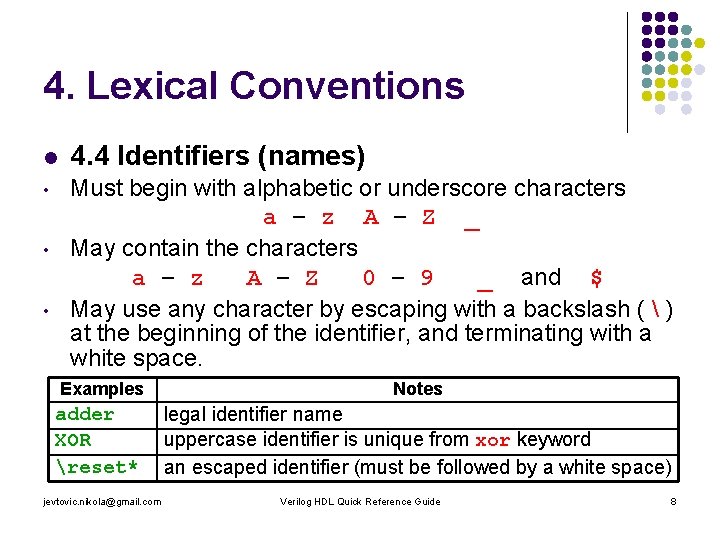

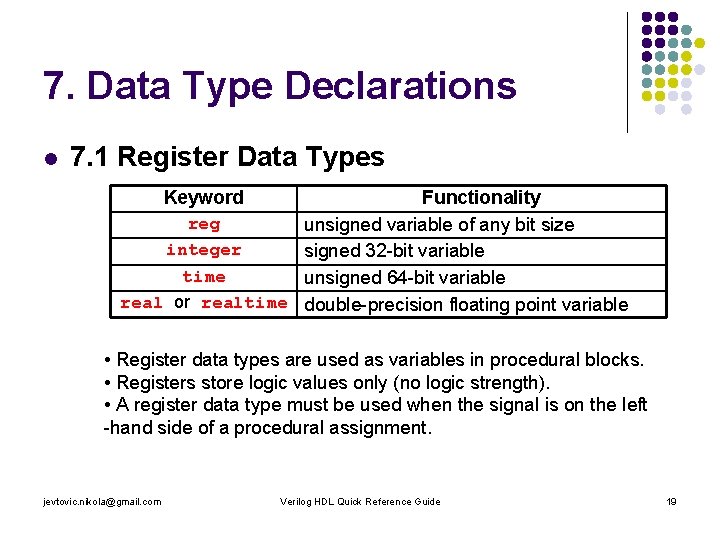

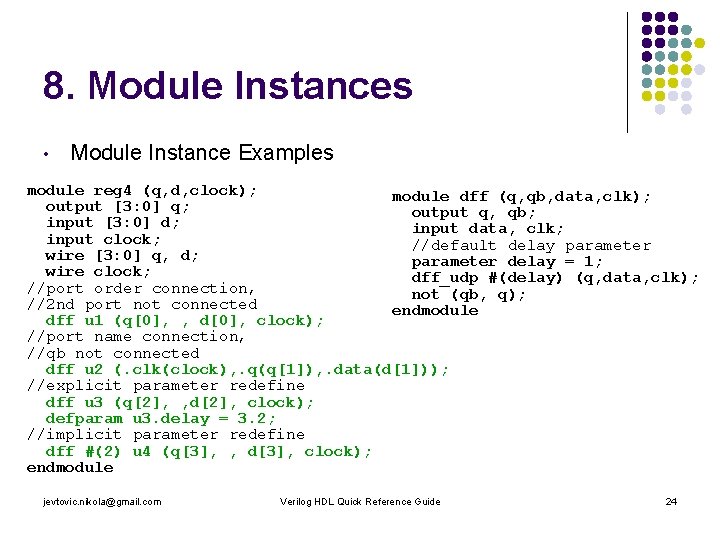

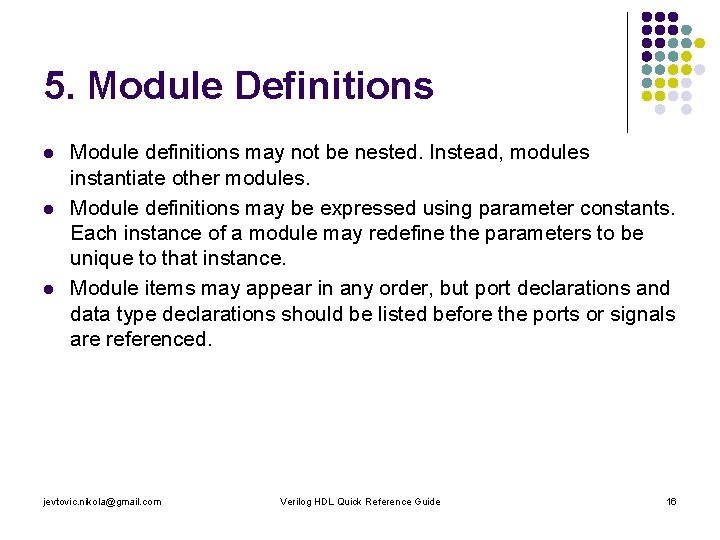

14. Function Definitions • Syntax function [size_or_type] function_name; input declarations local variable declarations procedural_statement or statement_group endfunction Example of a Function function [7: 0] Get. Byte; //FUNCTION DEFINITION input [63: 0] Word; //declaration order input [3: 0] Byte. Num; //determines order integer Bit; //of arguments when reg [7: 0] temp; //called begin for (Bit=0; Bit<=7; Bit=Bit+1) temp[Bit] = Word[((Byte. Num-1)*8)+Bit]; Get. Byte = temp; //A function returns end // the value assigned endfunction // to its name this_byte = Get. Byte(data, 4); //FUNCTION CALL jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 42

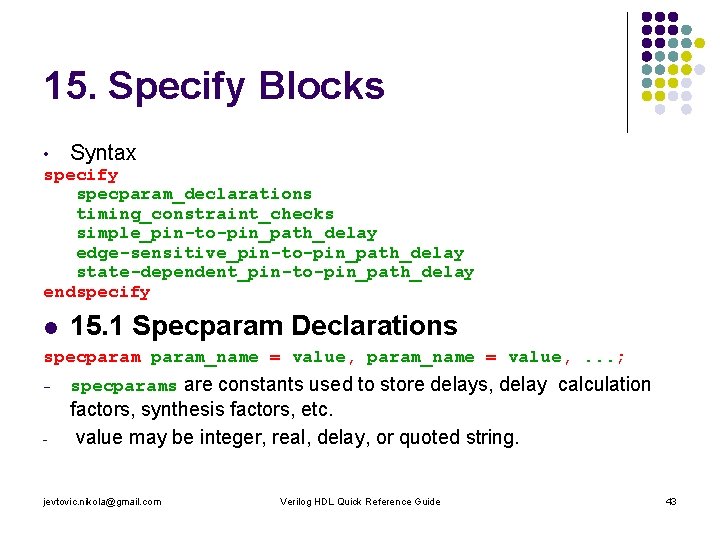

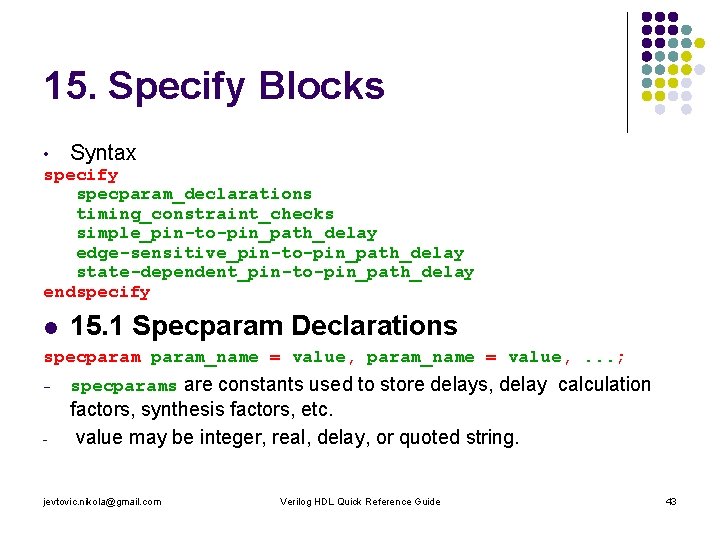

15. Specify Blocks • Syntax specify specparam_declarations timing_constraint_checks simple_pin-to-pin_path_delay edge-sensitive_pin-to-pin_path_delay state-dependent_pin-to-pin_path_delay endspecify l 15. 1 Specparam Declarations specparam_name = value, . . . ; - specparams are constants used to store delays, delay calculation - factors, synthesis factors, etc. value may be integer, real, delay, or quoted string. jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 43

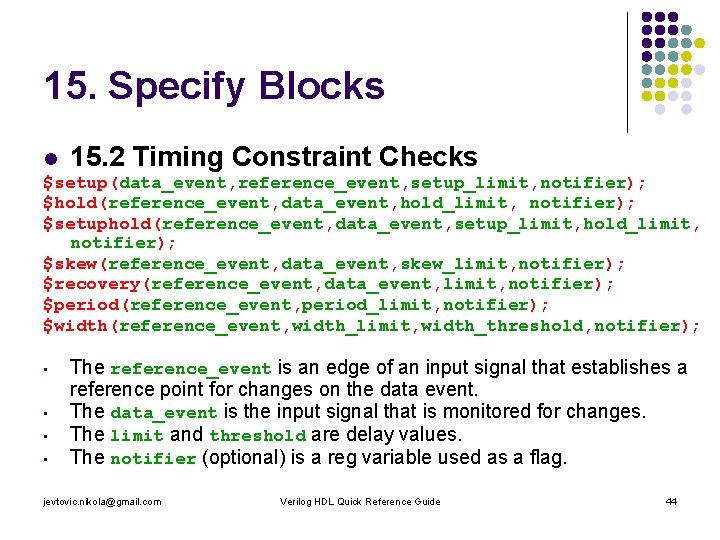

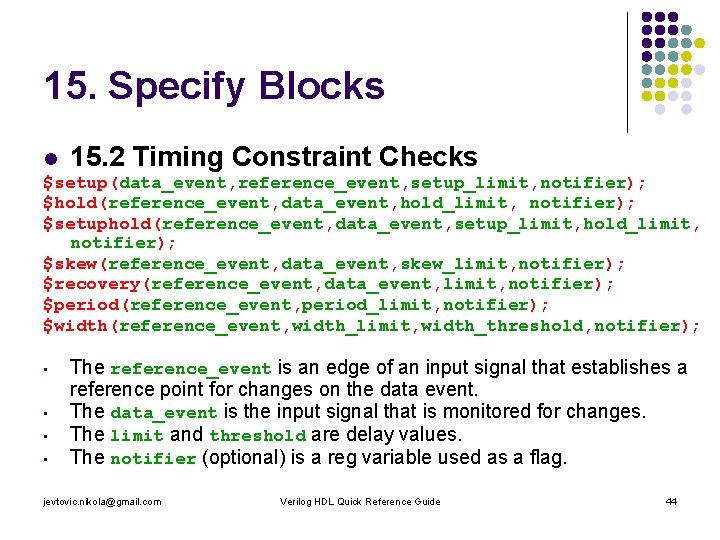

15. Specify Blocks l 15. 2 Timing Constraint Checks $setup(data_event, reference_event, setup_limit, notifier); $hold(reference_event, data_event, hold_limit, notifier); $setuphold(reference_event, data_event, setup_limit, hold_limit, notifier); $skew(reference_event, data_event, skew_limit, notifier); $recovery(reference_event, data_event, limit, notifier); $period(reference_event, period_limit, notifier); $width(reference_event, width_limit, width_threshold, notifier); • • The reference_event is an edge of an input signal that establishes a reference point for changes on the data event. The data_event is the input signal that is monitored for changes. The limit and threshold are delay values. The notifier (optional) is a reg variable used as a flag. jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 44

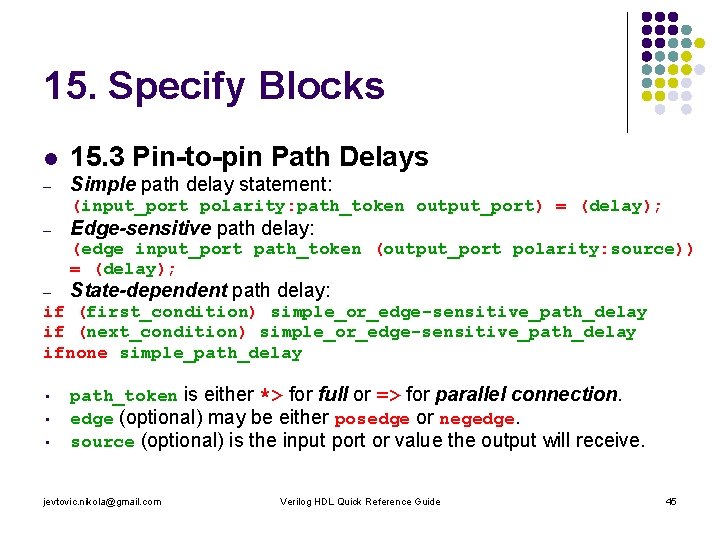

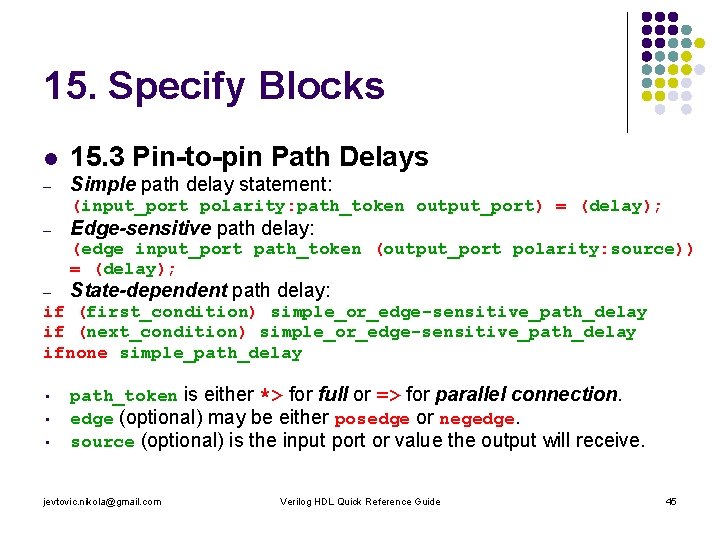

15. Specify Blocks l 15. 3 Pin-to-pin Path Delays – Simple path delay statement: (input_port polarity: path_token output_port) = (delay); – Edge-sensitive path delay: (edge input_port path_token (output_port polarity: source)) = (delay); – State-dependent path delay: if (first_condition) simple_or_edge-sensitive_path_delay if (next_condition) simple_or_edge-sensitive_path_delay ifnone simple_path_delay • • • path_token is either *> for full or => for parallel connection. edge (optional) may be either posedge or negedge. source (optional) is the input port or value the output will receive. jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 45

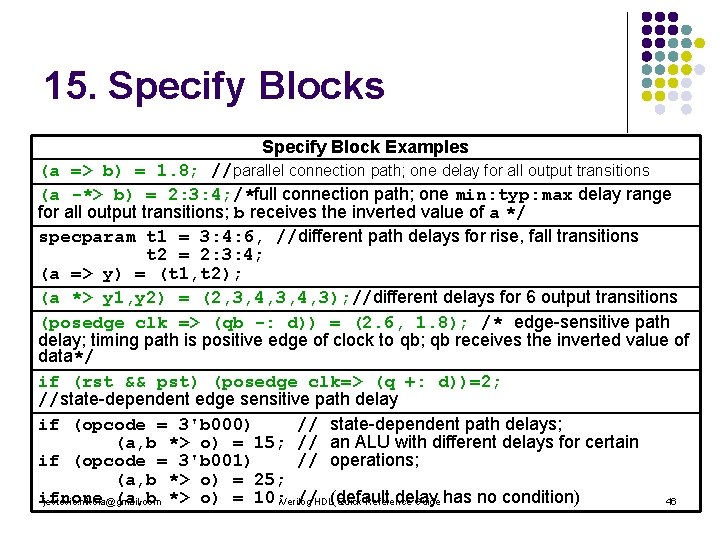

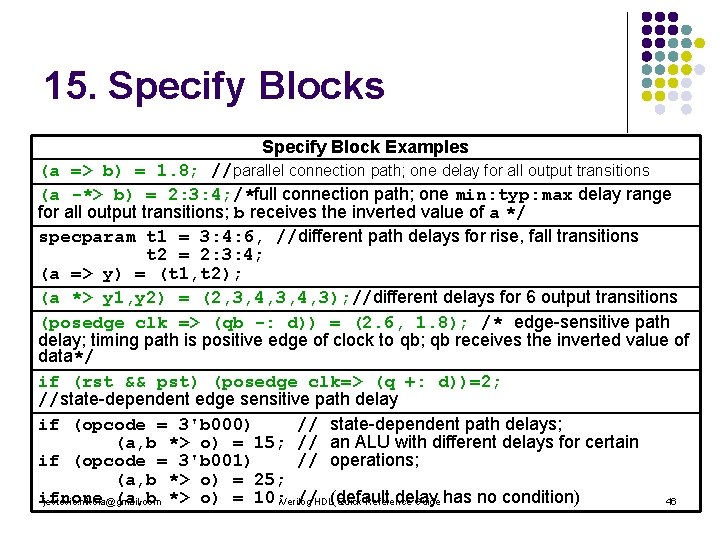

15. Specify Blocks Specify Block Examples (a => b) = 1. 8; //parallel connection path; one delay for all output transitions (a -*> b) = 2: 3: 4; /*full connection path; one min: typ: max delay range for all output transitions; b receives the inverted value of a */ specparam t 1 = 3: 4: 6, //different path delays for rise, fall transitions t 2 = 2: 3: 4; (a => y) = (t 1, t 2); (a *> y 1, y 2) = (2, 3, 4, 3); //different delays for 6 output transitions (posedge clk => (qb -: d)) = (2. 6, 1. 8); /* edge-sensitive path delay; timing path is positive edge of clock to qb; qb receives the inverted value of data*/ if (rst && pst) (posedge clk=> (q +: d))=2; //state-dependent edge sensitive path delay if (opcode = 3'b 000) // state-dependent path delays; (a, b *> o) = 15; // an ALU with different delays for certain if (opcode = 3'b 001) // operations; (a, b *> o) = 25; ifnone (a, b *> o) = 10; Verilog //HDL(default delay jevtovic. nikola@gmail. com Quick Reference Guide has no condition) 46

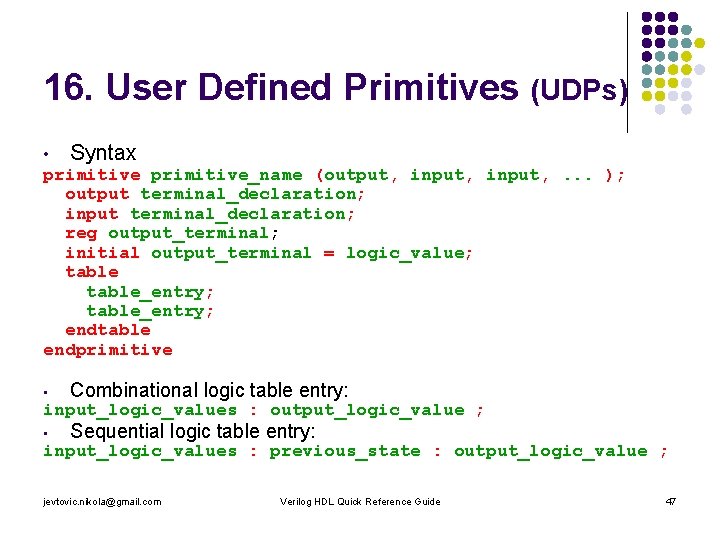

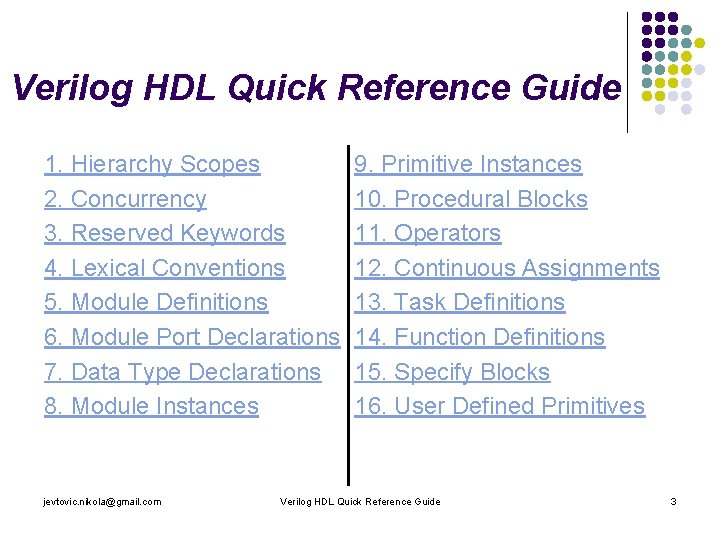

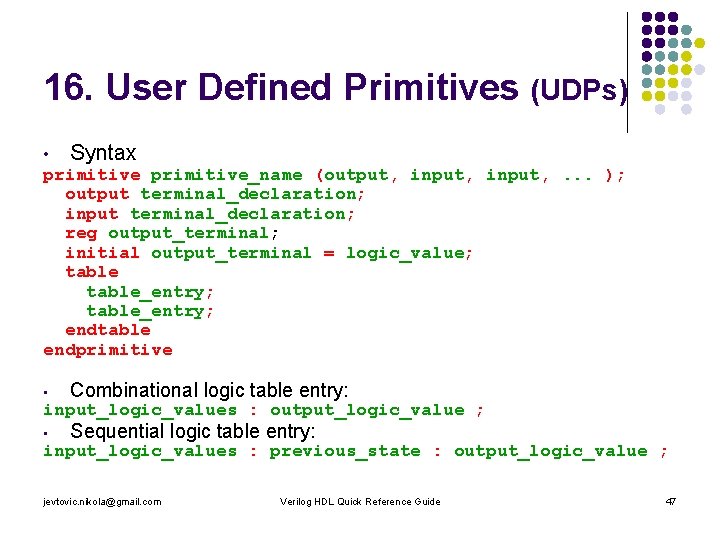

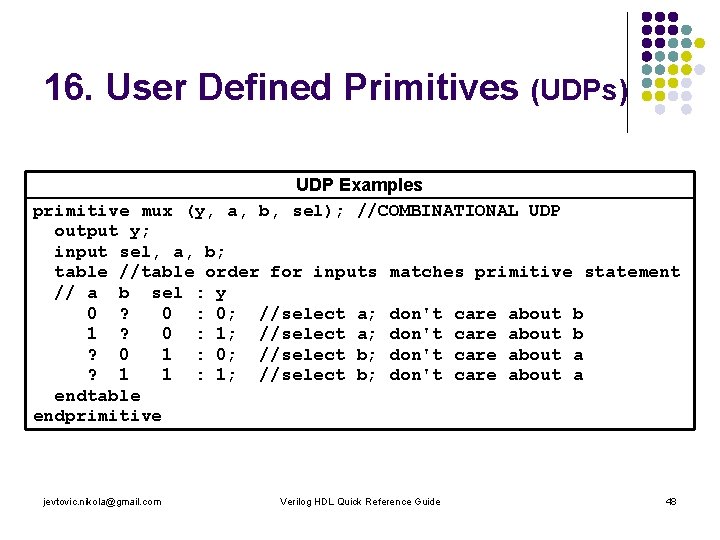

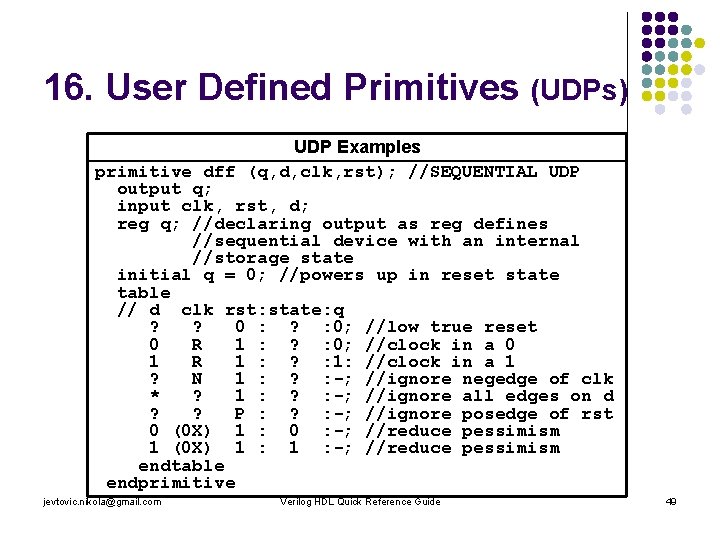

16. User Defined Primitives (UDPs) • Syntax primitive_name (output, input, . . . ); output terminal_declaration; input terminal_declaration; reg output_terminal; initial output_terminal = logic_value; table_entry; endtable endprimitive • Combinational logic table entry: input_logic_values : output_logic_value ; • Sequential logic table entry: input_logic_values : previous_state : output_logic_value ; jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 47

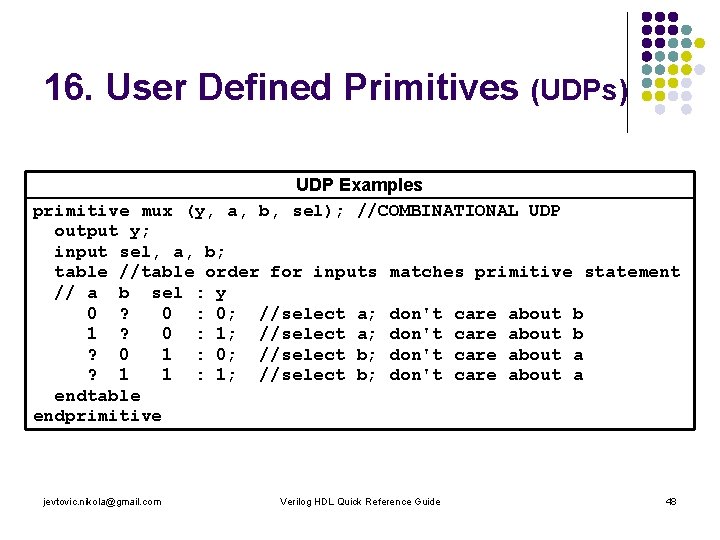

16. User Defined Primitives (UDPs) UDP Examples primitive mux (y, a, b, sel); //COMBINATIONAL UDP output y; input sel, a, b; table //table order for inputs matches primitive statement // a b sel : y 0 ? 0 : 0; //select a; don't care about b 1 ? 0 : 1; //select a; don't care about b ? 0 1 : 0; //select b; don't care about a ? 1 1 : 1; //select b; don't care about a endtable endprimitive jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 48

16. User Defined Primitives (UDPs) UDP Examples primitive dff (q, d, clk, rst); //SEQUENTIAL UDP output q; input clk, rst, d; reg q; //declaring output as reg defines //sequential device with an internal //storage state initial q = 0; //powers up in reset state table // d clk rst: state: q ? ? 0 : ? : 0; //low true reset 0 R 1 : ? : 0; //clock in a 0 1 R 1 : ? : 1: //clock in a 1 ? N 1 : ? : -; //ignore negedge of clk * ? 1 : ? : -; //ignore all edges on d ? ? P : ? : -; //ignore posedge of rst 0 (0 X) 1 : 0 : -; //reduce pessimism 1 (0 X) 1 : -; //reduce pessimism endtable endprimitive jevtovic. nikola@gmail. com Verilog HDL Quick Reference Guide 49