Verilog Gate Level Design 1 BASED ON THE

Verilog: Gate Level Design 1 BASED ON THE TUTORIAL ON THE BOOK CD 1/14/2022

Verilog 2 Each Verilog model is of a particular "level. " The level of a model depends on statements and constructs it contains. The levels of Verilog models are: Behavioral Register Transfer (RT) Gate, and Switch Chapter 4 : Gate level 1/14/2022

Objectives 3 predict the output of a gate level Verilog model given its inputs describe how to correct a gate level Verilog model given its source code, inputs and output write a Verilog gate-level model corresponding to a given simple schematic determine the schematic for a gate level Verilog model given its source code 1/14/2022

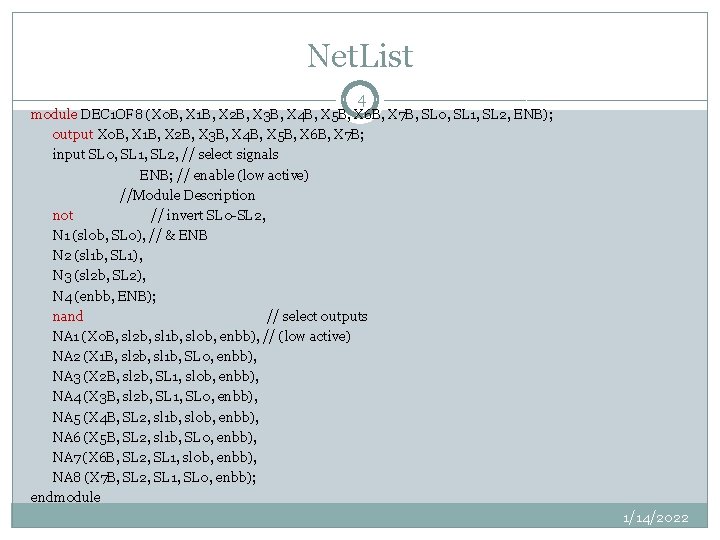

Net. List 4 module DEC 1 OF 8 (X 0 B, X 1 B, X 2 B, X 3 B, X 4 B, X 5 B, X 6 B, X 7 B, SL 0, SL 1, SL 2, ENB); output X 0 B, X 1 B, X 2 B, X 3 B, X 4 B, X 5 B, X 6 B, X 7 B; input SL 0, SL 1, SL 2, // select signals ENB; // enable (low active) //Module Description not // invert SL 0 -SL 2, N 1 (sl 0 b, SL 0), // & ENB N 2 (sl 1 b, SL 1), N 3 (sl 2 b, SL 2), N 4 (enbb, ENB); nand // select outputs NA 1 (X 0 B, sl 2 b, sl 1 b, sl 0 b, enbb), // (low active) NA 2 (X 1 B, sl 2 b, sl 1 b, SL 0, enbb), NA 3 (X 2 B, sl 2 b, SL 1, sl 0 b, enbb), NA 4 (X 3 B, sl 2 b, SL 1, SL 0, enbb), NA 5 (X 4 B, SL 2, sl 1 b, sl 0 b, enbb), NA 6 (X 5 B, SL 2, sl 1 b, SL 0, enbb), NA 7 (X 6 B, SL 2, SL 1, sl 0 b, enbb), NA 8 (X 7 B, SL 2, SL 1, SL 0, enbb); endmodule 1/14/2022

![Module embedding 5 module vabc (d, s); input [1: 0] s; output [3: 0] Module embedding 5 module vabc (d, s); input [1: 0] s; output [3: 0]](http://slidetodoc.com/presentation_image_h2/71a83ecbe754a2ee4f65b6bd01007f3f/image-5.jpg)

Module embedding 5 module vabc (d, s); input [1: 0] s; output [3: 0] d; not (s 1_, s[1]), (s 0_, s[0]); and (d[3], s 1_, s 0_); and (d[2], s 1_, s[0]); and (d[1], s 0_); and (d[0], s[1], s[0]); endmodule abc (a, b, c, d, s 1, s 0); input s 1, s 0; output a, b, c, d; not (s 1_, s 1), (s 0_, s 0); and (a, s 1_, s 0_); and (b, s 1_, s 0); and (c, s 1, s 0_); and (d, s 1, s 0); endmodule 1/14/2022

![Module abc in vabc 6 module vabc (d, s); input [1: 0] s; output Module abc in vabc 6 module vabc (d, s); input [1: 0] s; output](http://slidetodoc.com/presentation_image_h2/71a83ecbe754a2ee4f65b6bd01007f3f/image-6.jpg)

Module abc in vabc 6 module vabc (d, s); input [1: 0] s; output [3: 0] d; abc a 1 (d[3], d[2], d[1], d[0], s[1], s[0]); endmodule 1/14/2022

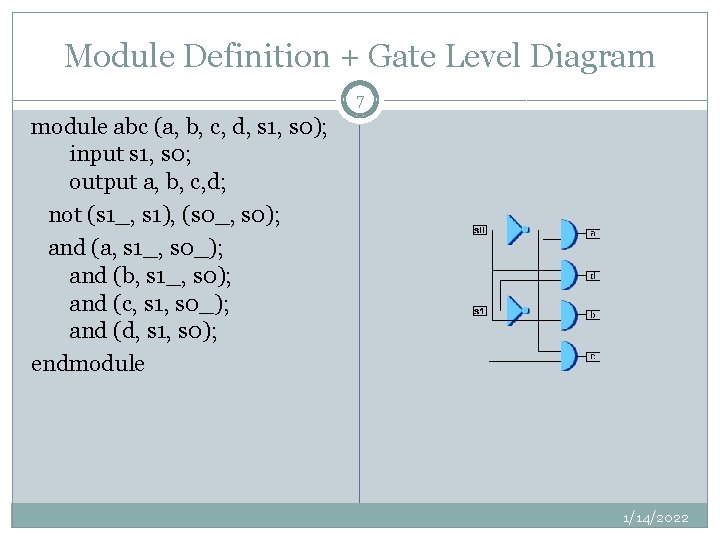

Module Definition + Gate Level Diagram 7 module abc (a, b, c, d, s 1, s 0); input s 1, s 0; output a, b, c, d; not (s 1_, s 1), (s 0_, s 0); and (a, s 1_, s 0_); and (b, s 1_, s 0); and (c, s 1, s 0_); and (d, s 1, s 0); endmodule 1/14/2022

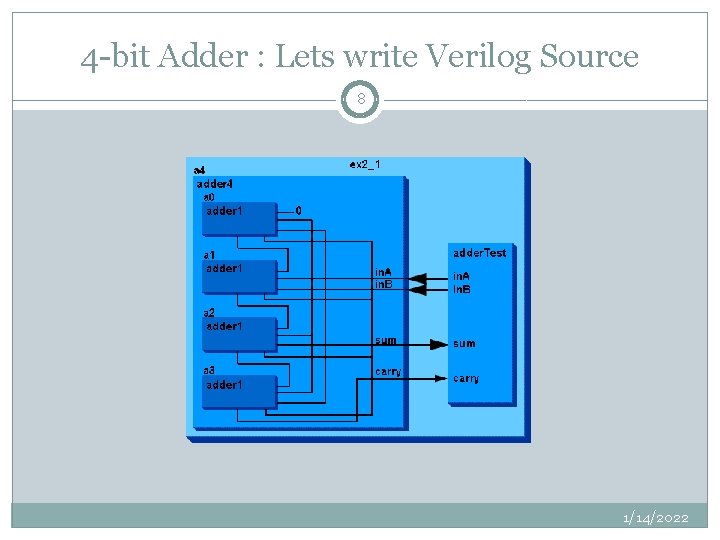

4 -bit Adder : Lets write Verilog Source 8 1/14/2022

- Slides: 8