Verilog A Cadence Simple example 1 Cadence using

- Slides: 21

Verilog A - Cadence Simple example 1

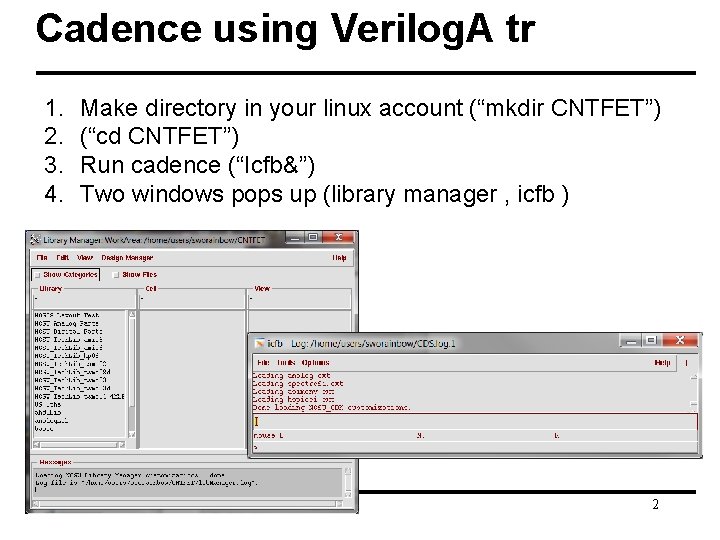

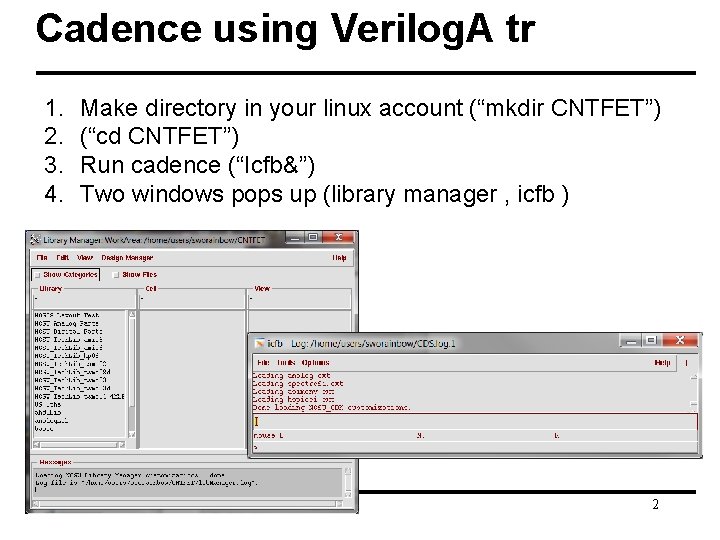

Cadence using Verilog. A tr 1. 2. 3. 4. Make directory in your linux account (“mkdir CNTFET”) (“cd CNTFET”) Run cadence (“Icfb&”) Two windows pops up (library manager , icfb ) 2

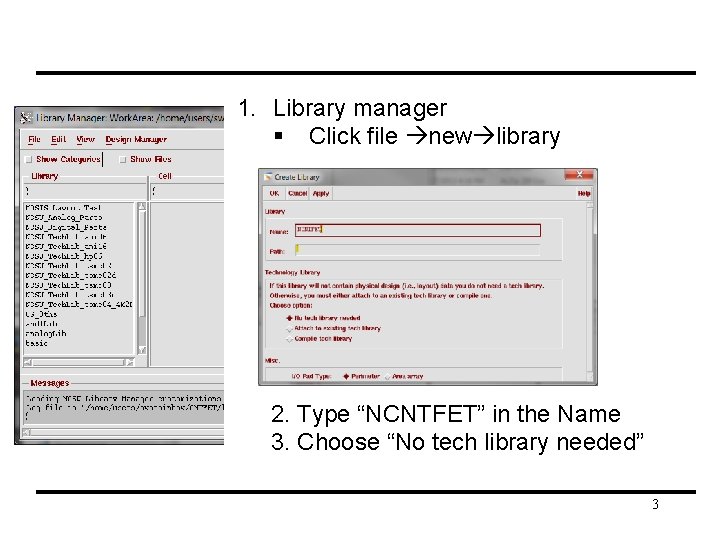

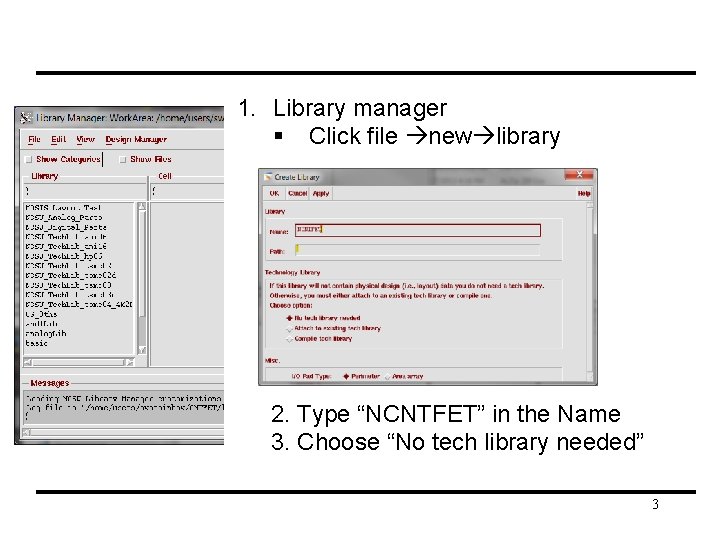

1. Library manager § Click file new library 2. Type “NCNTFET” in the Name 3. Choose “No tech library needed” 3

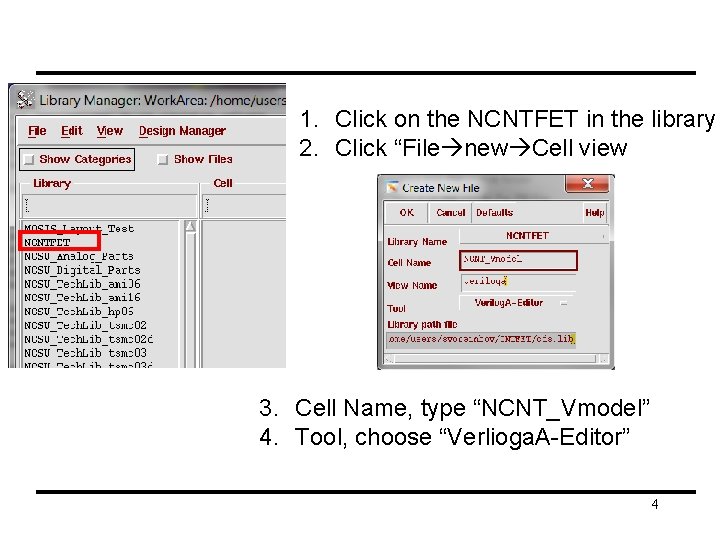

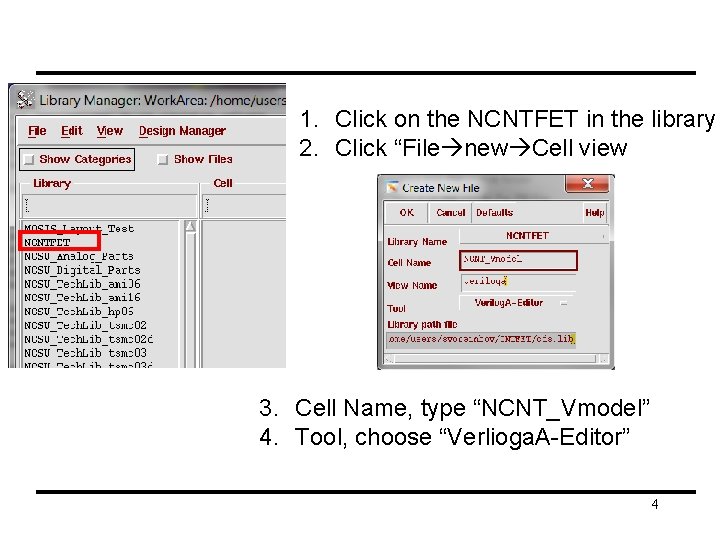

1. Click on the NCNTFET in the library 2. Click “File new Cell view 3. Cell Name, type “NCNT_Vmodel” 4. Tool, choose “Verlioga. A-Editor” 4

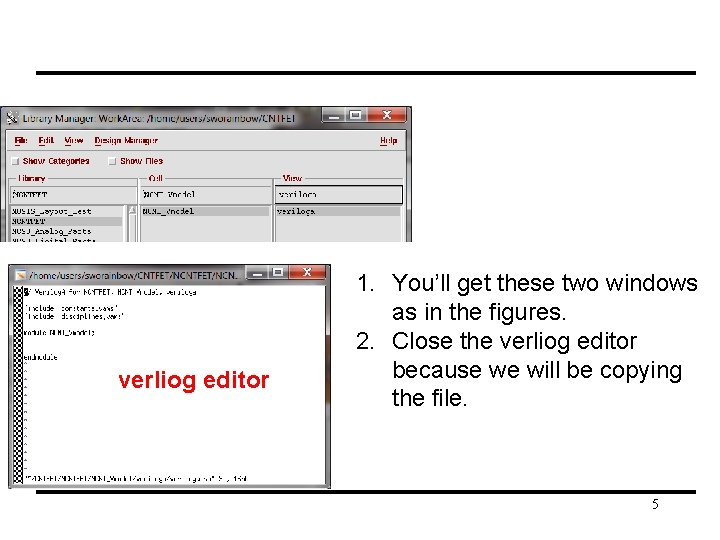

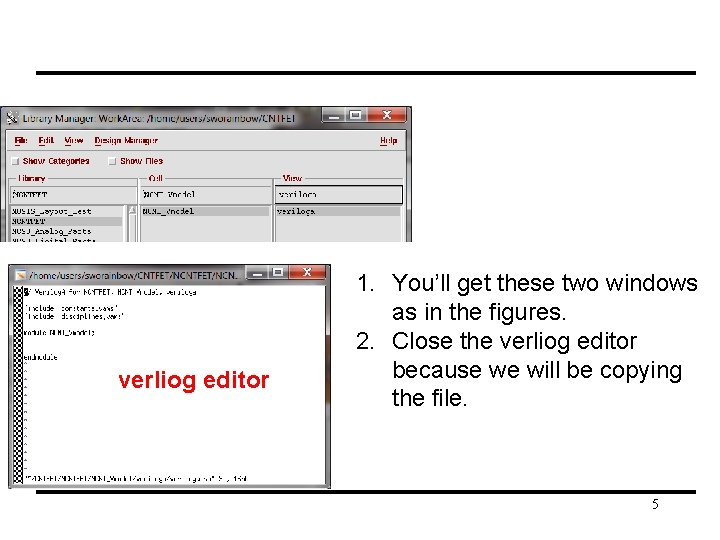

verliog editor 1. You’ll get these two windows as in the figures. 2. Close the verliog editor because we will be copying the file. 5

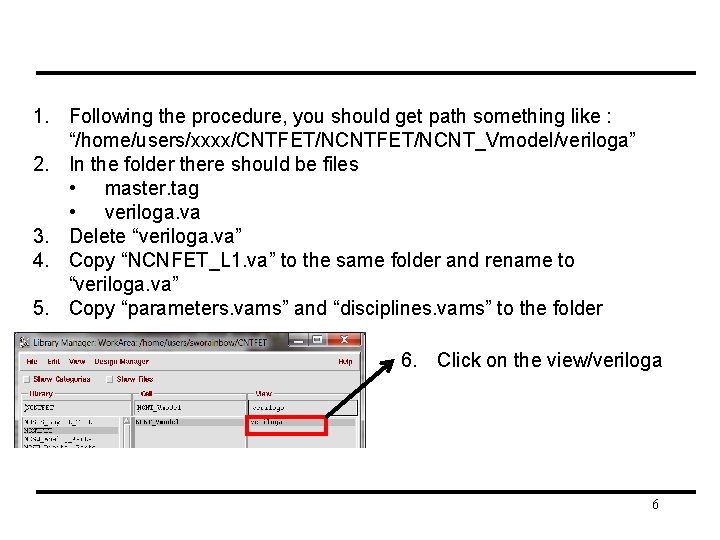

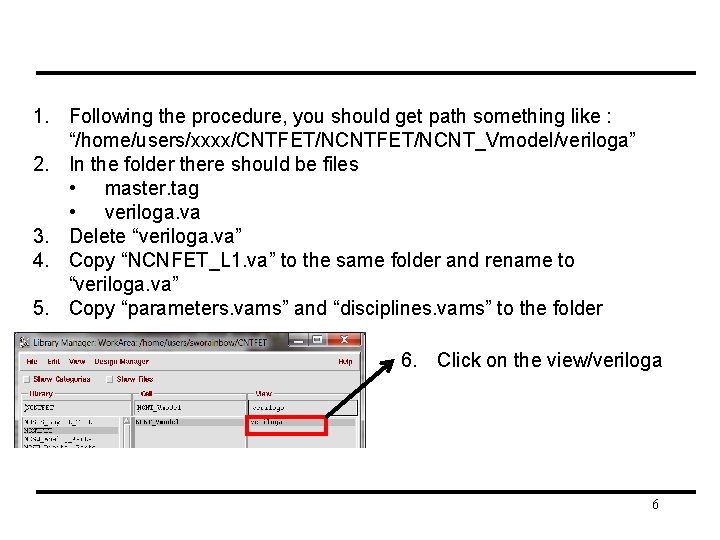

1. Following the procedure, you should get path something like : “/home/users/xxxx/CNTFET/NCNT_Vmodel/veriloga” 2. In the folder there should be files • master. tag • veriloga. va 3. Delete “veriloga. va” 4. Copy “NCNFET_L 1. va” to the same folder and rename to “veriloga. va” 5. Copy “parameters. vams” and “disciplines. vams” to the folder 6. Click on the view/veriloga 6

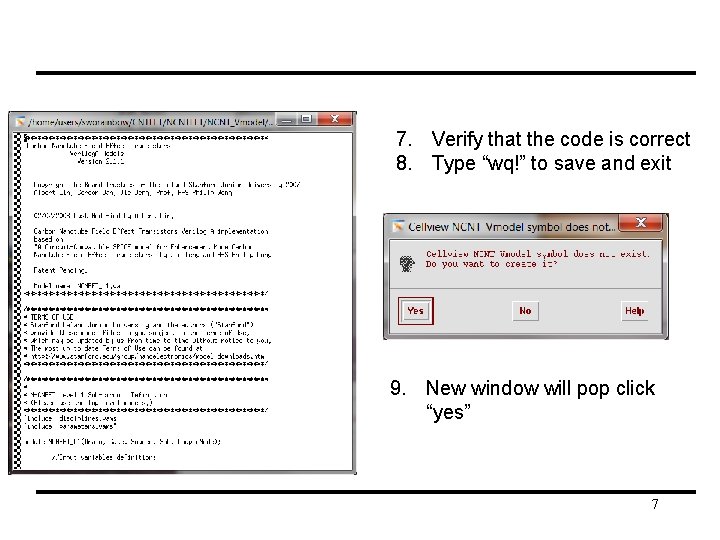

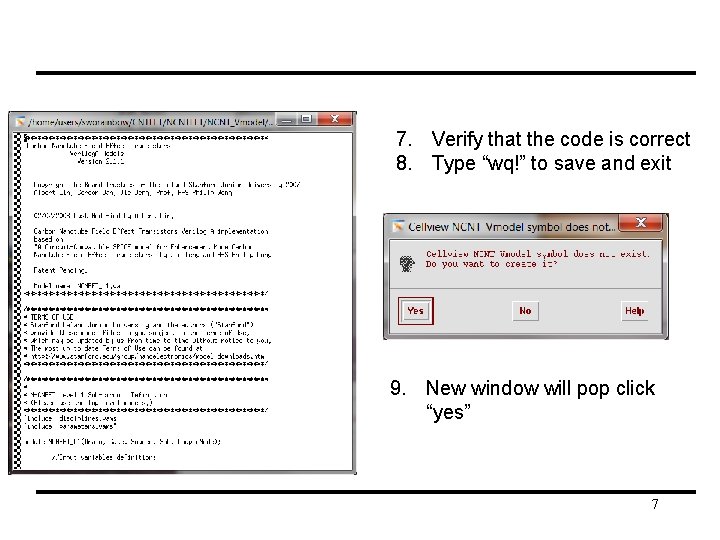

7. Verify that the code is correct 8. Type “wq!” to save and exit 9. New window will pop click “yes” 7

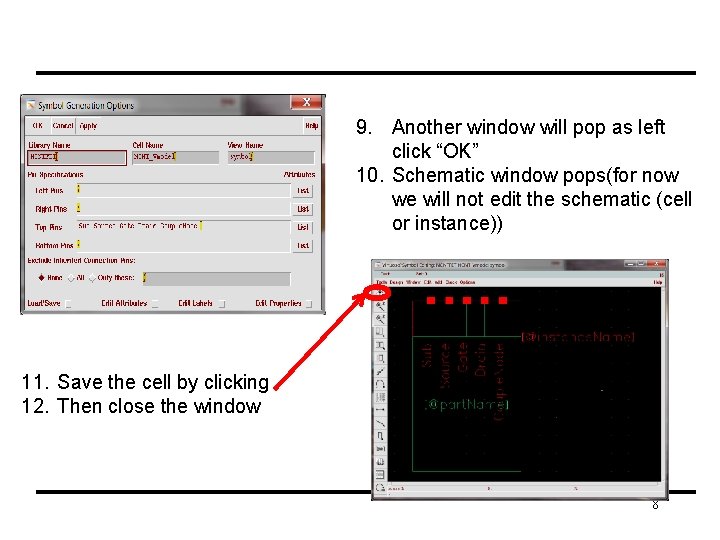

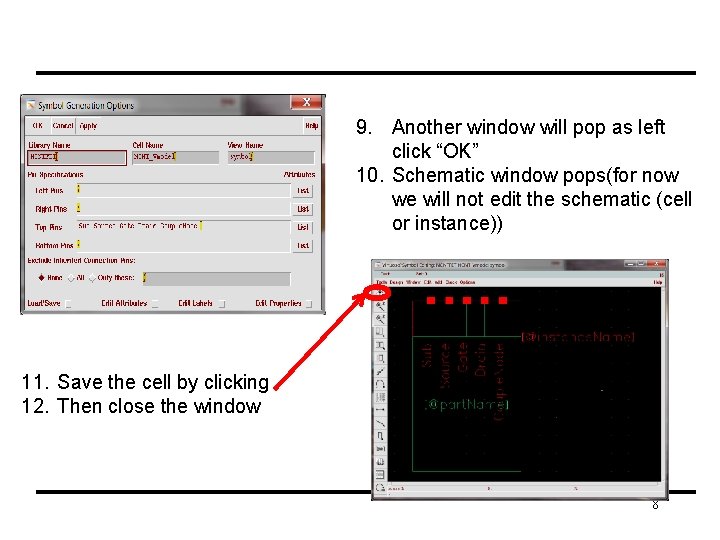

9. Another window will pop as left click “OK” 10. Schematic window pops(for now we will not edit the schematic (cell or instance)) 11. Save the cell by clicking 12. Then close the window 8

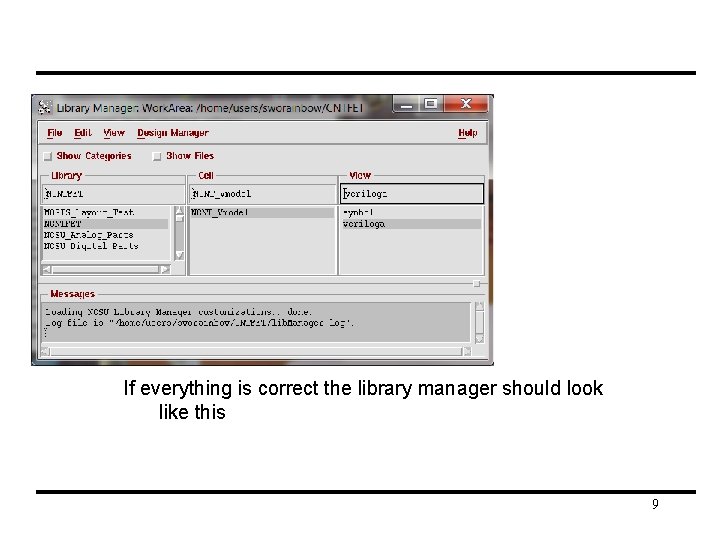

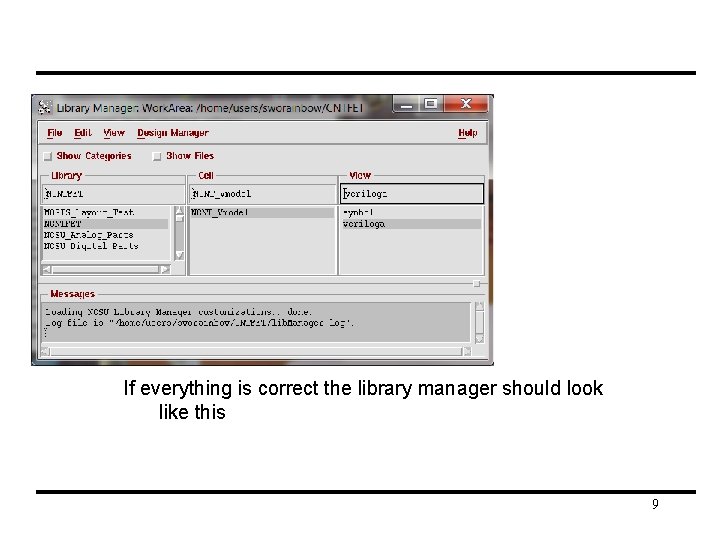

If everything is correct the library manager should look like this 9

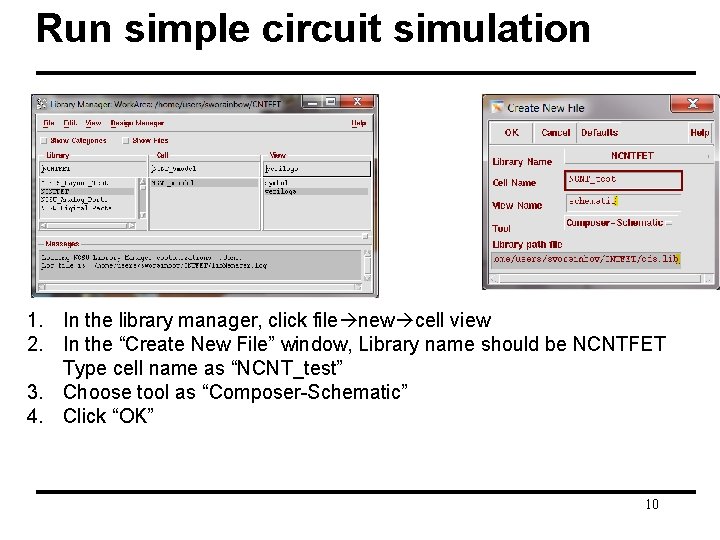

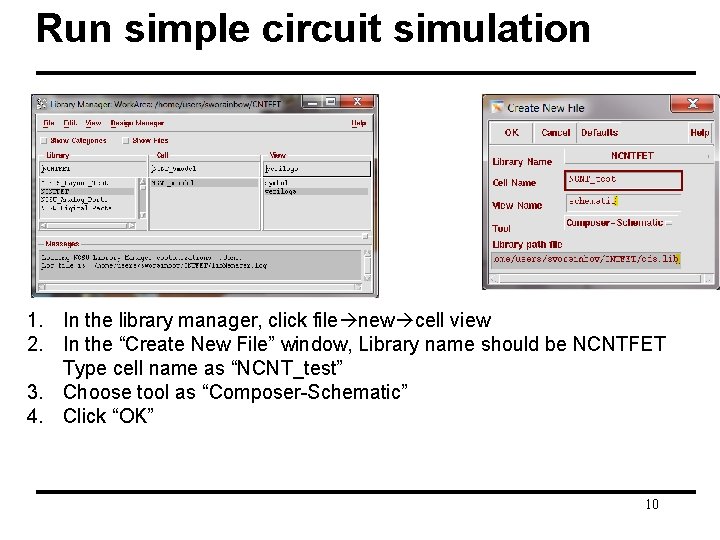

Run simple circuit simulation 1. In the library manager, click file new cell view 2. In the “Create New File” window, Library name should be NCNTFET Type cell name as “NCNT_test” 3. Choose tool as “Composer-Schematic” 4. Click “OK” 10

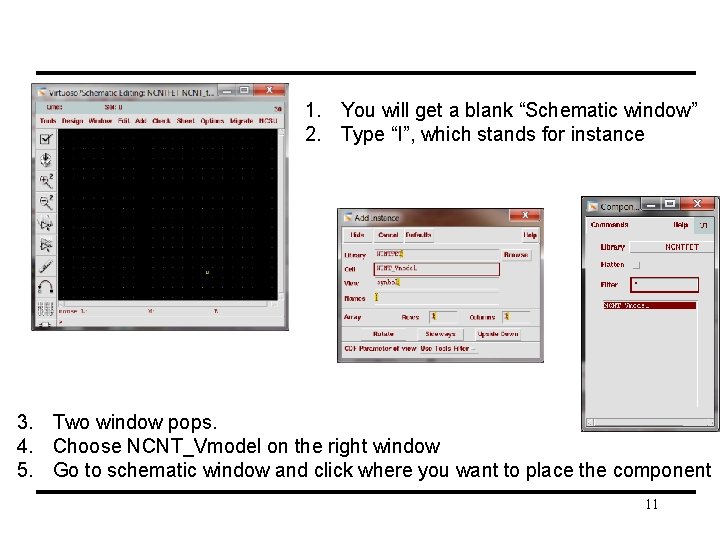

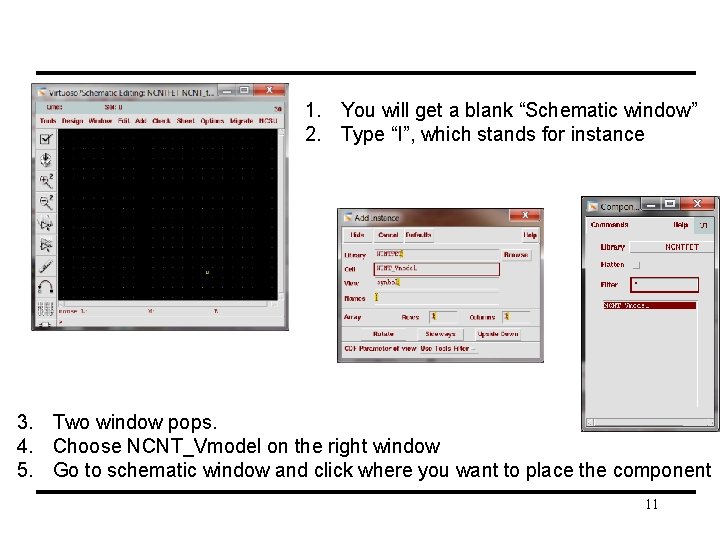

1. You will get a blank “Schematic window” 2. Type “I”, which stands for instance 3. Two window pops. 4. Choose NCNT_Vmodel on the right window 5. Go to schematic window and click where you want to place the component 11

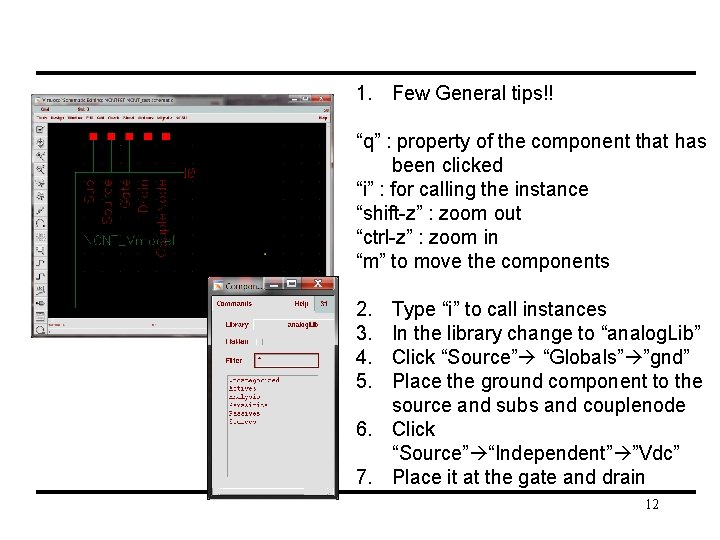

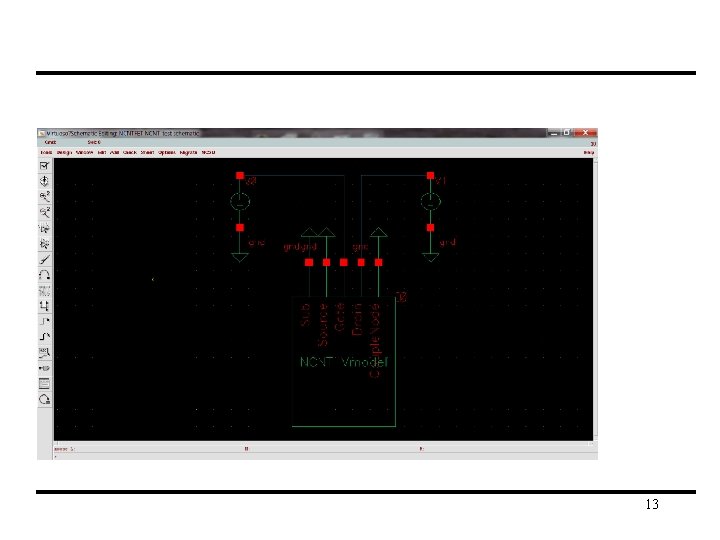

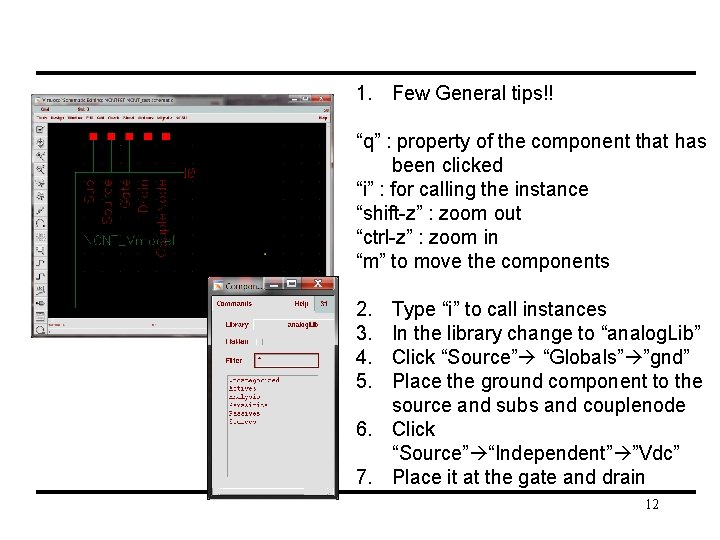

1. Few General tips!! “q” : property of the component that has been clicked “i” : for calling the instance “shift-z” : zoom out “ctrl-z” : zoom in “m” to move the components 2. 3. 4. 5. Type “i” to call instances In the library change to “analog. Lib” Click “Source” “Globals” ”gnd” Place the ground component to the source and subs and couplenode 6. Click “Source” “Independent” ”Vdc” 7. Place it at the gate and drain 12

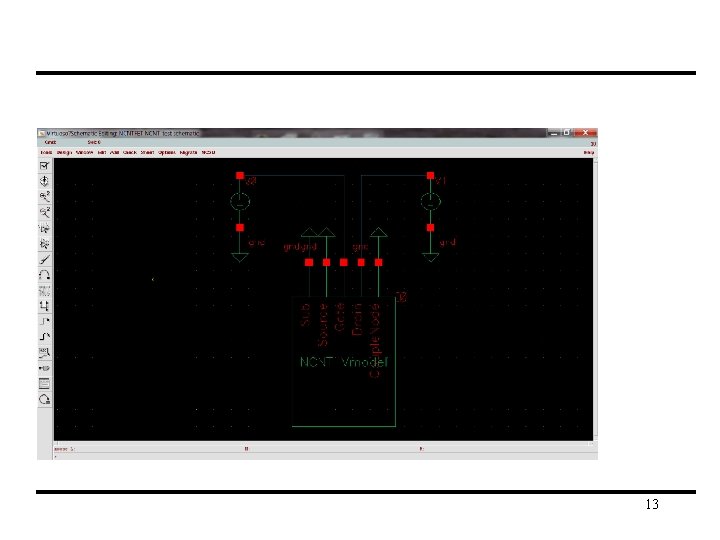

13

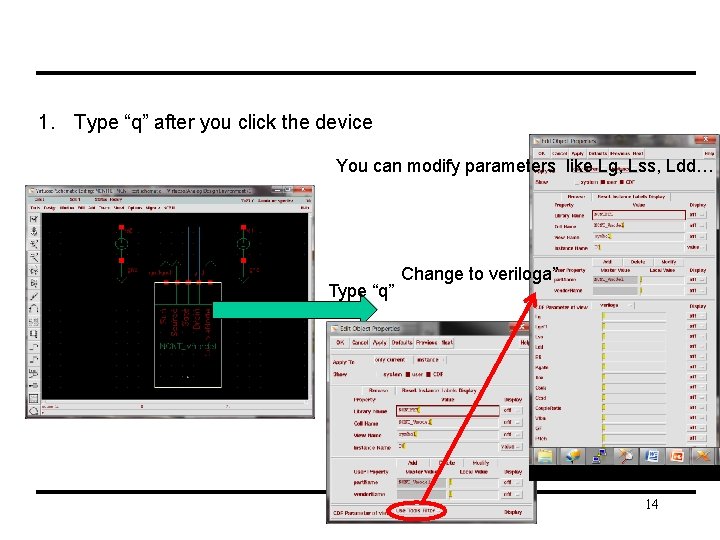

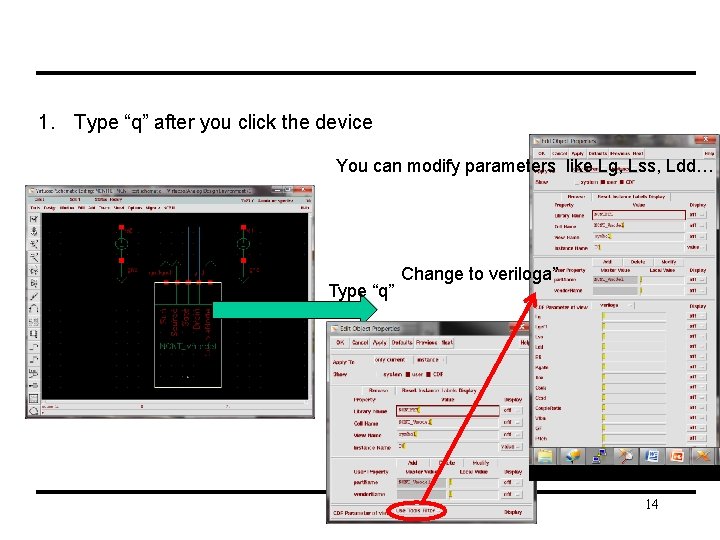

1. Type “q” after you click the device You can modify parameters like Lg, Lss, Ldd… Type “q” Change to veriloga” 14

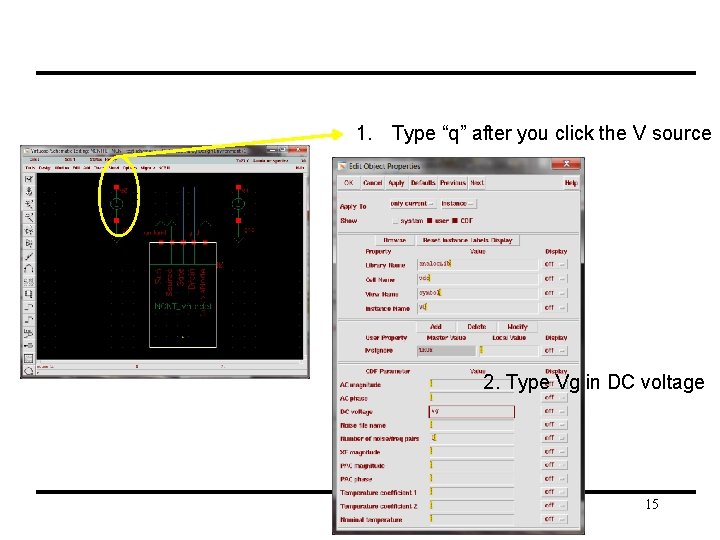

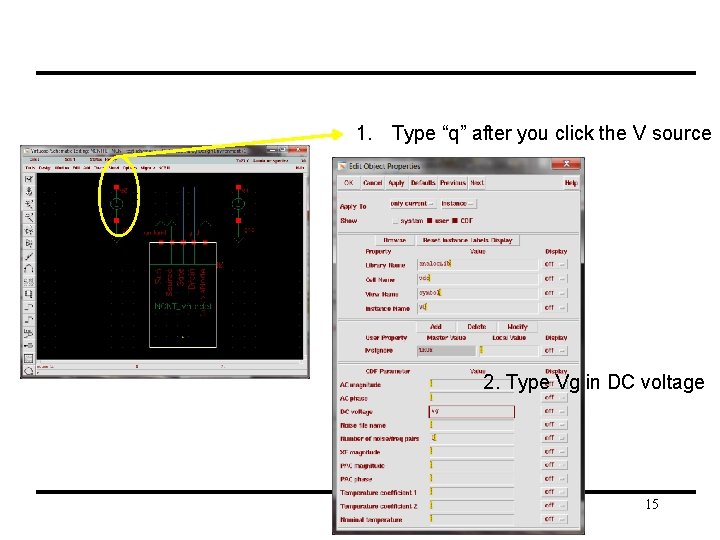

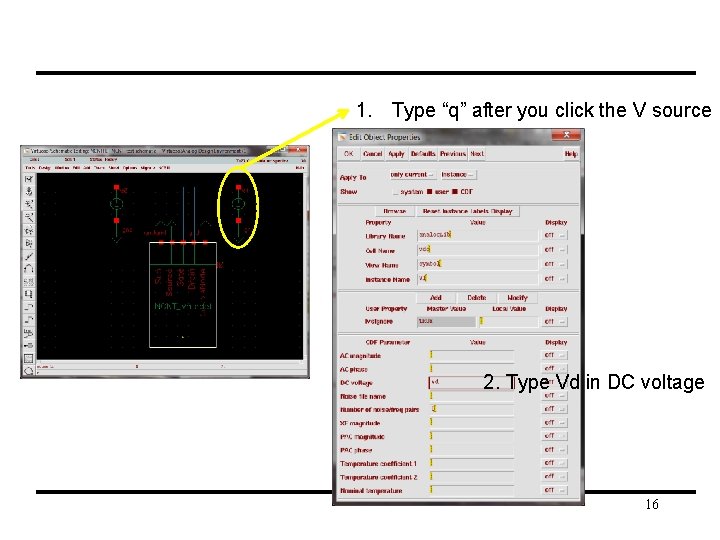

1. Type “q” after you click the V source 2. Type Vg in DC voltage 15

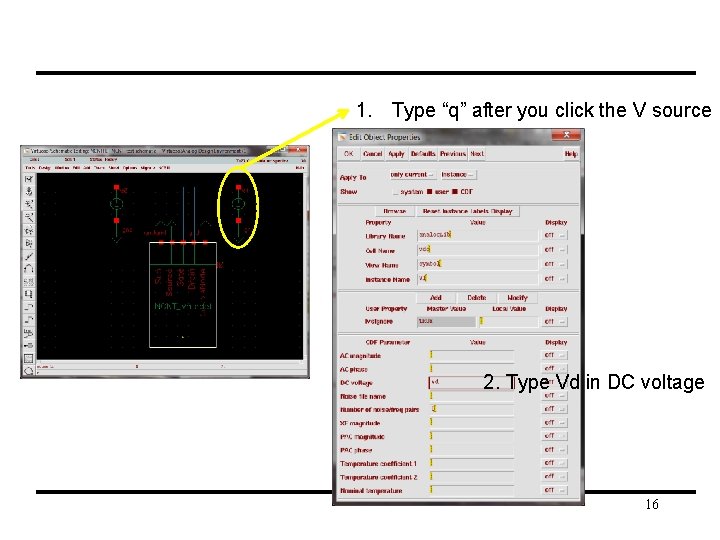

1. Type “q” after you click the V source 2. Type Vd in DC voltage 16

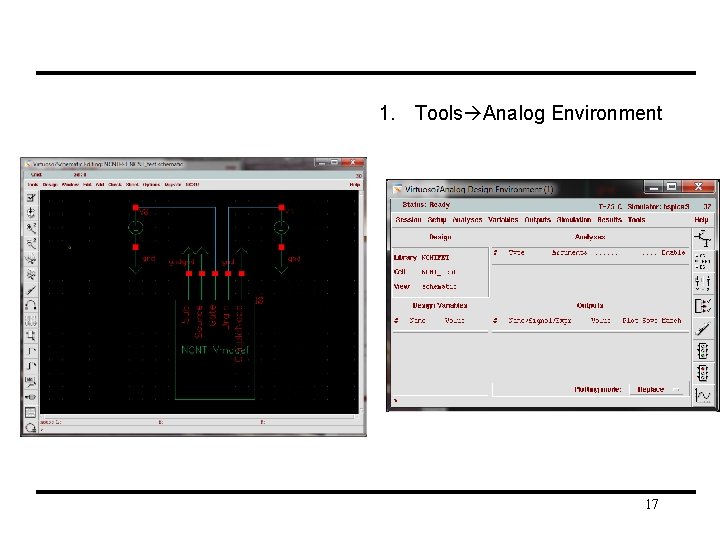

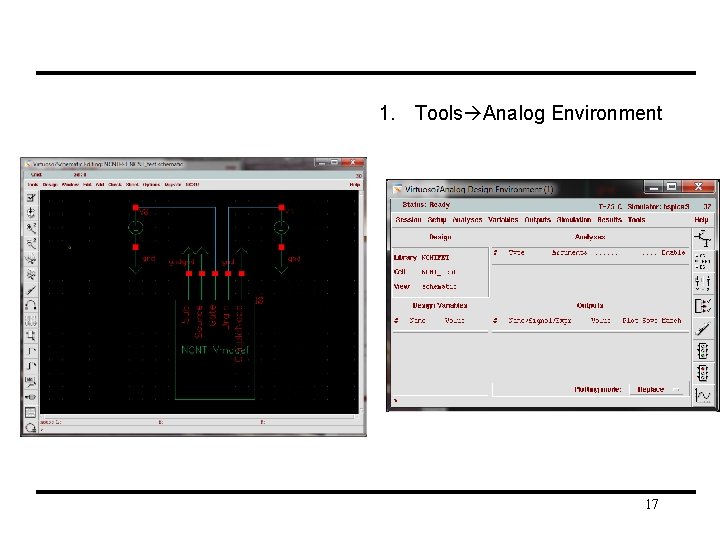

1. Tools Analog Environment 17

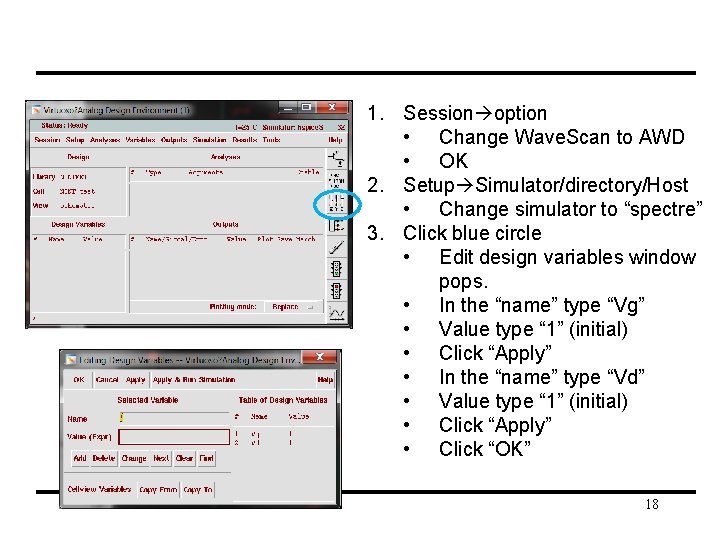

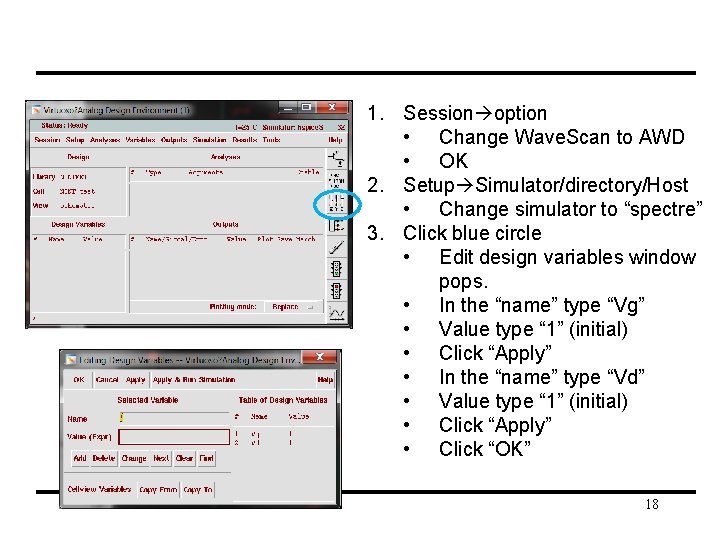

1. Session option • Change Wave. Scan to AWD • OK 2. Setup Simulator/directory/Host • Change simulator to “spectre” 3. Click blue circle • Edit design variables window pops. • In the “name” type “Vg” • Value type “ 1” (initial) • Click “Apply” • In the “name” type “Vd” • Value type “ 1” (initial) • Click “Apply” • Click “OK” 18

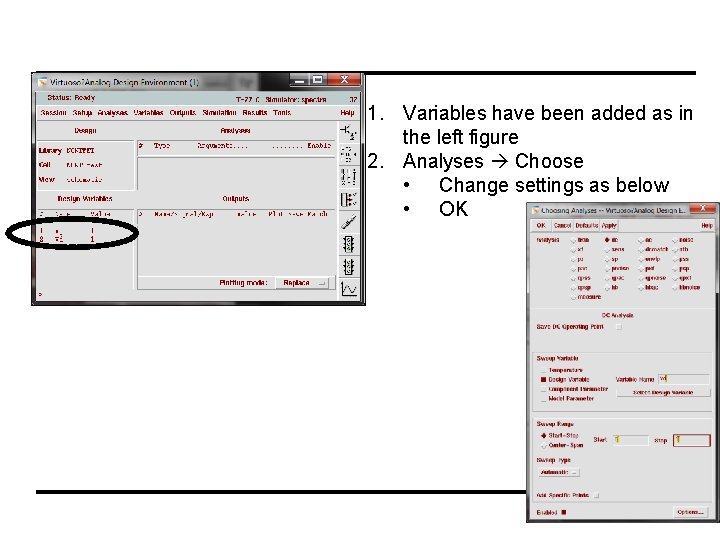

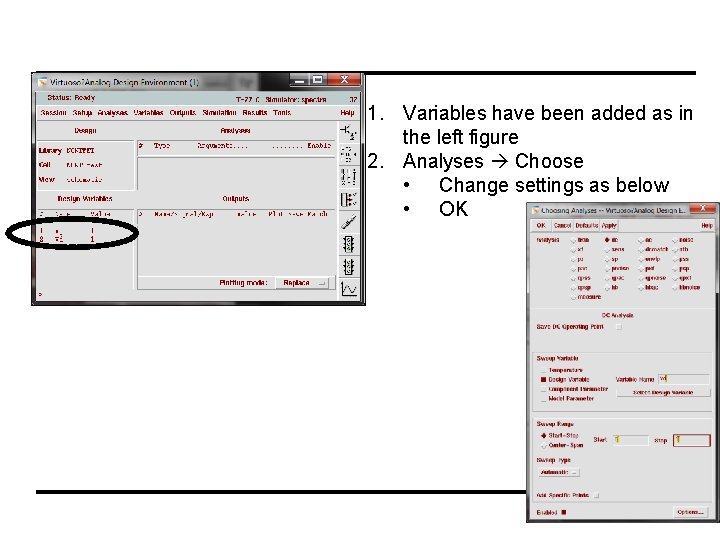

1. Variables have been added as in the left figure 2. Analyses Choose • Change settings as below • OK 19

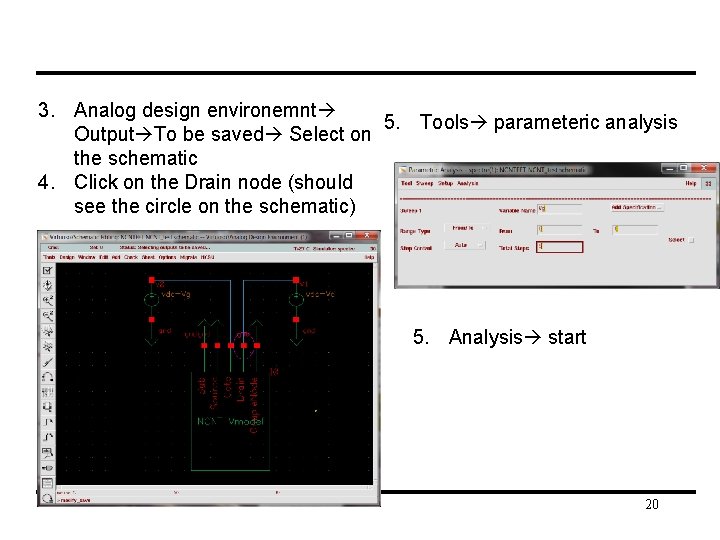

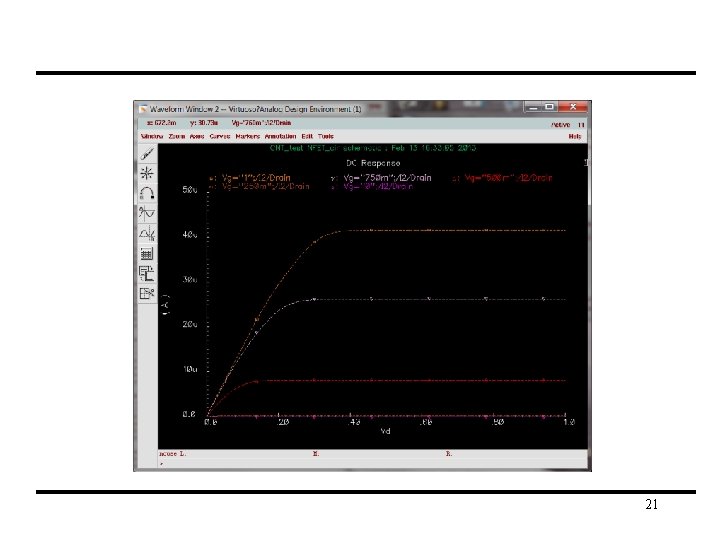

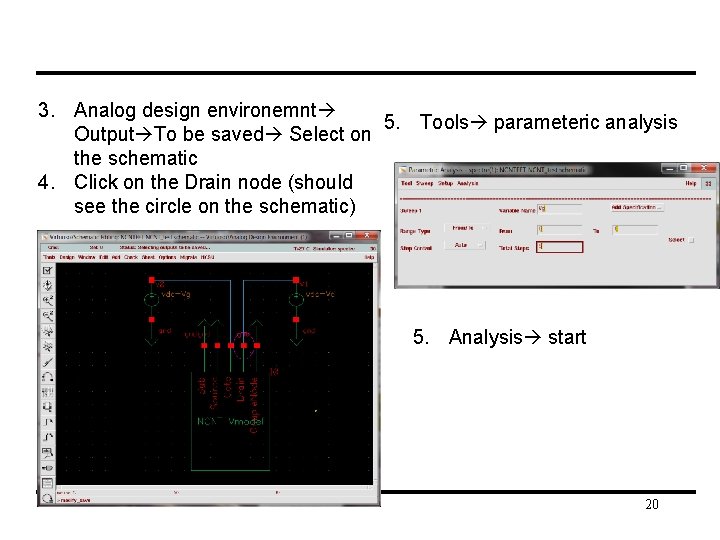

3. Analog design environemnt 5. Tools parameteric analysis Output To be saved Select on the schematic 4. Click on the Drain node (should see the circle on the schematic) 5. Analysis start 20

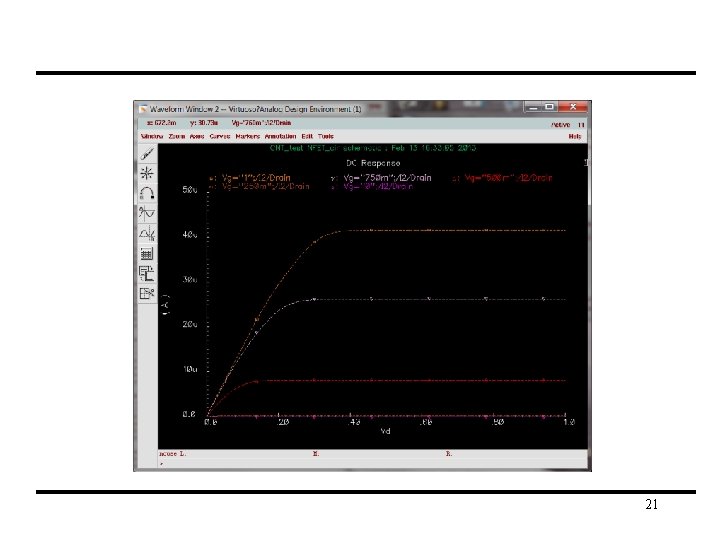

21