Velopix and Velopix J Buytaert Slides stolen from

Velopix and Velopix++ J. Buytaert Slides stolen from many other presentations. 2/24/2021 Brainstorming CPPM 1

Outline n Velopix q n Description and performances Velopix++ q q Requirements Implementing high precision timing. Data rates. More Front end processing needed ? 2/24/2021 Brainstorming CPPM 2

Velo. Pix Project Overview n n n Design started in June 2013 (after Timepix 3 submission) Change of technology (IBM 130 nm → TSMC 130 nm) The chip was submitted as an engineering run on May 2016 First wafers received on 31 st August 2016 Fabricated (and diced) chips back at CERN on 7 th September Functional testing TID & SEE Irradiation campaigns. Problems with excessive jitter on serial data outputs and SEL observed on custom HD library. ‘Minimal’ redesign and new submission 20 July 2017. New wafers November 2017. New functional test & irradiation campaign. Wafer probe test on 15 wafers finished. April 2018 New production order soon. Velo. Pix wafers ESE Seminar 8 th November 2016 3

Velo. Pix design contributors • Institutes: CERN & NIKHEF • ASIC designers: – R. Ballabriga, V. Gromov, X. Llopart, S. Miryala, T. Poikela, J. D. Schipper and W. Wong • IP Blocks: – e. CDRPLL: R. de Oliveira and P. Leitao – Band-Gap: S. Michelis • Support, readout and Testing: – J. Alozy, M. van Beuzekom, H. Boterenbrood, B. van der Heijden, J. Buytaert, M. Daldoss and E. Lemos, A. Fernandez Prieto, P. Vazquez. ESE Seminar 8 th November 2016 4

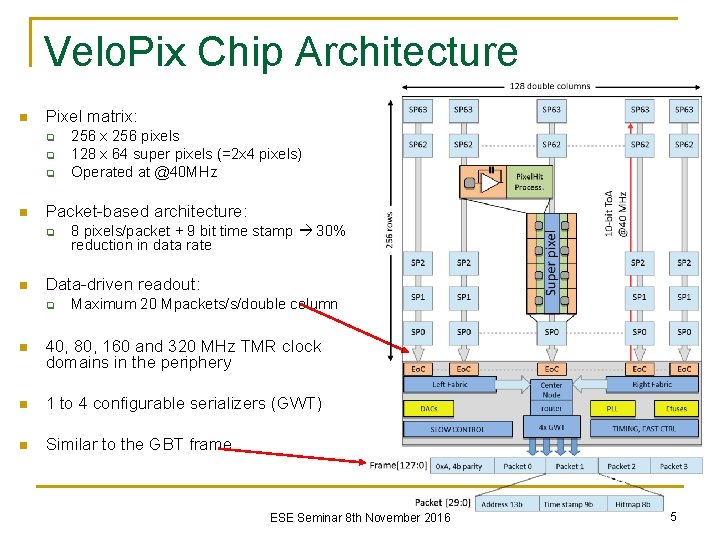

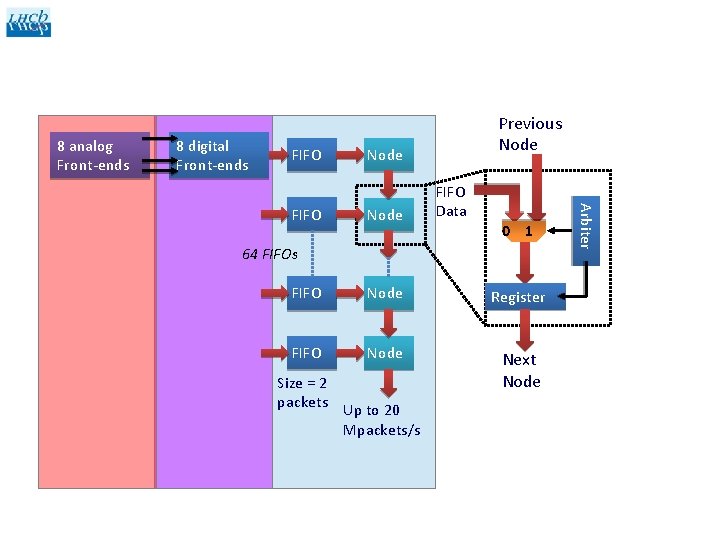

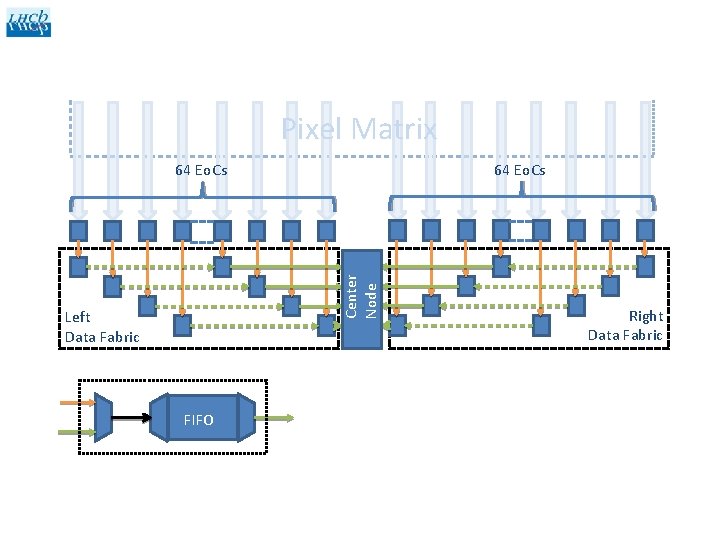

Velo. Pix Chip Architecture n Pixel matrix: q q q n Packet-based architecture: q n 256 x 256 pixels 128 x 64 super pixels (=2 x 4 pixels) Operated at @40 MHz 8 pixels/packet + 9 bit time stamp 30% reduction in data rate Data-driven readout: q Maximum 20 Mpackets/s/double column n 40, 80, 160 and 320 MHz TMR clock domains in the periphery n 1 to 4 configurable serializers (GWT) n Similar to the GBT frame ESE Seminar 8 th November 2016 5

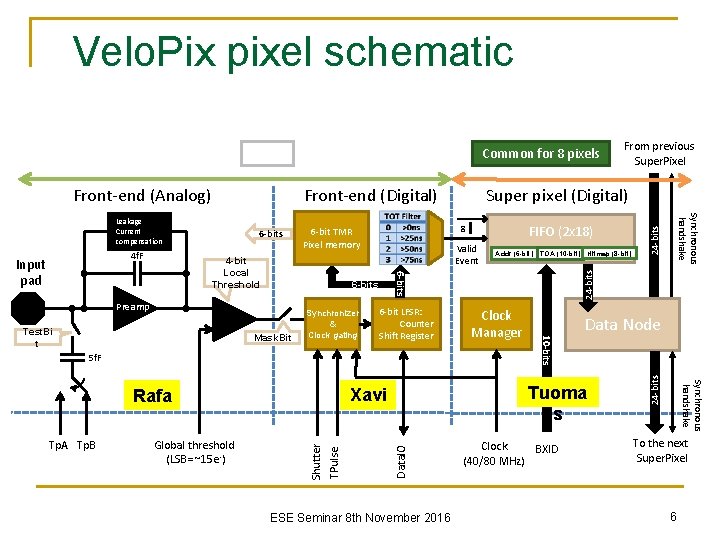

Velo. Pix pixel schematic 1 pixel 6 -bit LFSR: Counter Shift Register 5 f. F Data. IO Shutter TPulse Global threshold (LSB= ~15 e-) Data Node ESE Seminar 8 th November 2016 Clock BXID (40/80 MHz) Synchronous handshake Tp. A Tp. B Clock Manager Tuoma s Xavi Rafa TOA (10 -bit) Hitmap (8 -bit) 10 -bits Mask. Bit Synchronizer & Clock gating Addr (6 -bit) 24 -bits Valid Event 6 -bits Preamp FIFO (2 x 18) 24 -bits 4 -bit Local Threshold Test. Bi t 8 6 -bit TMR Pixel memory 6 -bits Input pad 6 -bits Synchronous handshake 4 f. F Super pixel (Digital) Front-end (Digital) Leakage Current compensation From previous Super. Pixel 24 -bits Front-end (Analog) Common for 8 pixels To the next Super. Pixel 6

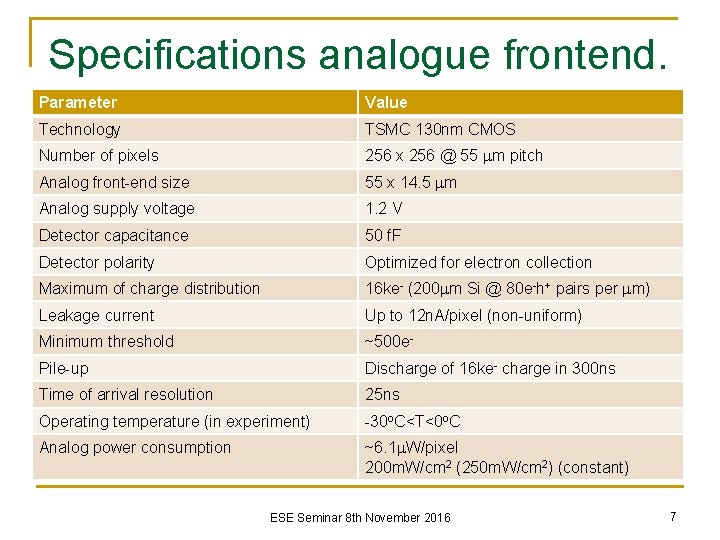

Specifications analogue frontend. Parameter Value Technology TSMC 130 nm CMOS Number of pixels 256 x 256 @ 55 mm pitch Analog front-end size 55 x 14. 5 mm Analog supply voltage 1. 2 V Detector capacitance 50 f. F Detector polarity Optimized for electron collection Maximum of charge distribution 16 ke- (200 mm Si @ 80 e-h+ pairs per mm) Leakage current Up to 12 n. A/pixel (non-uniform) Minimum threshold ~500 e- Pile-up Discharge of 16 ke- charge in 300 ns Time of arrival resolution 25 ns Operating temperature (in experiment) -30 o. C<T<0 o. C Analog power consumption ~6. 1 m. W/pixel 200 m. W/cm 2 (250 m. W/cm 2) (constant) ESE Seminar 8 th November 2016 7

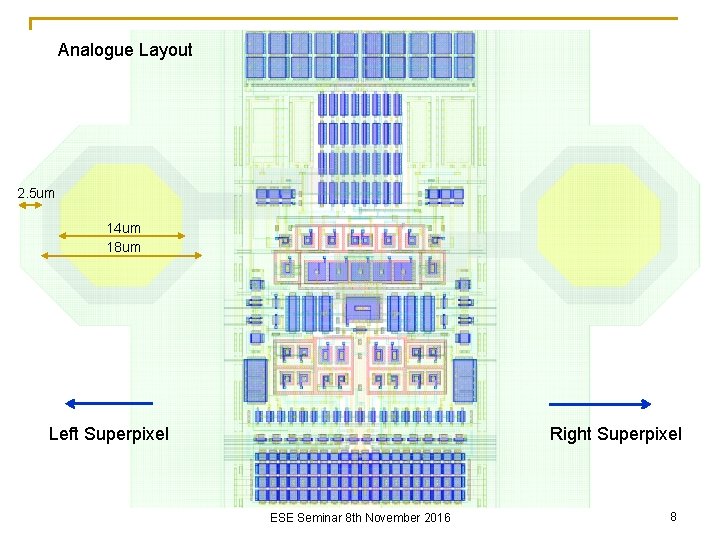

Analogue Layout 2. 5 um 14 um 18 um Left Superpixel Right Superpixel ESE Seminar 8 th November 2016 8

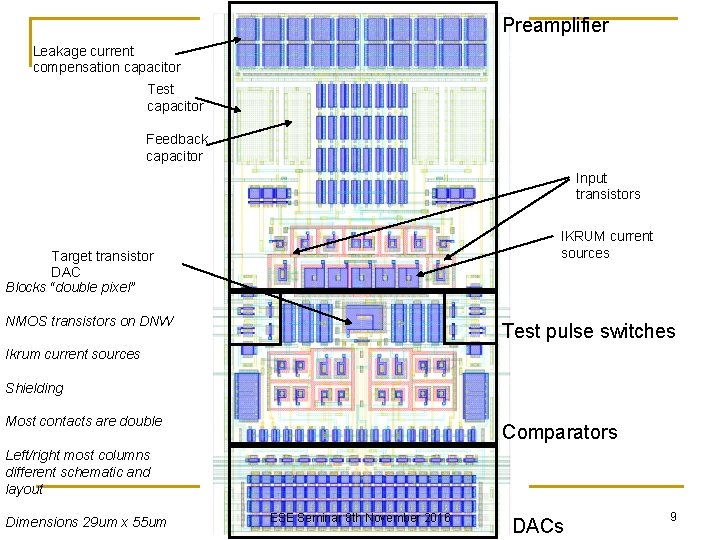

Preamplifier Leakage current compensation capacitor Test capacitor Feedback capacitor Input transistors IKRUM current sources Target transistor DAC Blocks “double pixel” NMOS transistors on DNW Test pulse switches Ikrum current sources Shielding Most contacts are double Comparators Left/right most columns different schematic and layout Dimensions 29 um x 55 um ESE Seminar 8 th November 2016 DACs 9

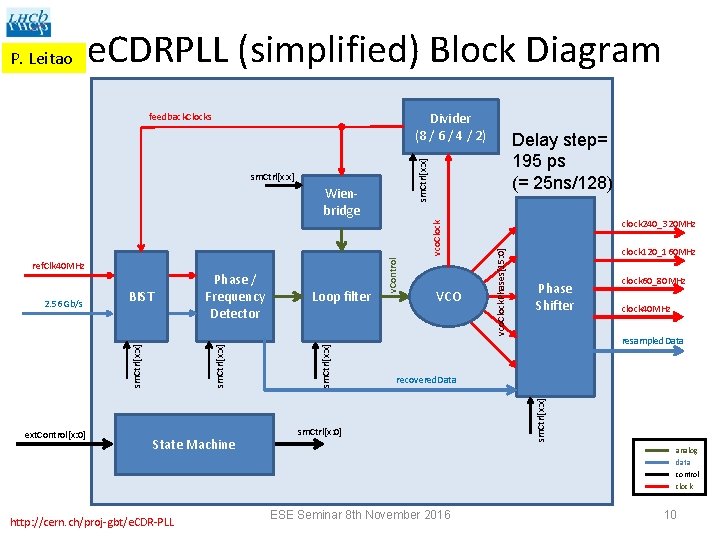

e. CDRPLL (simplified) Block Diagram Divider (8 / 6 / 4 / 2) sm. Ctrl[x: x] State Machine http: //cern. ch/proj-gbt/e. CDR-PLL VCO clock 240_320 MHz clock 120_160 MHz Phase Shifter clock 60_80 MHz clock 40 MHz resampled. Data recovered. Data sm. Ctrl[x: 0] sm. Ctrl[x: x] ext. Control[x: 0] Loop filter sm. Ctrl[x: x] BIST sm. Ctrl[x: x] 2. 56 Gb/s Phase / Frequency Detector v. Control vco. Clock Wienbridge ref. Clk 40 MHz Delay step= 195 ps (= 25 ns/128) sm. Ctrl[x: x] feedback. Clocks vco. Clock. Phases[15: 0] P. Leitao analog data control clock ESE Seminar 8 th November 2016 10

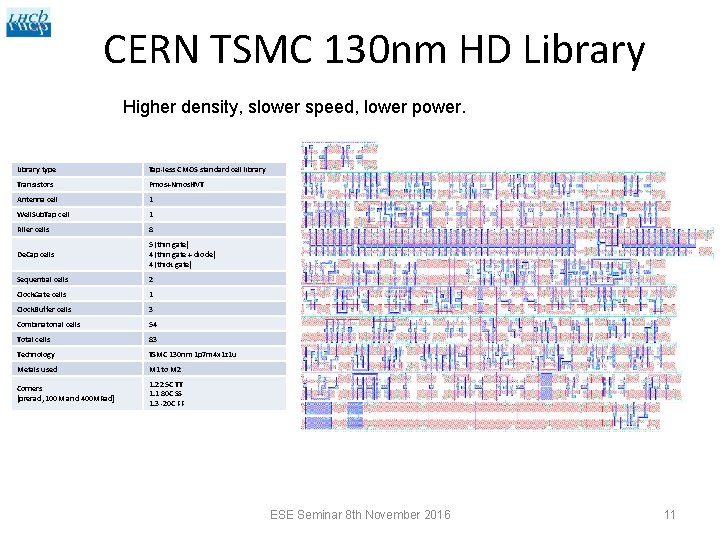

CERN TSMC 130 nm HD Library Higher density, slower speed, lower power. Library type Tap-less CMOS standard cell library Transistors Pmos+Nmos. HVT Antenna cell 1 Well. Sub. Tap cell 1 Filler cells 8 De. Cap cells 5 (thin gate) 4 (thin gate + diode) 4 (thick gate) Sequential cells 2 Clock. Gate cells 1 Clock. Buffer cells 3 Combinatorial cells 54 Total cells 83 Technology TSMC 130 nm 1 p 7 m 4 x 1 z 1 u Metals used M 1 to M 2 Corners [prerad, 100 M and 400 MRad] 1. 2 25 C TT 1. 1 80 C SS 1. 3 -20 C FF ESE Seminar 8 th November 2016 11

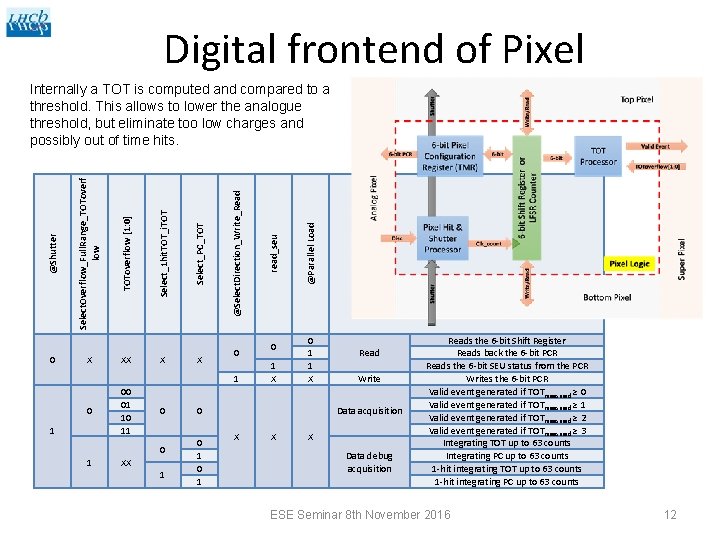

Digital frontend of Pixel 0 X XX 0 00 01 10 11 X X 0 1 1 0 0 1 XX 1 0 1 X @Parallel Load read_seu @Select. Direction_Write_Read Select_PC_TOT Select_1 hit. TOT_i. TOToverflow [1: 0] Select. Overflow_Full. Range_TOToverf low @Shutter Internally a TOT is computed and compared to a threshold. This allows to lower the analogue threshold, but eliminate too low charges and possibly out of time hits. 0 1 1 X 0 0 1 Read Write Data acquisition X X X Data debug acquisition Reads the 6 -bit Shift Register Reads back the 6 -bit PCR Reads the 6 -bit SEU status from the PCR Writes the 6 -bit PCR Valid event generated if TOTmeasured ≥ 0 Valid event generated if TOTmeasured ≥ 1 Valid event generated if TOTmeasured ≥ 2 Valid event generated if TOTmeasured ≥ 3 Integrating TOT up to 63 counts Integrating PC up to 63 counts 1 -hit integrating TOT up to 63 counts 1 -hit integrating PC up to 63 counts ESE Seminar 8 th November 2016 12

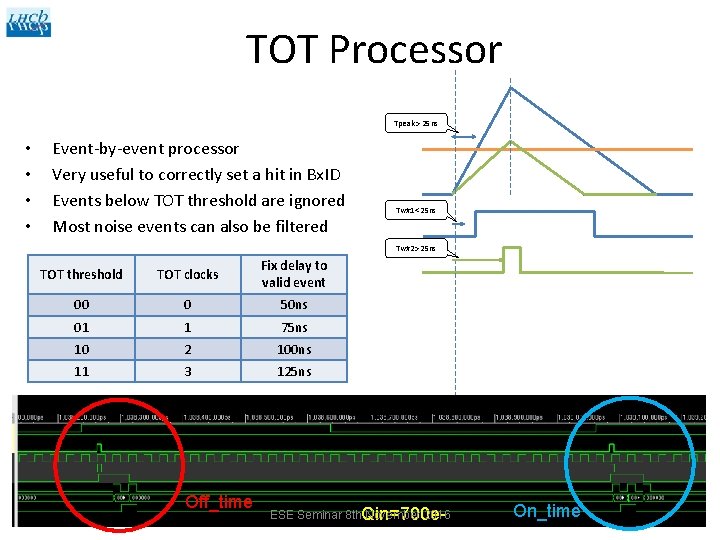

TOT Processor Tpeak > 25 ns • • Event-by-event processor Very useful to correctly set a hit in Bx. ID Events below TOT threshold are ignored Most noise events can also be filtered TOT threshold Tw#1< 25 ns Tw#2> 25 ns TOT clocks Fix delay to valid event 00 0 50 ns 01 1 75 ns 10 2 100 ns 11 3 125 ns Off_time ESE Seminar 8 th. Qin=700 e. November 2016 13 On_time

Double column datapath Sensor Timestamping @ 40 MHz 8 analog Front-ends 8 digital Front-ends FIFO Node FIFO Data Arbiter FIFO Previous Node 0 1 64 FIFOs FIFO Node Size = 2 packets Up to 20 Mpackets/s Analog pixel column Digital pixel column Super pixel column ESE Seminar 8 th November 2016 Register Next Node Arbiter is parametrised in column position Super pixel packet: Addr 6 b To. A 10 b hitmap 8 b 14

Periphery datapath 64 x up to 20 Mpackets/s Pixel Matrix 64 Eo. Cs Center Node 64 Eo. Cs Left Data Fabric 4. 8 Gbps per bus Data Node 19. 20 Gbps FIFO 160 Mpackets/s/node Right Data Fabric Lowest data rate in output Router/ Scramblers/ Framing ESE Seminar 8 th November 2016 4 x 5. 12 Gbps GWT link Data out 15

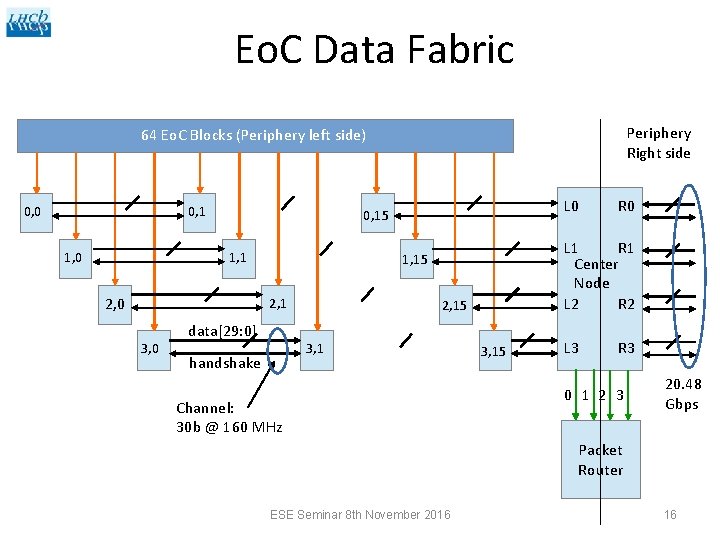

Eo. C Data Fabric Periphery Right side 64 Eo. C Blocks (Periphery left side) 0, 0 0, 1 1, 0 1, 1 2, 0 data[29: 0] 2, 15 3, 1 handshake Channel: 30 b @ 160 MHz R 0 L 1 R 1 Center Node L 2 R 2 1, 15 2, 1 3, 0 L 0 0, 15 3, 15 L 3 R 3 0 1 2 3 20. 48 Gbps Packet Router ESE Seminar 8 th November 2016 16

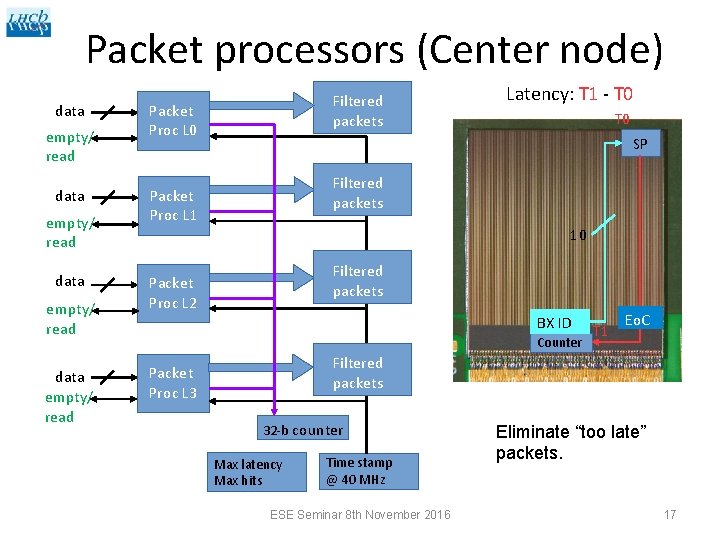

Packet processors (Center node) data empty/ read Filtered packets Packet Proc L 0 Latency: T 1 - T 0 SP Filtered packets Packet Proc L 1 10 Filtered packets Packet Proc L 2 BX ID Counter T 1 Eo. C Filtered packets Packet Proc L 3 32 -b counter Max latency Max hits Time stamp @ 40 MHz ESE Seminar 8 th November 2016 Eliminate “too late” packets. 17

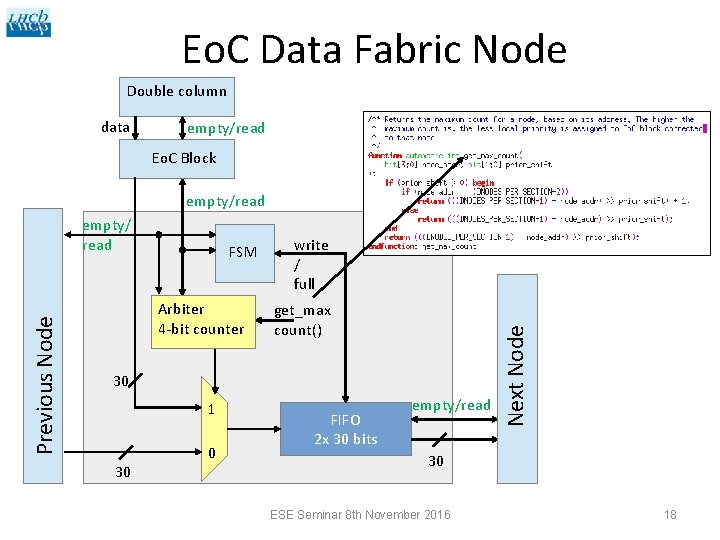

Eo. C Data Fabric Node Double column data empty/read Eo. C Block empty/read FSM Arbiter 4 -bit counter write / full get_max count() 30 1 30 0 FIFO 2 x 30 bits empty/read Next Node Previous Node empty/ read 30 ESE Seminar 8 th November 2016 18

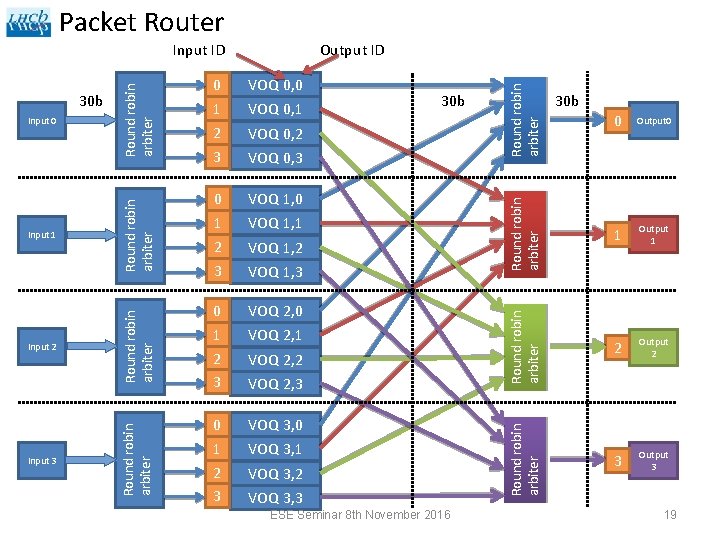

Packet Router VOQ 2, 0 VOQ 2, 1 VOQ 2, 2 VOQ 2, 3 0 1 2 3 VOQ 3, 0 VOQ 3, 1 VOQ 3, 2 VOQ 3, 3 ESE Seminar 8 th November 2016 Round robin arbiter 0 1 2 3 0 Output 0 Round robin arbiter VOQ 1, 0 VOQ 1, 1 VOQ 1, 2 VOQ 1, 3 30 b 1 Output 1 Round robin arbiter Input 3 0 1 2 3 30 b 2 Output 2 Round robin arbiter Input 1 VOQ 0, 0 VOQ 0, 1 VOQ 0, 2 VOQ 0, 3 Round robin arbiter Input 0 0 1 2 3 Round robin arbiter 30 b Output ID Round robin arbiter Input ID 3 Output 3 19

![Router and output block Fixed latency Channel Mask [3: 0] Eo. C Data Fabric Router and output block Fixed latency Channel Mask [3: 0] Eo. C Data Fabric](http://slidetodoc.com/presentation_image_h/100c6cdcfa41c98734090afd54a0be34/image-20.jpg)

Router and output block Fixed latency Channel Mask [3: 0] Eo. C Data Fabric f 2 r[0] f 2 r[1] f 2 r[2] Packet Router (4 x 4 crossbar) f 2 r[3] 160 MHz 4 x 128 b 4 x 30 b Scrambler Framing Serializer 160 MHz 40 MHz 128 b registers: parity + header ESE Seminar 8 th November 2016 320 MHz DDR 16 -to-1 b ser. Output drivers 20

![GWT (NIKHEF) • Low power 5. 12 Gbps byte-interleaved serializer and wireline transmitter] VDD_CORE GWT (NIKHEF) • Low power 5. 12 Gbps byte-interleaved serializer and wireline transmitter] VDD_CORE](http://slidetodoc.com/presentation_image_h/100c6cdcfa41c98734090afd54a0be34/image-21.jpg)

GWT (NIKHEF) • Low power 5. 12 Gbps byte-interleaved serializer and wireline transmitter] VDD_CORE 3Ω data 8 bit @ 320 MHz Reg <8: 15> VDD_HS MUX 16 phases Driver Reg <0: 7> dc: 9 m. A , ripples: 2 m. A p-p CMOS data 8 bit @ 320 MHz 5Ω serialized data @ 5. 12 Gbps posedge negedge ripples: 0. 05 m. A p-p 534 p. F Multi-phase DLL Edgecombiner ph_0 ph_1 ph_2 5Ω GND_HS ph_3 ph_14 ph_15 ~20 m. W/channel 3Ω GND_CORE ESE Seminar 8 th November 2016 21

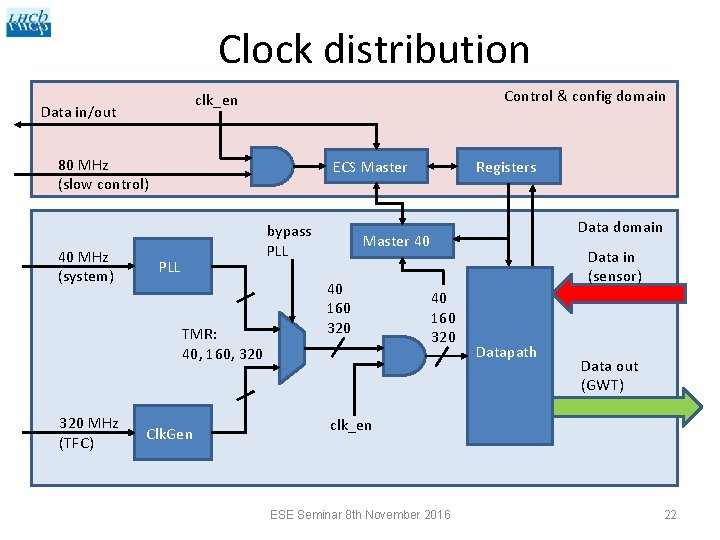

Clock distribution Control & config domain clk_en Data in/out 80 MHz (slow control) 40 MHz (system) ECS Master bypass PLL TMR: 40, 160, 320 MHz (TFC) Clk. Gen Registers Data domain Master 40 40 160 320 Data in (sensor) 40 160 320 Datapath Data out (GWT) clk_en ESE Seminar 8 th November 2016 22

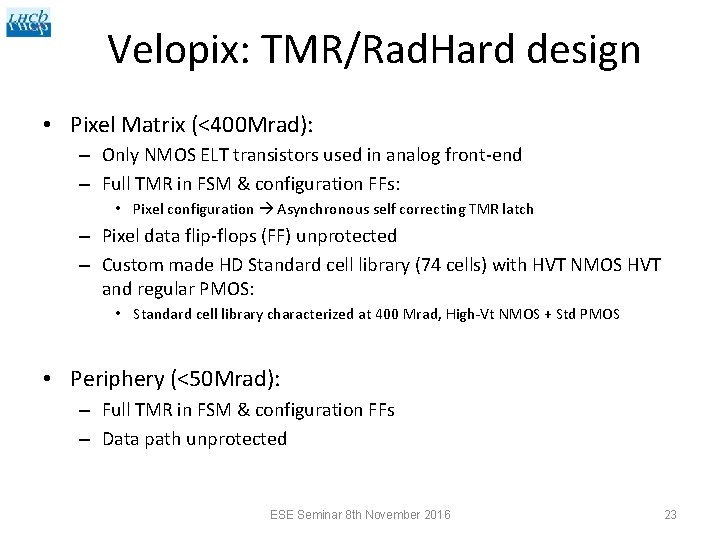

Velopix: TMR/Rad. Hard design • Pixel Matrix (<400 Mrad): – Only NMOS ELT transistors used in analog front-end – Full TMR in FSM & configuration FFs: • Pixel configuration Asynchronous self correcting TMR latch – Pixel data flip-flops (FF) unprotected – Custom made HD Standard cell library (74 cells) with HVT NMOS HVT and regular PMOS: • Standard cell library characterized at 400 Mrad, High-Vt NMOS + Std PMOS • Periphery (<50 Mrad): – Full TMR in FSM & configuration FFs – Data path unprotected ESE Seminar 8 th November 2016 23

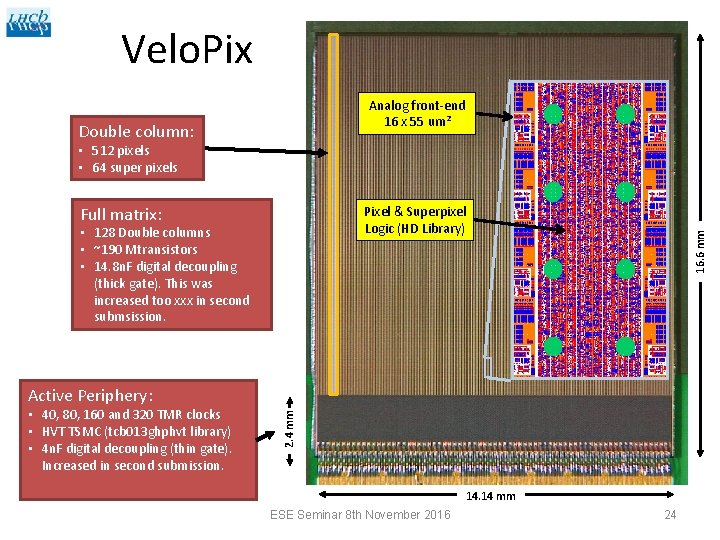

Velo. Pix Analog front-end 16 x 55 um² Double column: • 512 pixels • 64 super pixels Full matrix: • 128 Double columns • ~190 Mtransistors • 14. 8 n. F digital decoupling (thick gate). This was increased too xxx in second submsission. 16. 6 mm Pixel & Superpixel Logic (HD Library) • 40, 80, 160 and 320 TMR clocks • HVT TSMC (tcb 013 ghphvt library) • 4 n. F digital decoupling (thin gate). Increased in second submission. 2. 4 mm Active Periphery: 14. 14 mm ESE Seminar 8 th November 2016 24

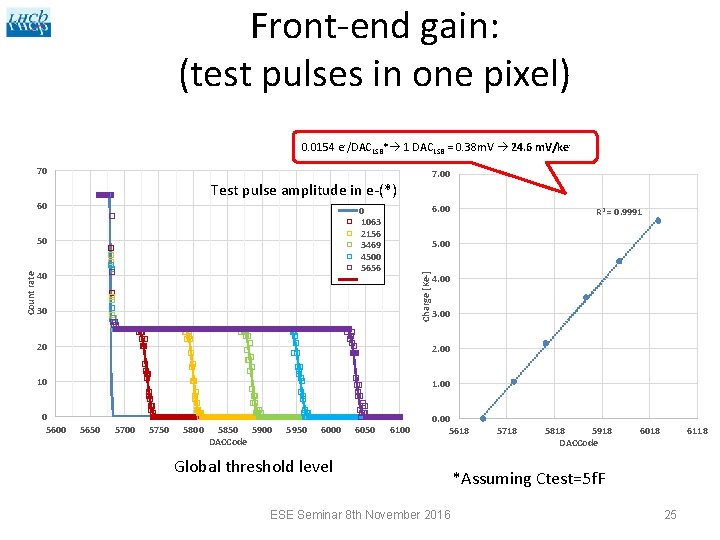

Front-end gain: (test pulses in one pixel) 0. 0154 e-/DACLSB* 1 DACLSB = 0. 38 m. V 24. 6 m. V/ke 70 Test pulse amplitude in e-(*) 60 40 5. 00 4. 00 30 3. 00 20 2. 00 10 1. 00 0 5600 R 2 = 0. 9991 Charge [Ke-] Count rate 6. 00 0 1063 2156 3469 4500 5656 50 7. 00 5650 5700 5750 5800 5850 5900 DACCode 5950 6000 6050 6100 0. 00 5618 Global threshold level ESE Seminar 8 th November 2016 5718 5818 5918 DACCode 6018 6118 *Assuming Ctest=5 f. F 25

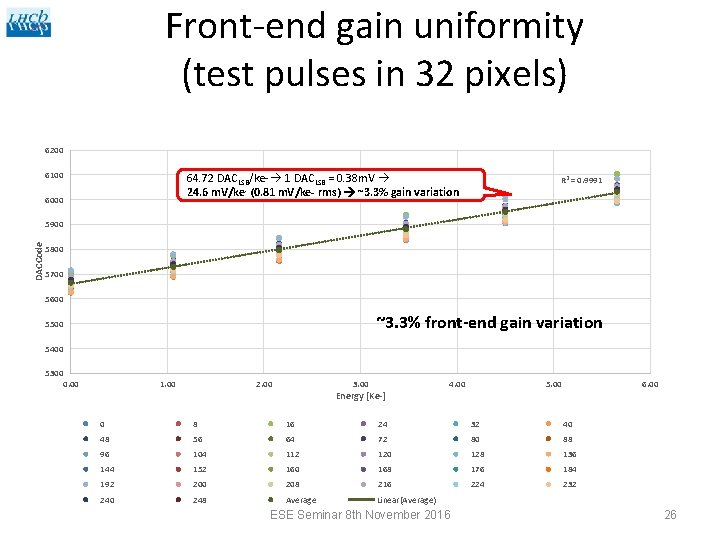

Front-end gain uniformity (test pulses in 32 pixels) 6200 6100 64. 72 DACLSB/ke- 1 DACLSB = 0. 38 m. V 24. 6 m. V/ke- (0. 81 m. V/ke- rms) ~3. 3% gain variation 6000 R 2 = 0. 9991 DACCode 5900 5800 5700 5600 ~3. 3% front-end gain variation 5500 5400 5300 0. 00 1. 00 2. 00 3. 00 Energy [Ke-] 4. 00 5. 00 6. 00 0 8 16 24 32 40 48 56 64 72 80 88 96 104 112 120 128 136 144 152 160 168 176 184 192 200 208 216 224 232 240 248 Average Linear(Average) ESE Seminar 8 th November 2016 26

![Pixel ENC. [Threshold scan over noise floor in PC mode] 8 pixels Typically ~60 Pixel ENC. [Threshold scan over noise floor in PC mode] 8 pixels Typically ~60](http://slidetodoc.com/presentation_image_h/100c6cdcfa41c98734090afd54a0be34/image-27.jpg)

Pixel ENC. [Threshold scan over noise floor in PC mode] 8 pixels Typically ~60 enc ESE Seminar 8 th November 2016 27

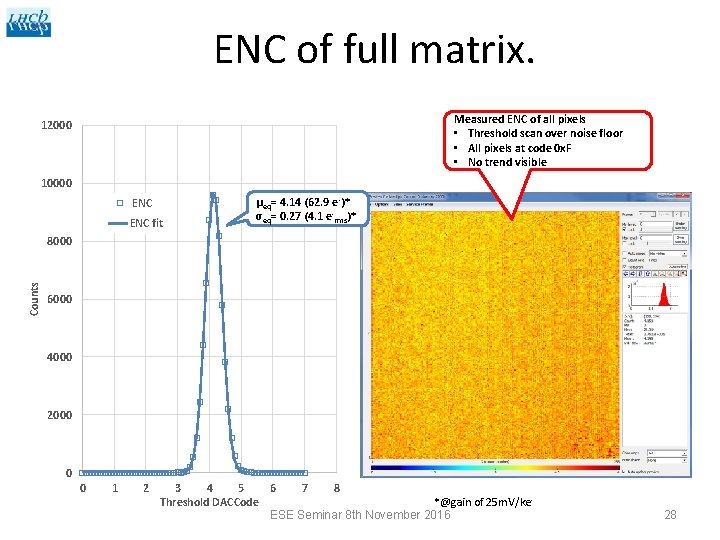

ENC of full matrix. Measured ENC of all pixels • Threshold scan over noise floor • All pixels at code 0 x. F • No trend visible 12000 10000 ENC fit µeq= 4. 14 (62. 9 e -)* σeq= 0. 27 (4. 1 e -rms)* Counts 8000 6000 4000 2000 0 0 1 2 3 4 5 6 7 8 *@gain of 25 m. V/ke. Threshold DACCode ESE Seminar 8 th November 2016 28

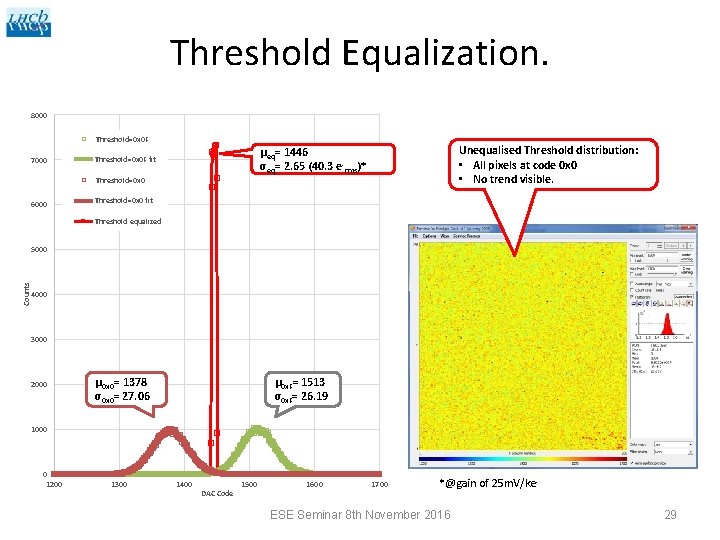

Threshold Equalization. 8000 Threshold=0 x 0 F 7000 Threshold=0 x 0 6000 Unequalised Threshold distribution: • All pixels at code 0 x 0 • No trend visible. µeq= 1446 σeq= 2. 65 (40. 3 e -rms)* Threshold=0 x 0 F fit Threshold=0 x 0 fit Threshold equalized Counts 5000 4000 3000 2000 µ 0 x 0= 1378 σ0 x 0= 27. 06 µ 0 x. F= 1513 σ0 x. F= 26. 19 1000 0 1200 1300 1400 DAC Code 1500 1600 1700 *@gain of 25 m. V/ke- ESE Seminar 8 th November 2016 29

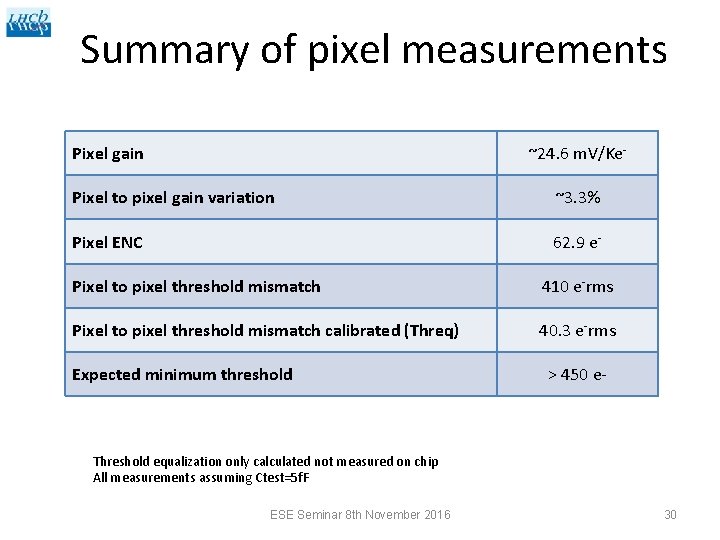

Summary of pixel measurements Pixel gain ~24. 6 m. V/Ke- Pixel to pixel gain variation ~3. 3% Pixel ENC 62. 9 e- Pixel to pixel threshold mismatch 410 e-rms Pixel to pixel threshold mismatch calibrated (Threq) 40. 3 e-rms Expected minimum threshold > 450 e- Threshold equalization only calculated not measured on chip All measurements assuming Ctest=5 f. F ESE Seminar 8 th November 2016 30

2/24/2021 Brainstorming CPPM 31

- Slides: 31