Vector Potential Equivalent Circuit Based on PEEC Inversion

Vector Potential Equivalent Circuit Based on PEEC Inversion Hao Yu and Lei He Electrical Engineering Department, UCLA http: //eda. ee. ucla. edu Partially Sponsored by NSF Career Award (0093273) , and UC-Micro fund from Analog Devices, Intel and LSI Logic

Outline v Introduction v Vector Potential Equivalent Circuit Model v VPEC Property and Sparsification v Conclusions and Future Work

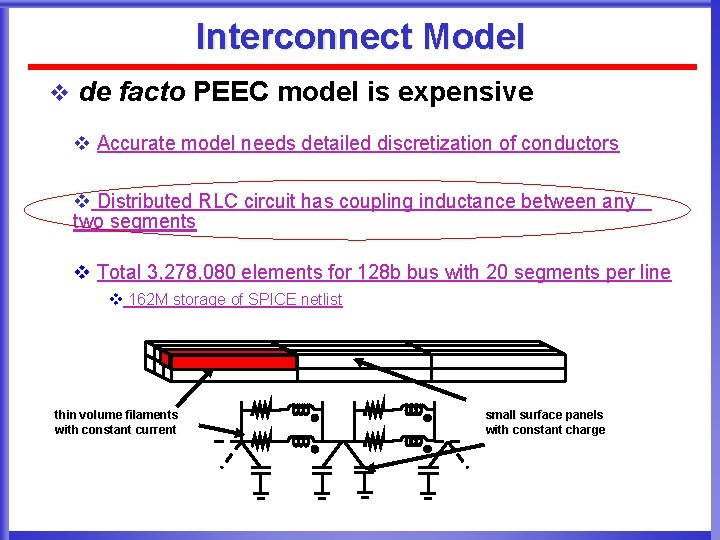

Interconnect Model v de facto PEEC model is expensive v Accurate model needs detailed discretization of conductors v Distributed RLC circuit has coupling inductance between any two segments v Total 3, 278, 080 elements for 128 b bus with 20 segments per line v 162 M storage of SPICE netlist thin volume filaments with constant current small surface panels with constant charge

Challenge of Inductance Sparisification v Partial inductance matrix L is not diagonal dominant v Direct truncation results loss of passivity v Existing passivity-guaranteed sparsification methods lack accuracy or theoretical justification v v Returned-loop [Shepard: TCAD’ 00] Shift-truncation (shell) [Krauter: ICCAD’ 95] K-element [Devgan: ICCAD’ 00] Localized VPEC [Pacelli: ICCAD’ 02]

K-Element Method v K-method v Observe that the inversion of L is M-matrix [Devgan: ICCAD’ 00] v Need to extend SPICE to simulate K-element [Ji: DAC’ 01] v Windowing v Extract the K-elements of sub-matrices to avoid full inversion [Beattie: DATE’ 01] v Wire-duplication v Improve the accuracy of windowing method [Zhong: ICCAD’ 02, DAC’ 03] v Inductwise v Heuristic bi-section the longest wire to guarantee K as M-matrix [Chen: ICCAD’ 02]

Contribution of Our Paper v Derive inversion based VPEC model from first principles v Replace inductances with effective magnetic resistances v Develop closed-formula for effective resistances v Enable direct and faster simulation in SPICE v Prove that circuit matrix in VPEC model is strictly diagonal dominant and hence passive v Enable various passivity preserved sparsifications

Outline v Introduction v Vector Potential Equivalent Circuit Model v VPEC circuit model v Inversion based VPEC v Accuracy comparison v VPEC Property and Sparsification v Conclusions and Future Work

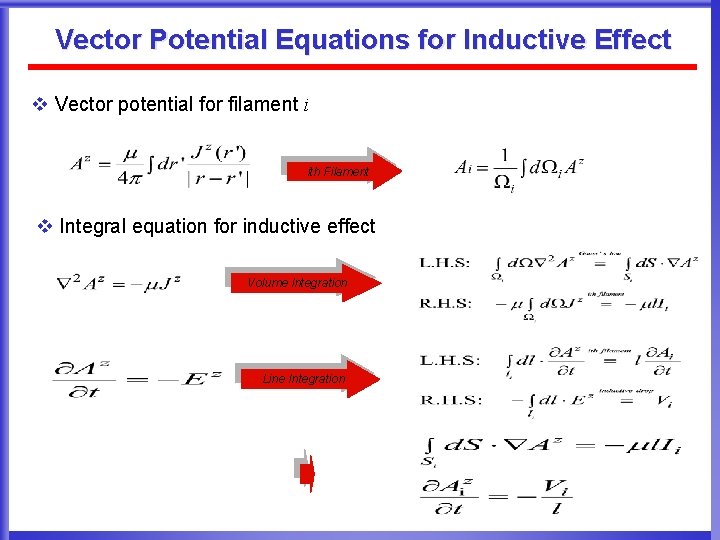

Vector Potential Equations for Inductive Effect v Vector potential for filament i ith Filament v Integral equation for inductive effect Volume Integration Line Integration

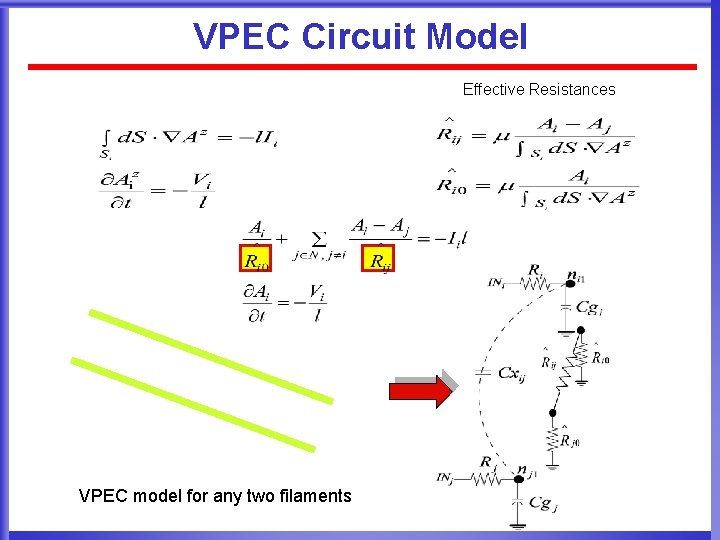

VPEC Circuit Model Effective Resistances VPEC model for any two filaments

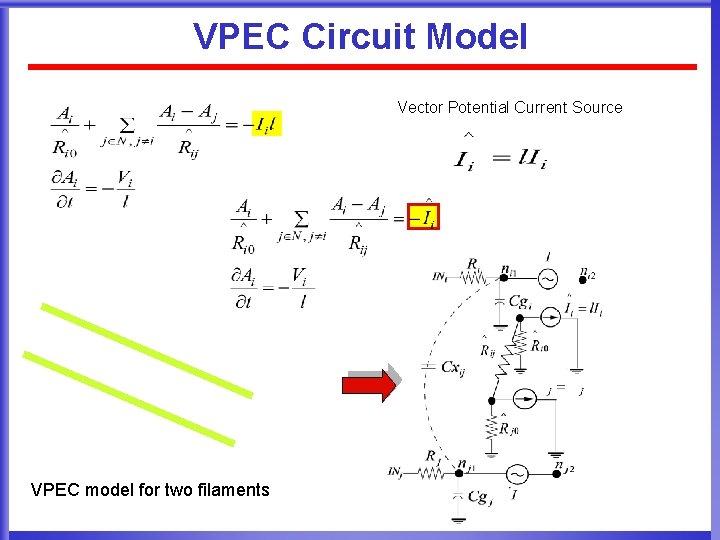

VPEC Circuit Model Vector Potential Current Source VPEC model for two filaments

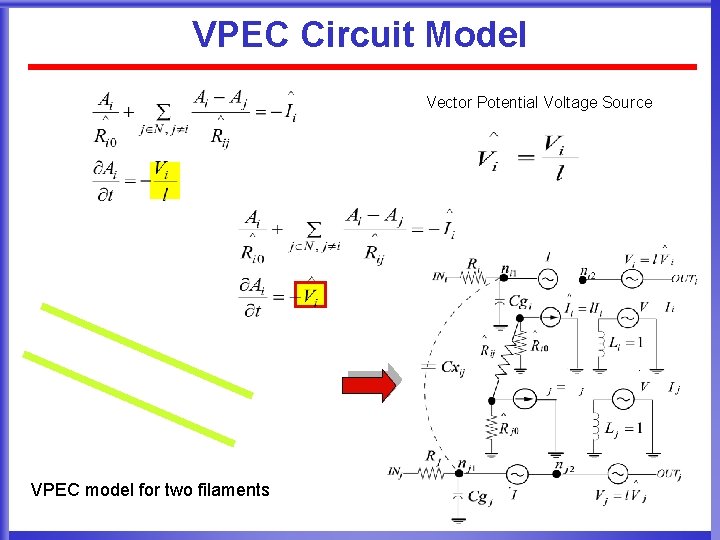

VPEC Circuit Model Vector Potential Voltage Source VPEC model for two filaments

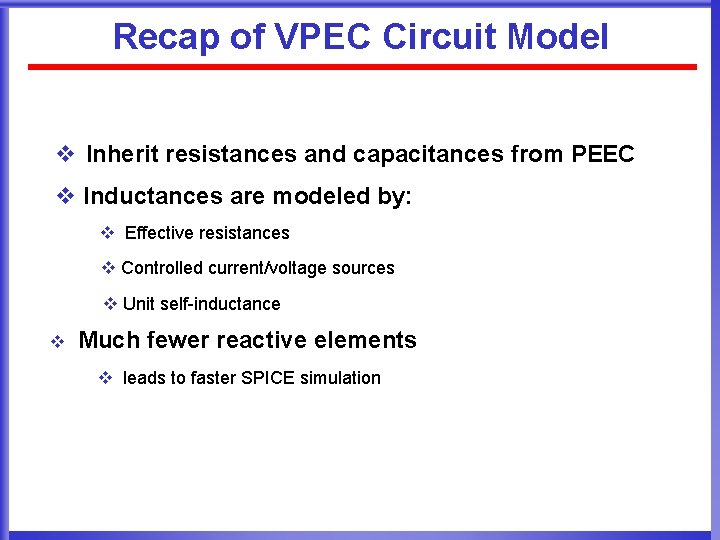

Recap of VPEC Circuit Model v Inherit resistances and capacitances from PEEC v Inductances are modeled by: v Effective resistances v Controlled current/voltage sources v Unit self-inductance v Much fewer reactive elements v leads to faster SPICE simulation

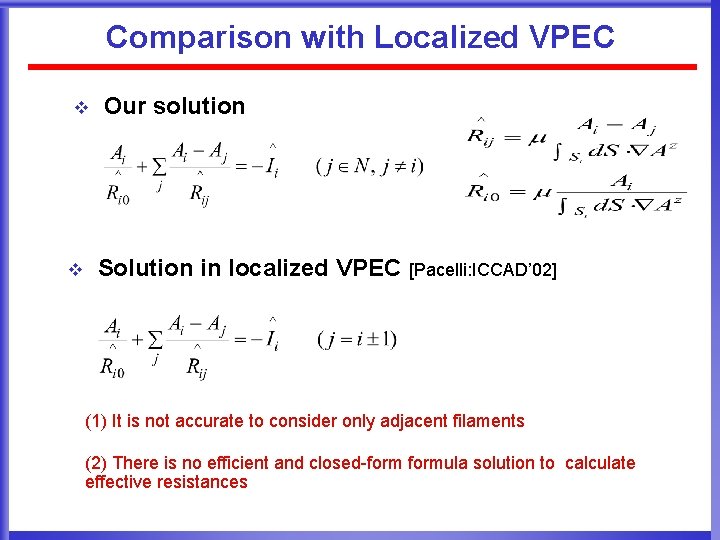

Comparison with Localized VPEC v v Our solution Solution in localized VPEC [Pacelli: ICCAD’ 02] (1) It is not accurate to consider only adjacent filaments (2) There is no efficient and closed-formula solution to calculate effective resistances

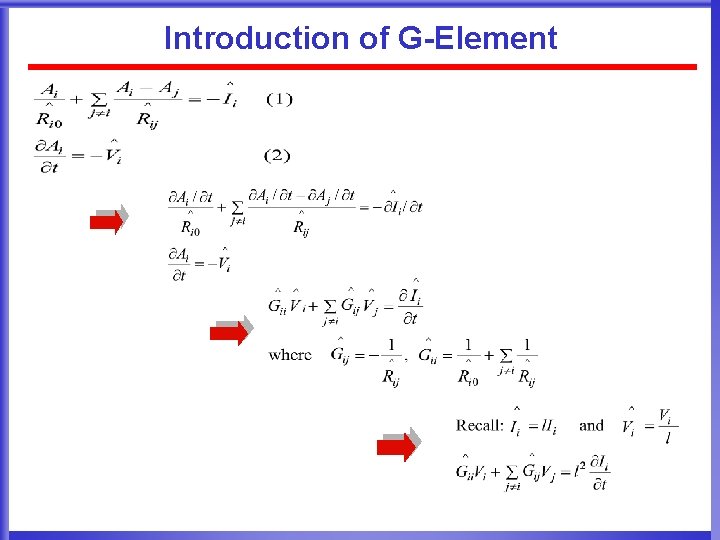

Introduction of G-Element

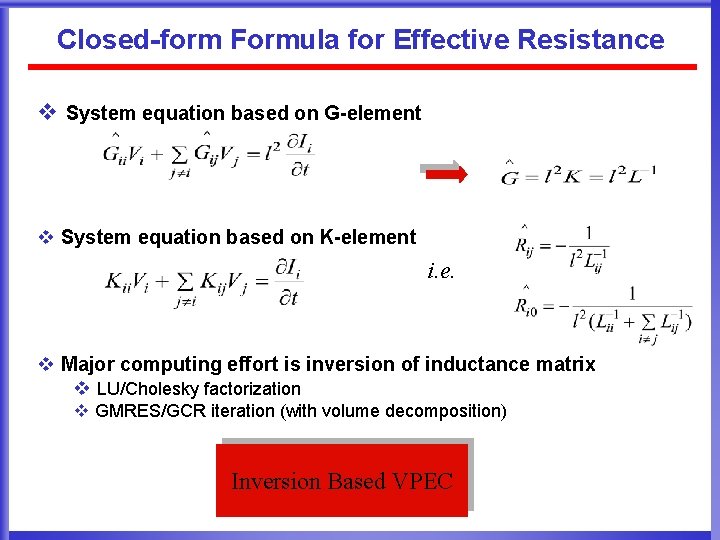

Closed-form Formula for Effective Resistance v System equation based on G-element v System equation based on K-element i. e. v Major computing effort is inversion of inductance matrix v LU/Cholesky factorization v GMRES/GCR iteration (with volume decomposition) Inversion Based VPEC

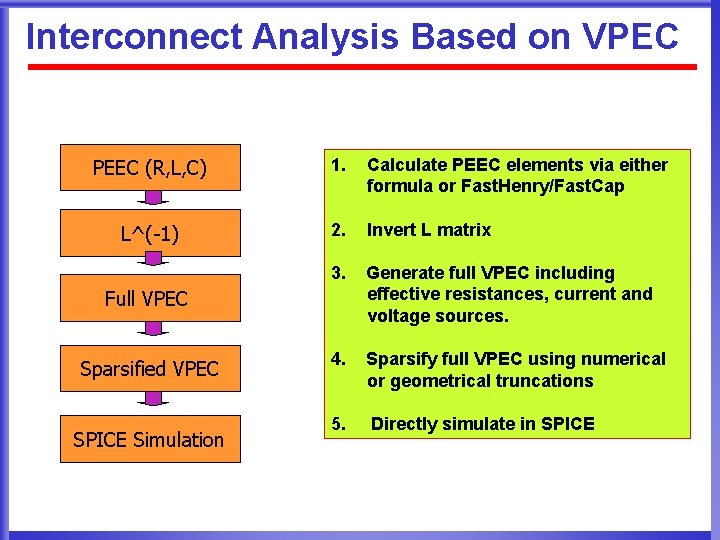

Interconnect Analysis Based on VPEC PEEC (R, L, C) 1. Calculate PEEC elements via either formula or Fast. Henry/Fast. Cap L^(-1) 2. Invert L matrix 3. Generate full VPEC including effective resistances, current and voltage sources. 4. Sparsify full VPEC using numerical or geometrical truncations 5. Directly simulate in SPICE Full VPEC Sparsified VPEC SPICE Simulation

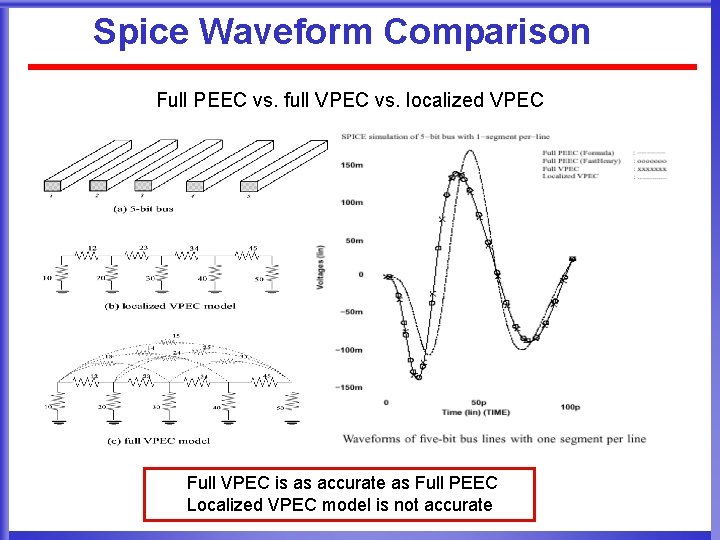

Spice Waveform Comparison Full PEEC vs. full VPEC vs. localized VPEC Full VPEC is as accurate as Full PEEC Localized VPEC model is not accurate

Spiral Inductor Non-bus Structure: Three-turn single layer on-chip spiral inductor Full VPEC model is accurate and can be applied for general layout

Outline v Introduction v Vector Potential Equivalent Circuit Model v VPEC Property and Sparsification v Conclusions and Future Work

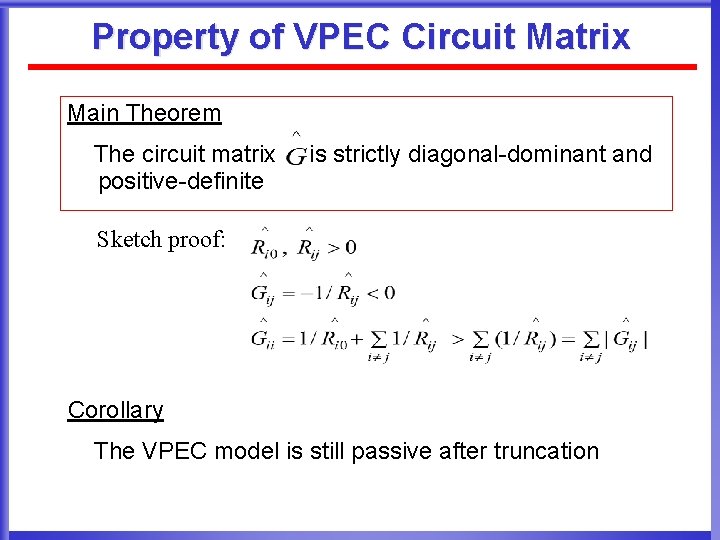

Property of VPEC Circuit Matrix Main Theorem The circuit matrix positive-definite is strictly diagonal-dominant and Sketch proof: Corollary The VPEC model is still passive after truncation

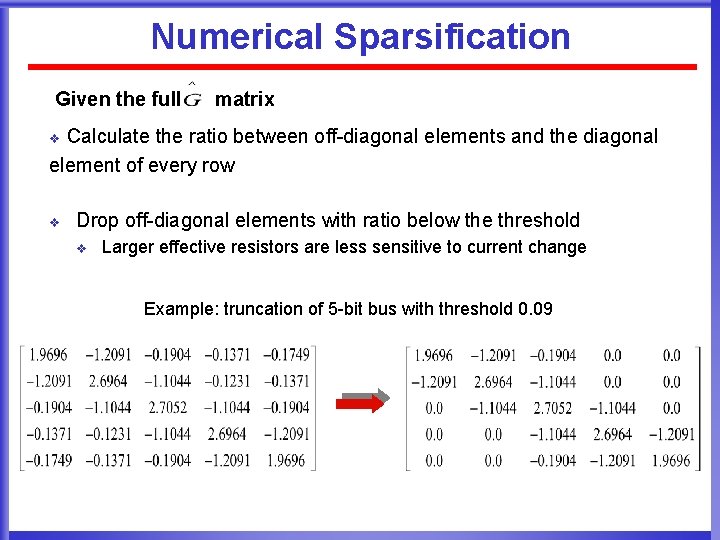

Numerical Sparsification Given the full matrix Calculate the ratio between off-diagonal elements and the diagonal element of every row v v Drop off-diagonal elements with ratio below the threshold v Larger effective resistors are less sensitive to current change Example: truncation of 5 -bit bus with threshold 0. 09

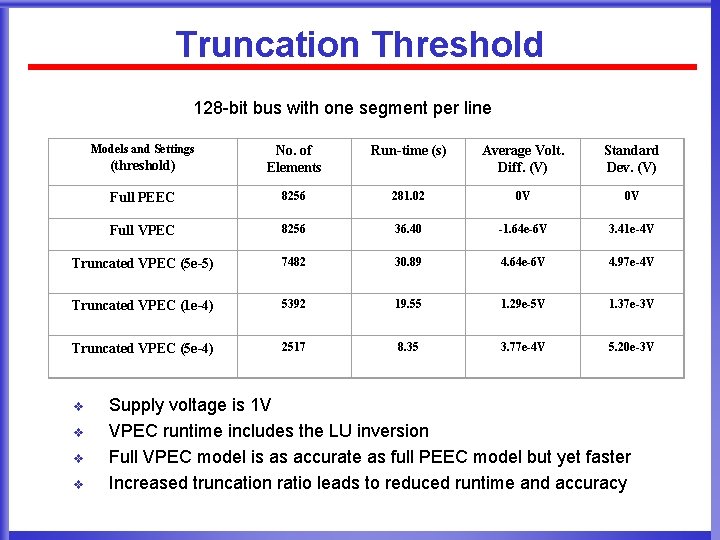

Truncation Threshold 128 -bit bus with one segment per line Models and Settings (threshold) No. of Elements Run-time (s) Average Volt. Diff. (V) Standard Dev. (V) Full PEEC 8256 281. 02 0 V 0 V Full VPEC 8256 36. 40 -1. 64 e-6 V 3. 41 e-4 V Truncated VPEC (5 e-5) 7482 30. 89 4. 64 e-6 V 4. 97 e-4 V Truncated VPEC (1 e-4) 5392 19. 55 1. 29 e-5 V 1. 37 e-3 V Truncated VPEC (5 e-4) 2517 8. 35 3. 77 e-4 V 5. 20 e-3 V v v Supply voltage is 1 V VPEC runtime includes the LU inversion Full VPEC model is as accurate as full PEEC model but yet faster Increased truncation ratio leads to reduced runtime and accuracy

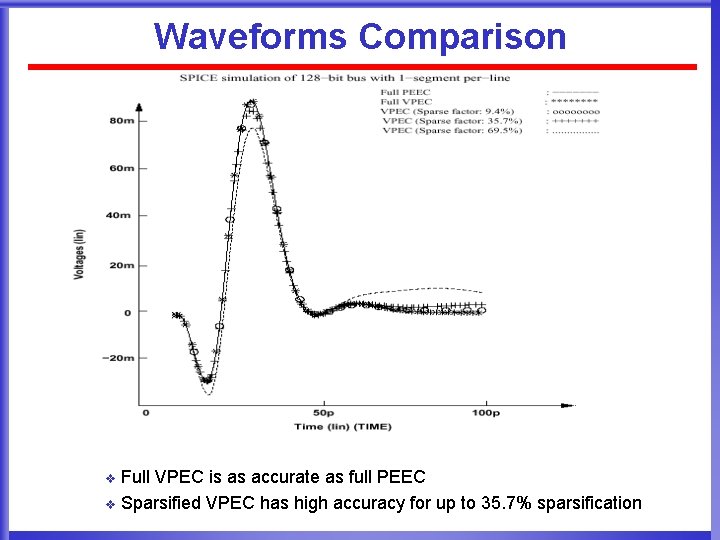

Waveforms Comparison Full VPEC is as accurate as full PEEC v Sparsified VPEC has high accuracy for up to 35. 7% sparsification v

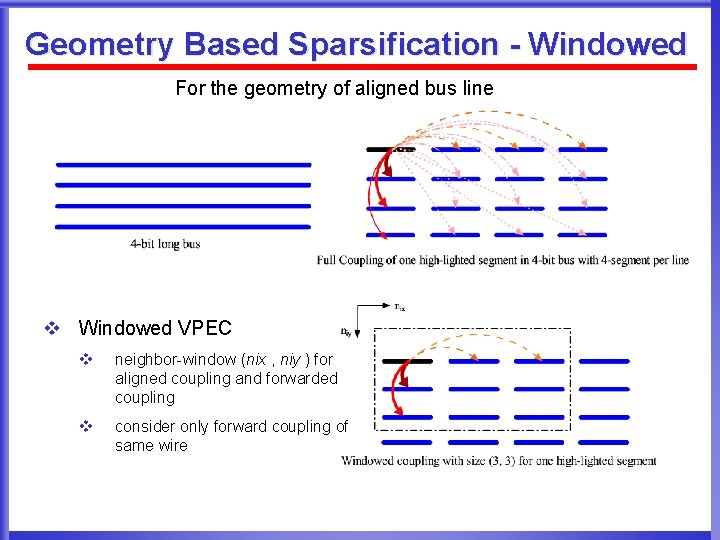

Geometry Based Sparsification - Windowed For the geometry of aligned bus line v Windowed VPEC v neighbor-window (nix , niy ) for aligned coupling and forwarded coupling v consider only forward coupling of same wire

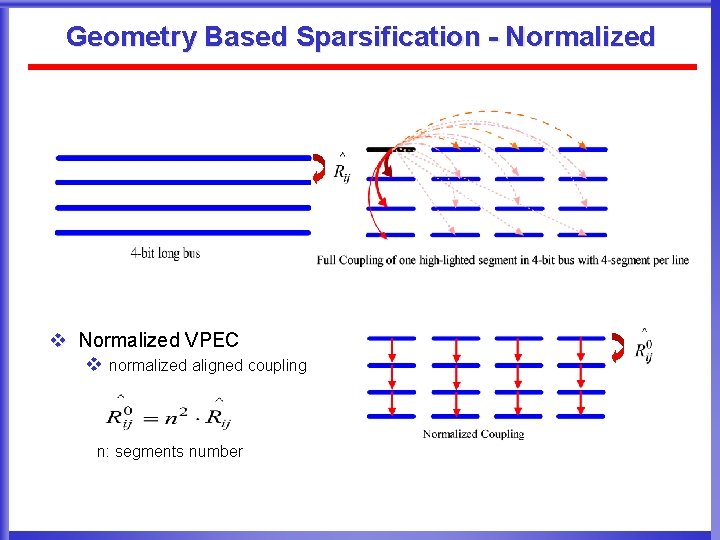

Geometry Based Sparsification - Normalized v Normalized VPEC v normalized aligned coupling n: segments number

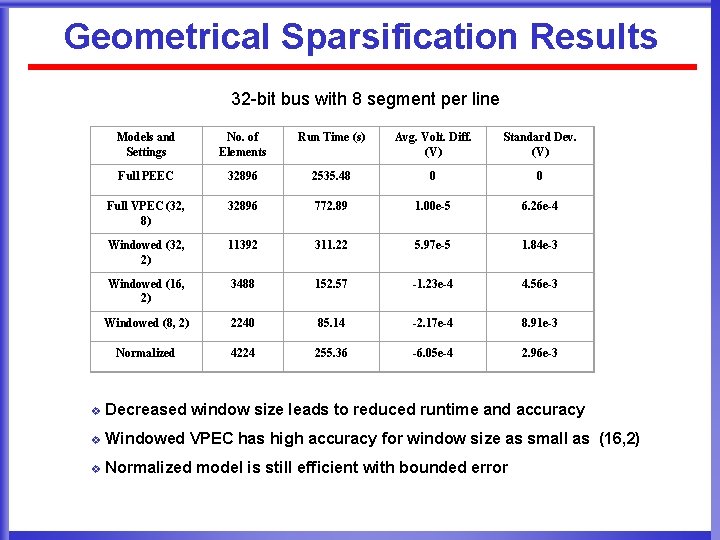

Geometrical Sparsification Results 32 -bit bus with 8 segment per line Models and Settings No. of Elements Run Time (s) Avg. Volt. Diff. (V) Standard Dev. (V) Full PEEC 32896 2535. 48 0 0 Full VPEC (32, 8) 32896 772. 89 1. 00 e-5 6. 26 e-4 Windowed (32, 2) 11392 311. 22 5. 97 e-5 1. 84 e-3 Windowed (16, 2) 3488 152. 57 -1. 23 e-4 4. 56 e-3 Windowed (8, 2) 2240 85. 14 -2. 17 e-4 8. 91 e-3 Normalized 4224 255. 36 -6. 05 e-4 2. 96 e-3 v Decreased window size leads to reduced runtime and accuracy v Windowed VPEC has high accuracy for window size as small as (16, 2) v Normalized model is still efficient with bounded error

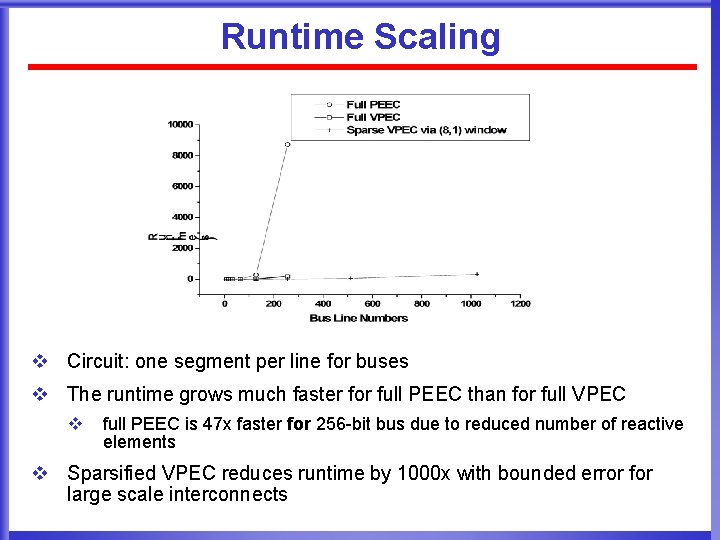

Runtime Scaling v Circuit: one segment per line for buses v The runtime grows much faster for full PEEC than for full VPEC v full PEEC is 47 x faster for 256 -bit bus due to reduced number of reactive elements v Sparsified VPEC reduces runtime by 1000 x with bounded error for large scale interconnects

Conclusions and Future Work v Derived inversion based VPEC from first principle v Shown that Full VPEC has the same accuracy as full PEEC but faster v Proved that VPEC model remains passive after truncation v To work on v. Fast iteration algorithms for inversion of L v. Model-order-reduction for VPEC (see ICCAD’ 2006)

- Slides: 28