VDD VDD M 16 M 3 M 4

- Slides: 14

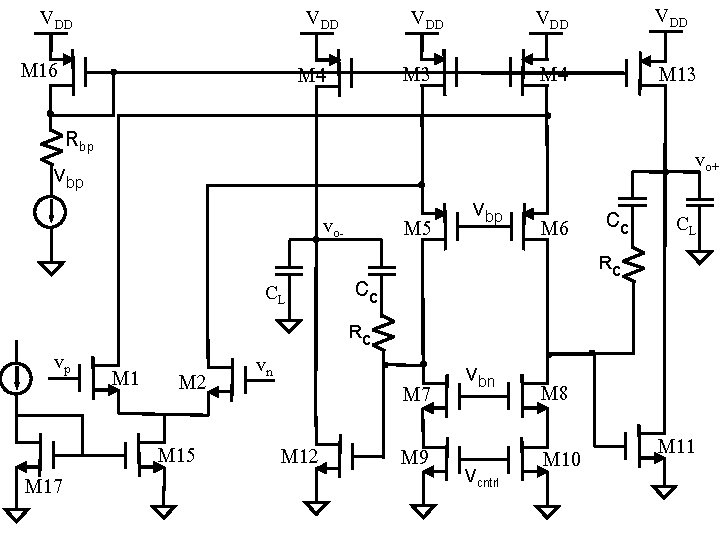

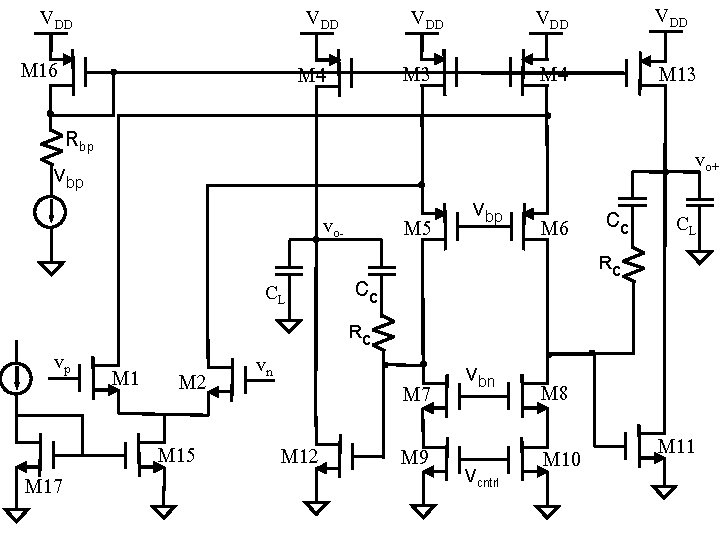

VDD VDD M 16 M 3 M 4 VDD M 4 M 13 Rbp vo+ vbp vo. CL M 5 vbp M 6 cc CL Rc cc Rc vp M 1 M 2 M 15 M 17 vn M 7 M 12 M 9 vbn Vcntrl M 8 M 10 M 11

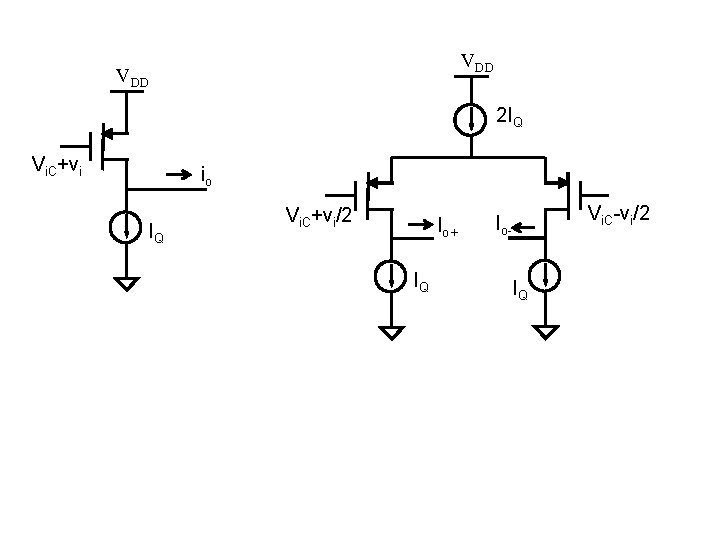

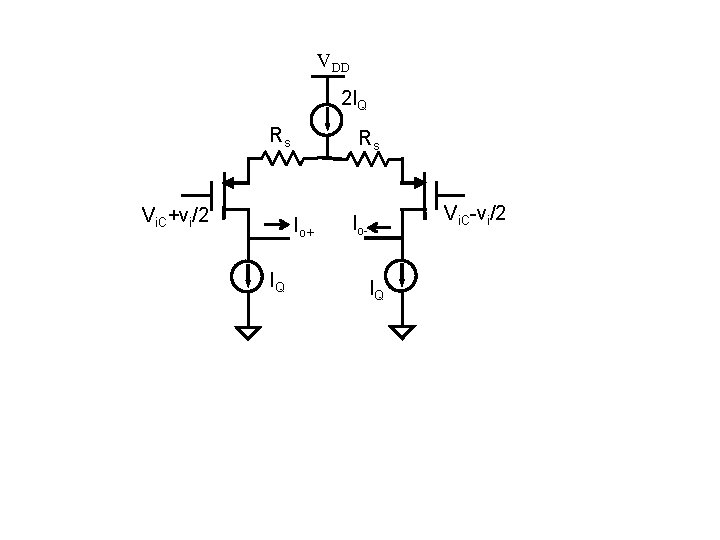

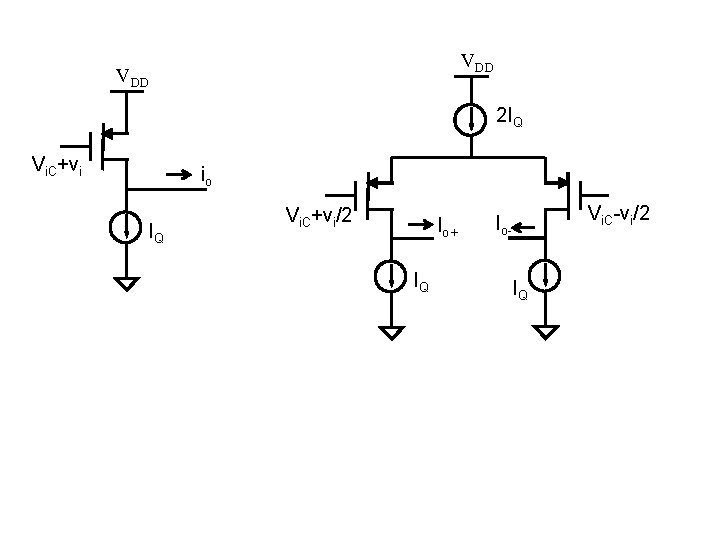

VDD 2 IQ Vi. C+vi io IQ Vi. C+vi/2 Io+ IQ Io. IQ Vi. C-vi/2

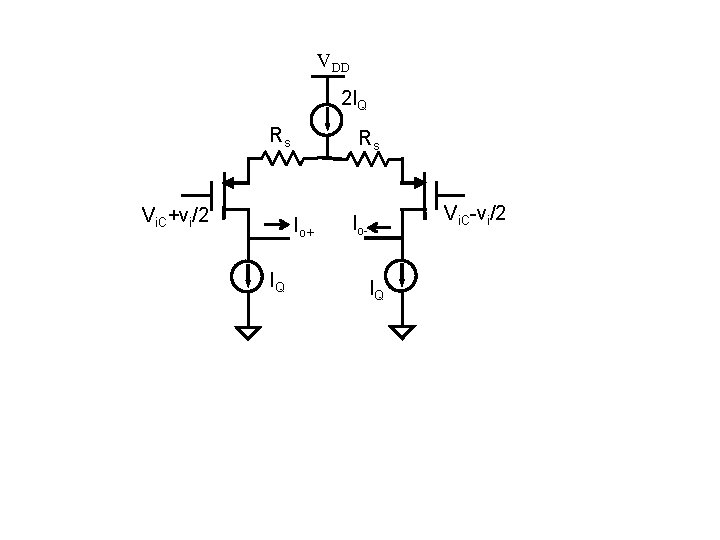

VDD 2 IQ Rs Vi. C+vi/2 Rs Io+ IQ Io. IQ Vi. C-vi/2

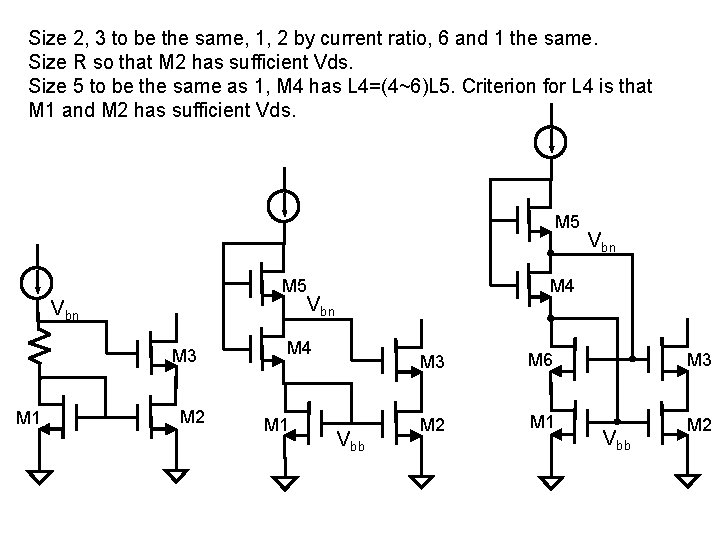

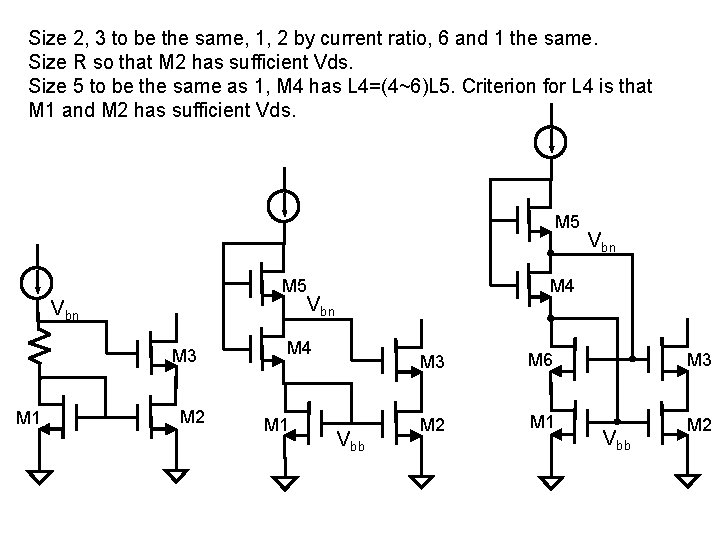

Size 2, 3 to be the same, 1, 2 by current ratio, 6 and 1 the same. Size R so that M 2 has sufficient Vds. Size 5 to be the same as 1, M 4 has L 4=(4~6)L 5. Criterion for L 4 is that M 1 and M 2 has sufficient Vds. M 5 M 3 M 1 M 4 Vbn M 2 M 4 M 1 Vbn Vbb M 3 M 6 M 3 M 2 M 1 M 2 Vbb

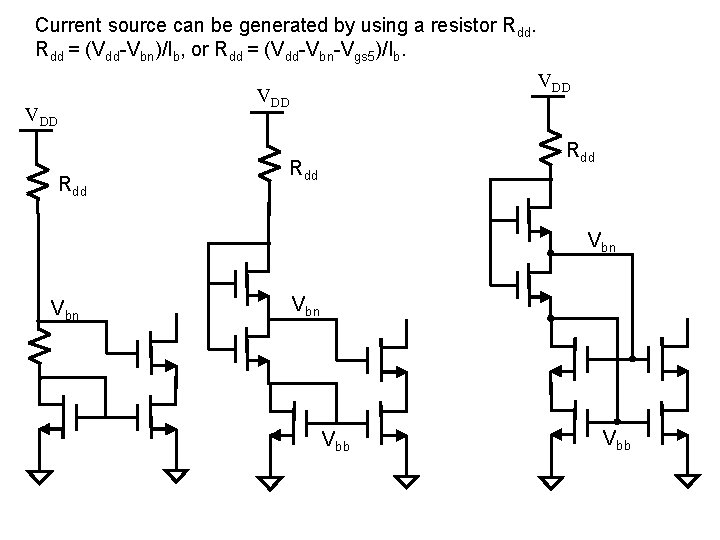

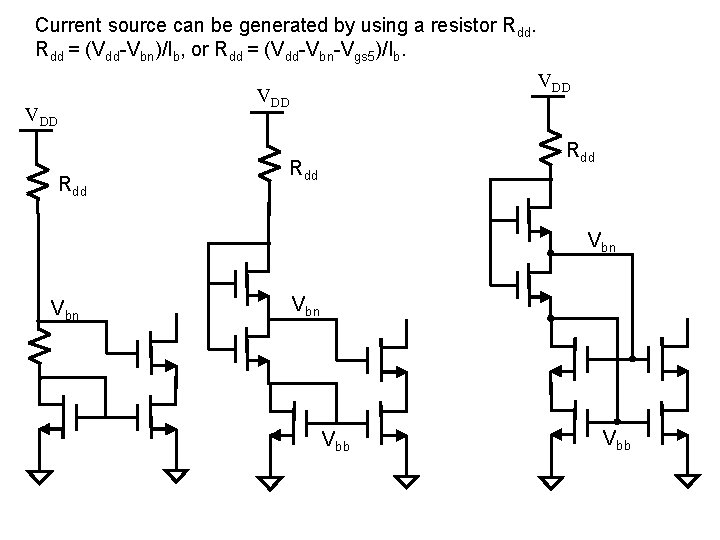

Current source can be generated by using a resistor Rdd = (Vdd-Vbn)/Ib, or Rdd = (Vdd-Vbn-Vgs 5)/Ib. VDD Rdd Vbn Vbn Vbb

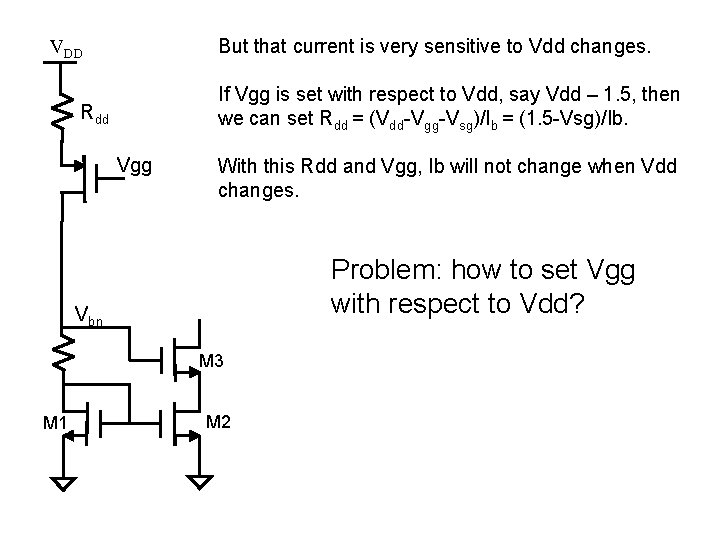

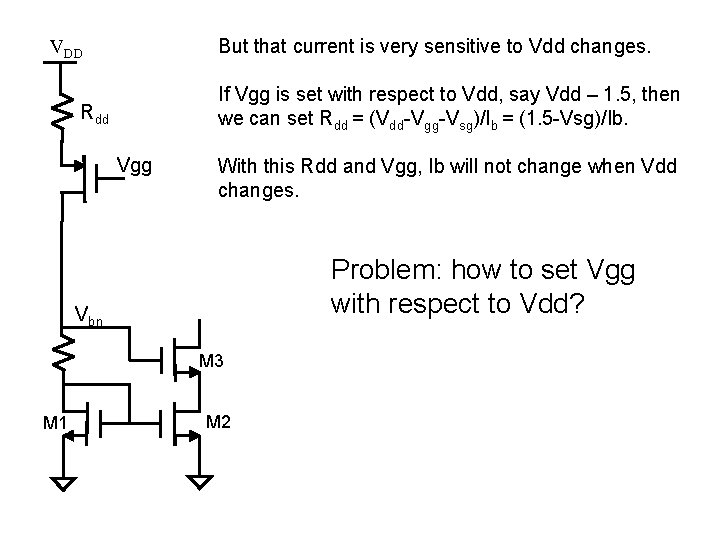

But that current is very sensitive to Vdd changes. VDD If Vgg is set with respect to Vdd, say Vdd – 1. 5, then we can set Rdd = (Vdd-Vgg-Vsg)/Ib = (1. 5 -Vsg)/Ib. Rdd Vgg With this Rdd and Vgg, Ib will not change when Vdd changes. Problem: how to set Vgg with respect to Vdd? Vbn M 3 M 1 M 2

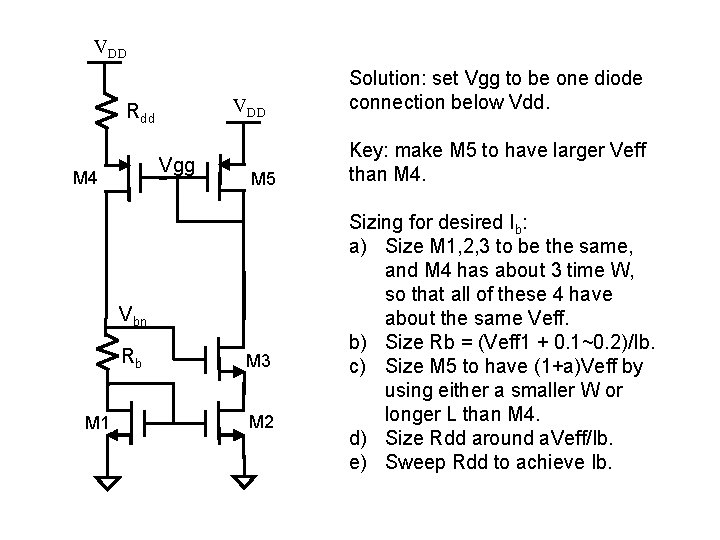

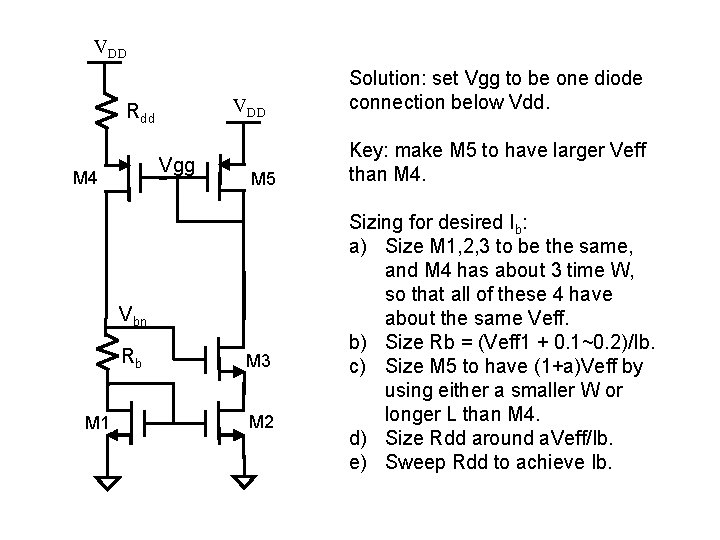

VDD Rdd Vgg M 4 M 5 Vbn Rb M 1 M 3 M 2 Solution: set Vgg to be one diode connection below Vdd. Key: make M 5 to have larger Veff than M 4. Sizing for desired Ib: a) Size M 1, 2, 3 to be the same, and M 4 has about 3 time W, so that all of these 4 have about the same Veff. b) Size Rb = (Veff 1 + 0. 1~0. 2)/Ib. c) Size M 5 to have (1+a)Veff by using either a smaller W or longer L than M 4. d) Size Rdd around a. Veff/Ib. e) Sweep Rdd to achieve Ib.

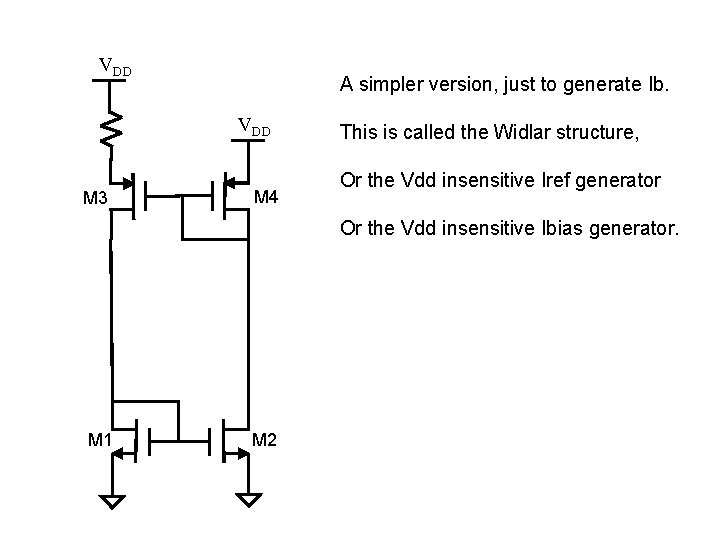

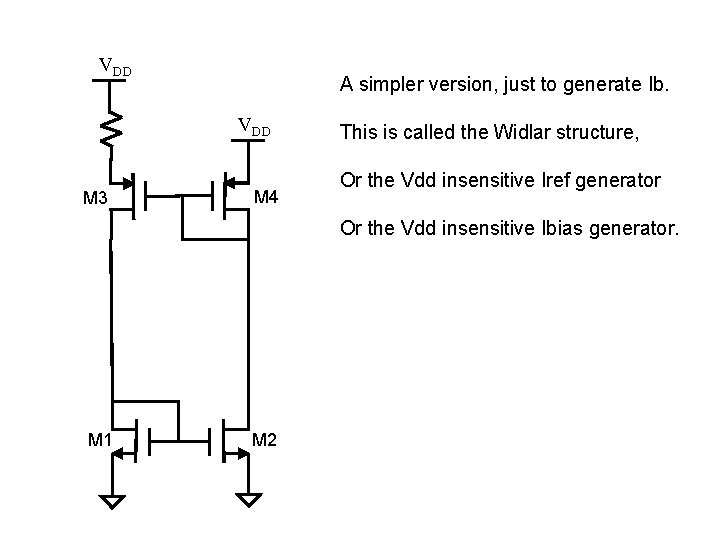

VDD A simpler version, just to generate Ib. VDD M 3 M 4 This is called the Widlar structure, Or the Vdd insensitive Iref generator Or the Vdd insensitive Ibias generator. M 1 M 2

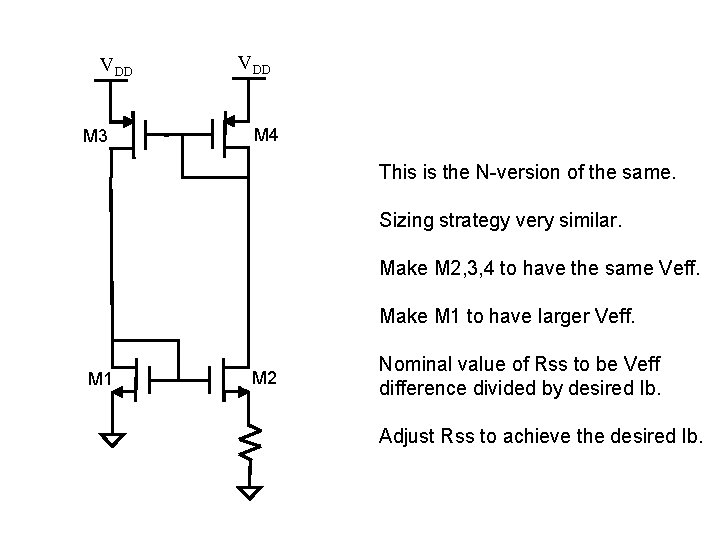

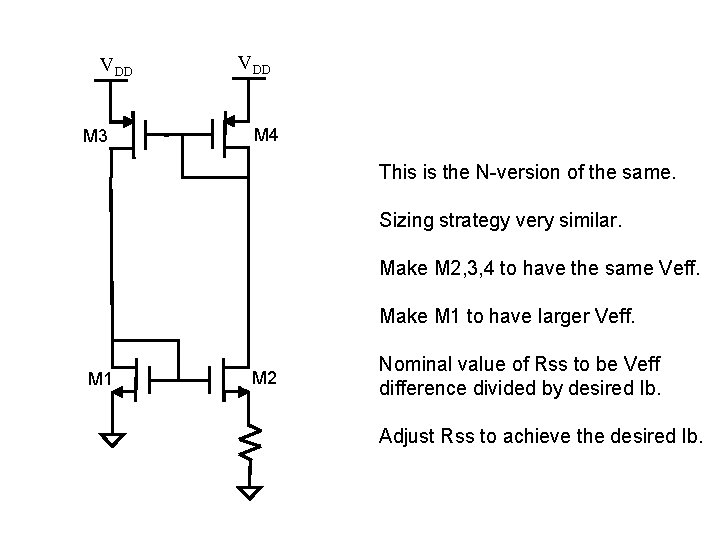

VDD M 3 VDD M 4 This is the N-version of the same. Sizing strategy very similar. Make M 2, 3, 4 to have the same Veff. Make M 1 to have larger Veff. M 1 M 2 Nominal value of Rss to be Veff difference divided by desired Ib. Adjust Rss to achieve the desired Ib.

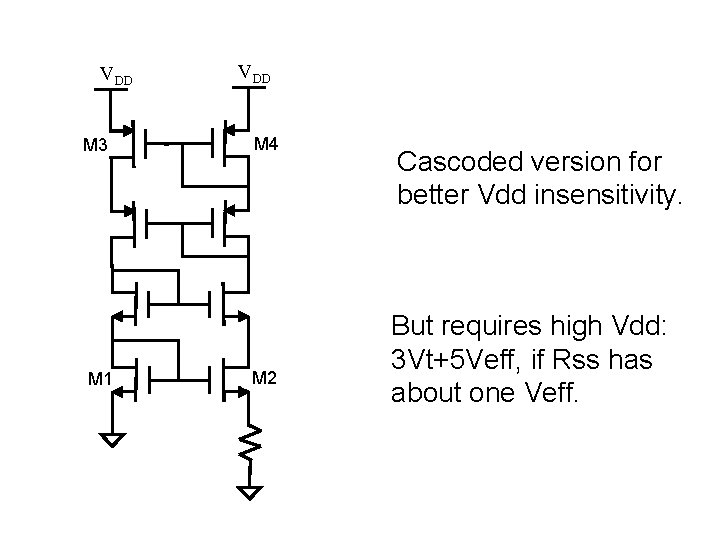

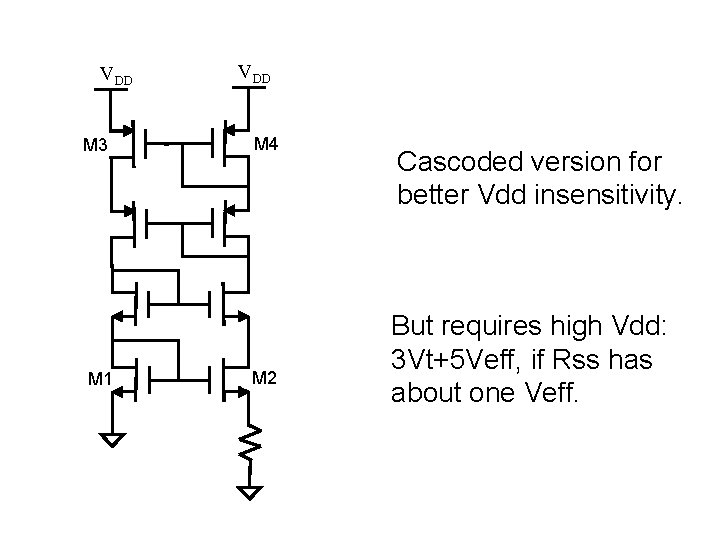

VDD M 3 M 1 VDD M 4 M 2 Cascoded version for better Vdd insensitivity. But requires high Vdd: 3 Vt+5 Veff, if Rss has about one Veff.

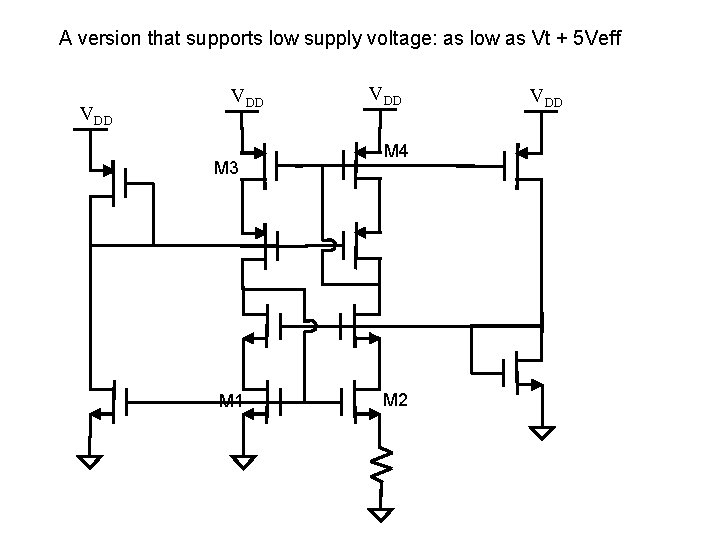

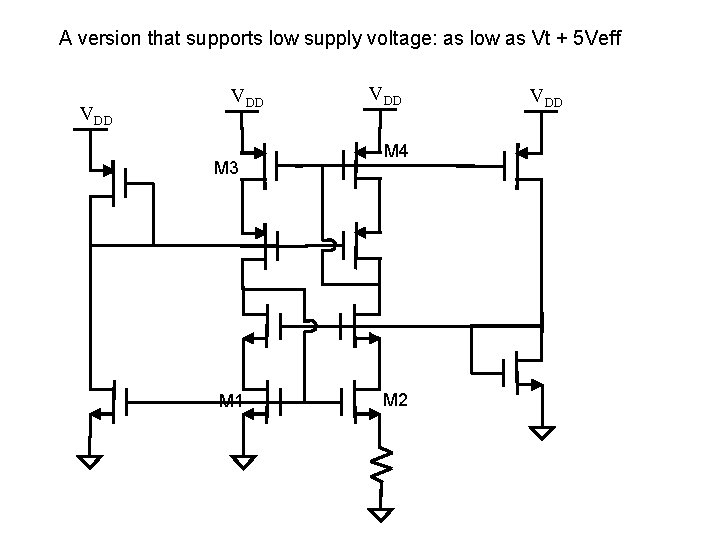

A version that supports low supply voltage: as low as Vt + 5 Veff VDD M 3 M 1 VDD M 4 M 2 VDD

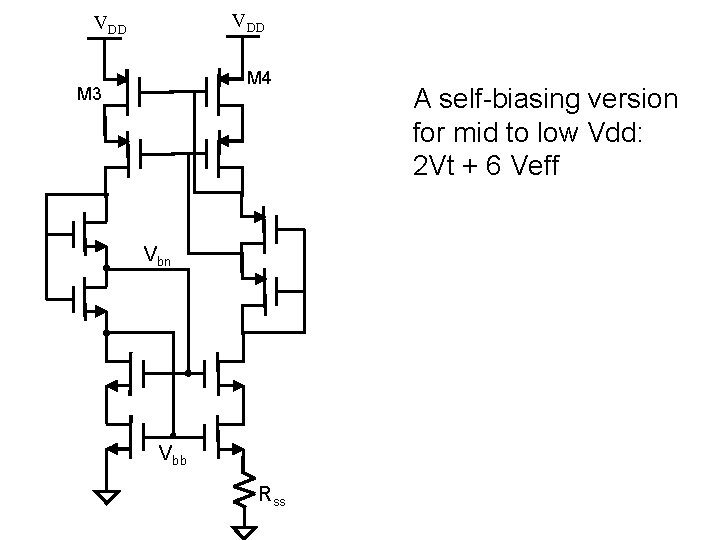

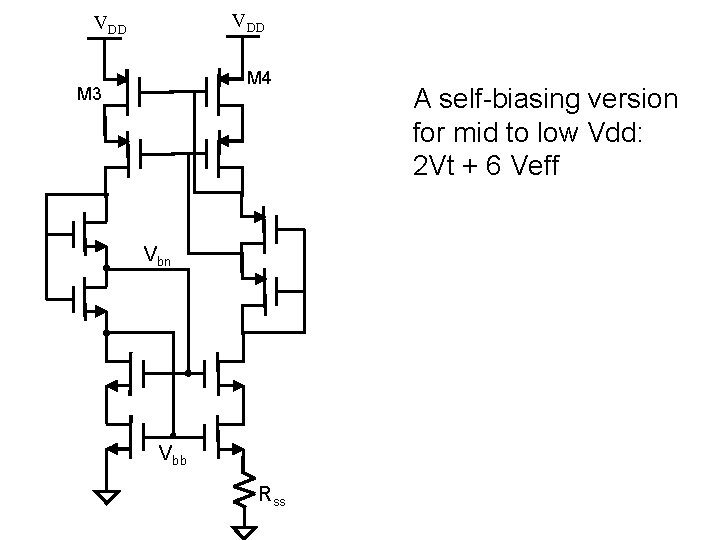

VDD M 4 M 3 Vbn Vbb Rss A self-biasing version for mid to low Vdd: 2 Vt + 6 Veff

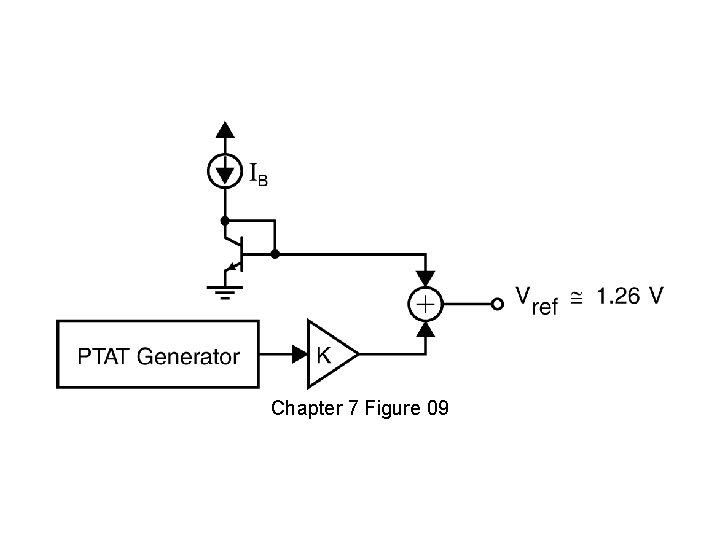

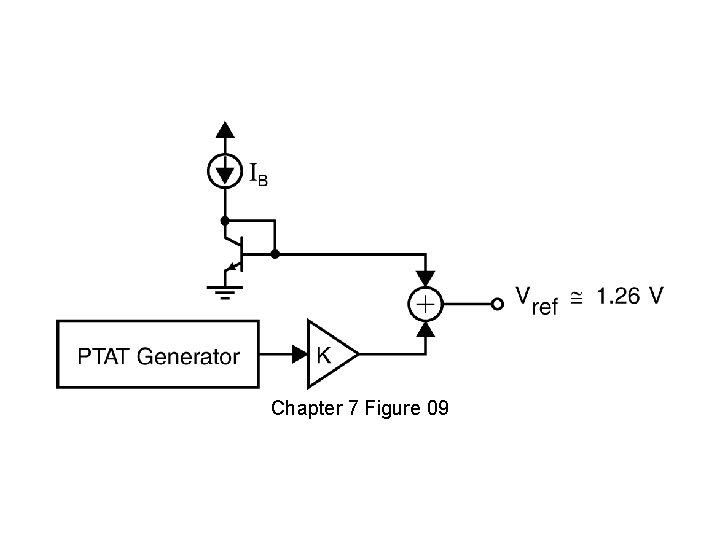

Chapter 7 Figure 09

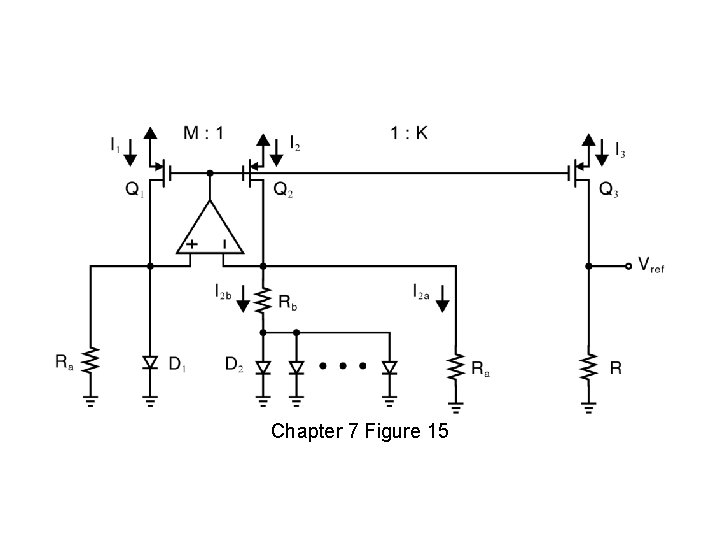

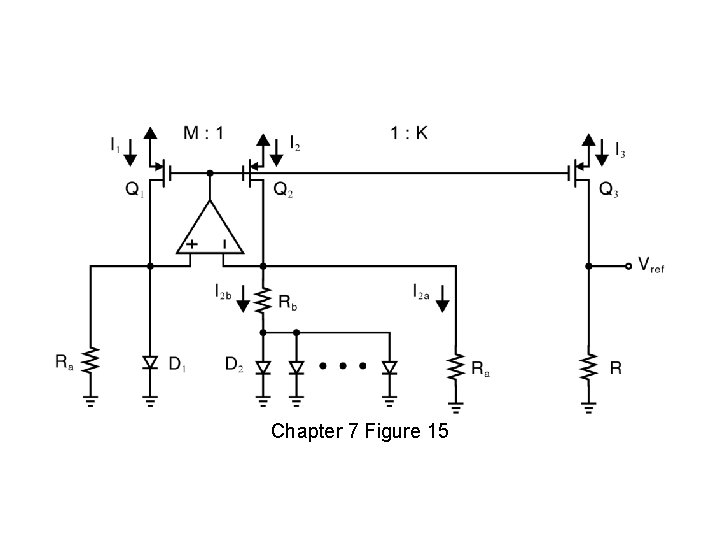

Chapter 7 Figure 15