VariabilityDriven Considerations in the Design of IntegratedCircuit Global

Variability-Driven Considerations in the Design of Integrated-Circuit Global Interconnects Lei He, Andrew B. Kahng*, Kingho Tam, Jinjun Xiong EE Department, University of California, Los Angeles *ECE Department, University of California, San Diego VMIC-2004, Waikoloa, October 2, 2004

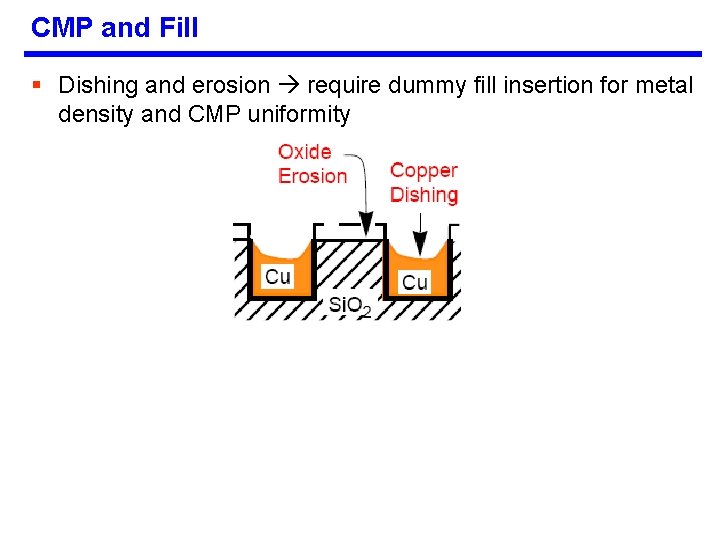

CMP and Fill § Dishing and erosion require dummy fill insertion for metal density and CMP uniformity

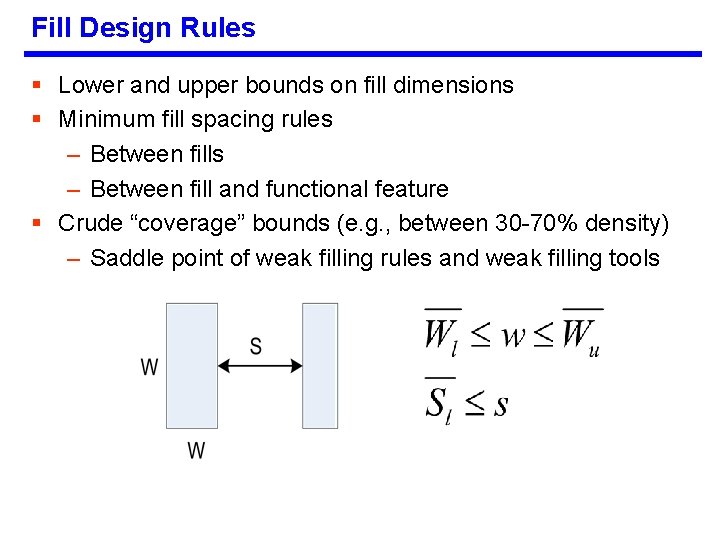

Fill Design Rules § Lower and upper bounds on fill dimensions § Minimum fill spacing rules – Between fill and functional feature § Crude “coverage” bounds (e. g. , between 30 -70% density) – Saddle point of weak filling rules and weak filling tools

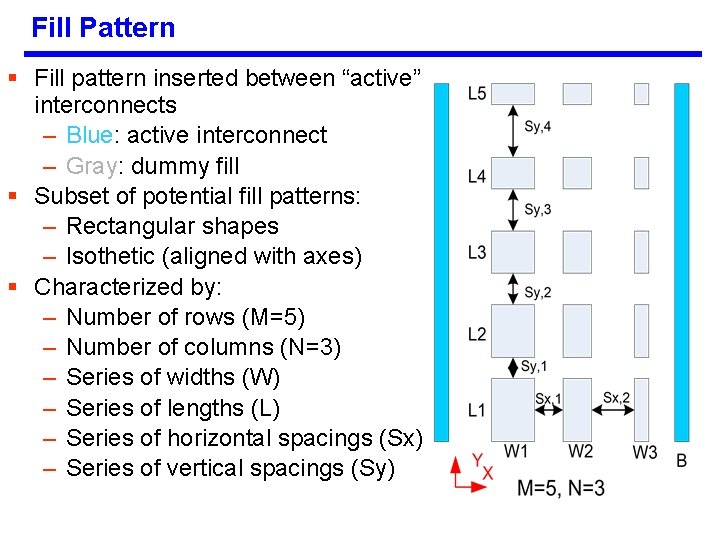

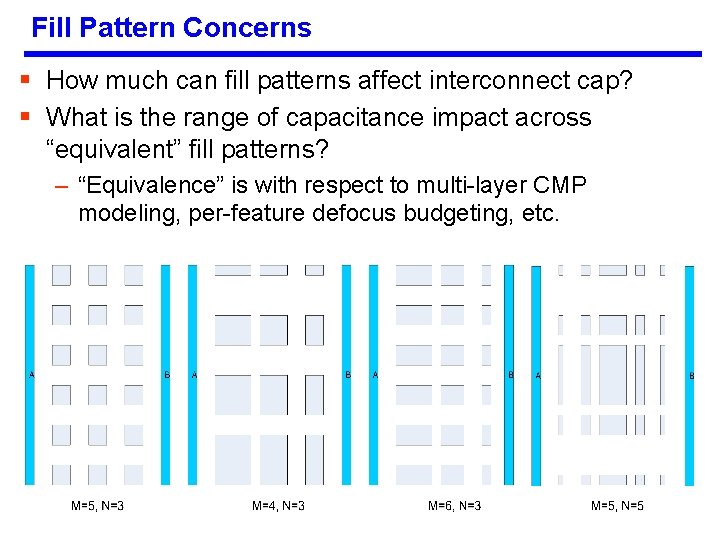

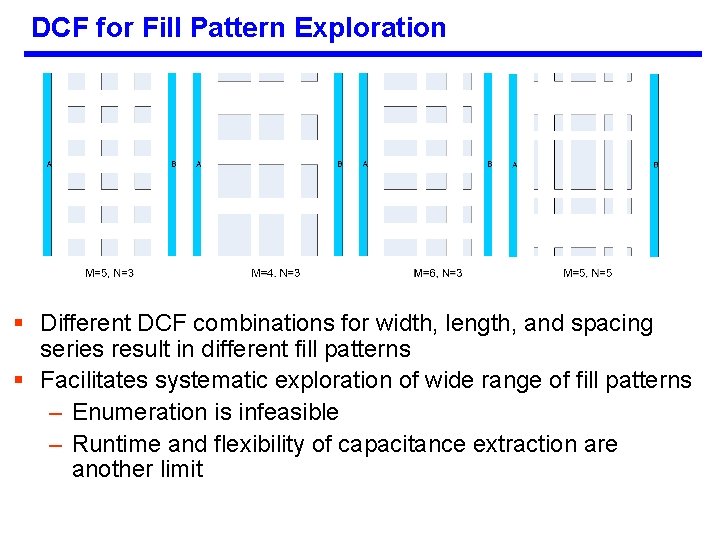

Fill Pattern § Fill pattern inserted between “active” interconnects – Blue: active interconnect – Gray: dummy fill § Subset of potential fill patterns: – Rectangular shapes – Isothetic (aligned with axes) § Characterized by: – Number of rows (M=5) – Number of columns (N=3) – Series of widths (W) – Series of lengths (L) – Series of horizontal spacings (Sx) – Series of vertical spacings (Sy)

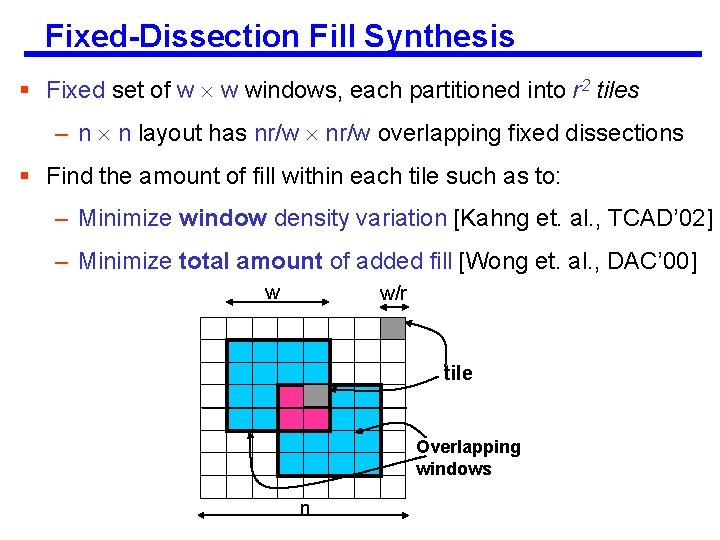

Fixed-Dissection Fill Synthesis § Fixed set of w w windows, each partitioned into r 2 tiles – n n layout has nr/w overlapping fixed dissections § Find the amount of fill within each tile such as to: – Minimize window density variation [Kahng et. al. , TCAD’ 02] – Minimize total amount of added fill [Wong et. al. , DAC’ 00] w w/r tile Overlapping windows n

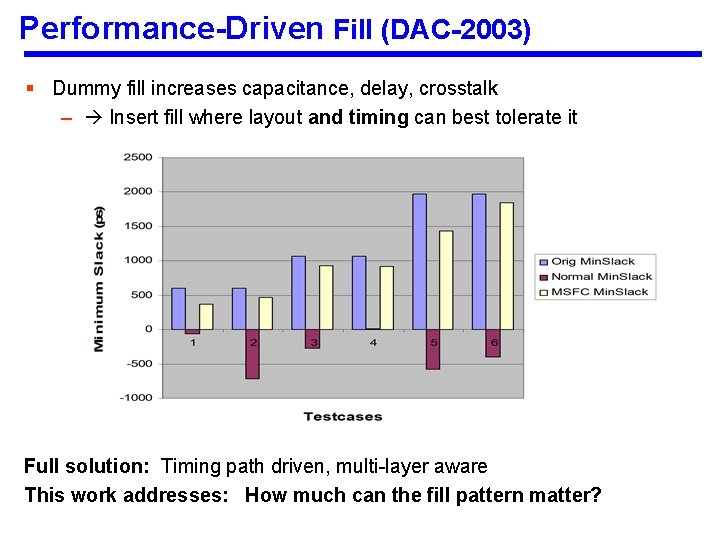

Performance-Driven Fill (DAC-2003) § Dummy fill increases capacitance, delay, crosstalk – Insert fill where layout and timing can best tolerate it Full solution: Timing path driven, multi-layer aware This work addresses: How much can the fill pattern matter?

Driving Questions § How much does fill affect coupling and total capacitance? § How much do dishing and erosion affect interconnect performance? – Is this impact on par with that of device variability? § What QOR loss is incurred by CMP-oblivious interconnect design? § Where this is leading: – – CMP-aware fill pattern synthesis CMP-aware fill and interconnect synthesis CMP-and fill-aware routing CMP modeling drives performance analysis, layout signoff

Outline § § Introduction and study goals Impact of fill insertion and fill patterns Impact of dishing/erosion on RC parasitics Impact on interconnect design – Bandwidth optimization – Delay minimization – CMP variation vs. random device variation § Conclusions § Note: This talk = outline of methodology and analysis framework to drive full-chip place/route

Fill Pattern Concerns § How much can fill patterns affect interconnect cap? § What is the range of capacitance impact across “equivalent” fill patterns? – “Equivalence” is with respect to multi-layer CMP modeling, per-feature defocus budgeting, etc.

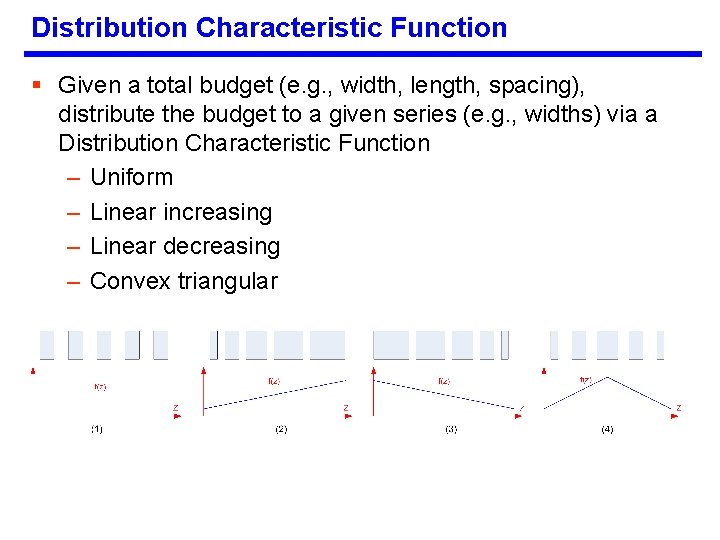

Distribution Characteristic Function § Given a total budget (e. g. , width, length, spacing), distribute the budget to a given series (e. g. , widths) via a Distribution Characteristic Function – Uniform – Linear increasing – Linear decreasing – Convex triangular

DCF for Fill Pattern Exploration § Different DCF combinations for width, length, and spacing series result in different fill patterns § Facilitates systematic exploration of wide range of fill patterns – Enumeration is infeasible – Runtime and flexibility of capacitance extraction are another limit

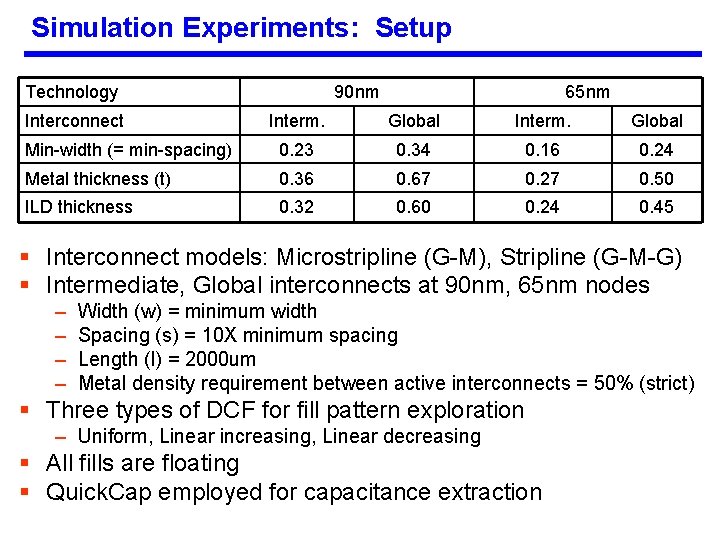

Simulation Experiments: Setup Technology Interconnect 90 nm 65 nm Interm. Global Min-width (= min-spacing) 0. 23 0. 34 0. 16 0. 24 Metal thickness (t) 0. 36 0. 67 0. 27 0. 50 ILD thickness 0. 32 0. 60 0. 24 0. 45 § Interconnect models: Microstripline (G-M), Stripline (G-M-G) § Intermediate, Global interconnects at 90 nm, 65 nm nodes – – Width (w) = minimum width Spacing (s) = 10 X minimum spacing Length (l) = 2000 um Metal density requirement between active interconnects = 50% (strict) § Three types of DCF for fill pattern exploration – Uniform, Linear increasing, Linear decreasing § All fills are floating § Quick. Cap employed for capacitance extraction

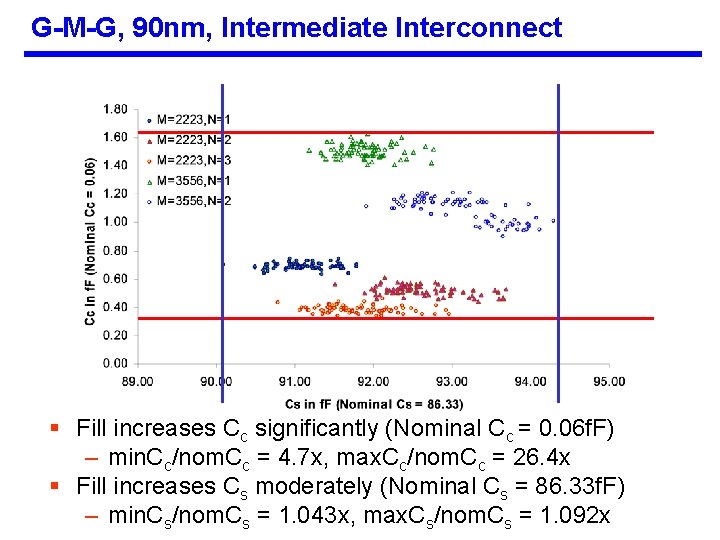

G-M-G, 90 nm, Intermediate Interconnect § Fill increases Cc significantly (Nominal Cc = 0. 06 f. F) – min. Cc/nom. Cc = 4. 7 x, max. Cc/nom. Cc = 26. 4 x § Fill increases Cs moderately (Nominal Cs = 86. 33 f. F) – min. Cs/nom. Cs = 1. 043 x, max. Cs/nom. Cs = 1. 092 x

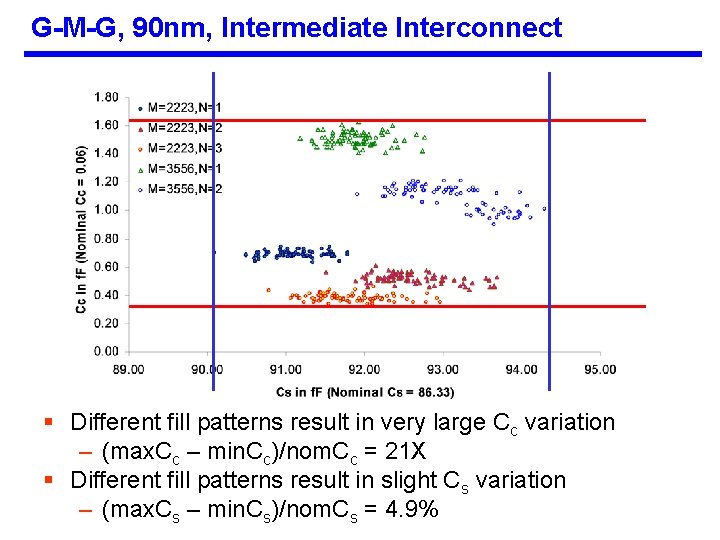

G-M-G, 90 nm, Intermediate Interconnect § Different fill patterns result in very large Cc variation – (max. Cc – min. Cc)/nom. Cc = 21 X § Different fill patterns result in slight Cs variation – (max. Cs – min. Cs)/nom. Cs = 4. 9%

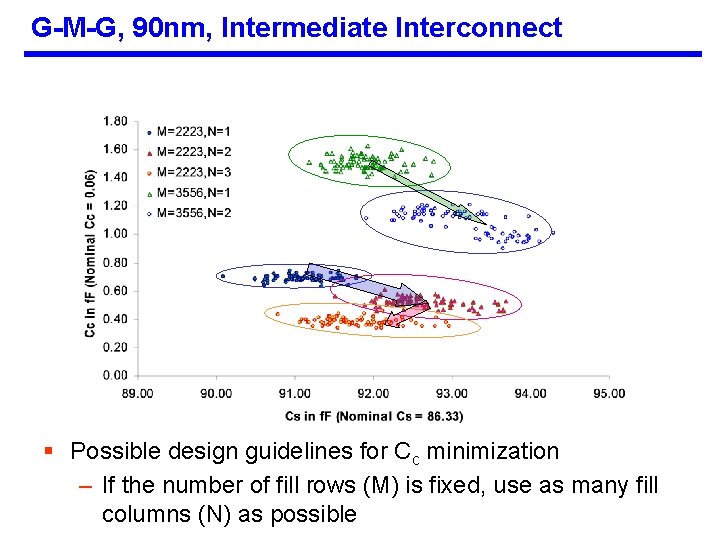

G-M-G, 90 nm, Intermediate Interconnect § Possible design guidelines for Cc minimization – If the number of fill rows (M) is fixed, use as many fill columns (N) as possible

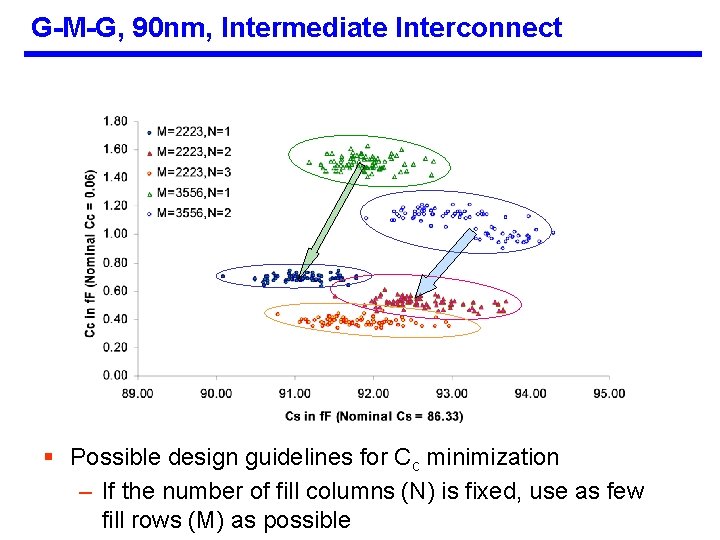

G-M-G, 90 nm, Intermediate Interconnect § Possible design guidelines for Cc minimization – If the number of fill columns (N) is fixed, use as few fill rows (M) as possible

G-M-G, 90 nm/65 nm, Intermediate/Global Interconnects

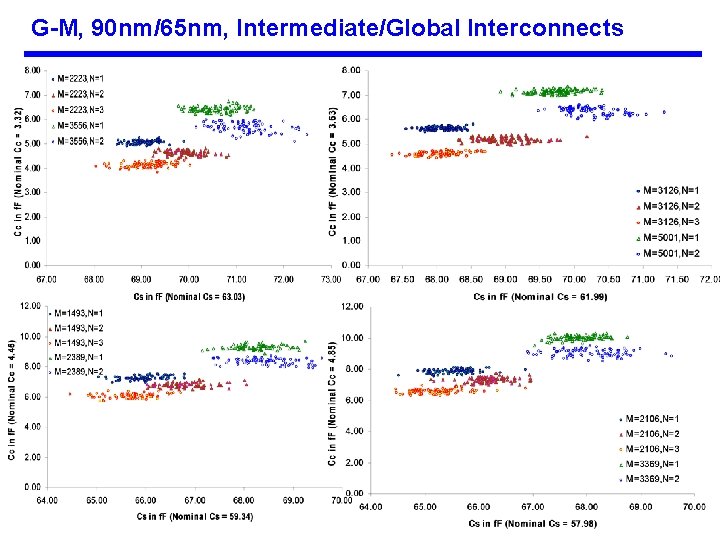

G-M, 90 nm/65 nm, Intermediate/Global Interconnects

Mini-Conclusion on Fill Insertion and Fill Pattern § Fill insertion can dramatically increase Cc and Cs over their respective nominal values – G-M-G, 90 nm, Intermediate: Cc 26 X, Cs 9% § Cc and Cs varies significantly across different fill patterns – G-M-G, 90 nm, Intermediate: Cc 21 X, Cs 5% § Useful fill pattern design guidelines may be possible, e. g. : – If the number of fill rows (M) is fixed, use as many fill columns (N) as possible – If the number of fill columns (N) is fixed, use as few fill rows (M) as possible § Additional studies needed with tighter wire pitches, more exhaustive analysis of fill patterns, etc.

Outline § § Introduction and study goals Impact of fill insertion and fill patterns Impact of dishing/erosion on RC parasitics Impact on interconnect design – Bandwidth optimization – Delay minimization – CMP variation vs. random device variation § Conclusions

![Modeling of Dishing and Erosion § Dishing/erosion model [Tugbawa et al. , CMP-MIC 1999] Modeling of Dishing and Erosion § Dishing/erosion model [Tugbawa et al. , CMP-MIC 1999]](http://slidetodoc.com/presentation_image_h/354901769449680c37008ac2263359cd/image-21.jpg)

Modeling of Dishing and Erosion § Dishing/erosion model [Tugbawa et al. , CMP-MIC 1999] – Affects only metal thicknesses – Is a function of metal density and metal width § We assume – Metal density requirement between active interconnect = 50% with fill insertion – Rectangular shape used to approximate the concave shape from dishing

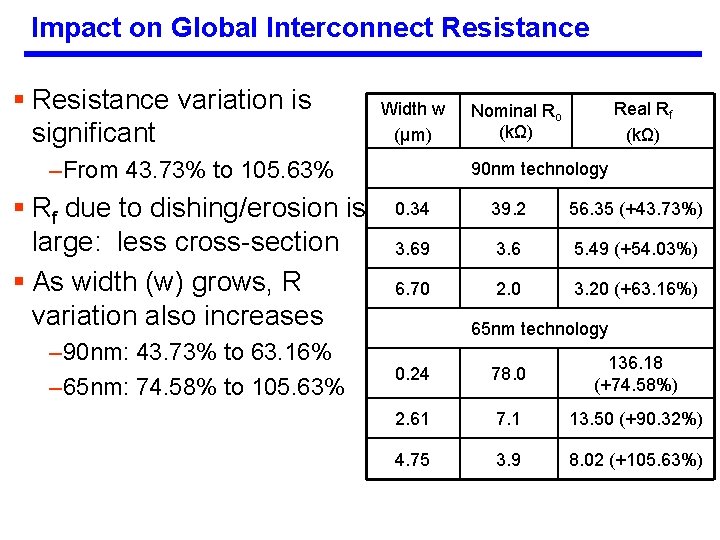

Impact on Global Interconnect Resistance § Resistance variation is significant Width w (μm) –From 43. 73% to 105. 63% § Rf due to dishing/erosion is large: less cross-section § As width (w) grows, R variation also increases – 90 nm: 43. 73% to 63. 16% – 65 nm: 74. 58% to 105. 63% Real Rf (kΩ) Nominal Ro (kΩ) 90 nm technology 0. 34 39. 2 56. 35 (+43. 73%) 3. 69 3. 6 5. 49 (+54. 03%) 6. 70 2. 0 3. 20 (+63. 16%) 65 nm technology 0. 24 78. 0 136. 18 (+74. 58%) 2. 61 7. 1 13. 50 (+90. 32%) 4. 75 3. 9 8. 02 (+105. 63%)

Impact on Global Interconnect Capacitance § Three scenarios: – S 1: Interconnect with nominal value – S 2: Interconnect affected by dishing/erosion, WITHOUT fill insertion – S 3: Interconnect affected by dishing/erosion, WITH fill insertion § Quick. Cap is used for capacitance extraction – Coupling Cc, total Cs § Fill pattern is chosen that results in minimum Cc

Impact on Global Interconnect Capacitance § (Eye chart omitted) § Dishing and erosion have comparatively smaller impact on capacitance § The fact of fill insertion itself has much larger impact on capacitance

Mini-Conclusion on Dishing/Erosion Impact § Dishing and erosion significantly increase interconnect resistance § Dishing and erosion impact on capacitance is ignorable – Is this really the case? – Any such assessment is design- and methodologydependent § Fill insertion has much larger impact than dishing/erosion on capacitance

Outline § § Introduction and study goals Impact of fill insertion and fill patterns Impact of dishing/erosion on RC parasitics Impact on interconnect design – Bandwidth optimization – Delay minimization – CMP variation vs. random device variation § Conclusions

Interconnect Design Concerns § How do CMP effects change conventional (CMP-oblivious) interconnect design ? § How do we take CMP effects into account for a better (CMP -aware) design flow? § Compared to random device variation, does CMP-induced variation really matter (e. g. , should the EDA vendors focus on Device-aware or on CMP-aware analysis and circuit optimization)?

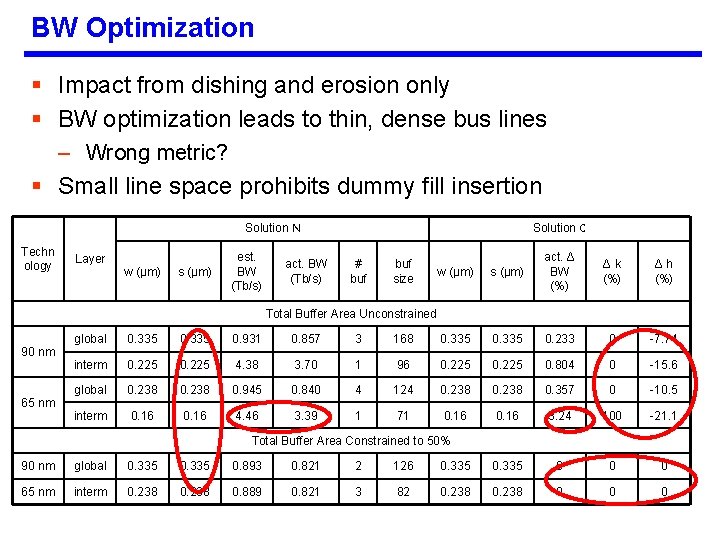

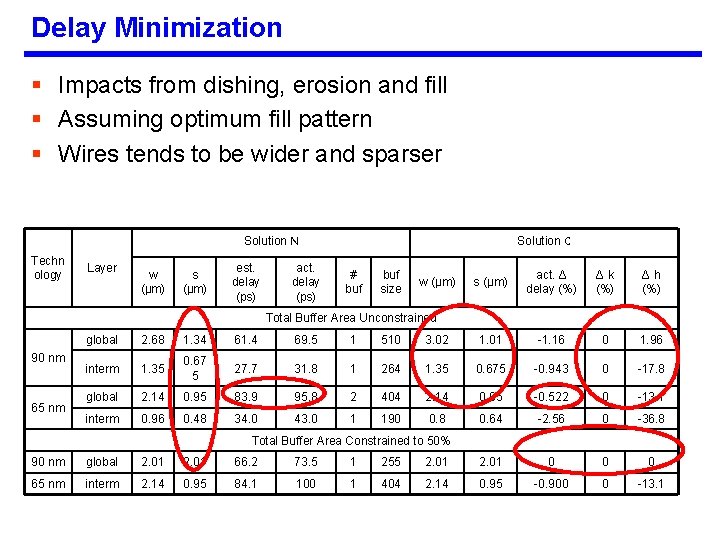

Experiment Setup § Interconnect design for parallel buses – Interconnect sizing (w) and spacing (s) – Buffer insertion (k) and sizing (h) § Figure-of-merit – Bandwidth: BW = #bits/delay [Pamunuwa et al. , ISCAS 02] – Delay § Two problem formulations – Bandwidth optimization • Variables: interconnect (width, space, bits), buffer (number, size) • Constraint: total bus area is fixed – Delay minimization • Variables: interconnect (width, space), buffer (number, size) • Constraints: total bus area and interconnect bits are fixed § Solution N (CMP-oblivious) vs. Solution C (CMP-aware)

BW Optimization § Impact from dishing and erosion only § BW optimization leads to thin, dense bus lines – Wrong metric? § Small line space prohibits dummy fill insertion Solution N Techn ology Layer w (μm) s (μm) est. BW (Tb/s) act. BW (Tb/s) Solution C # buf size w (μm) s (μm) act. Δ BW (%) Δk (%) Δh (%) Total Buffer Area Unconstrained 90 nm 65 nm global 0. 335 0. 931 0. 857 3 168 0. 335 0. 233 0 -7. 74 interm 0. 225 4. 38 3. 70 1 96 0. 225 0. 804 0 -15. 6 global 0. 238 0. 945 0. 840 4 124 0. 238 0. 357 0 -10. 5 interm 0. 16 4. 46 3. 39 1 71 0. 16 3. 24 100 -21. 1 Total Buffer Area Constrained to 50% 90 nm global 0. 335 0. 893 0. 821 2 126 0. 335 0 0 0 65 nm interm 0. 238 0. 889 0. 821 3 82 0. 238 0 0 0

Delay Minimization § Impacts from dishing, erosion and fill § Assuming optimum fill pattern § Wires tends to be wider and sparser Solution N Techn ology Layer w (μm) s (μm) est. delay (ps) act. delay (ps) Solution C # buf size w (μm) s (μm) act. Δ delay (%) Δk (%) Δh (%) Total Buffer Area Unconstrained 90 nm 65 nm global 2. 68 1. 34 61. 4 69. 5 1 510 3. 02 1. 01 -1. 16 0 1. 96 interm 1. 35 0. 67 5 27. 7 31. 8 1 264 1. 35 0. 675 -0. 943 0 -17. 8 global 2. 14 0. 95 83. 9 95. 8 2 404 2. 14 0. 95 -0. 522 0 -13. 1 interm 0. 96 0. 48 34. 0 43. 0 1 190 0. 8 0. 64 -2. 56 0 -36. 8 Total Buffer Area Constrained to 50% 90 nm global 2. 01 66. 2 73. 5 1 255 2. 01 0 0 0 65 nm interm 2. 14 0. 95 84. 1 100 1 404 2. 14 0. 95 -0. 900 0 -13. 1

Mini-Conclusion on Interconnect Design § CMP-oblivious design’s nominal values overestimate interconnect bandwidth – Up to 24% § CMP-oblivious design’s nominal values underestimate interconnect delay – Up to 26% § CMP-aware design can achieve up to 3% improvement for both BW and delay, compared to the “adjusted” CMPoblivious design – “Adjusted” = CMP effects considered § CMP induced variation is as important as random device variation (assuming ITRS bounds )

Outline § § Introduction and study goals Impact of fill insertion and fill patterns Impact of dishing/erosion on RC parasitics Impact on interconnect design – Bandwidth optimization – Delay minimization – CMP variation vs. random device variation § Conclusions

Conclusions § Dummy fill can cause very large coupling capacitance variation w. r. t. nominal § Dishing and erosion cause substantial resistance increase, but have limited impact on coupling § Design without considering these variations – Overestimates interconnect bandwidth – Underestimates interconnect delay § CMP-aware design can improve design quality § Ongoing directions – Integration of multi-layer CMP modeling into flow – CMP-aware fill pattern synthesis, then singleinterconnect wire and buffer sizing, then full routing

- Slides: 33