Validation of CodeImproving Transformations for Embedded Systems Robert

Validation of Code-Improving Transformations for Embedded Systems Robert van Engelen David Whalley Xin Yuan SAC 03

Introduction n Validation of: n n n Compiler optimizations Hand-crafted code optimizations VISTA: VPO Interactive System for Tuning Applications n n View of the assembly program representation Allows orchestrating compiler optimizations applied to application code Supports code editing at the assembly level Undo/redo facilities 10/2/2020 SAC 03 2

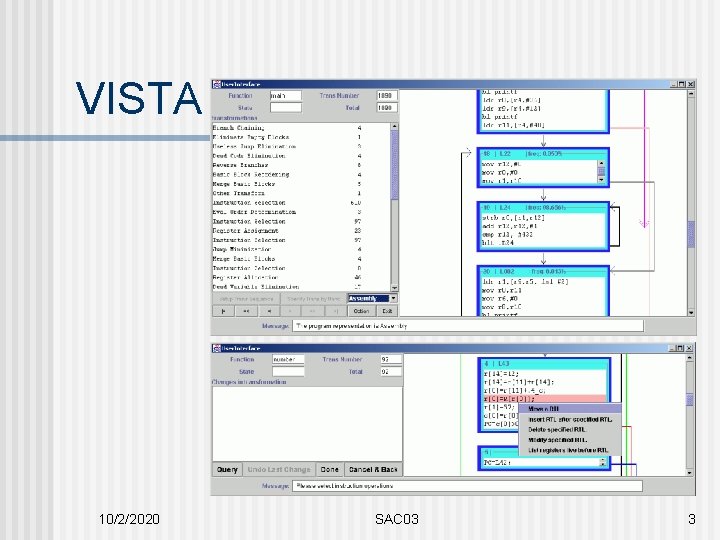

VISTA 10/2/2020 SAC 03 3

Motivation Embedded system software developers often write code in assembly to meet hardware/software design constraints n Hand-optimized assembly code is errorprone without tool support n Validation of compiler optimizations is important for high-risk systems n 10/2/2020 SAC 03 4

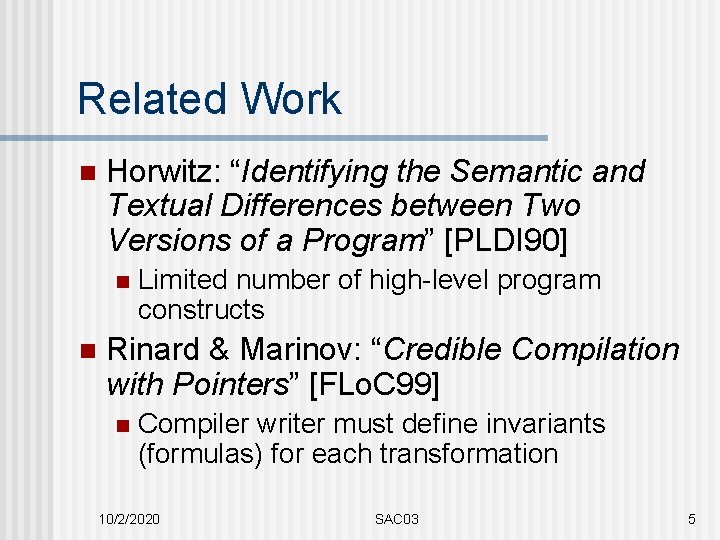

Related Work n Horwitz: “Identifying the Semantic and Textual Differences between Two Versions of a Program” [PLDI 90] n n Limited number of high-level program constructs Rinard & Marinov: “Credible Compilation with Pointers” [FLo. C 99] n Compiler writer must define invariants (formulas) for each transformation 10/2/2020 SAC 03 5

![Related Work (cont’d) n Necula: “Translation Validation for an Optimizing Compiler” [PLDI 00] n Related Work (cont’d) n Necula: “Translation Validation for an Optimizing Compiler” [PLDI 00] n](http://slidetodoc.com/presentation_image/b989f433bdbf289c7090d9d019166dbd/image-6.jpg)

Related Work (cont’d) n Necula: “Translation Validation for an Optimizing Compiler” [PLDI 00] n n Program slicing n n Transformations cannot change branch structure From a subset of program behavior reduce the program to a minimum form that produces the behavior Proving type and memory safeness n Complementary to our approach 10/2/2020 SAC 03 6

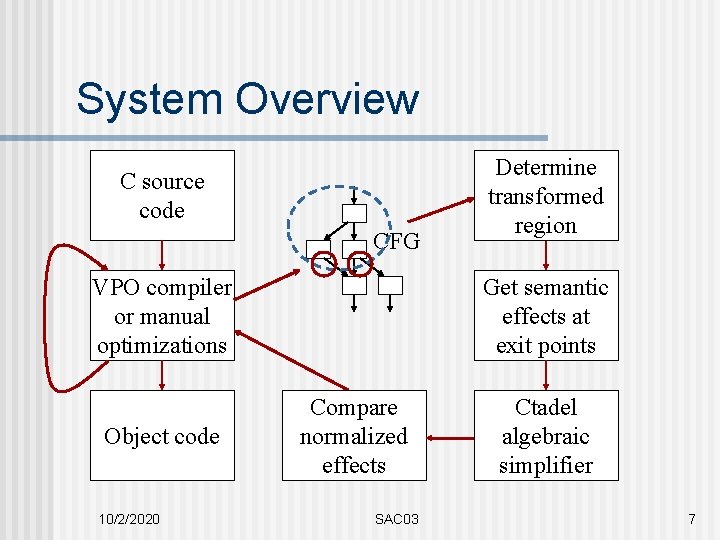

System Overview C source code CFG VPO compiler or manual optimizations Object code 10/2/2020 Determine transformed region Get semantic effects at exit points Compare normalized effects SAC 03 Ctadel algebraic simplifier 7

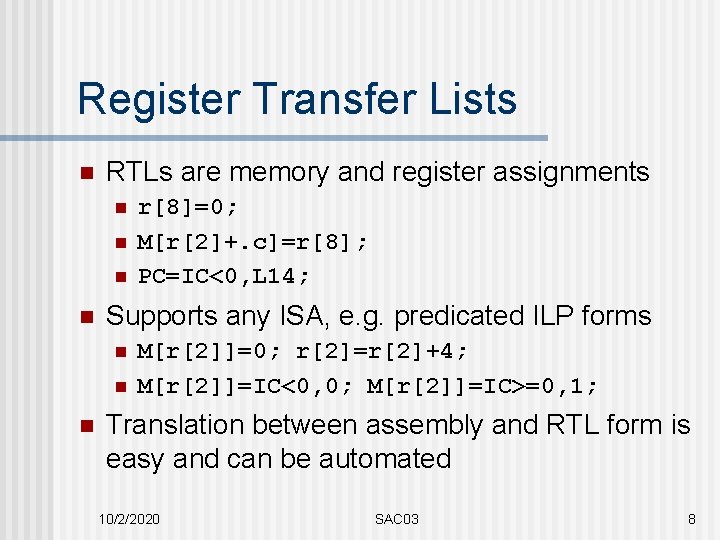

Register Transfer Lists n RTLs are memory and register assignments n n Supports any ISA, e. g. predicated ILP forms n n n r[8]=0; M[r[2]+. c]=r[8]; PC=IC<0, L 14; M[r[2]]=0; r[2]=r[2]+4; M[r[2]]=IC<0, 0; M[r[2]]=IC>=0, 1; Translation between assembly and RTL form is easy and can be automated 10/2/2020 SAC 03 8

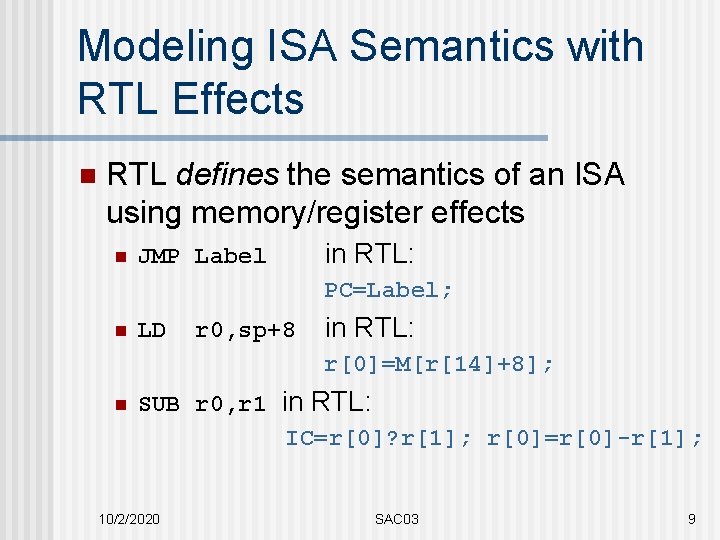

Modeling ISA Semantics with RTL Effects n RTL defines the semantics of an ISA using memory/register effects n JMP Label in RTL: PC=Label; n LD r 0, sp+8 in RTL: r[0]=M[r[14]+8]; n SUB r 0, r 1 in RTL: IC=r[0]? r[1]; r[0]=r[0]-r[1]; 10/2/2020 SAC 03 9

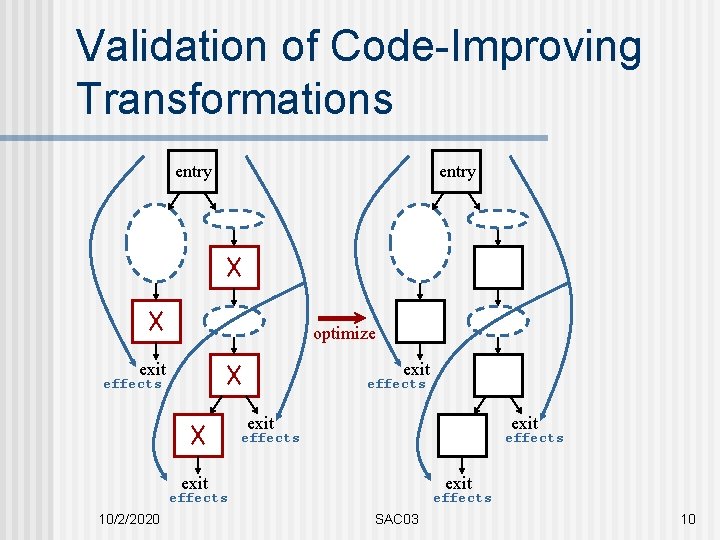

Validation of Code-Improving Transformations entry optimize exit effects exit effects 10/2/2020 effects SAC 03 10

![Example Transformation IC=r[8]? 0; PC=IC<0, L 14; r[8]=r[9]; M[r[14]+. c]=r[8]; PC=L 15; Register allocation: Example Transformation IC=r[8]? 0; PC=IC<0, L 14; r[8]=r[9]; M[r[14]+. c]=r[8]; PC=L 15; Register allocation:](http://slidetodoc.com/presentation_image/b989f433bdbf289c7090d9d019166dbd/image-11.jpg)

Example Transformation IC=r[8]? 0; PC=IC<0, L 14; r[8]=r[9]; M[r[14]+. c]=r[8]; PC=L 15; Register allocation: replace M[r[14]+. c] with r[10] 10/2/2020 r[8]=r[9]; r[8]=-r[8]; M[r[14]+. c]=r[8]; r[8]=M[r[14]+. c]; SAC 03 Dataflow analysis: M[r[14]+. c] is dead 11

![Calculating the Extent of a Region After a Transformation region IC=r[8]? 0; PC=IC<0, L Calculating the Extent of a Region After a Transformation region IC=r[8]? 0; PC=IC<0, L](http://slidetodoc.com/presentation_image/b989f433bdbf289c7090d9d019166dbd/image-12.jpg)

Calculating the Extent of a Region After a Transformation region IC=r[8]? 0; PC=IC<0, L 14; r[8]=r[9]; r[10]=r[8]; PC=L 15; Register allocation: replace M[r[14]+. c] with r[10] 10/2/2020 r[8]=r[9]; r[8]=-r[8]; r[10]=r[8]; r[8]=r[10]; r[10]: SAC 03 Dataflow analysis: r[10] is dead 12

![Merging the Effects of a Region region effects IC=r[8]? 0; PC=IC<0, L 14; r[8]=r[9]; Merging the Effects of a Region region effects IC=r[8]? 0; PC=IC<0, L 14; r[8]=r[9];](http://slidetodoc.com/presentation_image/b989f433bdbf289c7090d9d019166dbd/image-13.jpg)

Merging the Effects of a Region region effects IC=r[8]? 0; PC=IC<0, L 14; r[8]=r[9]; r[10]=r[8]; PC=L 15; r[8]=r[9]; r[8]=-r[8]; r[10]=r[8]; r[8]=r[9]; r[10]=r[9]; Register allocation: replace M[r[14]+. c] with r[10] r[8]=-r[9]; r[10]=-r[9]; r[8]=r[10]; r[8]= 10/2/2020 { r[10]: Dataflow analysis: r[10] is dead -r[9] if IC<0 r[9] if IC>=0 SAC 03 13

![Merging the Effects Within a Single Block region effects Merging (Before Transformation) r[16]=0; r[17]=HI[_s]; Merging the Effects Within a Single Block region effects Merging (Before Transformation) r[16]=0; r[17]=HI[_s];](http://slidetodoc.com/presentation_image/b989f433bdbf289c7090d9d019166dbd/image-14.jpg)

Merging the Effects Within a Single Block region effects Merging (Before Transformation) r[16]=0; r[17]=HI[_s]; r[19]=r[17]+LO[_s]; r[17]: r[16]=0; r[19]=HI[_s]+LO[_s]; r[17]=r[16]+r[19]; r[16]: Merging (After Transformation) r[16]=0; r[17]=HI[_s]; r[19]=r[17]+LO[_s]; r[19]=HI[_s]+LO[_s]; r[17]=r[19]; r[16]: r[17]: r[17]=HI[_s]+LO[_s]; r[19]=HI[_s]+LO[_s]; 10/2/2020 SAC 03 14

![Extending the Scope of a Region region effects Before Transformation r[16]=0; r[17]=HI[_s]; r[19]=r[17]+LO[_s]; r[17]=r[16]+r[19]; Extending the Scope of a Region region effects Before Transformation r[16]=0; r[17]=HI[_s]; r[19]=r[17]+LO[_s]; r[17]=r[16]+r[19];](http://slidetodoc.com/presentation_image/b989f433bdbf289c7090d9d019166dbd/image-15.jpg)

Extending the Scope of a Region region effects Before Transformation r[16]=0; r[17]=HI[_s]; r[19]=r[17]+LO[_s]; r[17]=r[16]+r[19]; r[17]: r[16]: r[17]=HI[_s]+LO[_s]; r[17]=r[16]+r[19]; r[19]=HI[_s]+LO[_s]; 10/2/2020 After Transformation r[16]=0; r[17]=HI[_s]; r[19]=r[17]+LO[_s]; r[17]=r[19]; Not Equivalent equivalent SAC 03 r[16]: r[17]: r[17]=HI[_s]+LO[_s]; r[17]=r[19]; r[19]=HI[_s]+LO[_s]; 15

![Merging Potential Set/Use Alias region M[r[2]] and M[r[3]] are potential aliases effects M[r[2]]=r[4]; r[5]=M[r[3]]; Merging Potential Set/Use Alias region M[r[2]] and M[r[3]] are potential aliases effects M[r[2]]=r[4]; r[5]=M[r[3]];](http://slidetodoc.com/presentation_image/b989f433bdbf289c7090d9d019166dbd/image-16.jpg)

Merging Potential Set/Use Alias region M[r[2]] and M[r[3]] are potential aliases effects M[r[2]]=r[4]; r[5]=M[r[3]]; M[r[2]]=r[4]; r[5]= 10/2/2020 { r[4] if r[2]==r[3] M[r[3]] if r[2]!=r[3] SAC 03 16

![Merging Potential Set/Set Alias region effects M[r[2]] and M[r[3]] are potential aliases M[r[2]]=r[4]; M[r[3]]=r[5]; Merging Potential Set/Set Alias region effects M[r[2]] and M[r[3]] are potential aliases M[r[2]]=r[4]; M[r[3]]=r[5];](http://slidetodoc.com/presentation_image/b989f433bdbf289c7090d9d019166dbd/image-17.jpg)

Merging Potential Set/Set Alias region effects M[r[2]] and M[r[3]] are potential aliases M[r[2]]=r[4]; M[r[3]]=r[5]; M[r[2]]= 10/2/2020 SAC 03 { r[5] if r[2]==r[3] r[4] if r[2]!=r[3] 17

![Merging Conditional Effects B 1 M[r[14]+. v]=r[8]; IC=r[8]? 0; PC=IC>=0, B 3; M[r[14]+. v]=(r[8] Merging Conditional Effects B 1 M[r[14]+. v]=r[8]; IC=r[8]? 0; PC=IC>=0, B 3; M[r[14]+. v]=(r[8]](http://slidetodoc.com/presentation_image/b989f433bdbf289c7090d9d019166dbd/image-18.jpg)

Merging Conditional Effects B 1 M[r[14]+. v]=r[8]; IC=r[8]? 0; PC=IC>=0, B 3; M[r[14]+. v]=(r[8] if r[8]>=0); M[r[14]+. v]=(r[8] if r[8]<0); B 2 M[r[14]+. v]= { r[9]=-r[8]; M[r[14]+. v]=r[9]; r[9] is dead M[r[14]+. v]=(-r[8] if r[8]<0); r[8] if r[8]>=0 -r[8] if r[8]<0 join B 3 r[8]=M[r[14]+. v]; r[8]= 10/2/2020 r[9]: { . v: r[8] if r[8]>=0 -r[8] if r[8]<0 SAC 03 . v is dead 18

![Loop Effects B 1 M[r[14]]=0; r[14]=r[14]+4; IC=r[8]? 0; r[8]=r[8]-1; PC=IC>=0, B 1; M[r[14]. . Loop Effects B 1 M[r[14]]=0; r[14]=r[14]+4; IC=r[8]? 0; r[8]=r[8]-1; PC=IC>=0, B 1; M[r[14]. .](http://slidetodoc.com/presentation_image/b989f433bdbf289c7090d9d019166dbd/image-19.jpg)

Loop Effects B 1 M[r[14]]=0; r[14]=r[14]+4; IC=r[8]? 0; r[8]=r[8]-1; PC=IC>=0, B 1; M[r[14]. . r[14]+4*i]=0; r[8]=r[8]-i; 10/2/2020 M[y(B 1, w+4, r[14]) until y(B 1, w-1, r[8])<0]=0; r[8]=y(B 2, w-1, r[8]) until y(B 1, w-1, r[8])<0; SAC 03 19

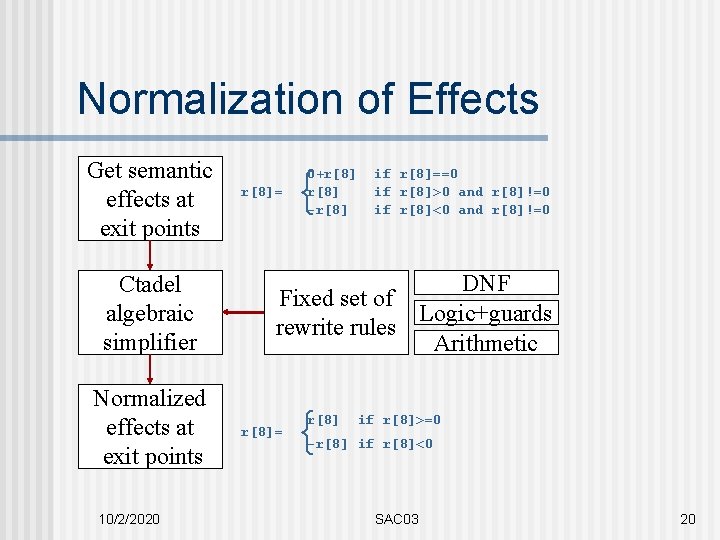

Normalization of Effects Get semantic effects at exit points Ctadel algebraic simplifier Normalized effects at exit points 10/2/2020 r[8]= { 0+r[8] -r[8] if r[8]==0 if r[8]>0 and r[8]!=0 if r[8]<0 and r[8]!=0 DNF Fixed set of Logic+guards rewrite rules Arithmetic r[8]= { r[8] if r[8]>=0 -r[8] if r[8]<0 SAC 03 20

![Normalization of Effects with DAGs M[r[14]]+. v]=r[8]; IC=r[8]? 0; PC=IC>=0, B 3 M[r[14]+. v]=(r[8] Normalization of Effects with DAGs M[r[14]]+. v]=r[8]; IC=r[8]? 0; PC=IC>=0, B 3 M[r[14]+. v]=(r[8]](http://slidetodoc.com/presentation_image/b989f433bdbf289c7090d9d019166dbd/image-21.jpg)

Normalization of Effects with DAGs M[r[14]]+. v]=r[8]; IC=r[8]? 0; PC=IC>=0, B 3 M[r[14]+. v]=(r[8] if r[8]>=0); M[r[14]+. v]=(r[8] if r[8]<0); r[9]=-r[8]; M[r[14]+. v]=r[9]; r[9]: M[r[14]+. v]=(-r[8] if r[8]<0); = M[r[14]. v] if if = - 10/2/2020 >=0 <0 SAC 03 r[8] 21

Benchmarks 10/2/2020 SAC 03 22

Benchmarks 10/2/2020 SAC 03 23

Benchmarks 10/2/2020 SAC 03 24

Conclusions Validation of both compiler and handspecified optimizations n Keep memory requirement low with DAG representation n Overhead is reasonable to justify assurance n 10/2/2020 SAC 03 25

- Slides: 25