Using Programmable Logic to Accelerate DSP Functions An

Using Programmable Logic to Accelerate DSP Functions “An Overview“ Greg Goslin Digital Signal Processing Applications Manager Corporate Applications Group 15 OCT 95

Agenda n When to use FPGAs for DSP, an Overview – What is Digital Signal Processing (DSP)? – Where is DSP Used? – Traditional DSP Approaches. n The Promise of Programmable Logic – Case Study: Finite Impulse Response Filter. – Case Study: Viterbi Decoder. n Building Fast Filters in FPGAs, a Tutorial – Efficient Algorithms for FPGAs. – Using Distributed Arithmetic for Filter Designs. – How to use an FPGA to Building Filter Designs. n Design Methodologies for DSP in FPGAs – Design Entry and Third Party Software Tools.

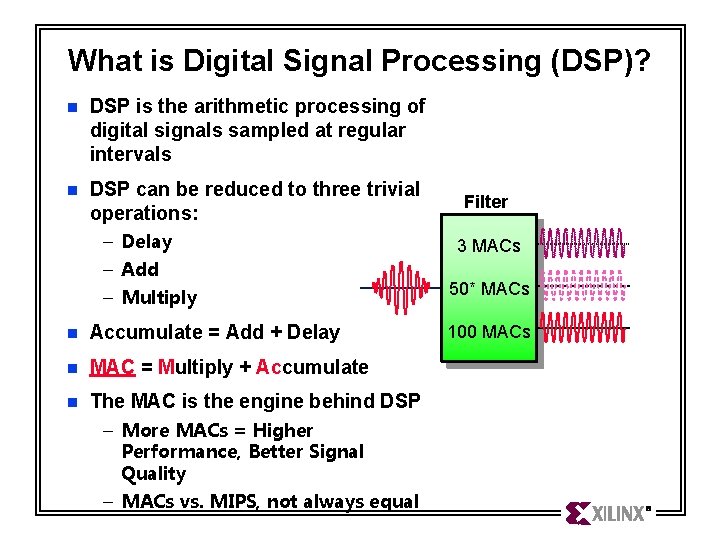

What is Digital Signal Processing (DSP)? n DSP is the arithmetic processing of digital signals sampled at regular intervals n DSP can be reduced to three trivial operations: – Delay – Add – Multiply n Accumulate = Add + Delay n MAC = Multiply + Accumulate n The MAC is the engine behind DSP – More MACs = Higher Performance, Better Signal Quality – MACs vs. MIPS, not always equal Filter 3 MACs 50* MACs 100 MACs

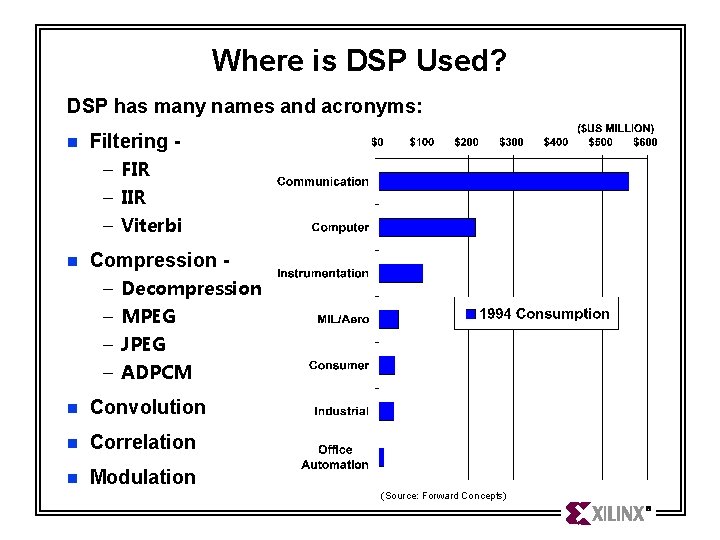

Where is DSP Used? DSP has many names and acronyms: n Filtering – FIR – IIR – Viterbi n Compression – Decompression – MPEG – JPEG – ADPCM n Convolution n Correlation n Modulation (Source: Forward Concepts)

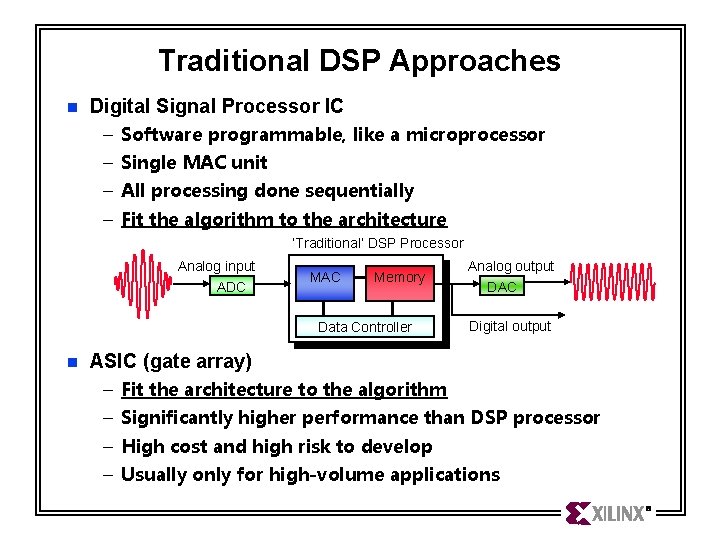

Traditional DSP Approaches n Digital Signal Processor IC – Software programmable, like a microprocessor – Single MAC unit – All processing done sequentially – Fit the algorithm to the architecture ‘Traditional’ DSP Processor Analog input ADC MAC Memory Data Controller n Analog output DAC Digital output ASIC (gate array) – Fit the architecture to the algorithm – Significantly higher performance than DSP processor – High cost and high risk to develop – Usually only for high-volume applications

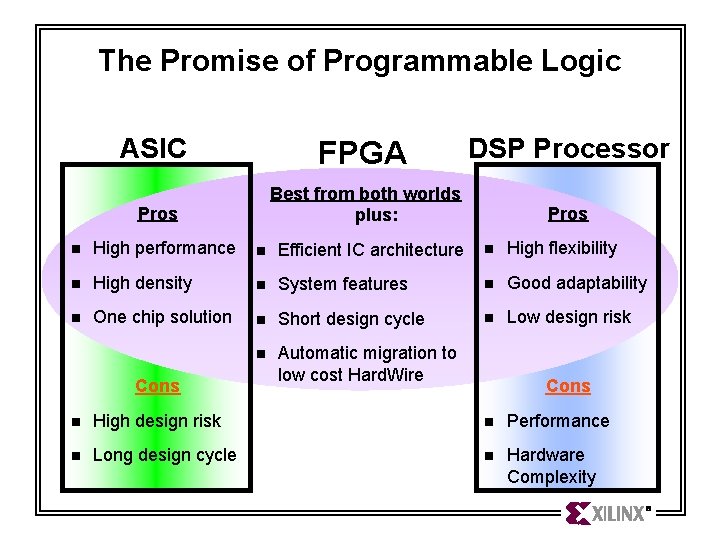

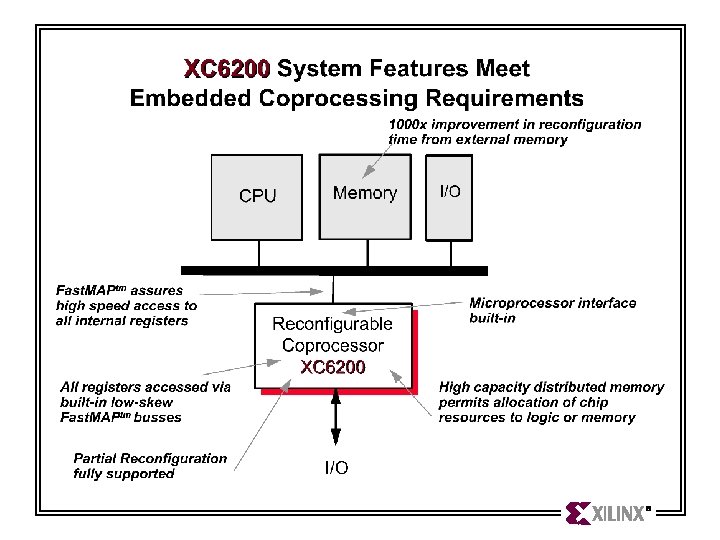

The Promise of Programmable Logic ASIC FPGA DSP Processor Pros Best from both worlds plus: Pros n High performance n Efficient IC architecture n High flexibility n High density n System features n Good adaptability n One chip solution n Short design cycle n Low design risk n Automatic migration to low cost Hard. Wire Cons n High design risk n Performance n Long design cycle n Hardware Complexity

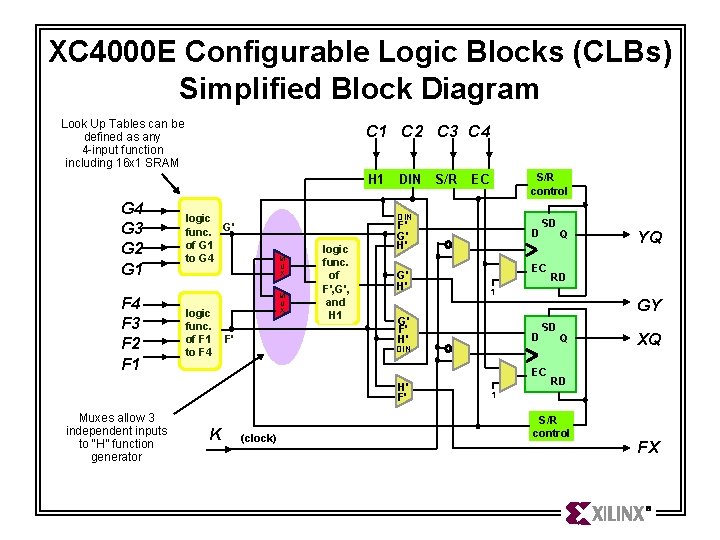

XC 4000 E Configurable Logic Blocks (CLBs) Simplified Block Diagram Look Up Tables can be defined as any 4 -input function including 16 x 1 SRAM C 1 C 2 C 3 C 4 H 1 G 4 G 3 G 2 G 1 F 4 F 3 F 2 F 1 S/R control EC M U X F' logic func. of F', G', and H 1 F' G' H' D SD EC D RD SD DIN (clock) YQ GY EC K Q 1 G' F' H' H' F' Muxes allow 3 independent inputs to “H” function generator S/R DIN logic func. G' of G 1 to G 4 logic func. of F 1 to F 4 DIN Q XQ RD 1 S/R control FX

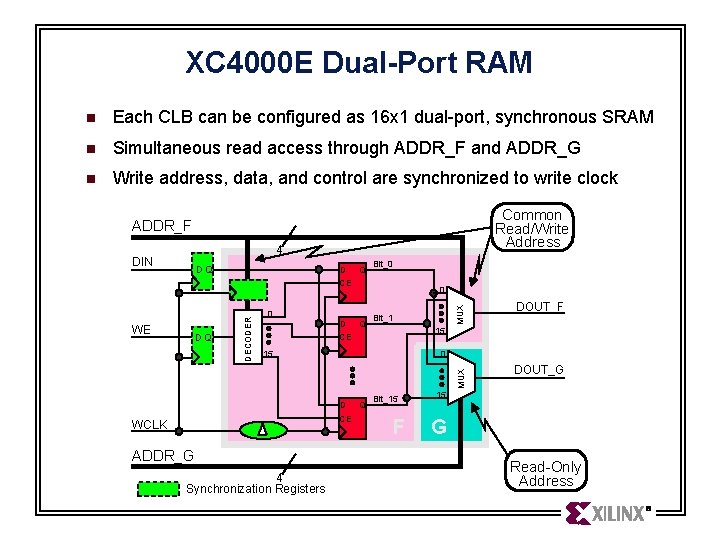

XC 4000 E Dual-Port RAM n Each CLB can be configured as 16 x 1 dual-port, synchronous SRAM n Simultaneous read access through ADDR_F and ADDR_G n Write address, data, and control are synchronized to write clock Common Read/Write Address ADDR_F 4 DQ 0 D Q CE Bit_0 0 Bit_1 15 0 D Q CE WCLK ADDR_G 4 Synchronization Registers DOUT_F 15 MUX DQ DECODER WE D Q CE MUX DIN Bit_15 F DOUT_G 15 G Read-Only Address

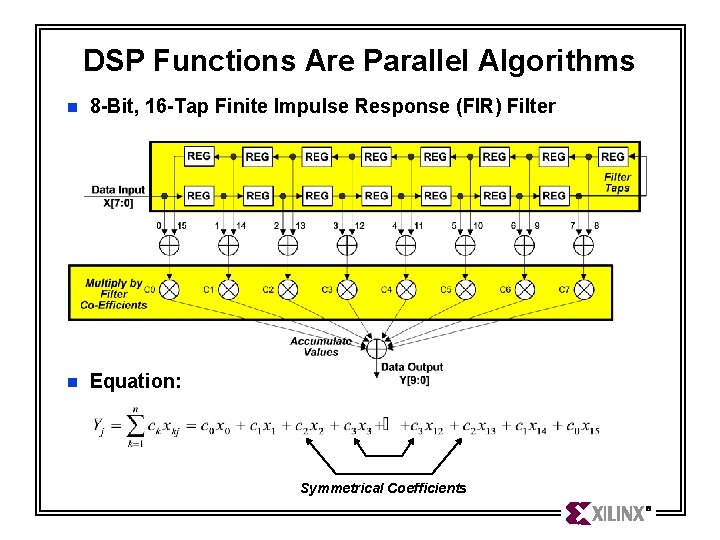

DSP Functions Are Parallel Algorithms n 8 -Bit, 16 -Tap Finite Impulse Response (FIR) Filter n Equation: Symmetrical Coefficients

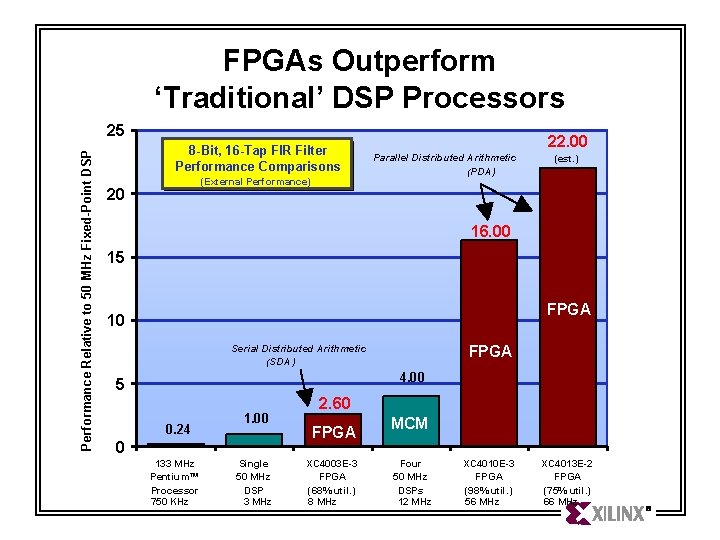

FPGAs Outperform ‘Traditional’ DSP Processors Performance Relative to 50 MHz Fixed-Point DSP 25 8 -Bit, 16 -Tap FIR Filter Performance Comparisons (External Performance) 20 22. 00 Parallel Distributed Arithmetic (PDA) (est. ) 16. 00 15 FPGA 10 FPGA Serial Distributed Arithmetic (SDA) 4. 00 5 0. 24 1. 00 0 133 MHz Pentium™ Processor 750 KHz Single 50 MHz DSP 3 MHz 2. 60 FPGA XC 4003 E-3 FPGA (68% util. ) 8 MHz MCM Four 50 MHz DSPs 12 MHz XC 4010 E-3 FPGA (98% util. ) 56 MHz XC 4013 E-2 FPGA (75% util. ) 66 MHz

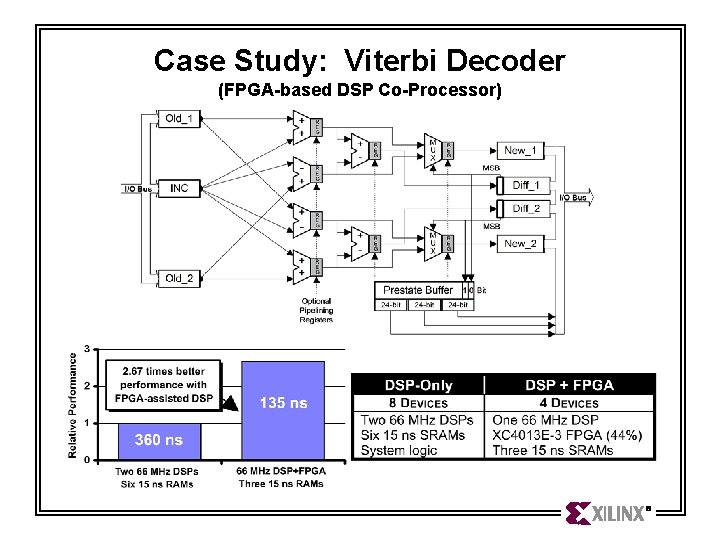

Case Study: Viterbi Decoder (FPGA-based DSP Co-Processor)

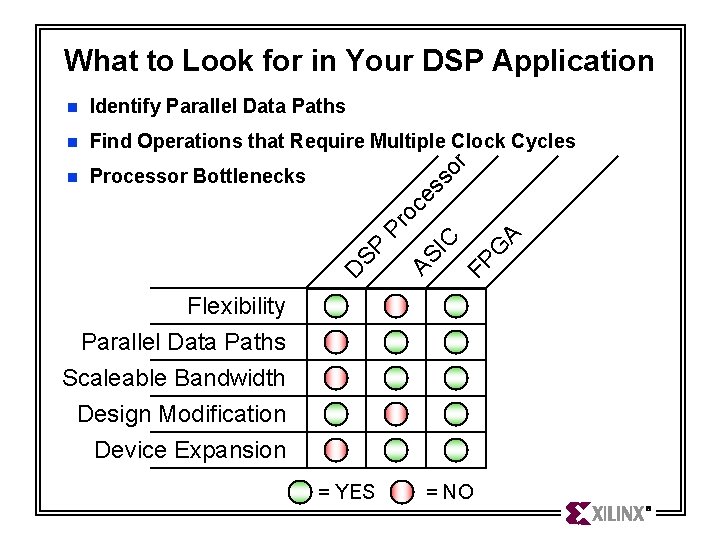

What to Look for in Your DSP Application Identify Parallel Data Paths n Find Operations that Require Multiple Clock Cycles n Processor Bottlenecks A FP G IC AS D SP Pr o ce ss or n Flexibility Parallel Data Paths Scaleable Bandwidth Design Modification Device Expansion = YES = NO

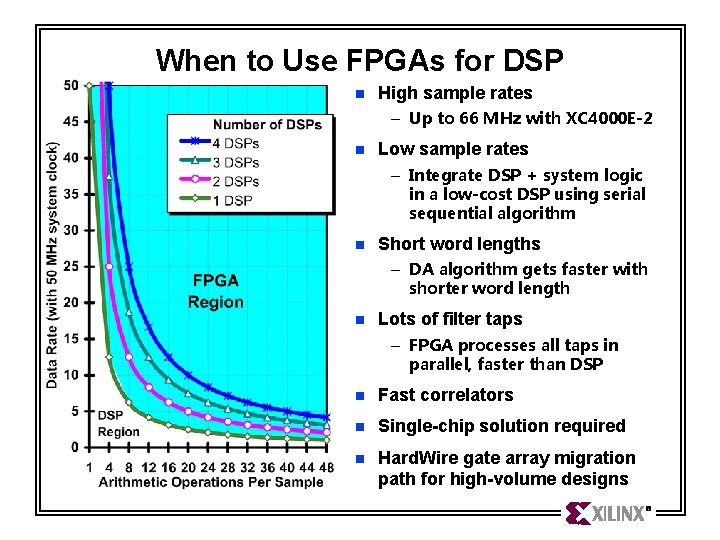

When to Use FPGAs for DSP n High sample rates – Up to 66 MHz with XC 4000 E-2 n Low sample rates – Integrate DSP + system logic in a low-cost DSP using serial sequential algorithm n Short word lengths – DA algorithm gets faster with shorter word length n Lots of filter taps – FPGA processes all taps in parallel, faster than DSP n Fast correlators n Single-chip solution required n Hard. Wire gate array migration path for high-volume designs

Information on DSP Applications n Greg Goslin – Digital Signal and Image Processing Applications Manager n Email: dsp@xilinx. com n WEB: http: //www. xilinx. com/dsp. htm n Fax: 408 -879 -4442

- Slides: 15