Uses of Synchronized Clocks in Test and Measurement

- Slides: 37

Uses of Synchronized Clocks in Test and Measurement Systems Jeff Burch, Adam Cataldo, John Eidson, Andrew Fernandez, Conrad Proft, Dieter Vook Measurement Research Laboratory, Agilent Technologies, Inc. CHESS March 3, 2009

Agenda 1. Overview of clock synchronization and driving applications 2. Test & measurement (LXI Class B instrumentation & DAQ) 3. Experimental results 4. Conclusions CHESS Slide March 3, 2009

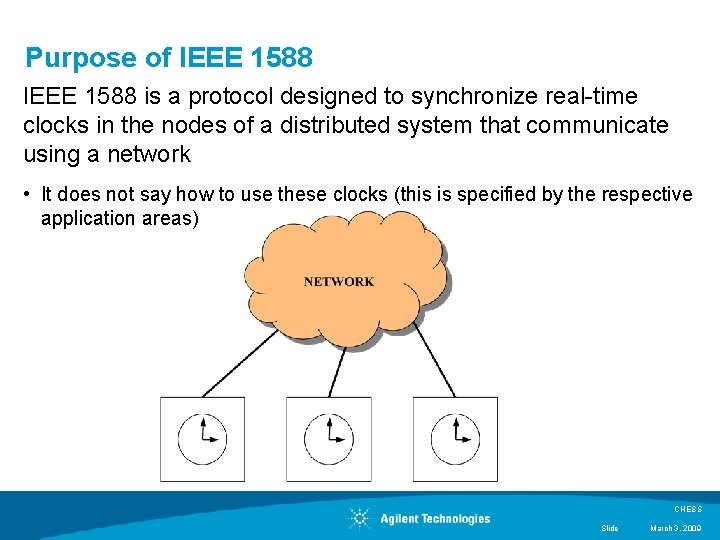

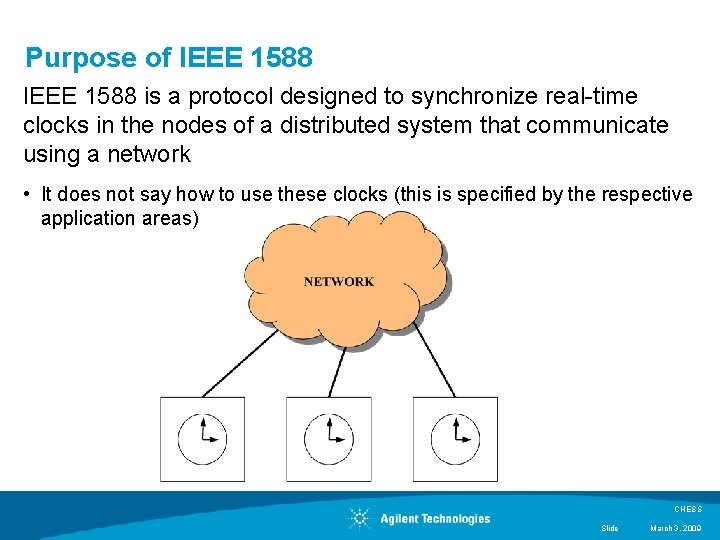

Purpose of IEEE 1588 is a protocol designed to synchronize real-time clocks in the nodes of a distributed system that communicate using a network • It does not say how to use these clocks (this is specified by the respective application areas) CHESS Slide March 3, 2009

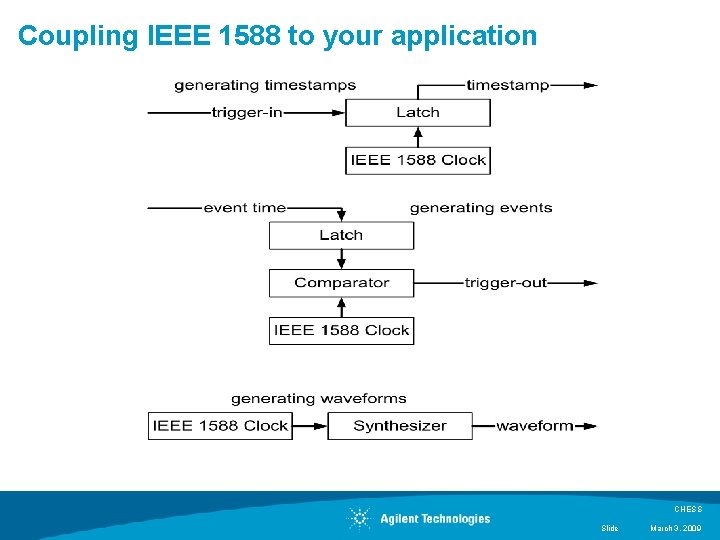

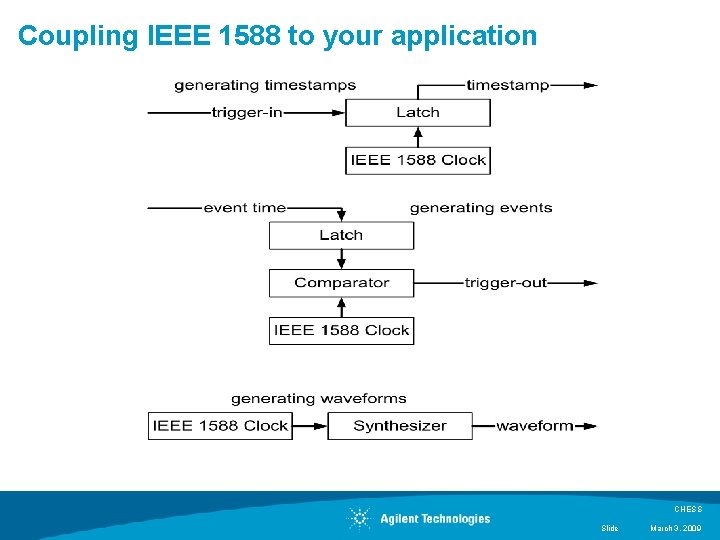

Coupling IEEE 1588 to your application CHESS Slide March 3, 2009

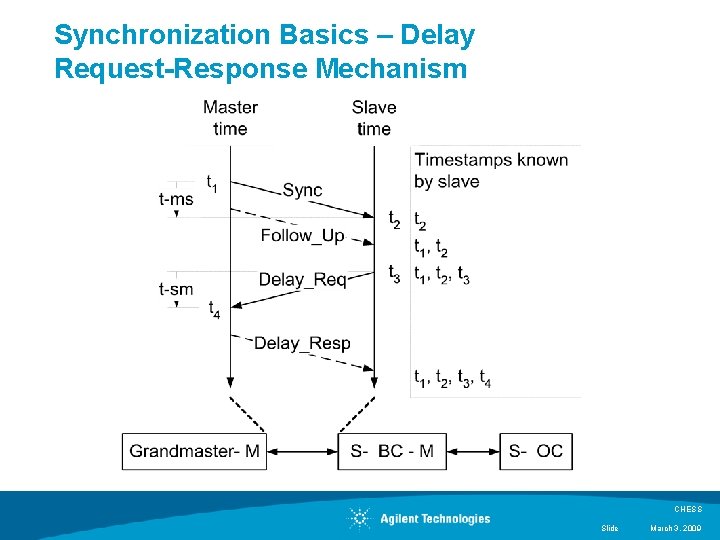

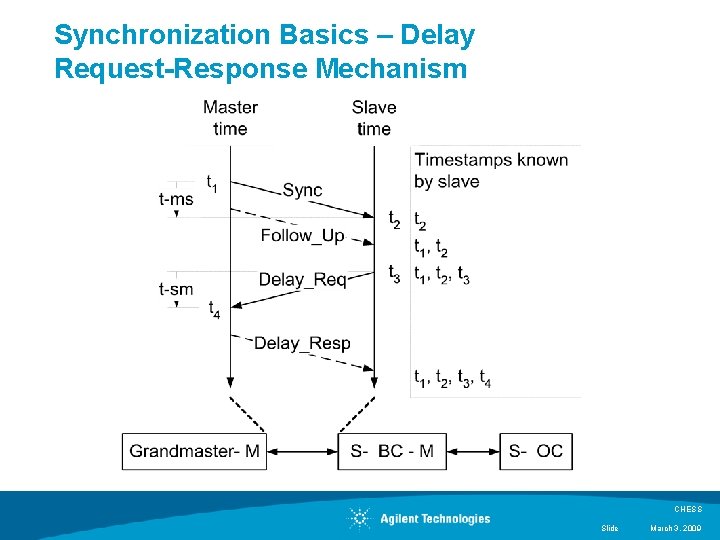

Synchronization Basics – Delay Request-Response Mechanism CHESS Slide March 3, 2009

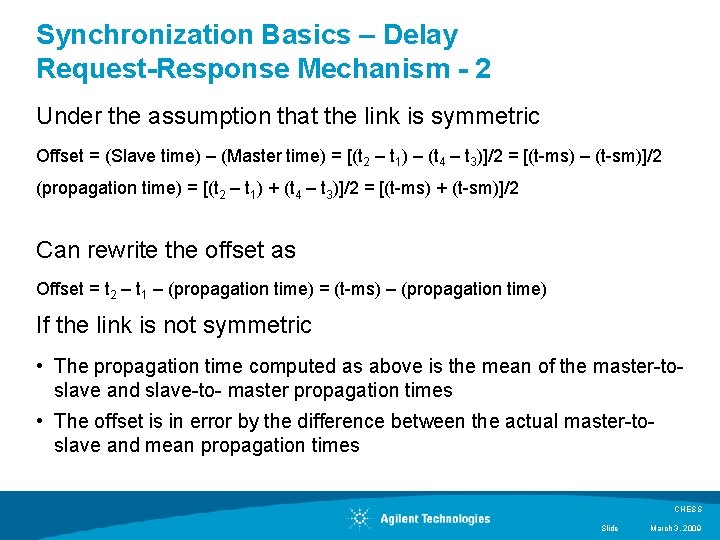

Synchronization Basics – Delay Request-Response Mechanism - 2 Under the assumption that the link is symmetric Offset = (Slave time) – (Master time) = [(t 2 – t 1) – (t 4 – t 3)]/2 = [(t-ms) – (t-sm)]/2 (propagation time) = [(t 2 – t 1) + (t 4 – t 3)]/2 = [(t-ms) + (t-sm)]/2 Can rewrite the offset as Offset = t 2 – t 1 – (propagation time) = (t-ms) – (propagation time) If the link is not symmetric • The propagation time computed as above is the mean of the master-toslave and slave-to- master propagation times • The offset is in error by the difference between the actual master-toslave and mean propagation times CHESS Slide March 3, 2009

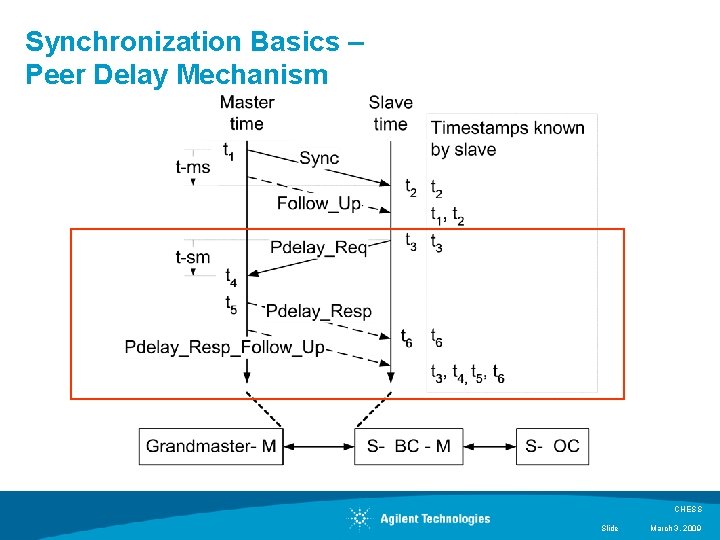

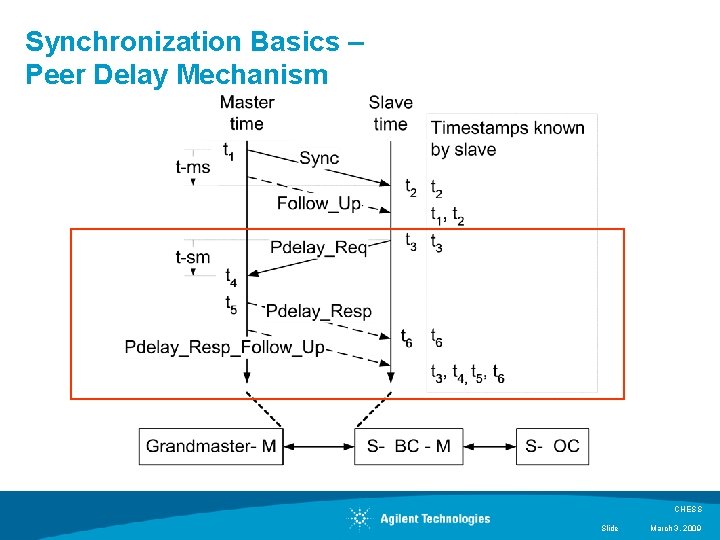

Synchronization Basics – Peer Delay Mechanism CHESS Slide March 3, 2009

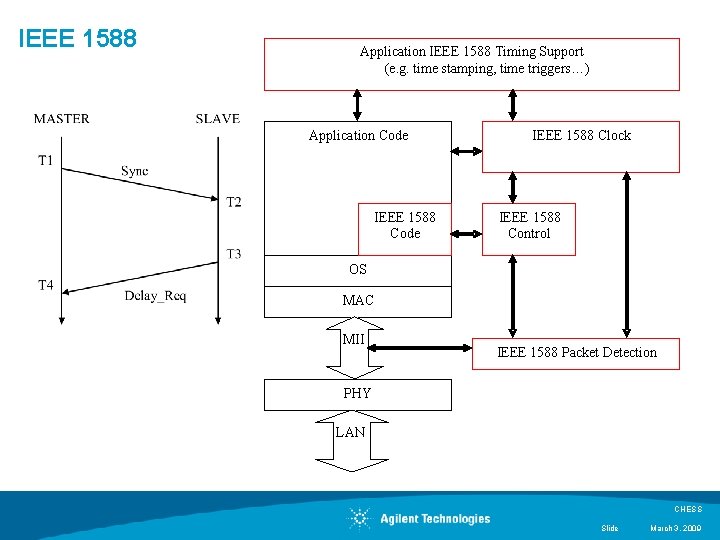

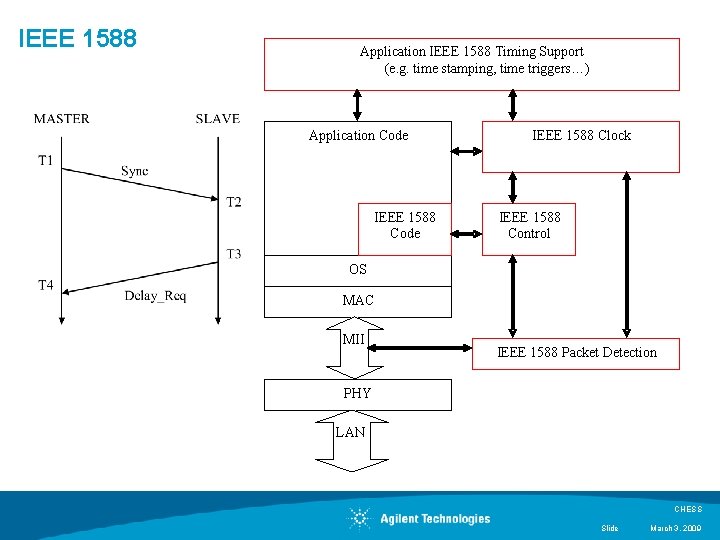

IEEE 1588 Application IEEE 1588 Timing Support (e. g. time stamping, time triggers…) Application Code IEEE 1588 Clock IEEE 1588 Control OS MAC MII IEEE 1588 Packet Detection PHY LAN CHESS Slide March 3, 2009

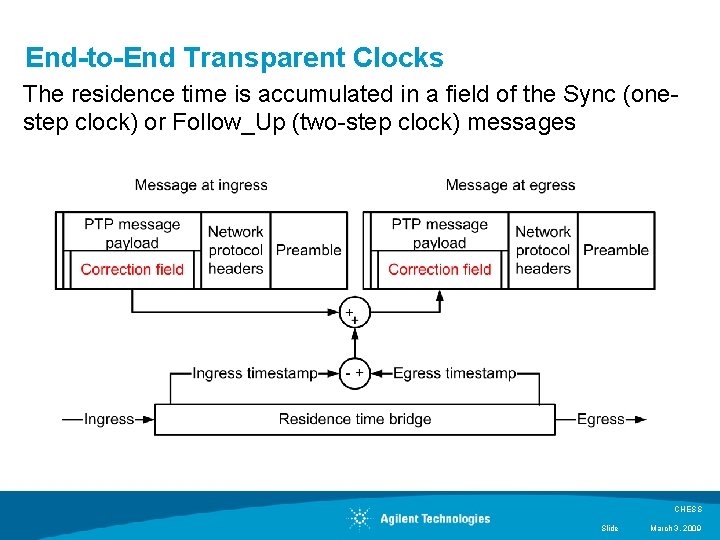

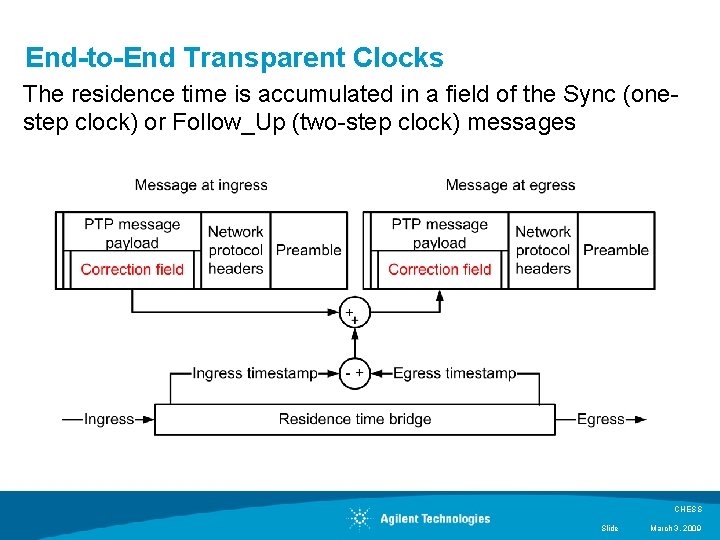

End-to-End Transparent Clocks The residence time is accumulated in a field of the Sync (onestep clock) or Follow_Up (two-step clock) messages CHESS Slide March 3, 2009

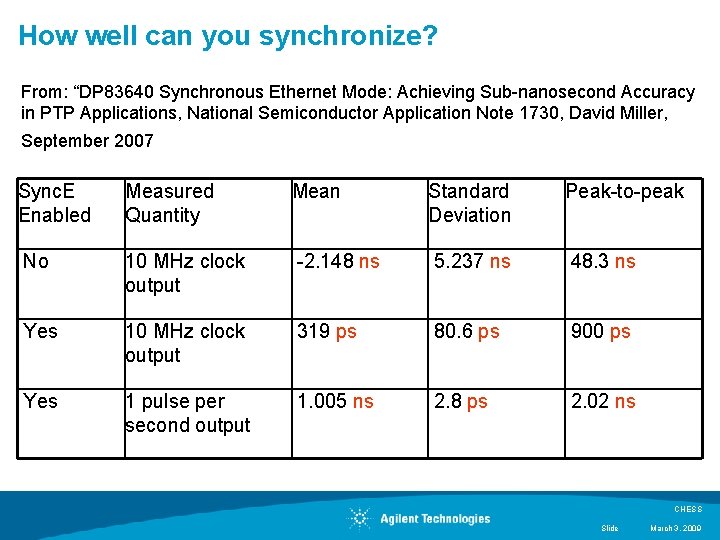

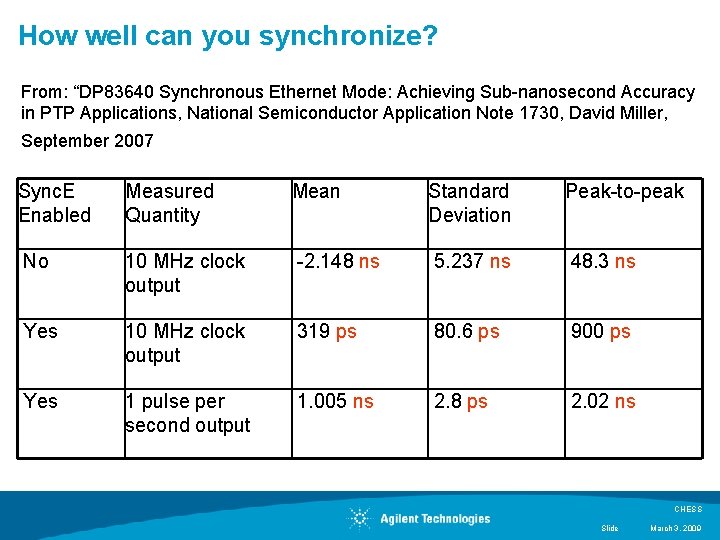

How well can you synchronize? From: “DP 83640 Synchronous Ethernet Mode: Achieving Sub-nanosecond Accuracy in PTP Applications, National Semiconductor Application Note 1730, David Miller, September 2007 Sync. E Enabled Measured Quantity Mean Standard Deviation Peak-to-peak No 10 MHz clock output -2. 148 ns 5. 237 ns 48. 3 ns Yes 10 MHz clock output 319 ps 80. 6 ps 900 ps Yes 1 pulse per second output 1. 005 ns 2. 8 ps 2. 02 ns CHESS Slide March 3, 2009

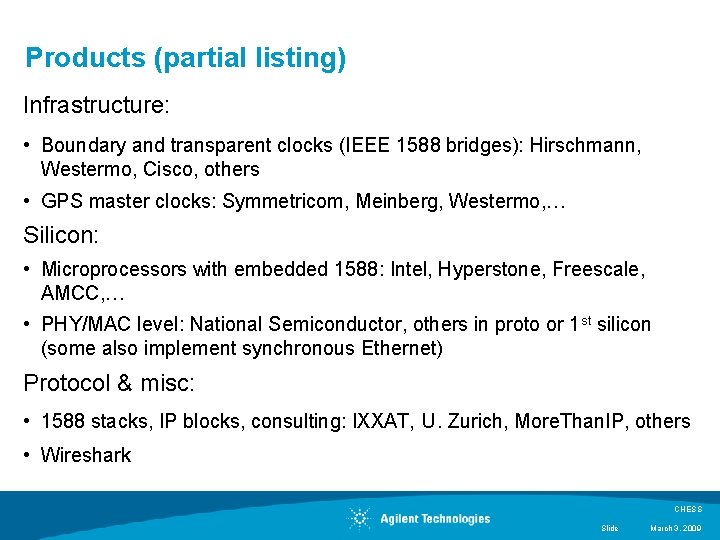

Products (partial listing) Infrastructure: • Boundary and transparent clocks (IEEE 1588 bridges): Hirschmann, Westermo, Cisco, others • GPS master clocks: Symmetricom, Meinberg, Westermo, … Silicon: • Microprocessors with embedded 1588: Intel, Hyperstone, Freescale, AMCC, … • PHY/MAC level: National Semiconductor, others in proto or 1 st silicon (some also implement synchronous Ethernet) Protocol & misc: • 1588 stacks, IP blocks, consulting: IXXAT, U. Zurich, More. Than. IP, others • Wireshark CHESS Slide March 3, 2009

Websites General IEEE 1588 site: contains product pointers, conference records, general guidance, standards related http: //ieee 1588. nist. gov/ ISPCS (International IEEE Symposium on Precision Clock Synchronization) site: Conference on IEEE 1588 and related subjects http: //www. ispcs. org/ CHESS Slide March 3, 2009

Robo. Team in Action: Process Relative Motion Courtesy of Kuka Robotics Corp. CHESS Slide March 3, 2009

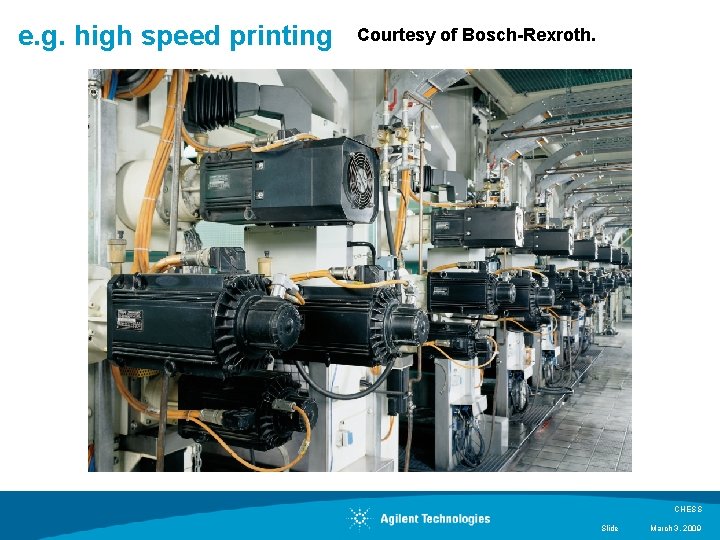

e. g. high speed printing Courtesy of Bosch-Rexroth. CHESS Slide March 3, 2009

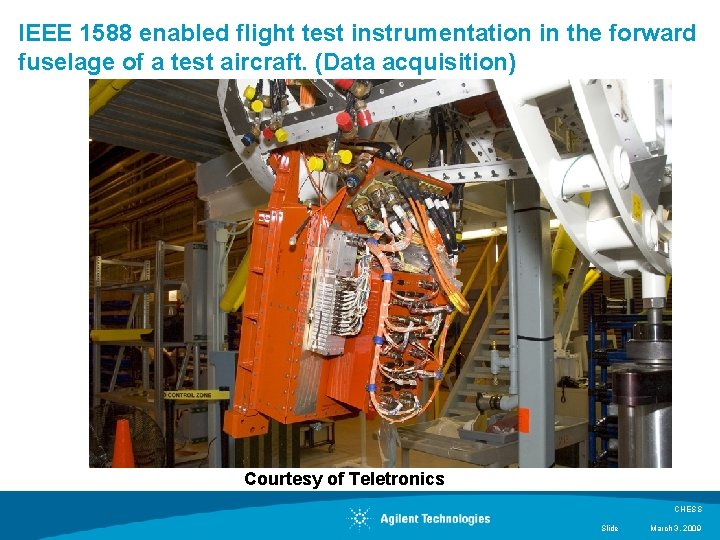

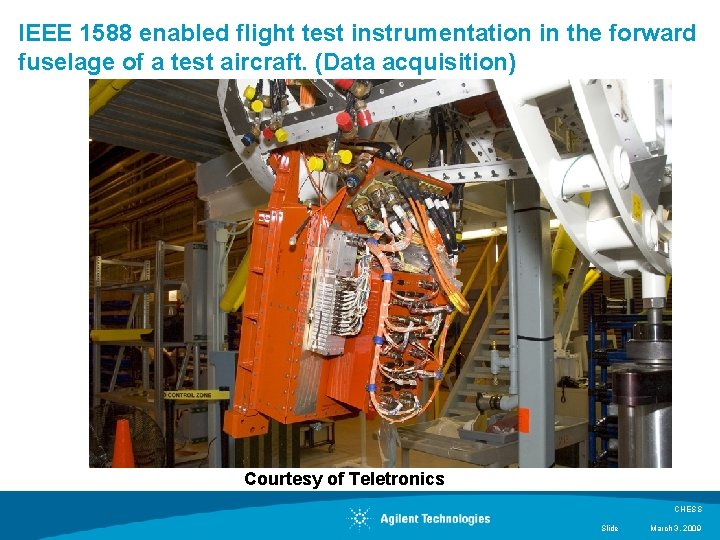

IEEE 1588 enabled flight test instrumentation in the forward fuselage of a test aircraft. (Data acquisition) Courtesy of Teletronics CHESS Slide March 3, 2009

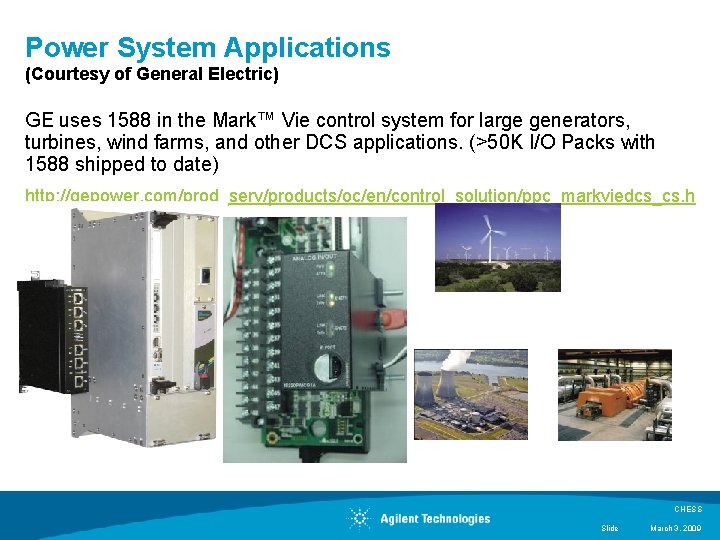

Power System Applications (Courtesy of General Electric) GE uses 1588 in the Mark™ Vie control system for large generators, turbines, wind farms, and other DCS applications. (>50 K I/O Packs with 1588 shipped to date) http: //gepower. com/prod_serv/products/oc/en/control_solution/ppc_markviedcs_cs. h tm CHESS Slide March 3, 2009

Power System Applications IEEE Power System Relaying Committee (PSRC) recently approved formation of Working Group H 7 "IEEE 1588 Profile for Protection Applications" CHESS Slide March 3, 2009

Telecommunications Applications Cellular backhaul is the major telecom application to date. Metro. Ethernet in field trial. Femtocells beginning. Companies involved (partial list): • Nokia-Siemens, Brilliant, Semtech, Zarlink, … CHESS Slide March 3, 2009

Audio/video systems applications Consumer electronics: IEEE 802. 1 as http: //www. ieee 802. org/1/pages/802. 1 as. html The “AVB” effort should be carefully investigated by both PTIDES and PRET. CHESS Slide March 3, 2009

LXI Class A&B Instrument Overview LXI Class-C A B Instrument LAN TCP HTTP PHY UDP SCPI TX RX P 2 P Meas FW Meas HW DUT TT TS App Code Event Log IEEE 1588 LXI Class B • IEEE 1588 Clock Sync • Peer-to-Peer Messages • Event Logs • Downloaded Application Code 8 LVDS Trigger Bus LXI Class A • Trigger Bus CHESS Slide March 3, 2009

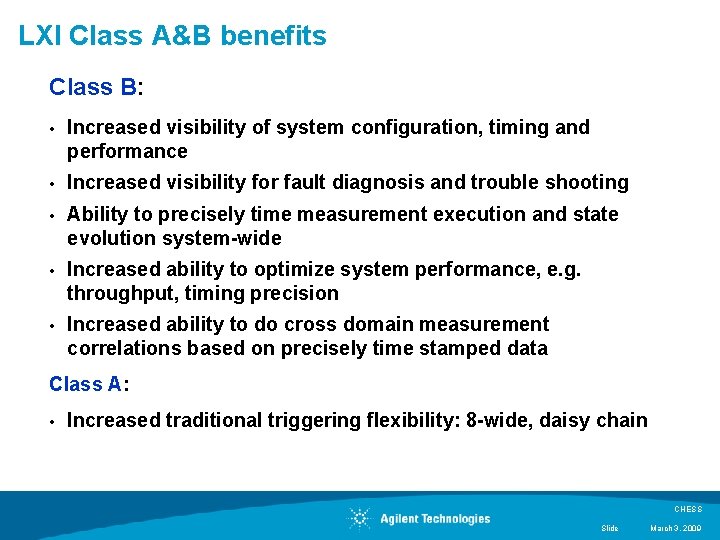

LXI Class A&B benefits Class B: • Increased visibility of system configuration, timing and performance • Increased visibility for fault diagnosis and trouble shooting • Ability to precisely time measurement execution and state evolution system-wide • Increased ability to optimize system performance, e. g. throughput, timing precision • Increased ability to do cross domain measurement correlations based on precisely time stamped data Class A: • Increased traditional triggering flexibility: 8 -wide, daisy chain CHESS Slide March 3, 2009

DEMO TIME! CHESS Slide March 3, 2009

LXI Class B experimental test system Experiments: 1. Frequency response 2. Fault shutdown Test system block diagram CHESS Slide March 3, 2009

LXI Class B experimental test system CHESS Slide March 3, 2009

PC Paced Instrument Sequencing-frequency response *TRG; *OPC? HW Trigger DONE CHESS Slide March 3, 2009

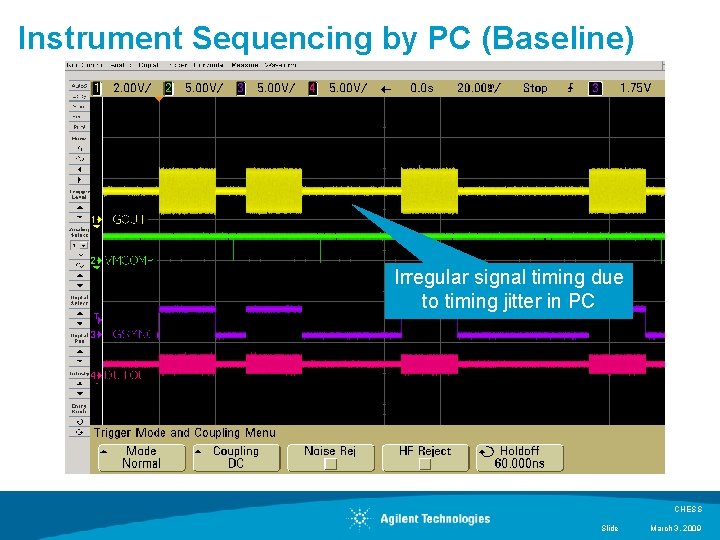

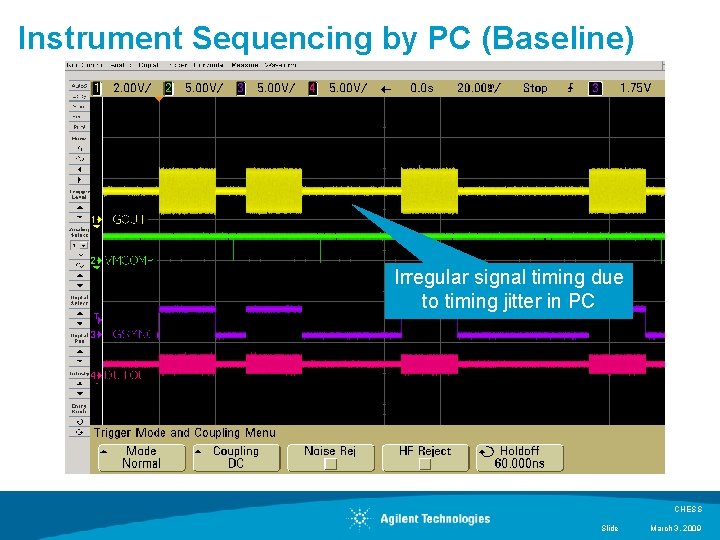

Instrument Sequencing by PC (Baseline) Irregular signal timing due to timing jitter in PC CHESS Slide March 3, 2009

Peer-to-Peer Instrument Sequencing MEASURE STEP COMPLETE CHESS Slide March 3, 2009

Instrument Sequencing by P 2 P Messages More regular signal timing CHESS Slide March 3, 2009

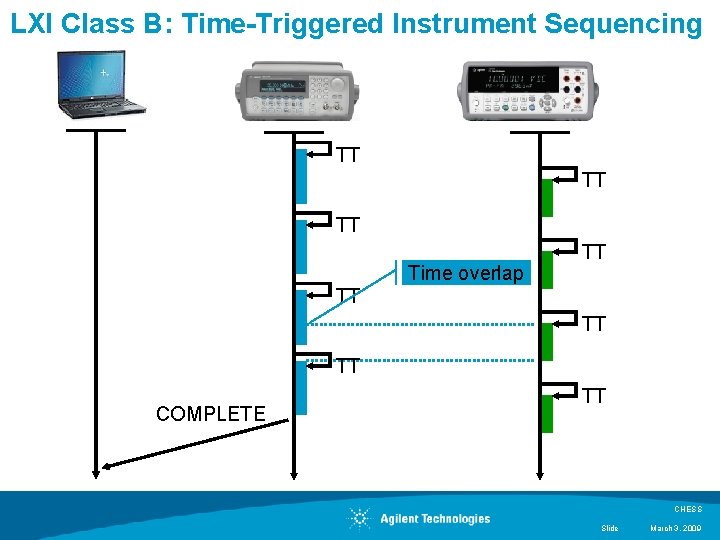

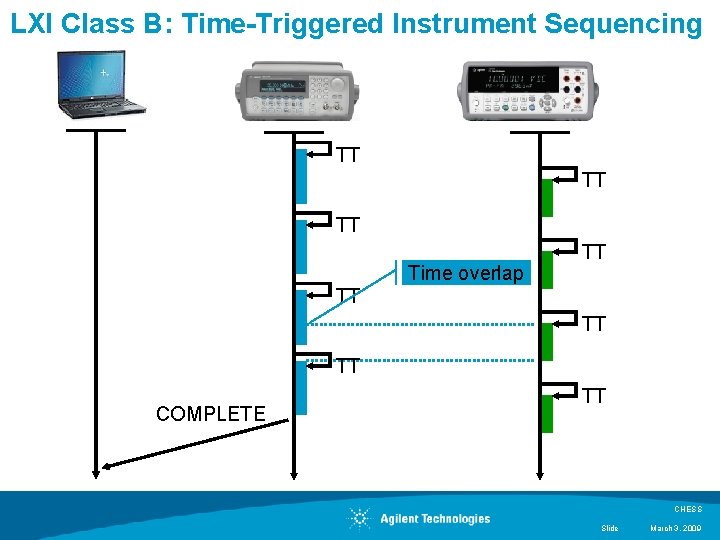

LXI Class B: Time-Triggered Instrument Sequencing TT TT TT Time overlap TT TT COMPLETE TT CHESS Slide March 3, 2009

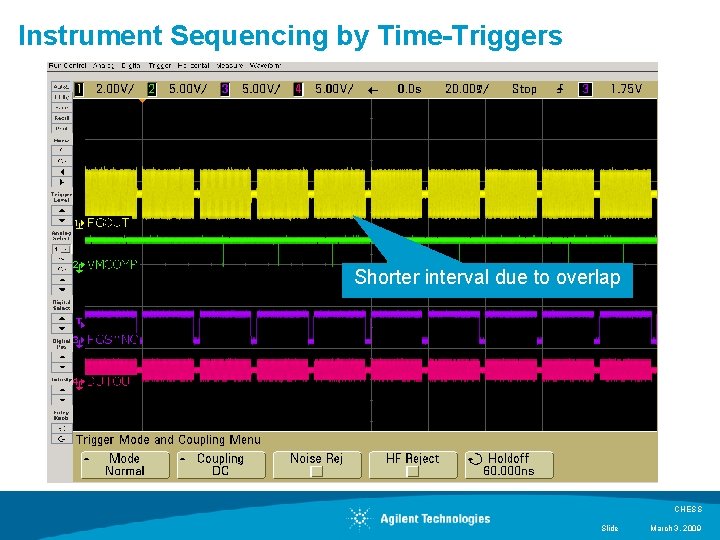

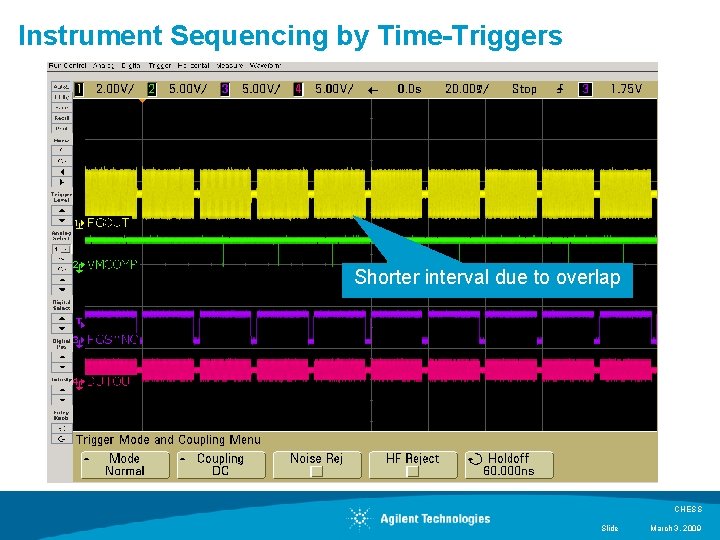

Instrument Sequencing by Time-Triggers Shorter interval due to overlap CHESS Slide March 3, 2009

Sequencing to measure frequency response CHESS Slide March 3, 2009

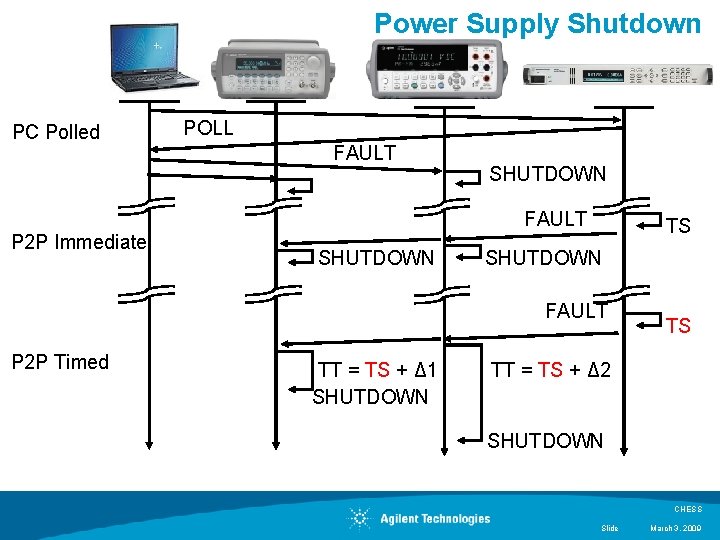

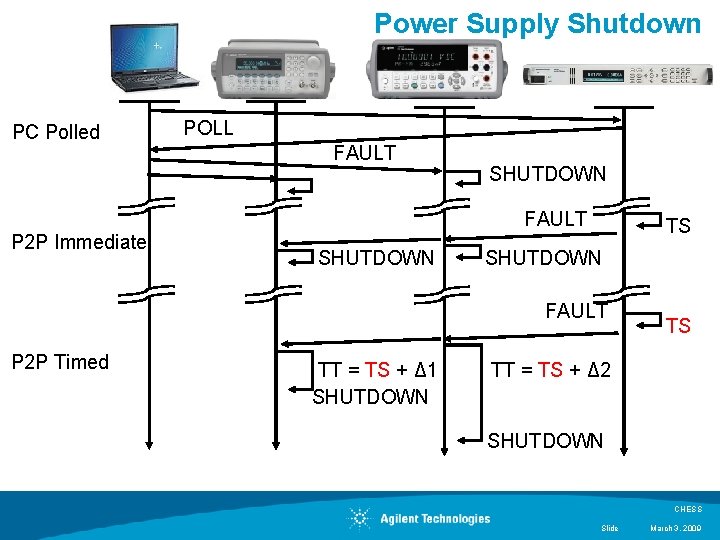

Power Supply Shutdown PC Polled P 2 P Immediate POLL FAULT SHUTDOWN TS SHUTDOWN FAULT P 2 P Timed TT = TS + Δ 1 SHUTDOWN TS TT = TS + Δ 2 SHUTDOWN CHESS Slide March 3, 2009

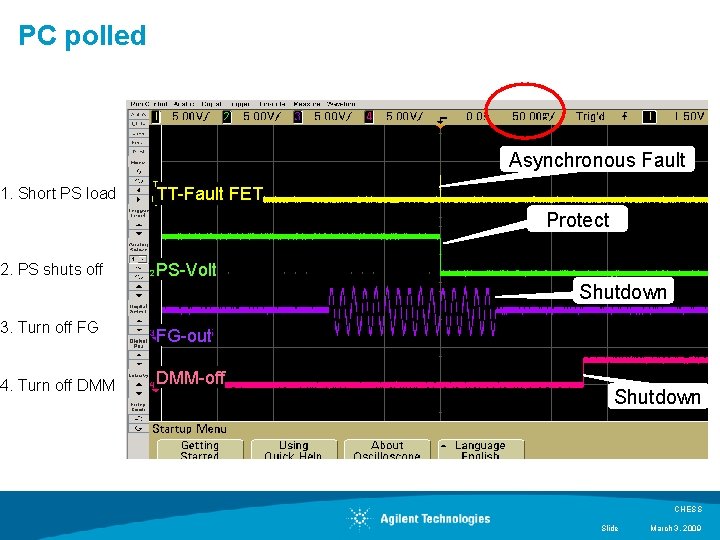

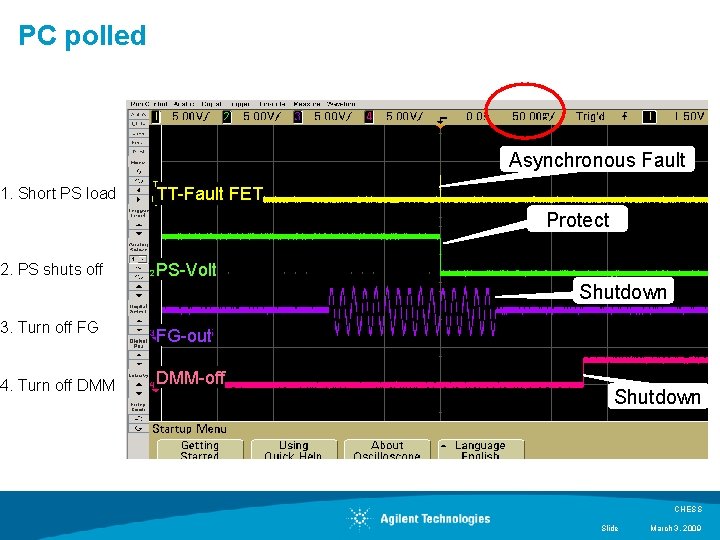

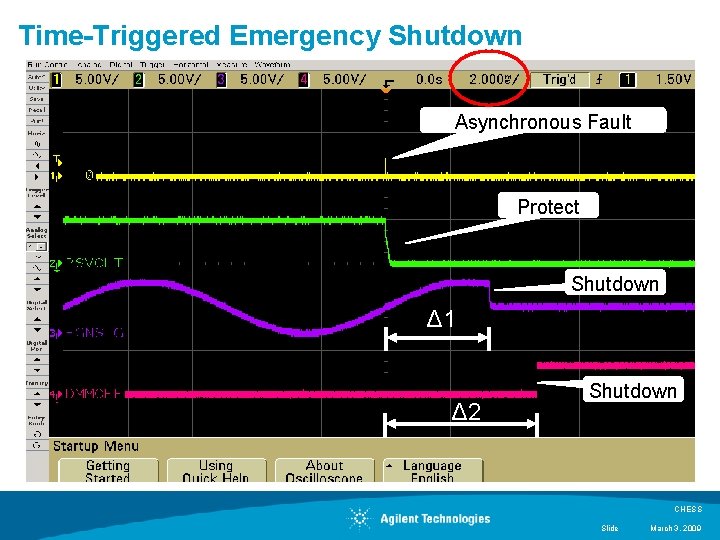

PC polled 1. Short PS load 2. PS shuts off Asynchronous Fault TT-Fault FET Protect PS-Volt Shutdown 3. Turn off FG FG-out 4. Turn off DMM-off Shutdown CHESS Slide March 3, 2009

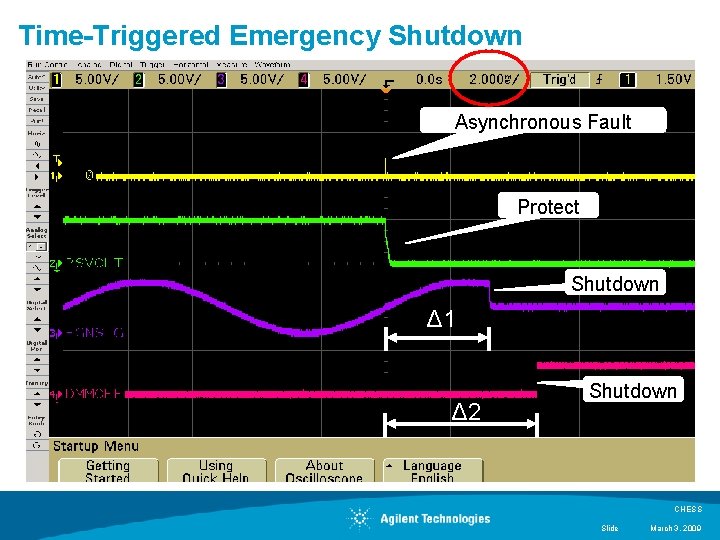

Time-Triggered Emergency Shutdown Asynchronous Fault Protect Shutdown Δ 1 Δ 2 Shutdown CHESS Slide March 3, 2009

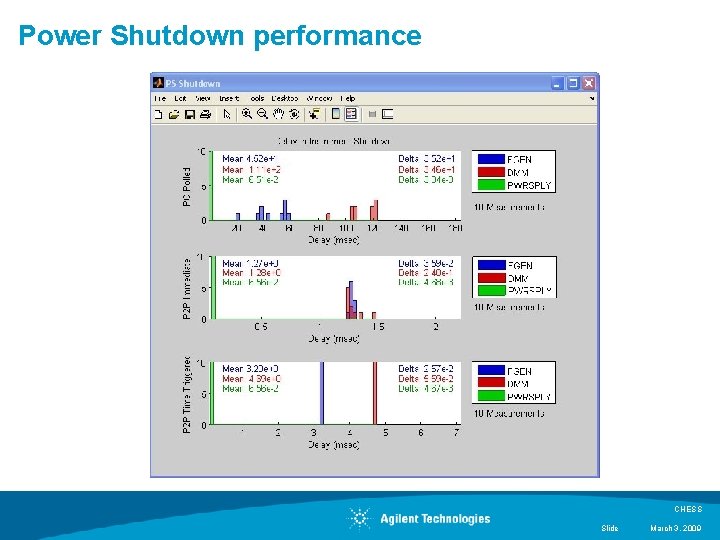

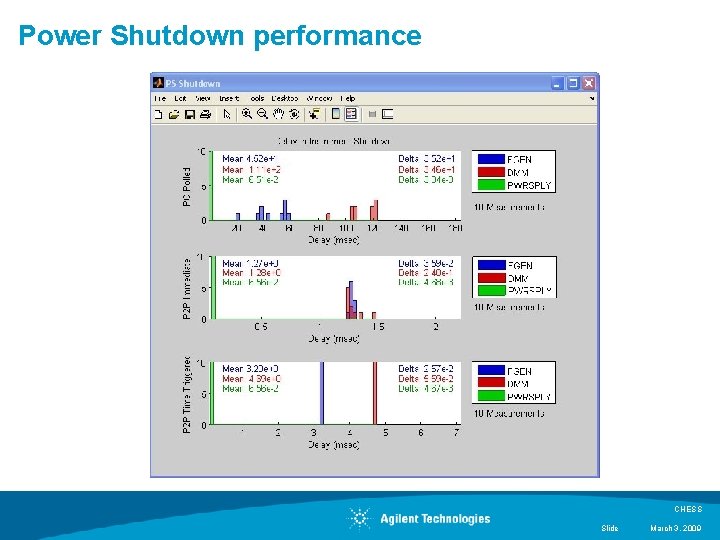

Power Shutdown performance CHESS Slide March 3, 2009

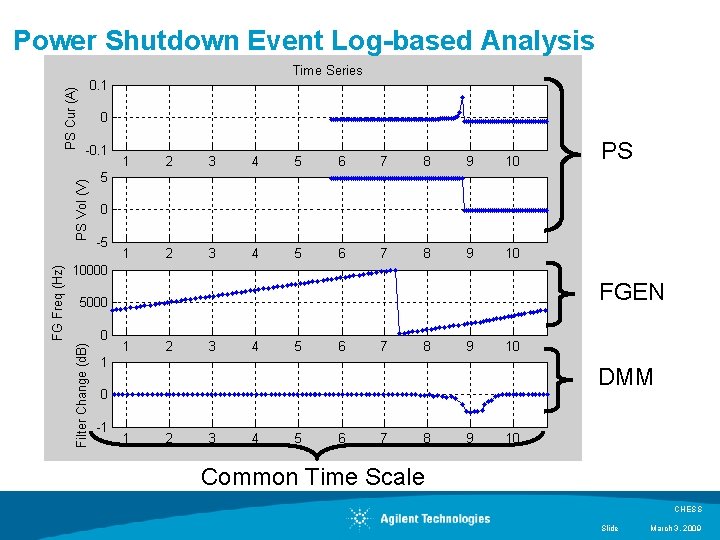

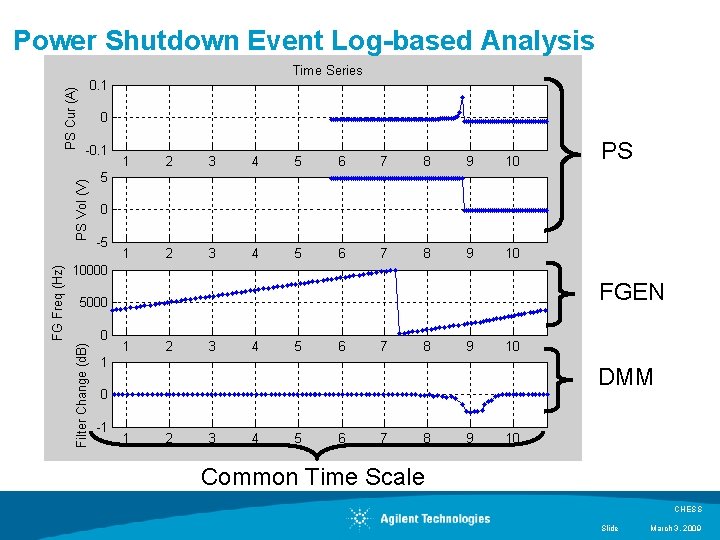

Power Shutdown Event Log-based Analysis PS FGEN DMM Common Time Scale CHESS Slide March 3, 2009

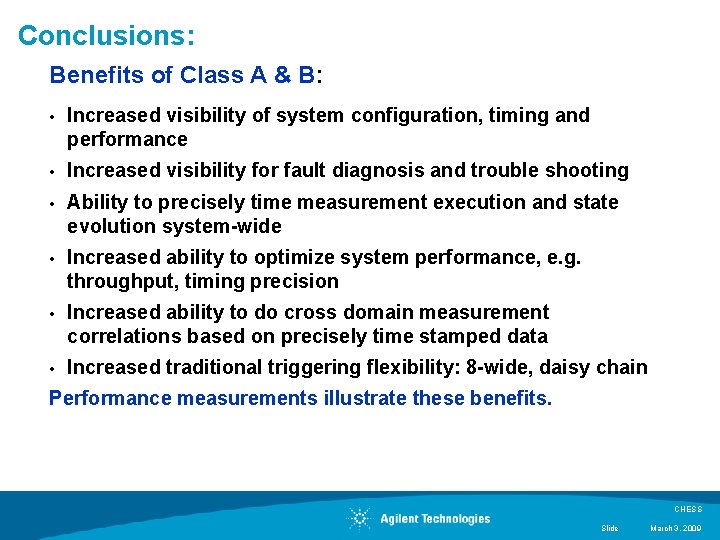

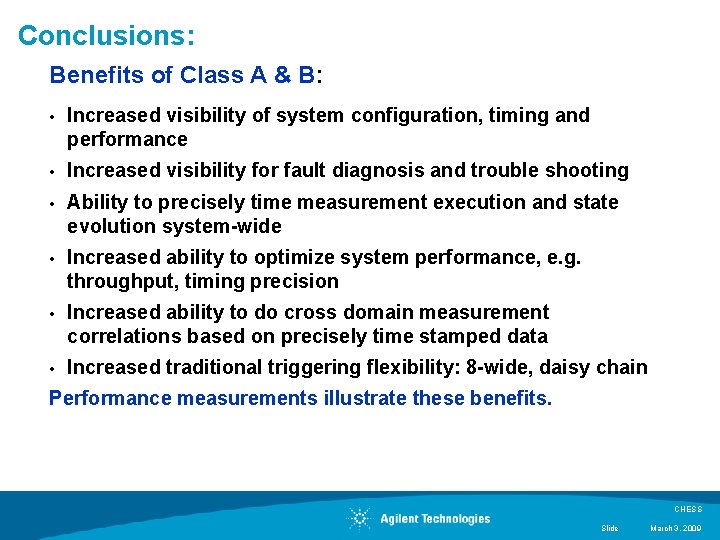

Conclusions: Benefits of Class A & B: • Increased visibility of system configuration, timing and performance • Increased visibility for fault diagnosis and trouble shooting • Ability to precisely time measurement execution and state evolution system-wide • Increased ability to optimize system performance, e. g. throughput, timing precision • Increased ability to do cross domain measurement correlations based on precisely time stamped data • Increased traditional triggering flexibility: 8 -wide, daisy chain Performance measurements illustrate these benefits. CHESS Slide March 3, 2009