USARTS CS 212 Dick Steflik Some Terminology Full

- Slides: 14

USARTS CS 212 Dick Steflik

Some Terminology Full Duplex - the ability to transmit and receive simultaneously Half Duplex - can transmit and receive but not at the same time RS-232 – A communications standard for bit serial communications Parity - An error detection mechanism based on the sum of the bits of a packet. The transmitted parity must equal the received parity Even Parity – the sum of the bits must always be even. Enforced by using an extra bit that is set on or off to ensure the sum on the bits is even. Odd Parity – the sum of the bits must always be odd. . Enforced by using an extra bit that is set on or off to ensure the sum on the bits is odd.

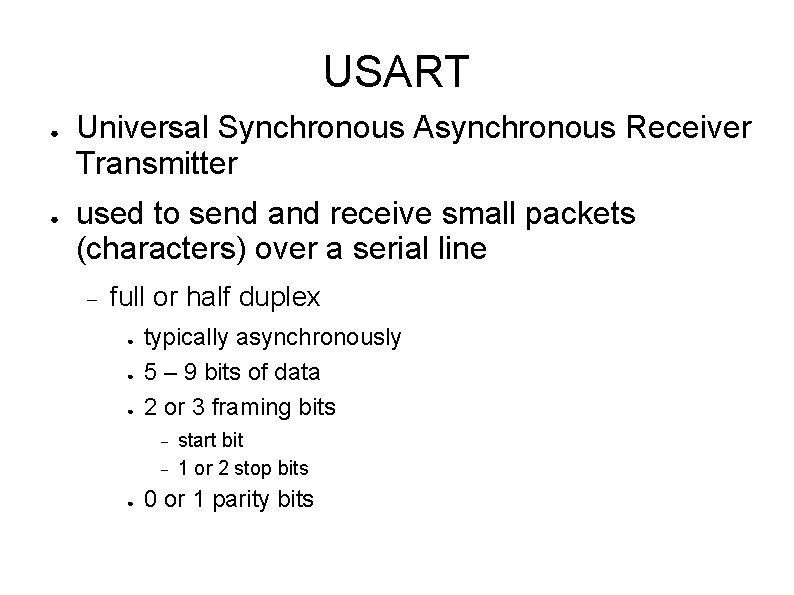

USART ● ● Universal Synchronous Asynchronous Receiver Transmitter used to send and receive small packets (characters) over a serial line full or half duplex ● ● ● typically asynchronously 5 – 9 bits of data 2 or 3 framing bits ● start bit 1 or 2 stop bits 0 or 1 parity bits

Data Format ● Must be agreed on by sender and receiver before any exchanges can be made ● stop bit (1 to 0 transition) ● 5 – 9 data bits ● 0 or 1 parity bits (odd or even parity) ● 1 or 2 stop bits (logic 0)

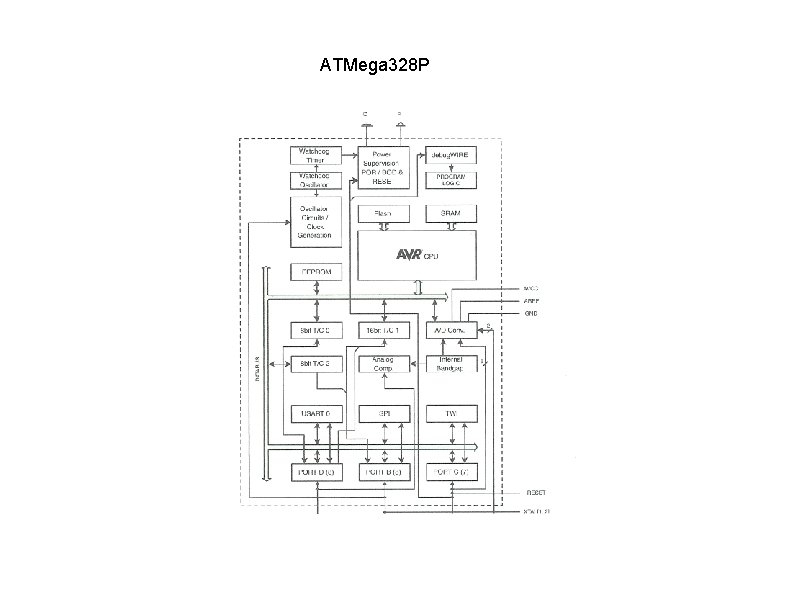

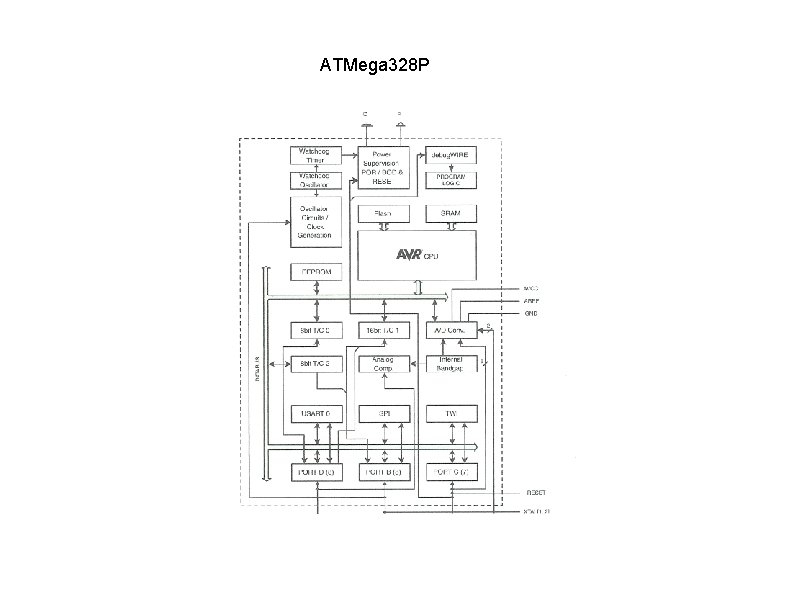

ATMega 328 P

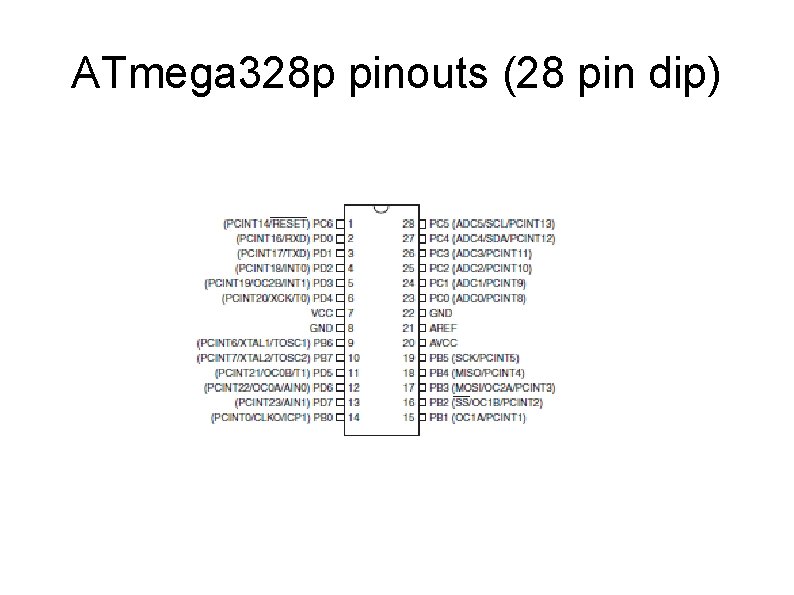

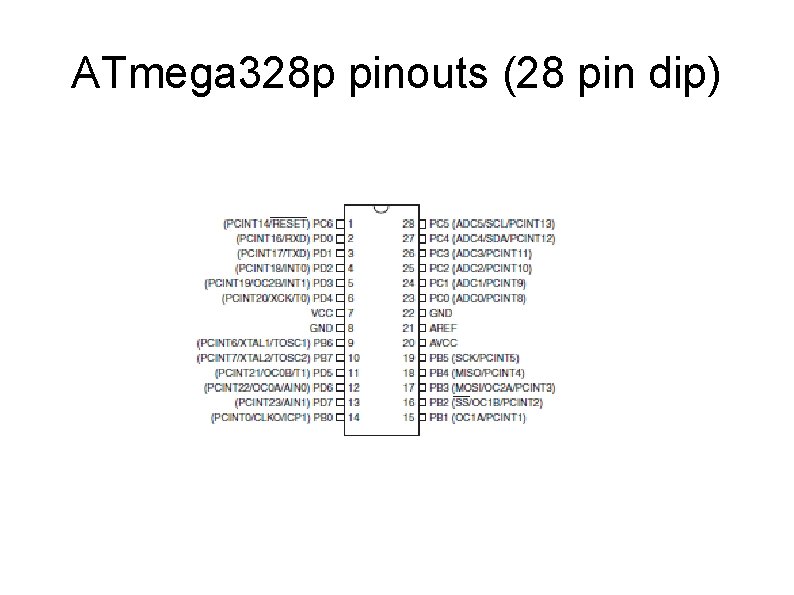

ATmega 328 p pinouts (28 pin dip)

Parity ● error detection mechanism ● odd parity ● even parity ● ● if an even number of data bits are 1 the parity bit is set to 1 to ensure an odd number of 1 s if an off number of data bits are 1 the parity bit is set to 1 to ensure an even number of bits are 1 s calculated and set by transmitter recalculated by receiver and compared to transmitted value, if no match a bit was either picked or dropped in transmission.

Programming Model ● Data input register ● Data output register ● Control register ● Status register ● speed, data bits, parity, stop bits, start, stop data ready, transmitting interrupts overflow, underflow, data ready, data sent

Sending data ● Remember synchronization is on a character by character basis ● check status ● load data register ● start transmit ● ● wait for transmission complete status or for interrupt repeat

Receiving data ● poll status register for data ready or wait for interrupt ● read data (save it) ● repeat

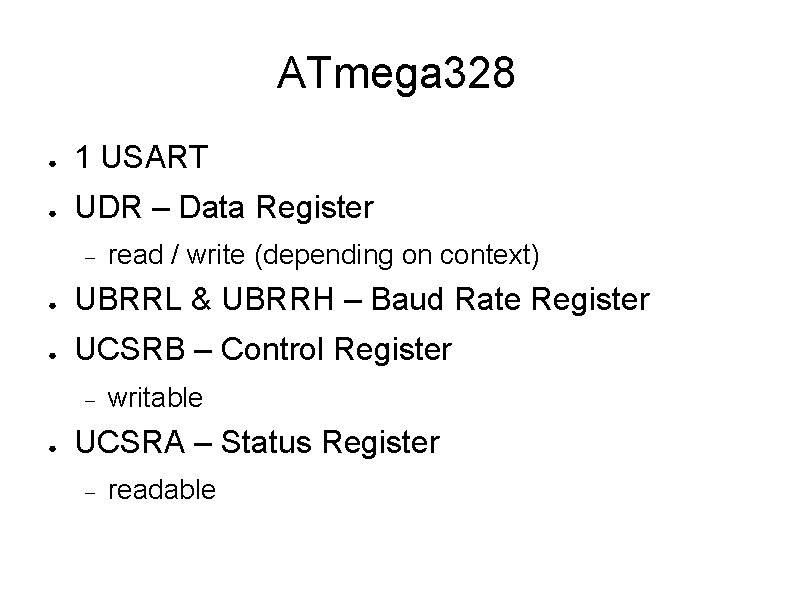

ATmega 328 ● 1 USART ● UDR – Data Register read / write (depending on context) ● UBRRL & UBRRH – Baud Rate Register ● UCSRB – Control Register ● writable UCSRA – Status Register readable

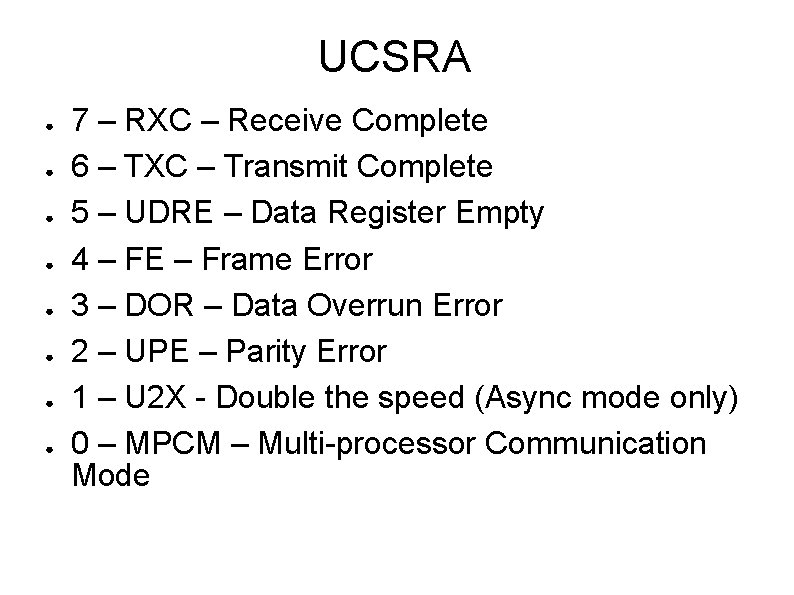

UCSRA ● ● ● ● 7 – RXC – Receive Complete 6 – TXC – Transmit Complete 5 – UDRE – Data Register Empty 4 – FE – Frame Error 3 – DOR – Data Overrun Error 2 – UPE – Parity Error 1 – U 2 X - Double the speed (Async mode only) 0 – MPCM – Multi-processor Communication Mode

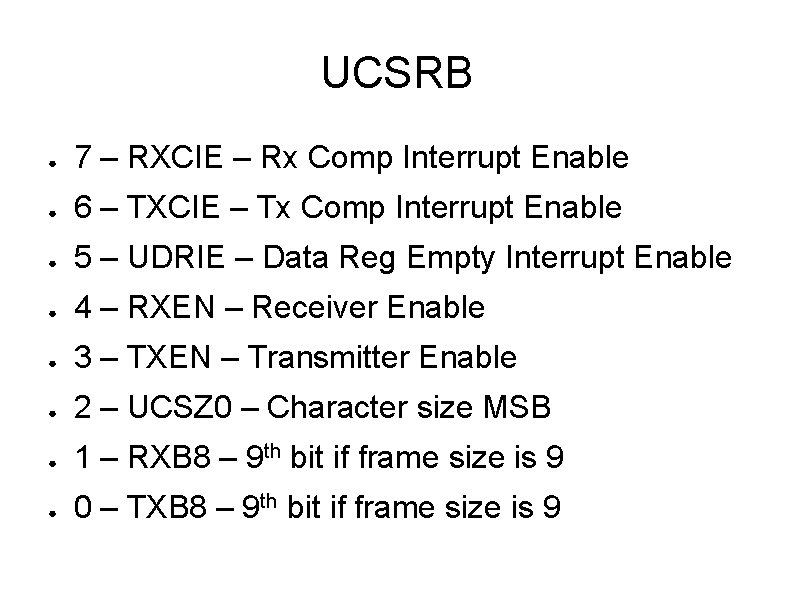

UCSRB ● 7 – RXCIE – Rx Comp Interrupt Enable ● 6 – TXCIE – Tx Comp Interrupt Enable ● 5 – UDRIE – Data Reg Empty Interrupt Enable ● 4 – RXEN – Receiver Enable ● 3 – TXEN – Transmitter Enable ● 2 – UCSZ 0 – Character size MSB ● 1 – RXB 8 – 9 th bit if frame size is 9 ● 0 – TXB 8 – 9 th bit if frame size is 9

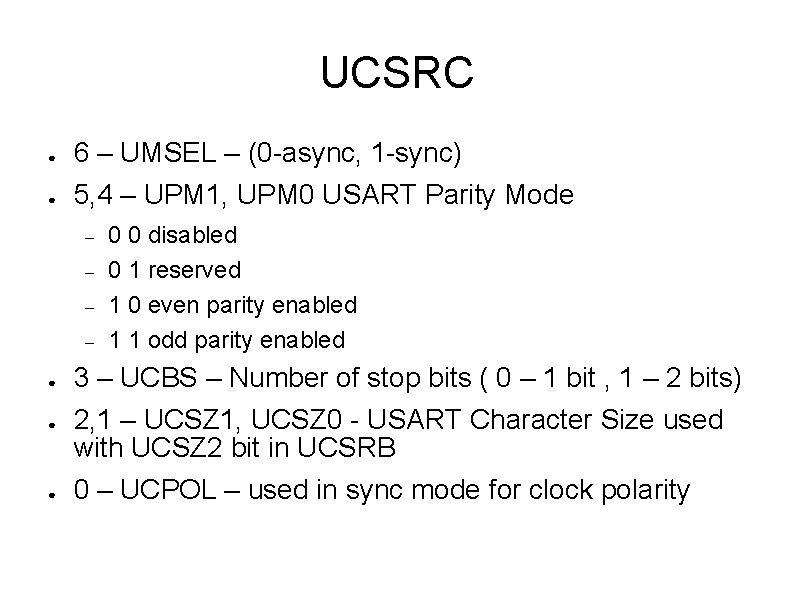

UCSRC ● 6 – UMSEL – (0 -async, 1 -sync) ● 5, 4 – UPM 1, UPM 0 USART Parity Mode ● ● ● 0 0 disabled 0 1 reserved 1 0 even parity enabled 1 1 odd parity enabled 3 – UCBS – Number of stop bits ( 0 – 1 bit , 1 – 2 bits) 2, 1 – UCSZ 1, UCSZ 0 - USART Character Size used with UCSZ 2 bit in UCSRB 0 – UCPOL – used in sync mode for clock polarity