University of Salahaddin College of Engineering Software Informatics

- Slides: 23

University of Salahaddin College of Engineering Software & Informatics Dep. COMPUTER ARCHITECTURE 2 ND STAGE ASSISTANT LECTURER: ESIL SEMIR KHURSHED [Lec 2] 2020 – 2019

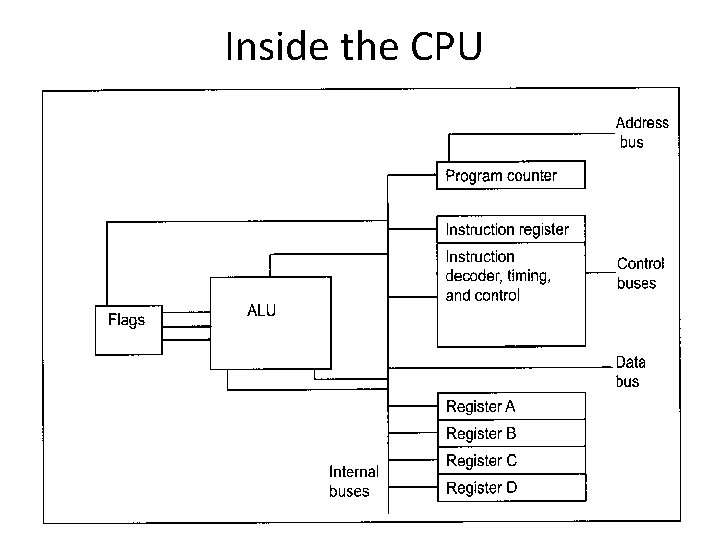

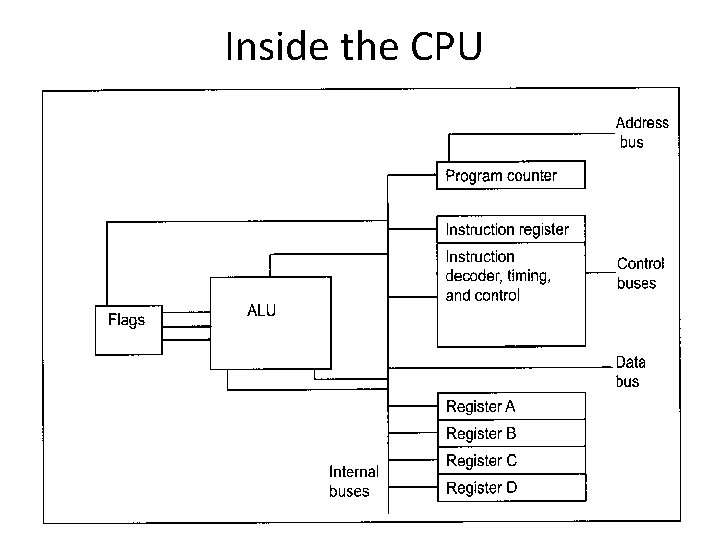

Inside the CPU

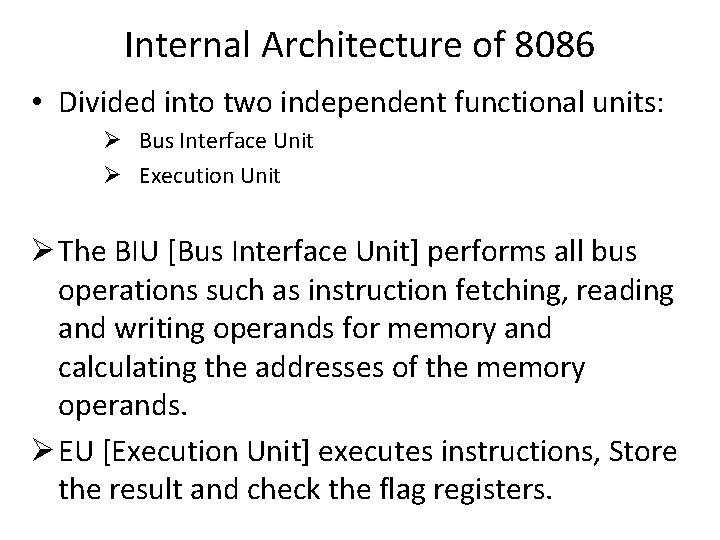

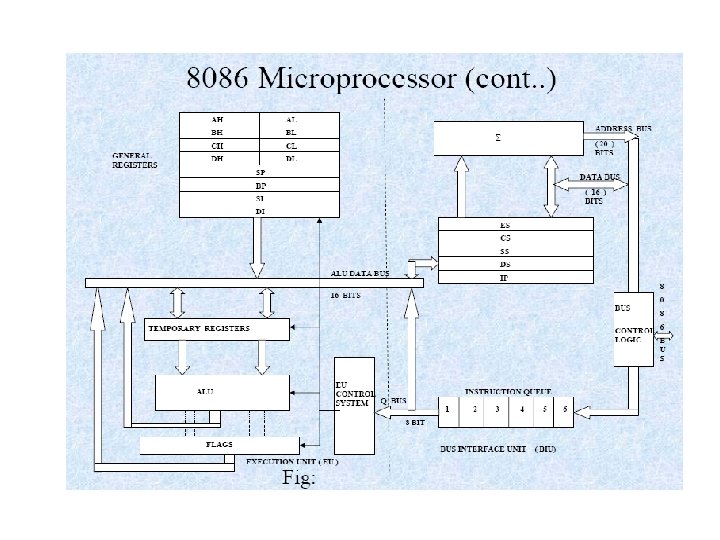

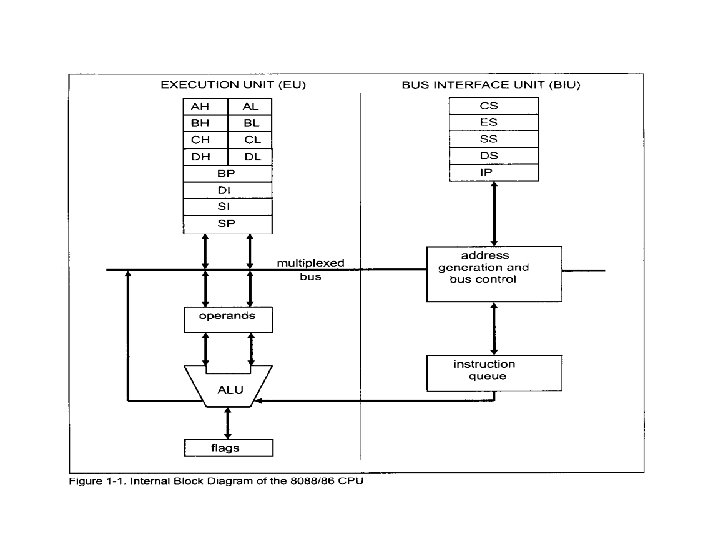

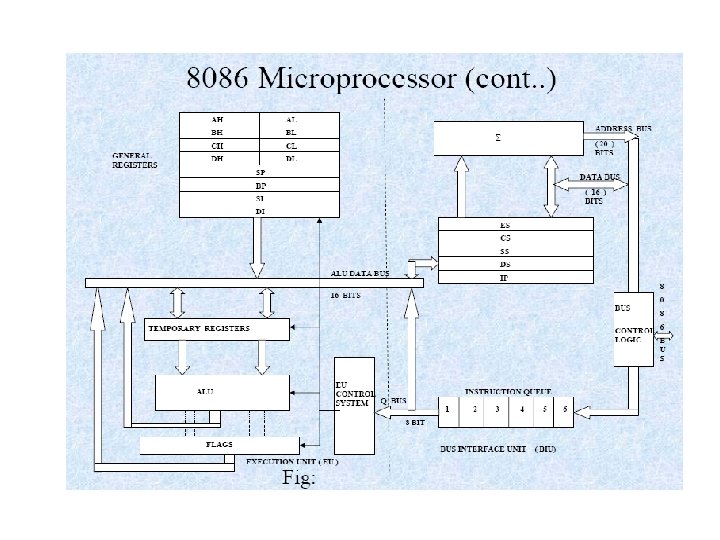

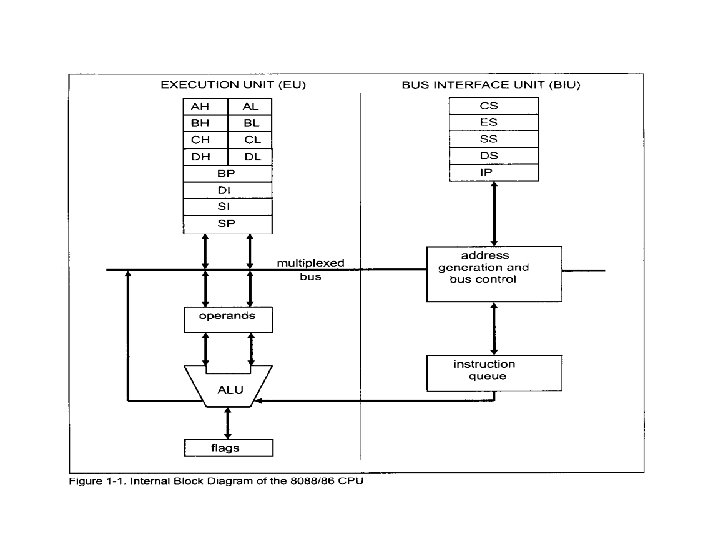

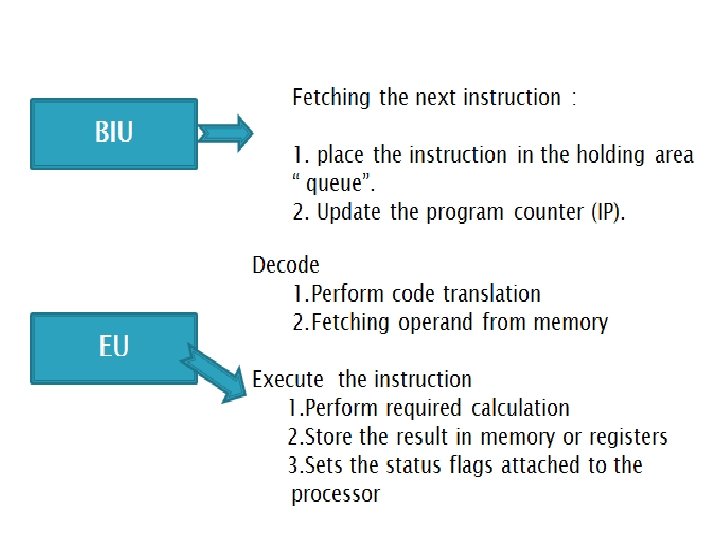

Internal Architecture of 8086 • Divided into two independent functional units: Ø Bus Interface Unit Ø Execution Unit Ø The BIU [Bus Interface Unit] performs all bus operations such as instruction fetching, reading and writing operands for memory and calculating the addresses of the memory operands. Ø EU [Execution Unit] executes instructions, Store the result and check the flag registers.

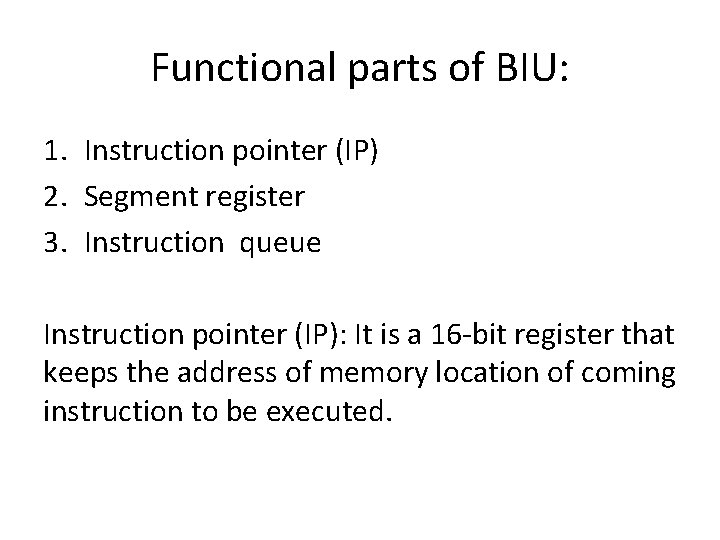

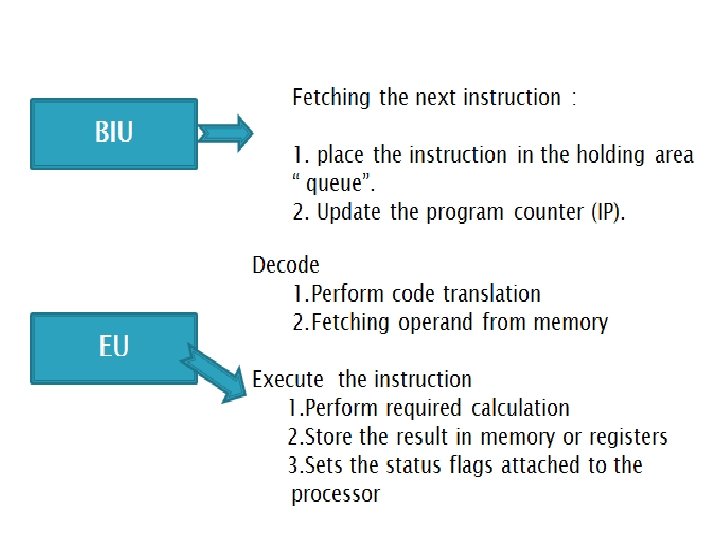

Functional parts of BIU: 1. Instruction pointer (IP) 2. Segment register 3. Instruction queue Instruction pointer (IP): It is a 16 -bit register that keeps the address of memory location of coming instruction to be executed.

• Segment register: the memory space 1 MB of 8086 segment into 4 block, each block specified by register with max size 64 -kb. • • Code segment (CS) Data segment (DS) Stack segment (SS) Extra segment (ES)

Instruction Queue: Is the main linkage between the two functional blocks is the instruction queue. • BIU performs its operation in parallel with execution unit. • BIU fetches instruction byte while execution unit is executing operations. • The pre-fetched inst. Is saved in group of high speed register and is known as instruction queue.

instruction queue • It is of 6 Bytes. • To increase the execution speed, BIU fetches as many as six instruction bytes ahead to time from memory. • It operates on the principle first in first out (FIFO). • Then all bytes are given to EU one by one. • This pre-fetching operation of BIU may be in parallel with execution operation of EU. • It improves the execution speed of the instruction

Internal Architecture of 8086 • Both units operate asynchronously to give the 8086 an overlapping instruction fetch and execution mechanism which is called as Pipelining. This results in efficient use of the system bus and system performance. • Pipelining is the process of accumulating instruction from the processor through a pipeline. It allows storing and executing instructions in an orderly process.

• BIU contains Instruction queue, Segment registres, Instruction pointer, Address adder. • EU contains Control circuitry, Instruction decoder, ALU, Pointer and Index register, Flag register. • The BIU uses a mechanism known as an instruction stream queue to implement a pipeline architecture.

EU Operation 1. Fetch an instruction from instruction queue. 2. According to the instruction, EU control logic generates control signal. [this process is also referred to as instruction decoding]. 3. Depending on the control signal, EU performs one of the following operation: ØAn arithmetic operation ØA logic operation ØStoring a data into a register ØMoving a data into a register ØChanging flag register

Functional parts of EU: • • • General purpose register. Pointer and indexed register. ALU Flag register. Timing and Control unit.

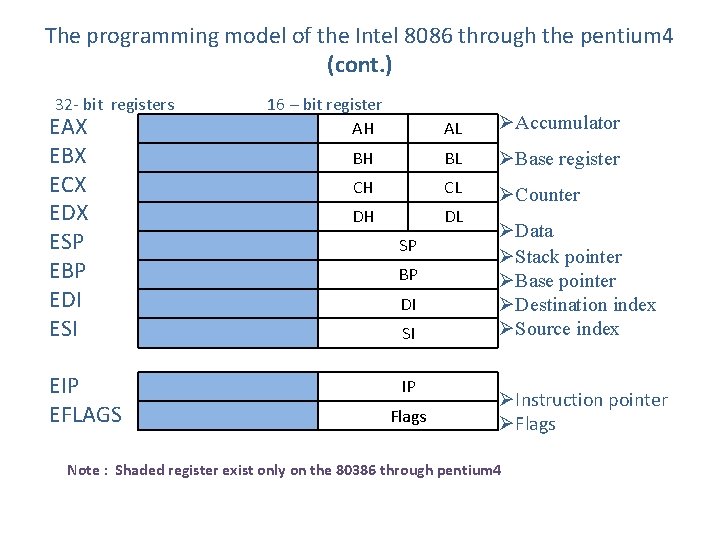

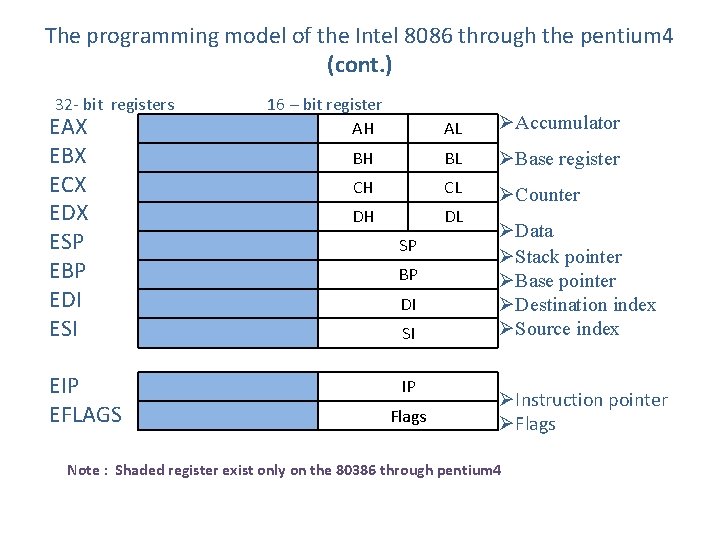

The programming model of the Intel 8086 through the pentium 4 (cont. ) 32 - bit registers EAX EBX ECX EDX ESP EBP EDI ESI EIP EFLAGS 16 – bit register AH AL ØAccumulator BH BL ØBase register CH CL ØCounter DH DL SP BP DI SI IP Flags ØData ØStack pointer ØBase pointer ØDestination index ØSource index ØInstruction pointer ØFlags Note : Shaded register exist only on the 80386 through pentium 4

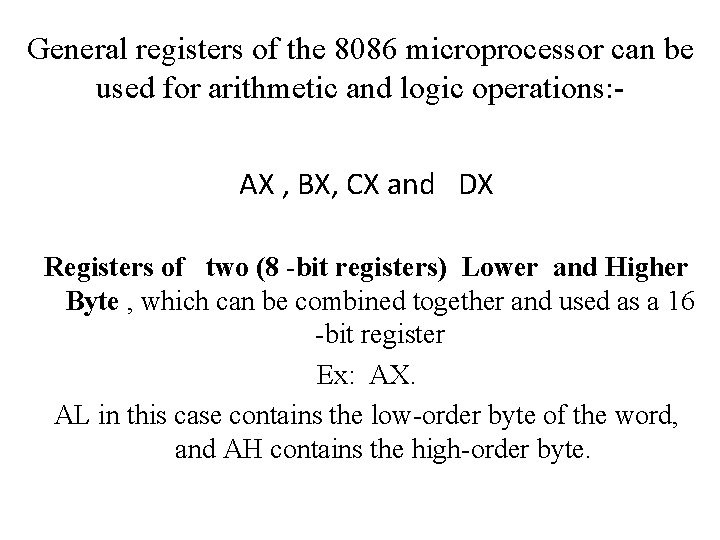

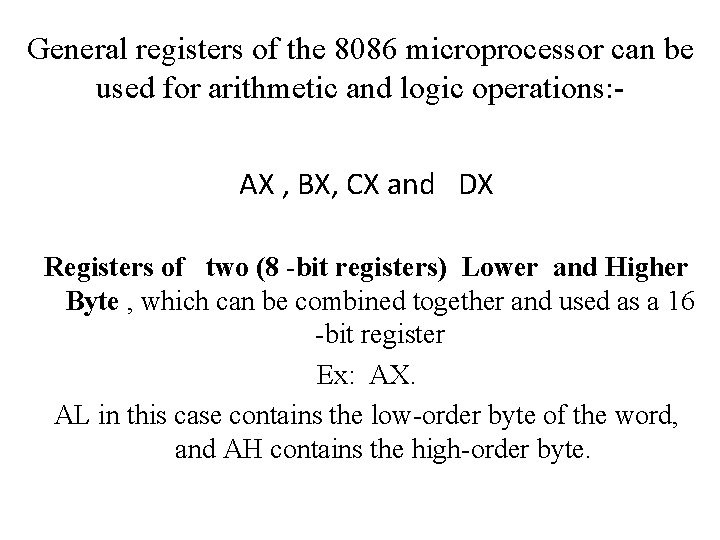

General registers of the 8086 microprocessor can be used for arithmetic and logic operations: AX , BX, CX and DX Registers of two (8 -bit registers) Lower and Higher Byte , which can be combined together and used as a 16 -bit register Ex: AX. AL in this case contains the low-order byte of the word, and AH contains the high-order byte.

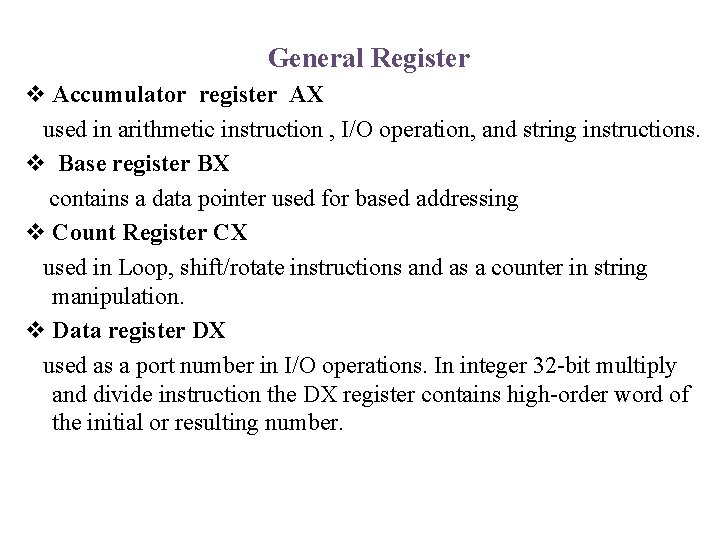

General Register v Accumulator register AX used in arithmetic instruction , I/O operation, and string instructions. v Base register BX contains a data pointer used for based addressing v Count Register CX used in Loop, shift/rotate instructions and as a counter in string manipulation. v Data register DX used as a port number in I/O operations. In integer 32 -bit multiply and divide instruction the DX register contains high-order word of the initial or resulting number.

Pointer Registers both general and index registers: • Stack Pointer (SP) pointing to program stack. • Base Pointer (BP) pointing to data in stack segment BP register is usually used as based address. • Instruction Pointer (IP) Address next instruction in the code segment.

Index Registers • Source Index (SI) used for indexed, based indexed and register indirect addressing, as well as a source data address in string manipulation instructions. • Destination Index (DI) used for indexed, based indexed and register indirect addressing, as well as a destination data address in string manipulation instructions.

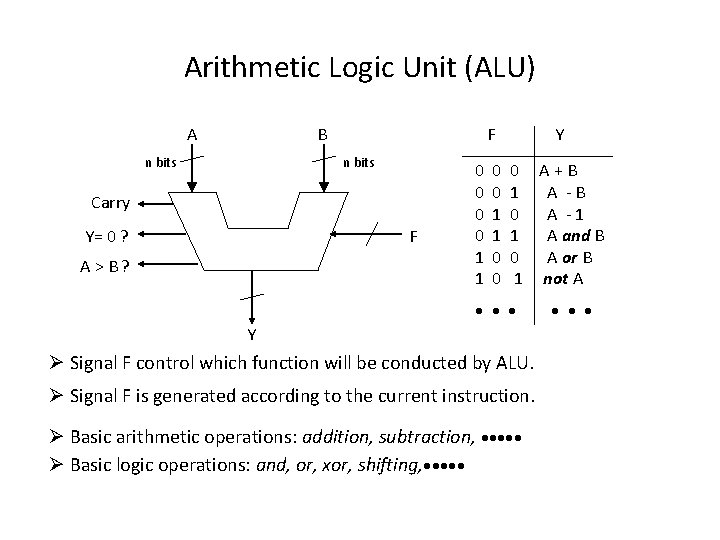

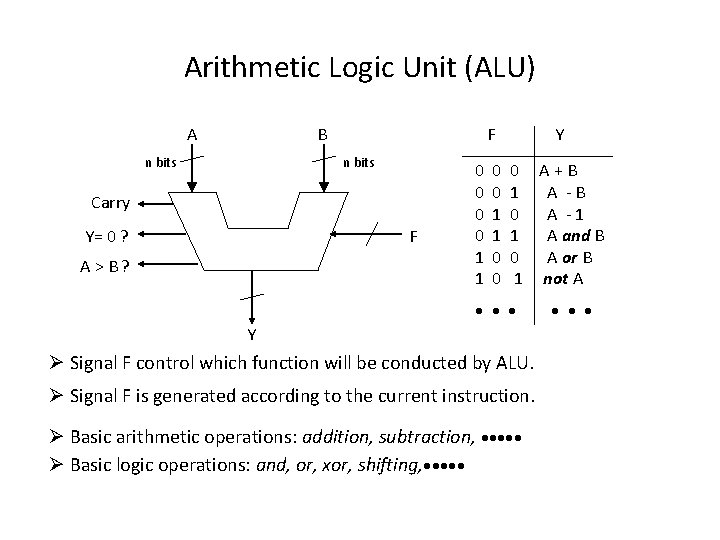

Arithmetic Logic Unit (ALU) A B n bits F n bits Carry Y= 0 ? F A>B? 0 0 1 1 0 0 Y 0 A+B 1 A -B 0 A -1 1 A and B 0 A or B 1 not A Y Ø Signal F control which function will be conducted by ALU. Ø Signal F is generated according to the current instruction. Ø Basic arithmetic operations: addition, subtraction, Ø Basic logic operations: and, or, xor, shifting,

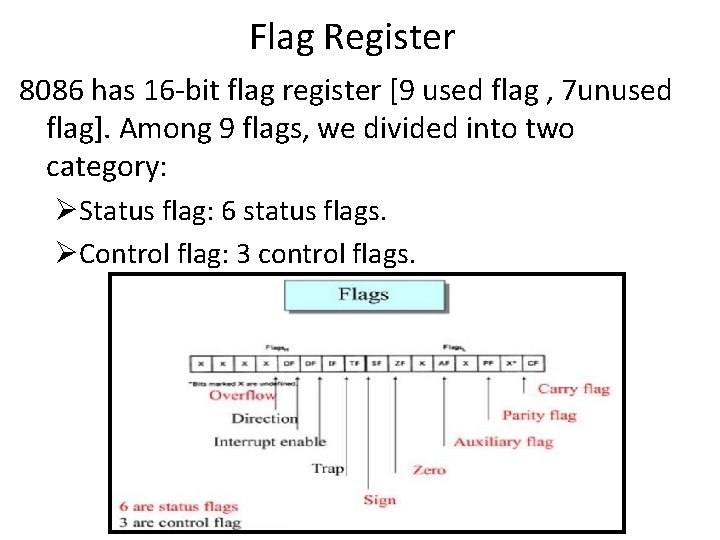

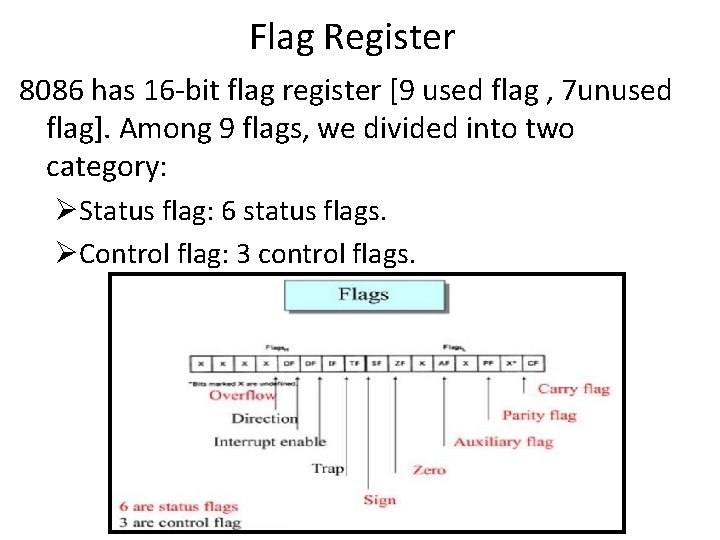

Flag Register 8086 has 16 -bit flag register [9 used flag , 7 unused flag]. Among 9 flags, we divided into two category: ØStatus flag: 6 status flags. ØControl flag: 3 control flags.

Flag Register • Carry Flag (CF) - set if there was a carry from or borrow to the most significant bit during last result calculation. • Parity Flag (PF) - set if parity (the number of "1" bits) in the low-order byte of the result is even. • Auxiliary carry Flag (AF) - set if there was a carry from or borrow to bits 0 -3 in the AL register. • Zero Flag (ZF) - set if the result is zero. • Sign Flag (SF) - set if the most significant bit of the result is set. • Single-step Flag (TF) – enable trapping through debugging feature. • Interrupt-enable Flag (IF) - setting this bit enables Mask able interrupts.

Timing and controlling unit • Keeps all the part of system ( Reg, ALU, memory and IO) working together in right time. • The CU of EU direct all internal operations and also responsible of generation of control signal.