Universitt Rostock Fakultt fr Informatik und Elektrotechnik Institut

- Slides: 28

Universität Rostock Fakultät für Informatik und Elektrotechnik Institut für Angewandte Mikroelektronik und Datentechnik Untersuchung und Reduzierung des Leckstroms integrierter Schaltungen in Nanometer-Technologien bei konstanten Performanceanforderungen Verteidigung der Dissertation zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr. -Ing. ) der Fakultät für Informatik und Elektrotechnik der Universität Rostock Dipl. -Ing. Frank Sill Rostock, den 5. Dezember 2007 1

Übersicht § Motivation – Leckströme in Nanometer-Technologien § Grundlagen – Leckstromarten – Bekannte Ansätze zur Reduzierung des Leckstroms § Der „Mixed Gates“-Ansatz – Grundidee – Anforderungen an den neuen Ansatz – Resultate § Zusammenfassung und Ausblick Frank Sill 2

Motivation Problem: Energieverbrauch § Kontinuierlich steigende Leistungsanforderungen § Steigender Energieverbrauch technischer Geräte § Heute: Energieverbrauch ist ein Hauptproblem § Großer Energieverbrauch führt zu: L Reduzierte Betriebsdauer L Hoher Kühlungsaufwand L Höheres Gewicht (Akkus) L Steigende Betriebskosten L Geringere Mobilität L Geringere Ausfallsicherheit Frank Sill 3

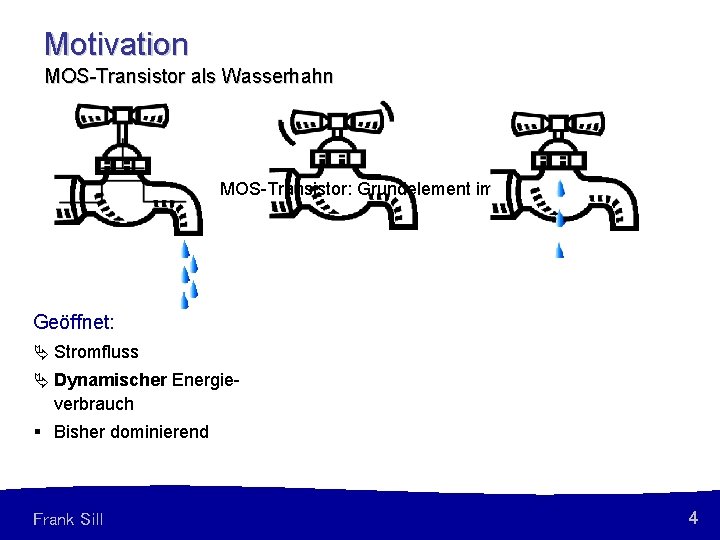

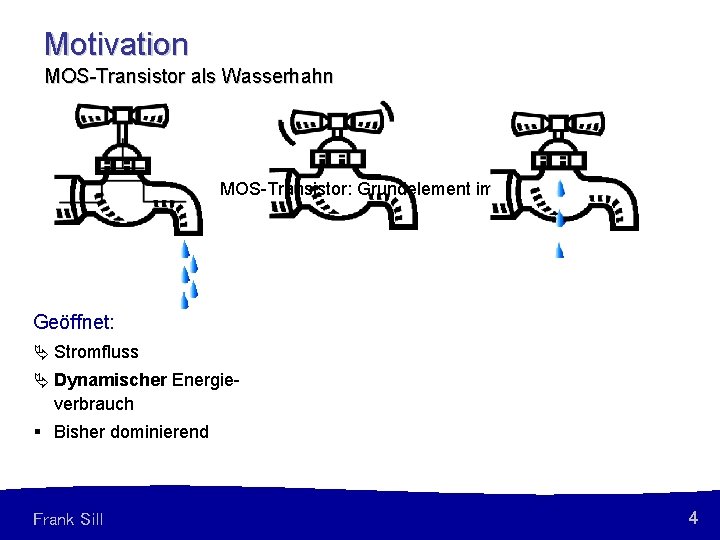

Motivation MOS-Transistor als Wasserhahn MOS-Transistor: Grundelement im Chipdesign Geöffnet: Gesperrt (ideal): Gesperrt (real): Stromfluss Kein Stromfluss Trotzdem Stromfluss Dynamischer Energie- Kein Energieverbrauch § Bisher dominierend Frank Sill (Leckströme) Energieverbrauch 4

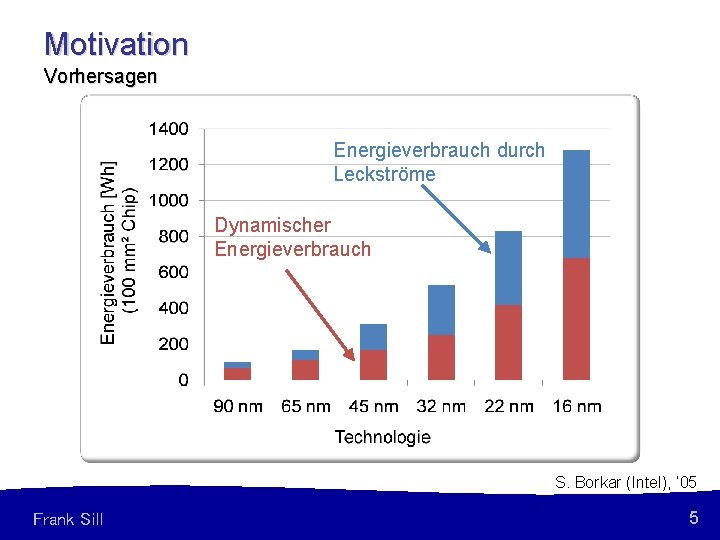

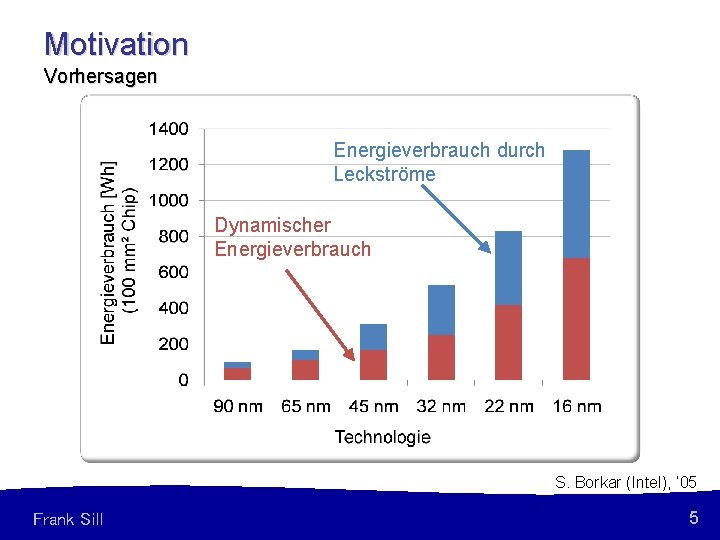

Motivation Vorhersagen Energieverbrauch durch Leckströme Dynamischer Energieverbrauch S. Borkar (Intel), ‘ 05 Frank Sill 5

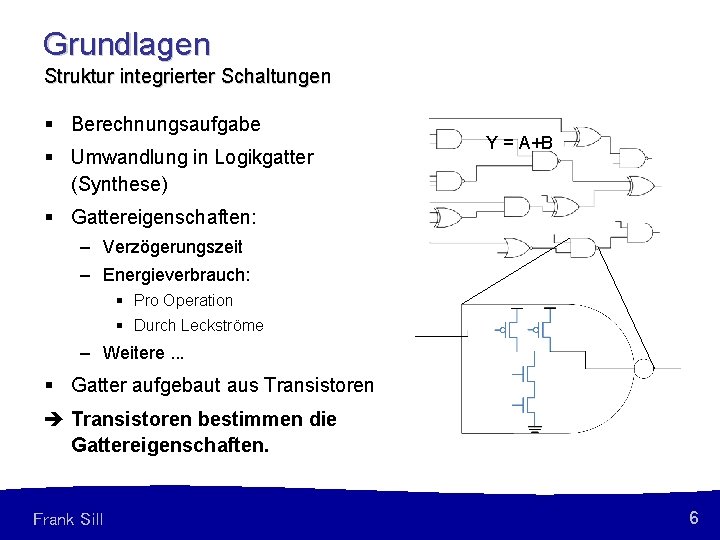

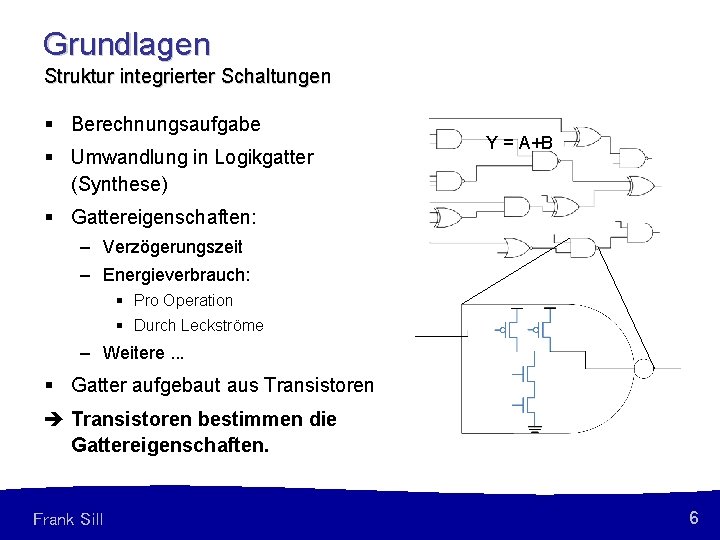

Grundlagen Struktur integrierter Schaltungen § Berechnungsaufgabe § Umwandlung in Logikgatter (Synthese) Y = A+B § Gattereigenschaften: – Verzögerungszeit – Energieverbrauch: § Pro Operation § Durch Leckströme – Weitere. . . § Gatter aufgebaut aus Transistoren è Transistoren bestimmen die Gattereigenschaften. Frank Sill 6

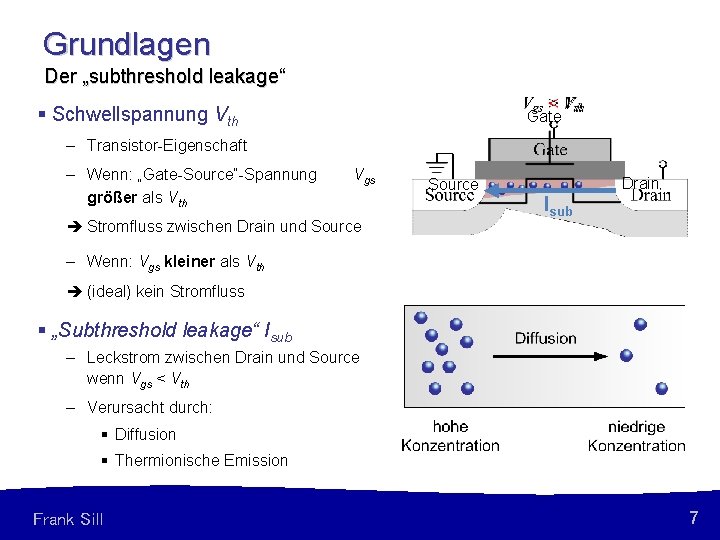

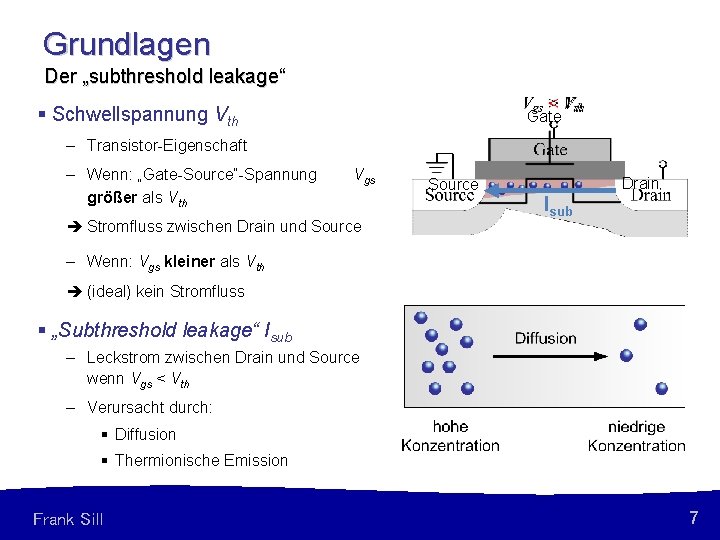

Grundlagen Der „subthreshold leakage“ § Schwellspannung Vth Gate – Transistor-Eigenschaft – Wenn: „Gate-Source“-Spannung größer als Vth Vgs è Stromfluss zwischen Drain und Source Drain Isub – Wenn: Vgs kleiner als Vth è (ideal) kein Stromfluss § „Subthreshold leakage“ Isub – Leckstrom zwischen Drain und Source wenn Vgs < Vth – Verursacht durch: § Diffusion § Thermionische Emission Frank Sill 7

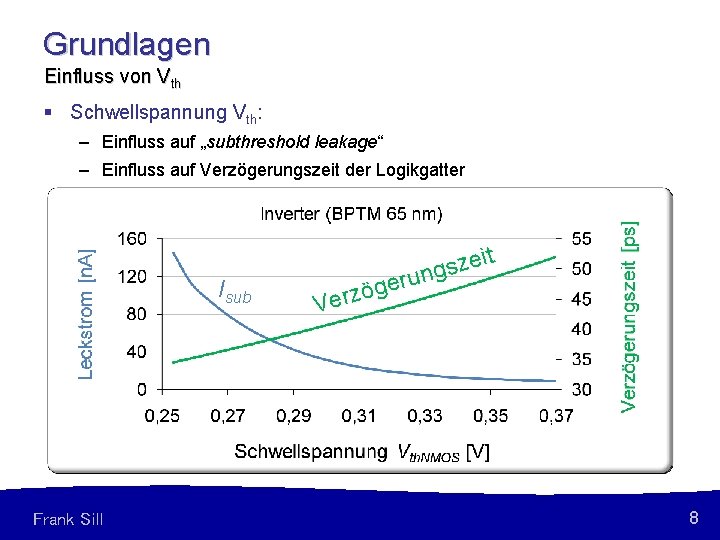

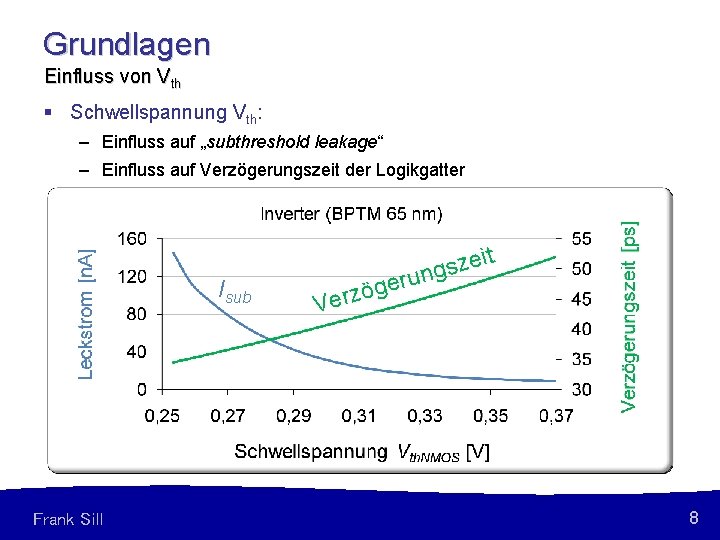

Grundlagen Einfluss von Vth § Schwellspannung Vth: – Einfluss auf „subthreshold leakage“ – Einfluss auf Verzögerungszeit der Logikgatter Isub Frank Sill it e z s rung e ög z r e V 8

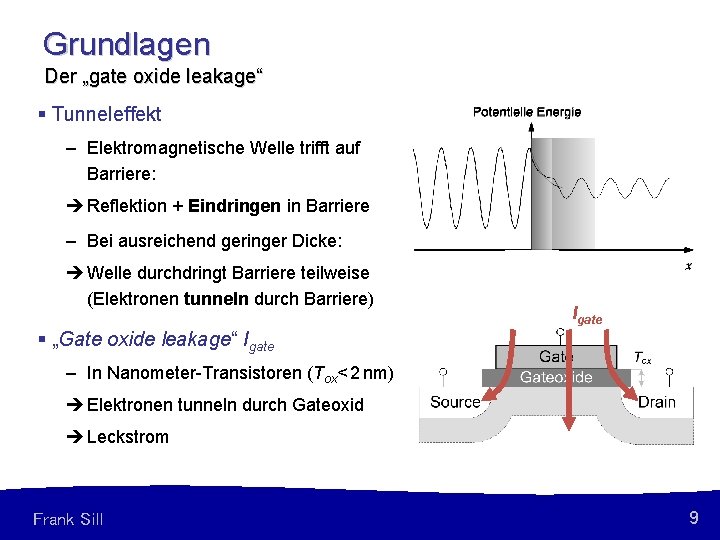

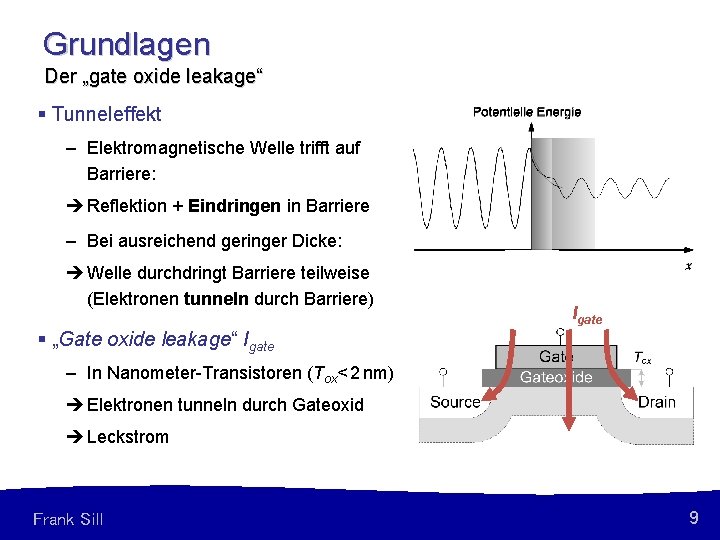

Grundlagen Der „gate oxide leakage“ § Tunneleffekt – Elektromagnetische Welle trifft auf Barriere: è Reflektion + Eindringen in Barriere – Bei ausreichend geringer Dicke: è Welle durchdringt Barriere teilweise (Elektronen tunneln durch Barriere) Igate § „Gate oxide leakage“ Igate – In Nanometer-Transistoren (Tox< 2 nm) è Elektronen tunneln durch Gateoxid è Leckstrom Frank Sill 9

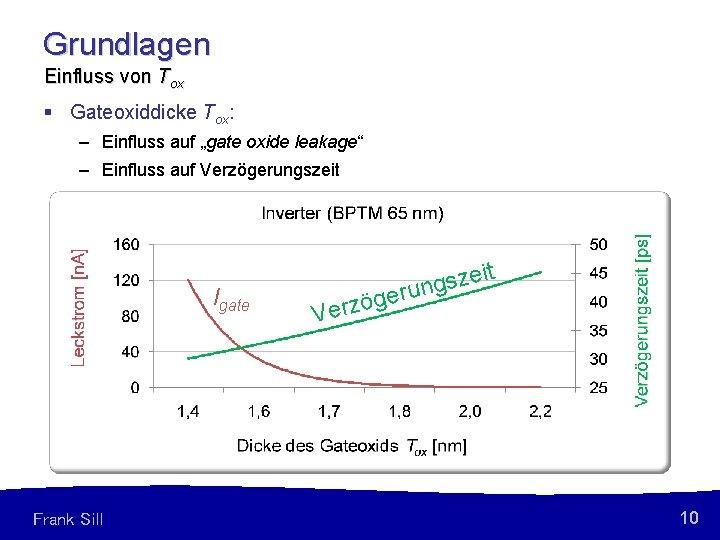

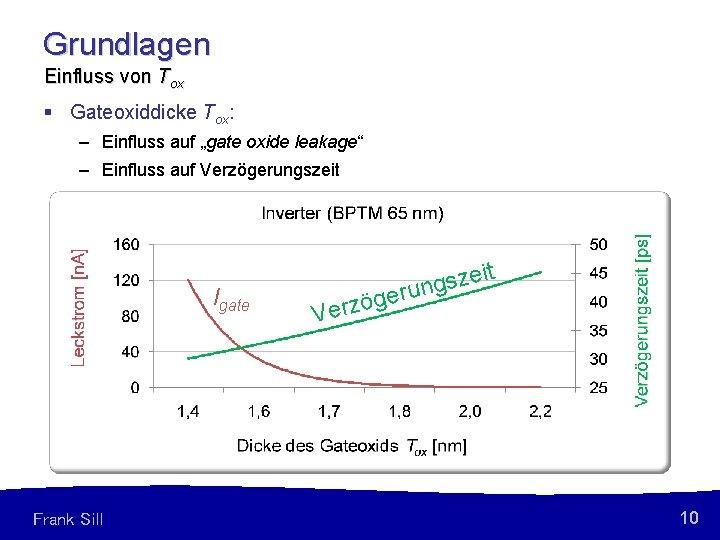

Grundlagen Einfluss von Tox § Gateoxiddicke Tox: – Einfluss auf „gate oxide leakage“ – Einfluss auf Verzögerungszeit Igate Frank Sill it e z s rung ge ö z r e V 10

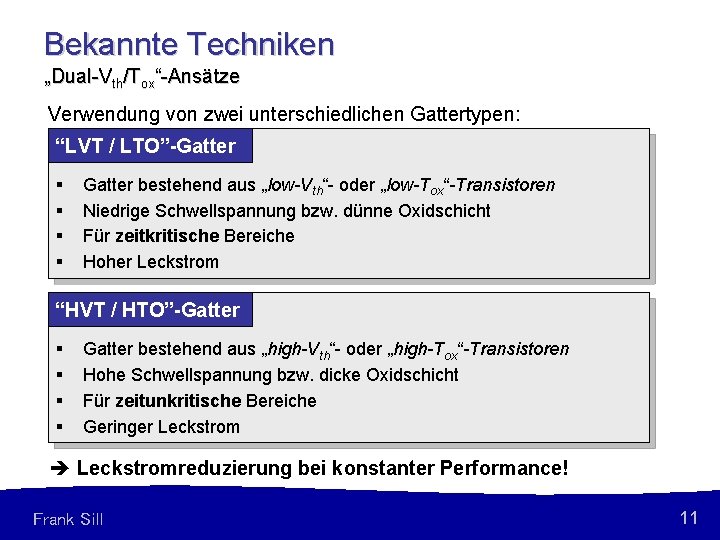

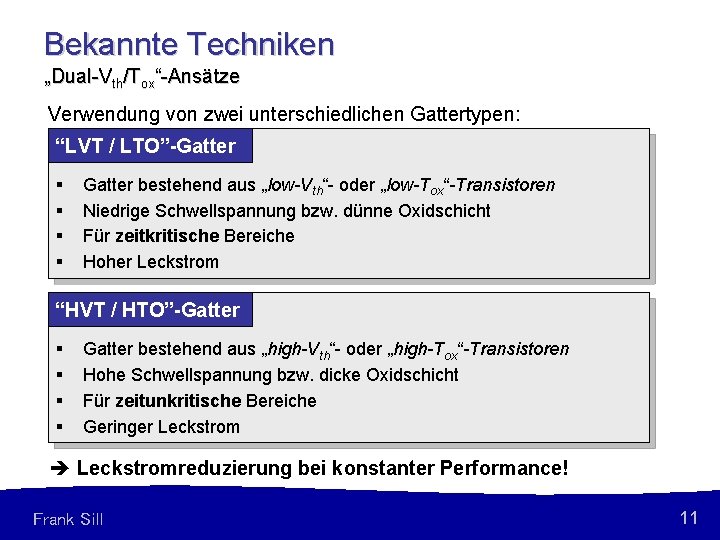

Bekannte Techniken „Dual-Vth/Tox“-Ansätze Verwendung von zwei unterschiedlichen Gattertypen: “LVT / LTO”-Gatter § § Gatter bestehend aus „low-Vth“- oder „low-Tox“-Transistoren Niedrige Schwellspannung bzw. dünne Oxidschicht Für zeitkritische Bereiche Hoher Leckstrom “HVT / HTO”-Gatter § § Gatter bestehend aus „high-Vth“- oder „high-Tox“-Transistoren Hohe Schwellspannung bzw. dicke Oxidschicht Für zeitunkritische Bereiche Geringer Leckstrom è Leckstromreduzierung bei konstanter Performance! Frank Sill 11

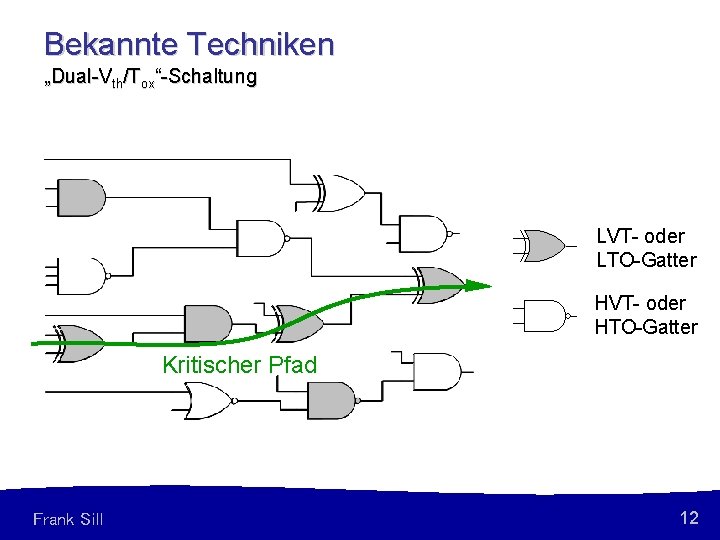

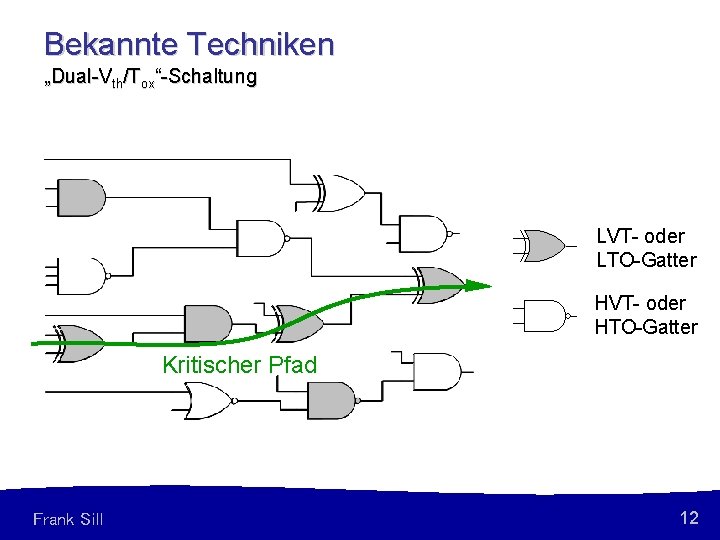

Bekannte Techniken „Dual-Vth/Tox“-Schaltung LVT- oder LTO-Gatter HVT- oder HTO-Gatter Kritischer Pfad Frank Sill 12

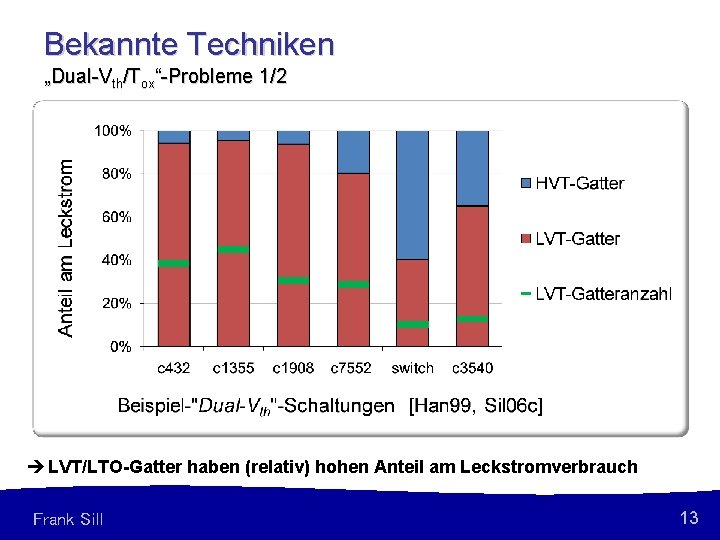

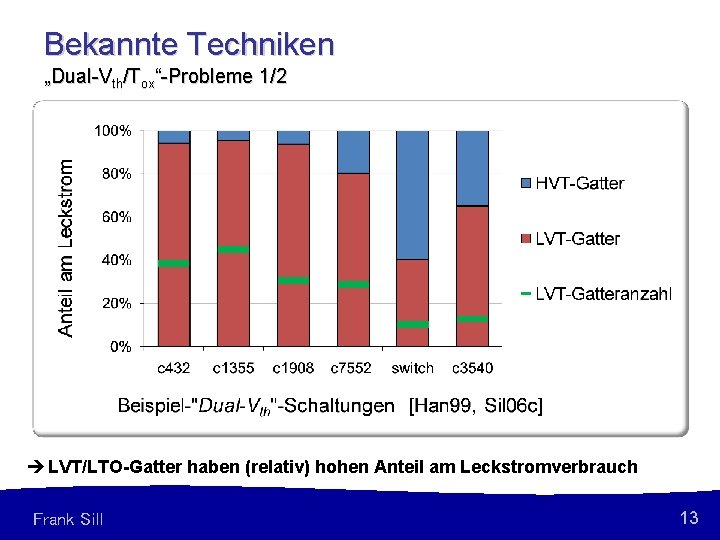

Bekannte Techniken „Dual-Vth/Tox“-Probleme 1/2 è LVT/LTO-Gatter haben (relativ) hohen Anteil am Leckstromverbrauch Frank Sill 13

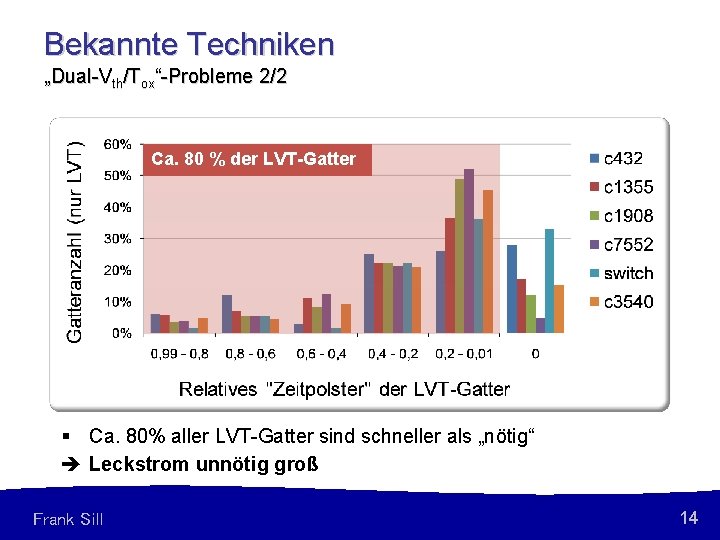

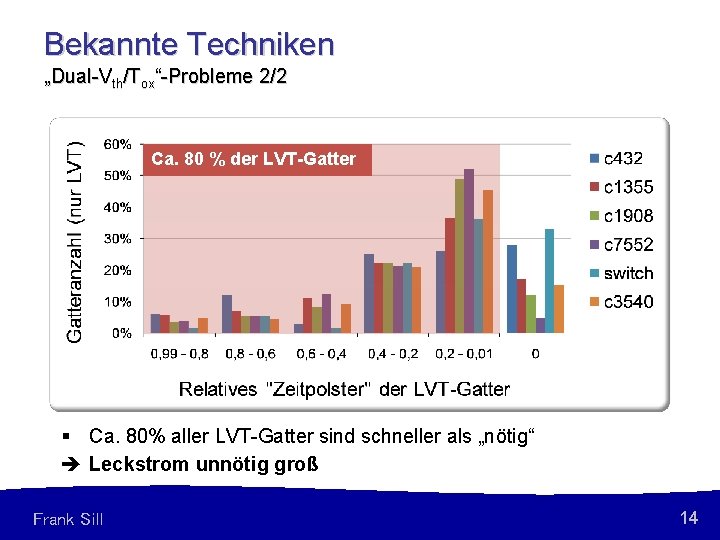

Bekannte Techniken „Dual-Vth/Tox“-Probleme 2/2 Ca. 80 % der LVT-Gatter § Ca. 80% aller LVT-Gatter sind schneller als „nötig“ è Leckstrom unnötig groß Frank Sill 14

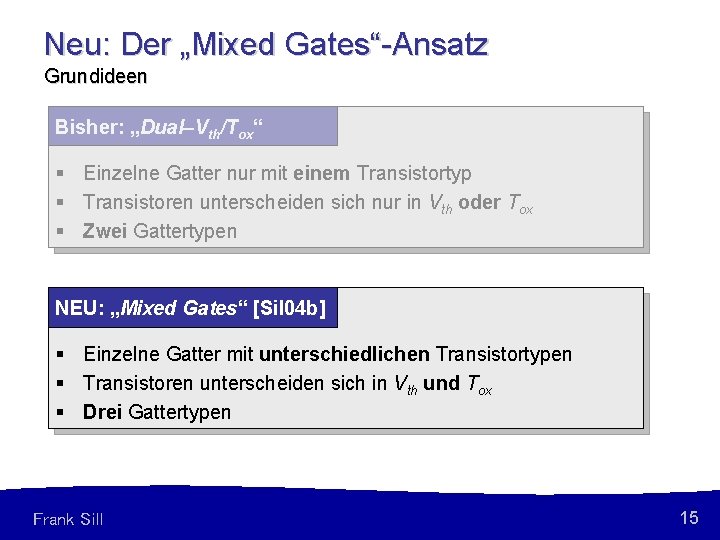

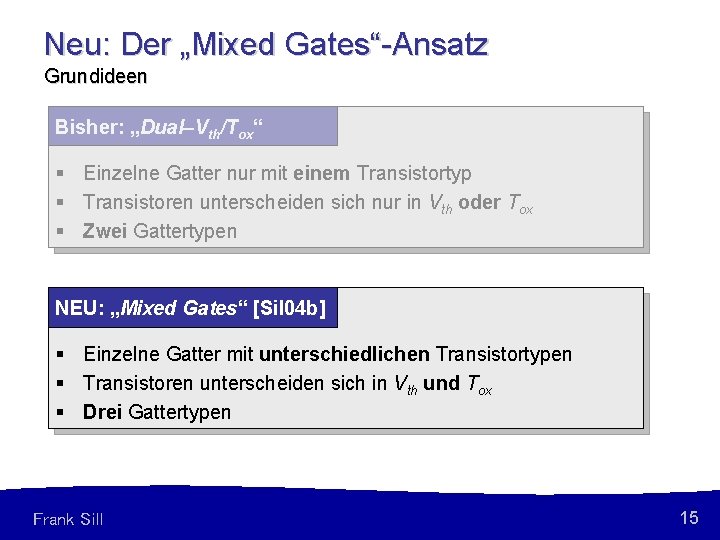

Neu: Der „Mixed Gates“-Ansatz Grundideen Bisher: „Dual–Vth/Tox“ § Einzelne Gatter nur mit einem Transistortyp § Transistoren unterscheiden sich nur in Vth oder Tox § Zwei Gattertypen NEU: „Mixed Gates“ [Sil 04 b] § Einzelne Gatter mit unterschiedlichen Transistortypen § Transistoren unterscheiden sich in Vth und Tox § Drei Gattertypen Frank Sill 15

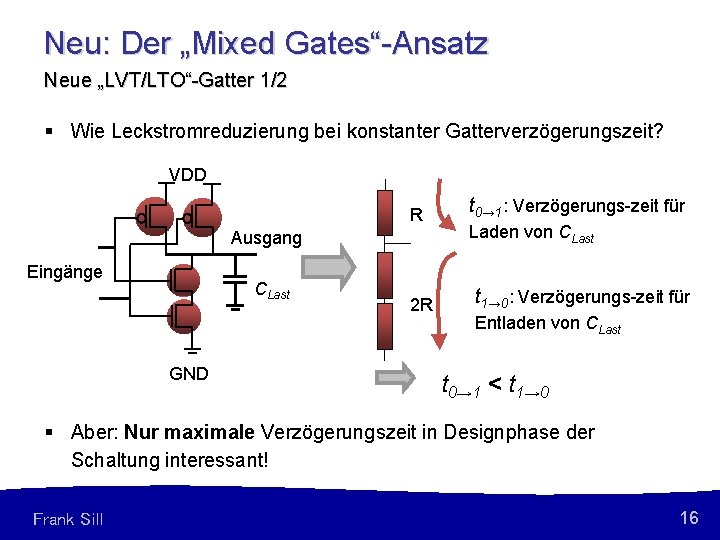

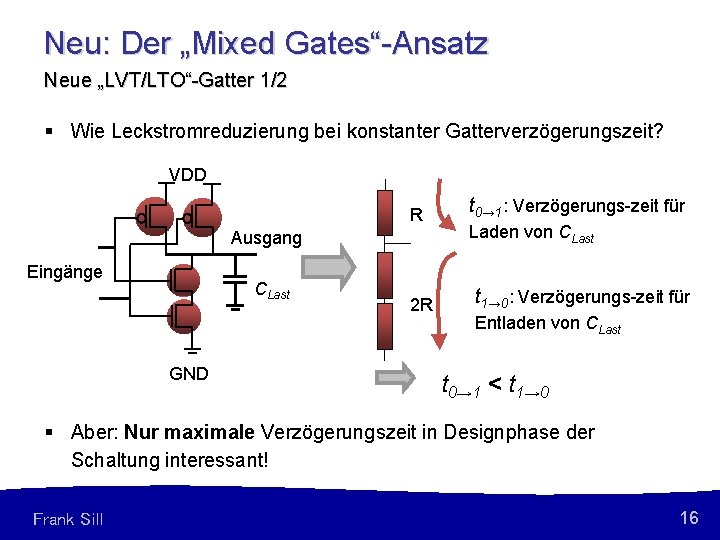

Neu: Der „Mixed Gates“-Ansatz Neue „LVT/LTO“-Gatter 1/2 § Wie Leckstromreduzierung bei konstanter Gatterverzögerungszeit? VDD R Ausgang Eingänge CLast GND 2 R t 0→ 1: Verzögerungs-zeit für Laden von CLast t 1→ 0: Verzögerungs-zeit für Entladen von CLast t 0→ 1 < t 1→ 0 § Aber: Nur maximale Verzögerungszeit in Designphase der Schaltung interessant! Frank Sill 16

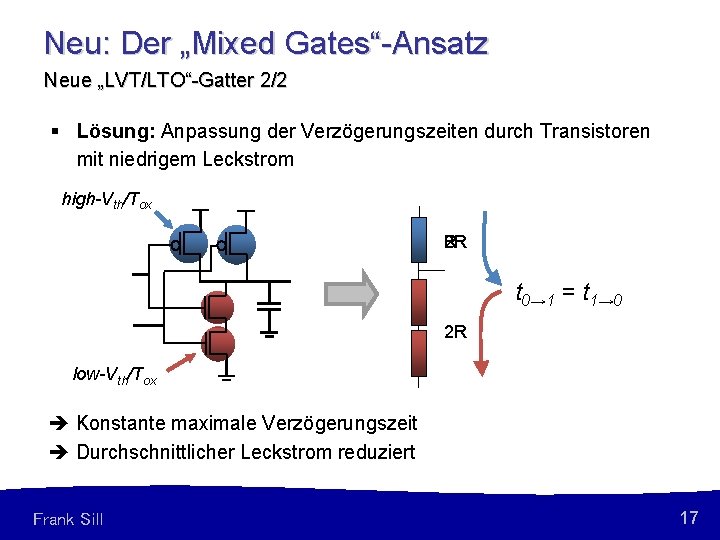

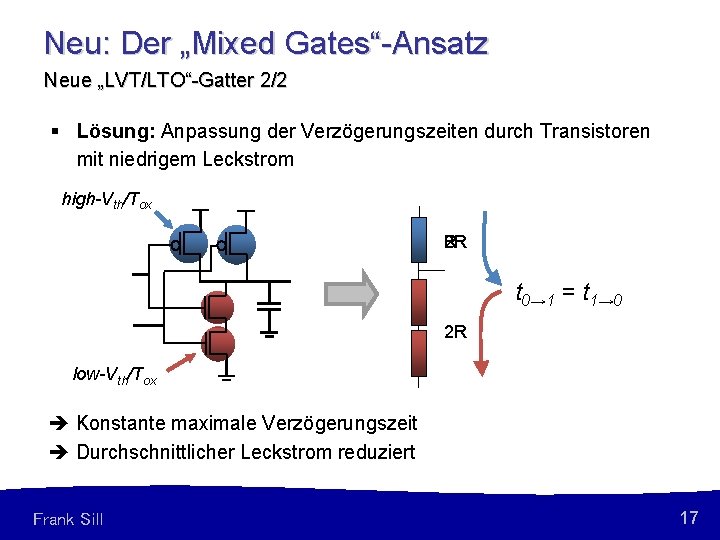

Neu: Der „Mixed Gates“-Ansatz Neue „LVT/LTO“-Gatter 2/2 § Lösung: Anpassung der Verzögerungszeiten durch Transistoren mit niedrigem Leckstrom high-Vth/Tox R 2 R t 0→ 1 = t 1→ 0 2 R low-Vth/Tox è Konstante maximale Verzögerungszeit è Durchschnittlicher Leckstrom reduziert Frank Sill 17

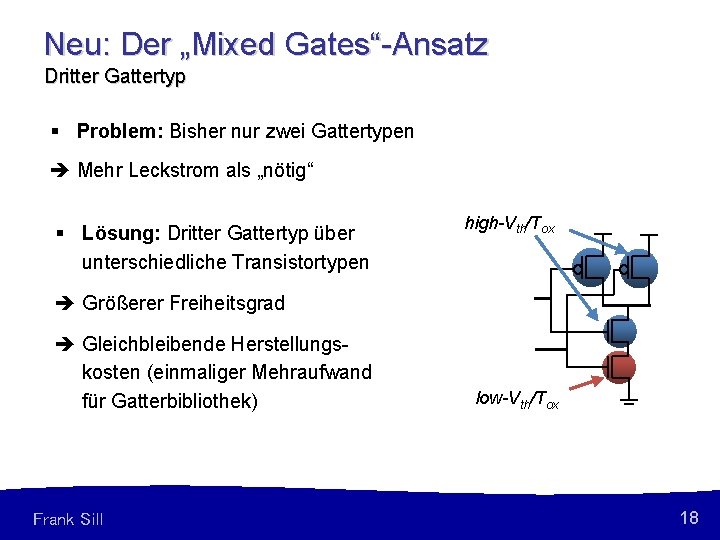

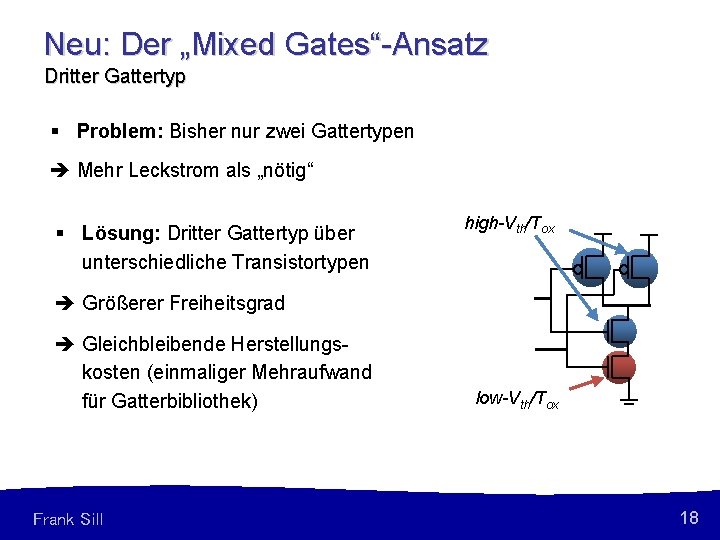

Neu: Der „Mixed Gates“-Ansatz Dritter Gattertyp § Problem: Bisher nur zwei Gattertypen è Mehr Leckstrom als „nötig“ § Lösung: Dritter Gattertyp über unterschiedliche Transistortypen high-Vth/Tox è Größerer Freiheitsgrad è Gleichbleibende Herstellungskosten (einmaliger Mehraufwand für Gatterbibliothek) Frank Sill low-Vth/Tox 18

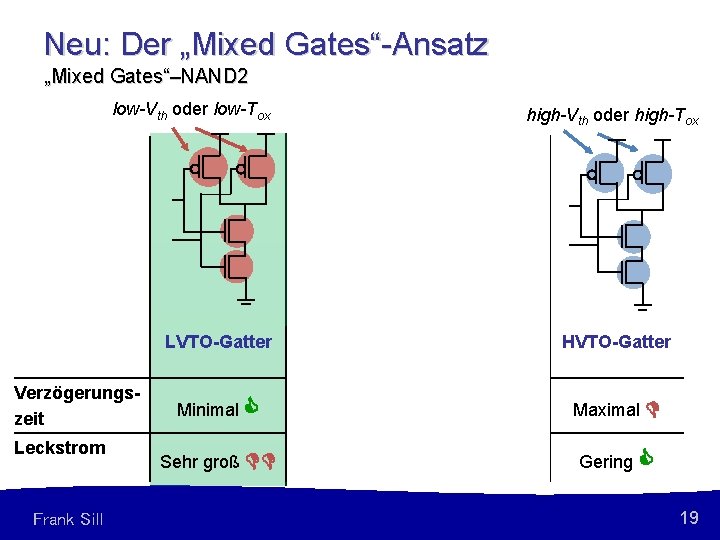

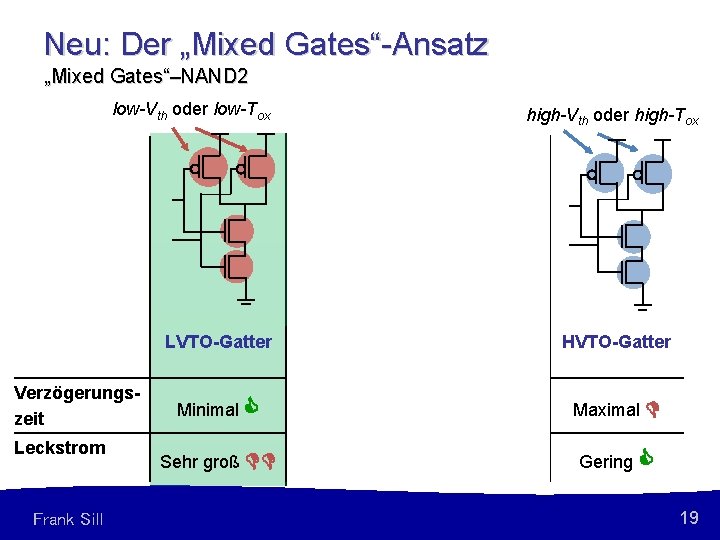

Neu: Der „Mixed Gates“-Ansatz „Mixed Gates“–NAND 2 low-V th oder th/Tlow-T ox ox Verzögerungszeit Leckstrom Frank Sill high-Vththoder /Tox high-Tox LVTO-Gatter F-MG-Gatter HVTO-Gatter Minimal Mittel Maximal Sehr groß Groß Mittel Gering 19

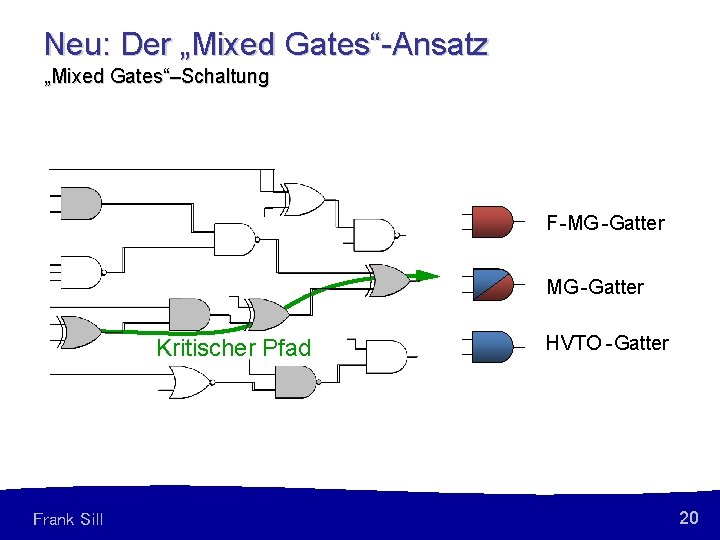

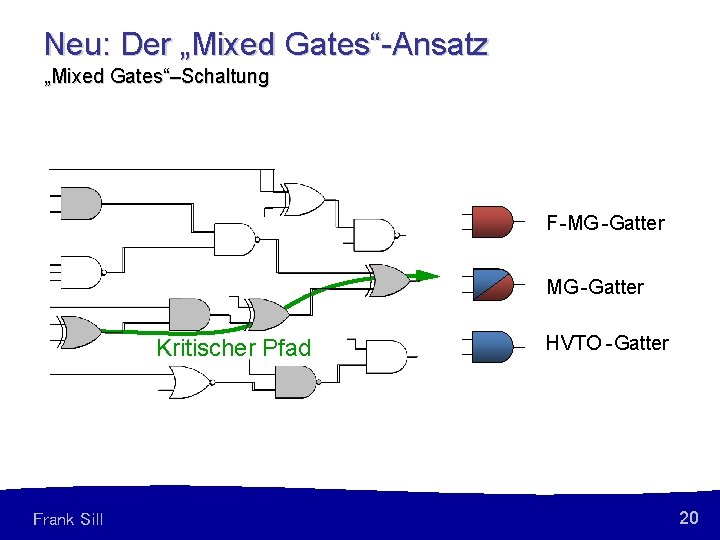

Neu: Der „Mixed Gates“-Ansatz „Mixed Gates“–Schaltung F-MG -Gatter Kritischer Pfad Frank Sill HVTO -Gatter 20

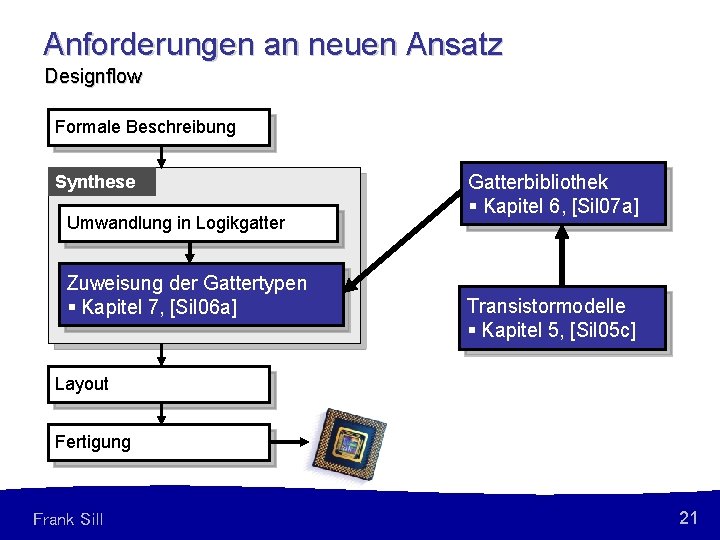

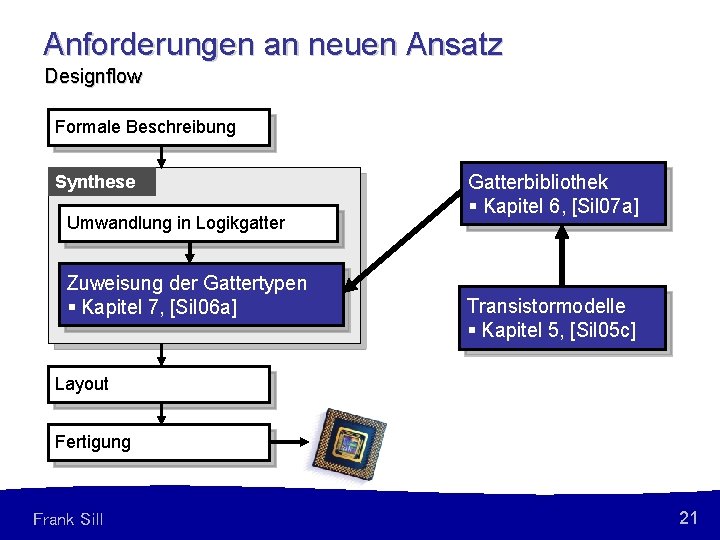

Anforderungen an neuen Ansatz Designflow Formale Beschreibung Synthese Umwandlung in Logikgatter Zuweisung der Gattertypen § Kapitel 7, [Sil 06 a] Gatterbibliothek § Kapitel 6, [Sil 07 a] Transistormodelle § Kapitel 5, [Sil 05 c] Layout Fertigung Frank Sill 21

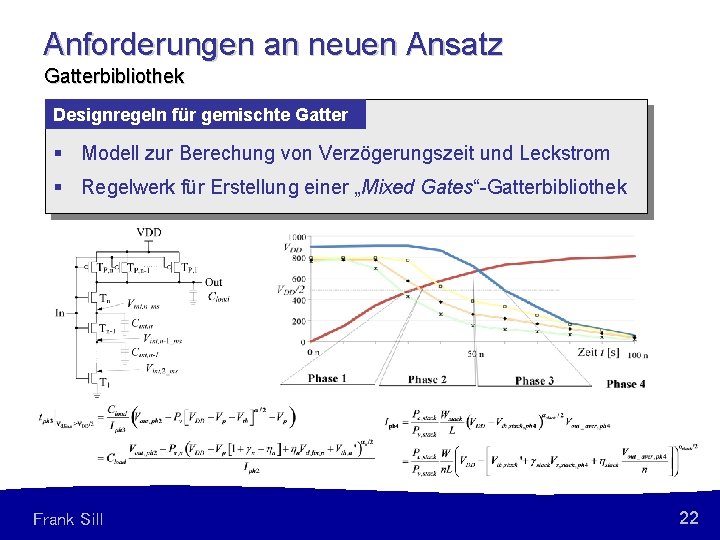

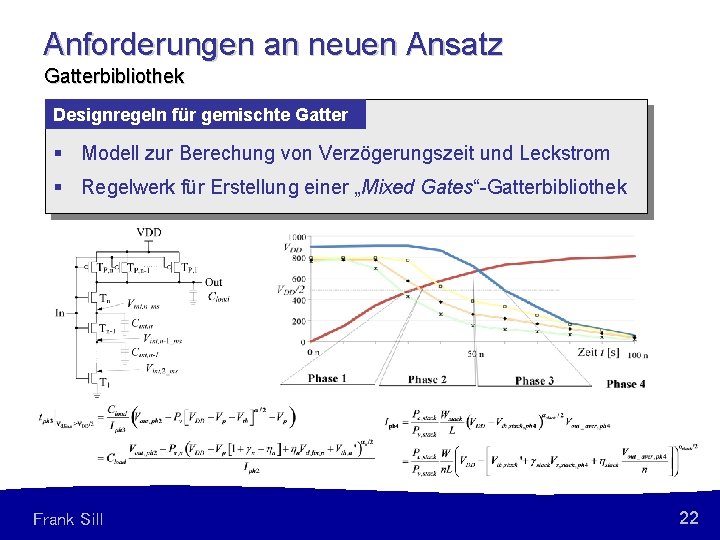

Anforderungen an neuen Ansatz Gatterbibliothek Designregeln für gemischte Gatter § Modell zur Berechung von Verzögerungszeit und Leckstrom § Regelwerk für Erstellung einer „Mixed Gates“-Gatterbibliothek Frank Sill 22

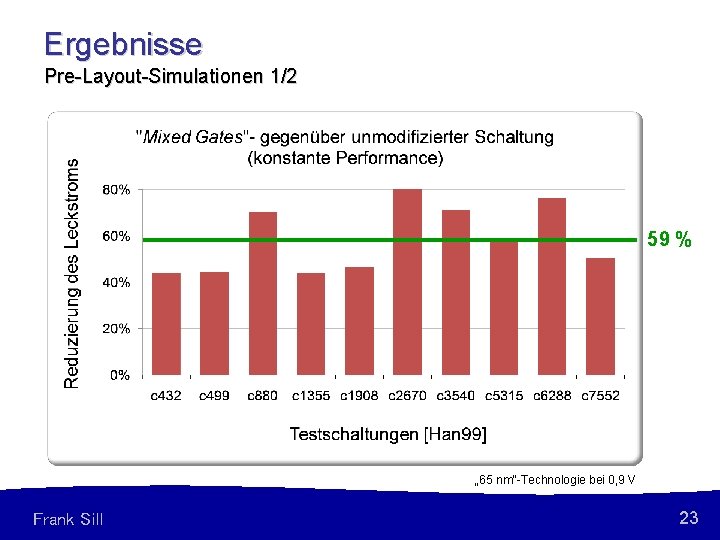

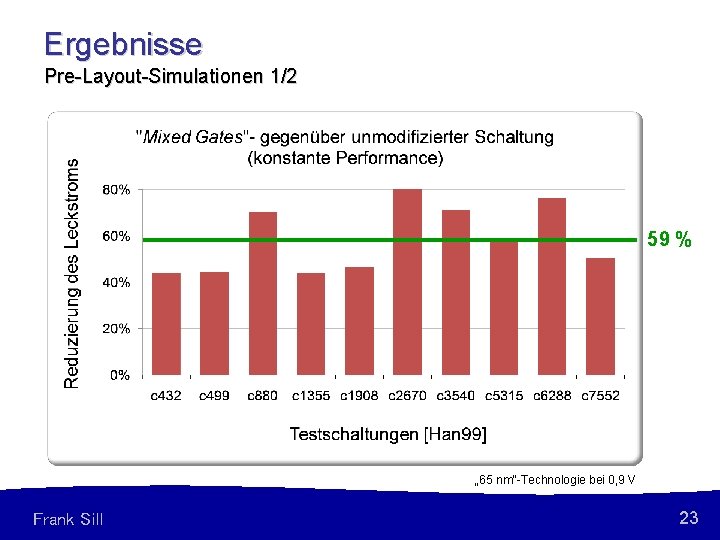

Ergebnisse Pre-Layout-Simulationen 1/2 59 % „ 65 nm“-Technologie bei 0, 9 V Frank Sill 23

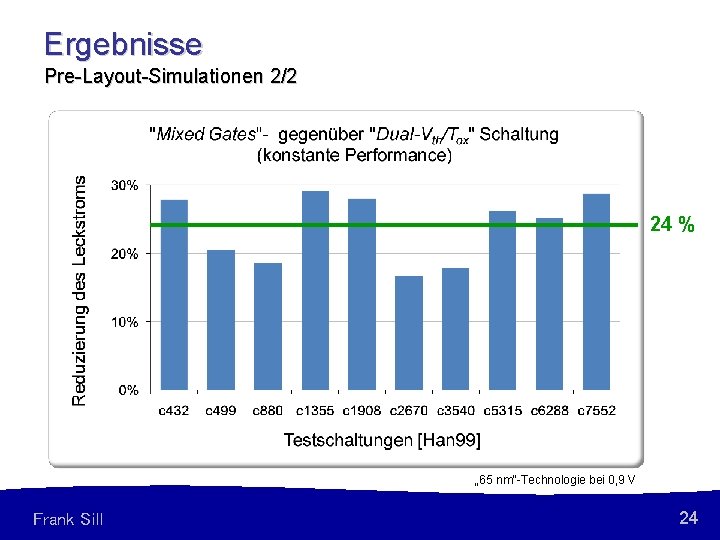

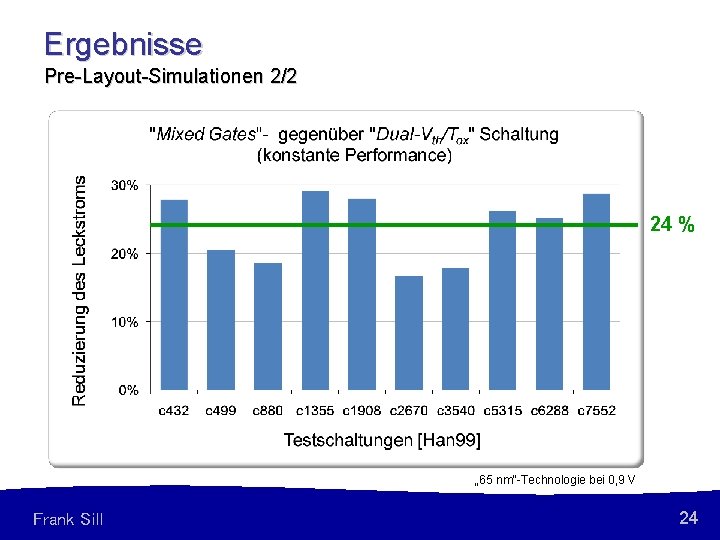

Ergebnisse Pre-Layout-Simulationen 2/2 24 % „ 65 nm“-Technologie bei 0, 9 V Frank Sill 24

Zusammenfassung “Mixed Gates”-Ansatz § Unterschiedliche Transistortypen innerhalb der Gatter § Drei verschiedene Gattertypen § Reduzierung der zwei größten Leckstromkomponenten § Leckstromreduzierung bei konstanter Performance: – Bis zu Faktor 5 (unmodifizierte Schaltungen) – Durchschnittlich 24 % („Dual-Vth/Tox“-Schaltungen) § Vereint Vorteile von Ansätzen auf Transistor- und Gatterebene Frank Sill 25

Zusammenfassung Weitere Ergebnisse § Umfassende Einführung in Leckstromproblematik § Betrachtungen im Gesamtkontext des neuen Ansatzes in aktuellen Nanometer-Technologien – Analyse der Technologie-Parameter – Regelwerk zur Generierung einer Gatterbibliothek – Erweiterter Algorithmus zur Zuweisung der Gattertypen § Analysen zur Anwendbarkeit von Evolutionsstrategien § Untersuchungen zu Grenzen der Leckstromreduzierung bei konstanter Performance Frank Sill 26

Ausblick § Analyse des Einflusses neuer Technologien (bspw. „high-k“Materialien, „metal gates“, …) § Kombination mit weiteren Techniken (bspw. „Dual-VDD“, „sleep transistor“, … ) § Untersuchung des Einflusses von Parametervariationen § „Mixed Gates“-Layout in kommerzieller Technologie Frank Sill 27

Universität Rostock Fakultät für Informatik und Elektrotechnik Institut für Angewandte Mikroelektronik und Datentechnik Untersuchung und Reduzierung des Leckstroms integrierter Schaltungen in Nanometer-Technologien bei konstanten Performanceanforderungen Verteidigung der Dissertation zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr. -Ing. ) der Fakultät für Informatik und Elektrotechnik der Universität Rostock Dipl. -Ing. Frank Sill Rostock, den 5. Dezember 2007 28