Universitatea Politehnica Bucureti Facultatea de Automatic i Calculatoare

Universitatea Politehnica Bucureşti, Facultatea de Automatică şi Calculatoare Sisteme cu Microprocesoare Laborator 4 Microprocesorul Intel 80386 Laborant ing. Mihai Matei

Cuprins Evoluție 8086 -80386 Microarhitectura 80386 Registre, moduri de funcționare, set de instrucțiuni Boot IA 32 Arhitectura IA 32 a sistemelor de operare Descriptori de gate-uri

Evoluție 8086 - 80386 8086 – magistrale 16 biți (date + regiștrii), adrese de 20 – maxim 1 MB folosind segementare 80386 – octombrie 1985 – septembrie 2007 (RIP - Intel) 80386 – magistrale 32 biți (adrese + date + regiștrii) – maxim 4 GB, deși se păstrează mecanismul de segementare 80386 - ALU îmbunătățit – 32 biți + instrucțiuni noi 80386 – set instrucțiuni IA 32 80386 – microprocresor cu suport pentru sisteme de operare - moduri real (maxim 1 MB, VGA bios), protected (toate resursele procesorului ) - MMU – sistem de paginare (suport mai bun pentru memorie virtuală), suport hardware pentru debug (breakpoints) Model memorie: flat vs segmentat vs real (legacy) Memoria paginată, segementată mecanism MMU NU model memorie

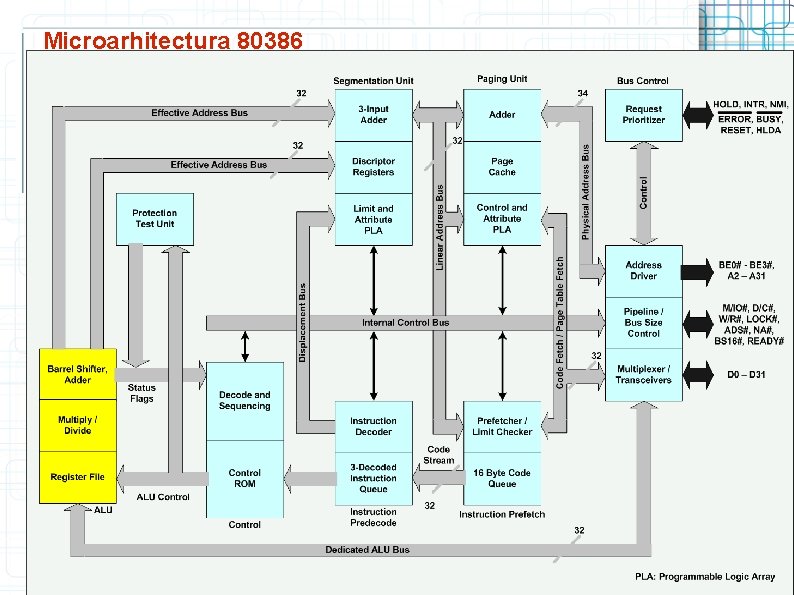

Microarhitectura 80386

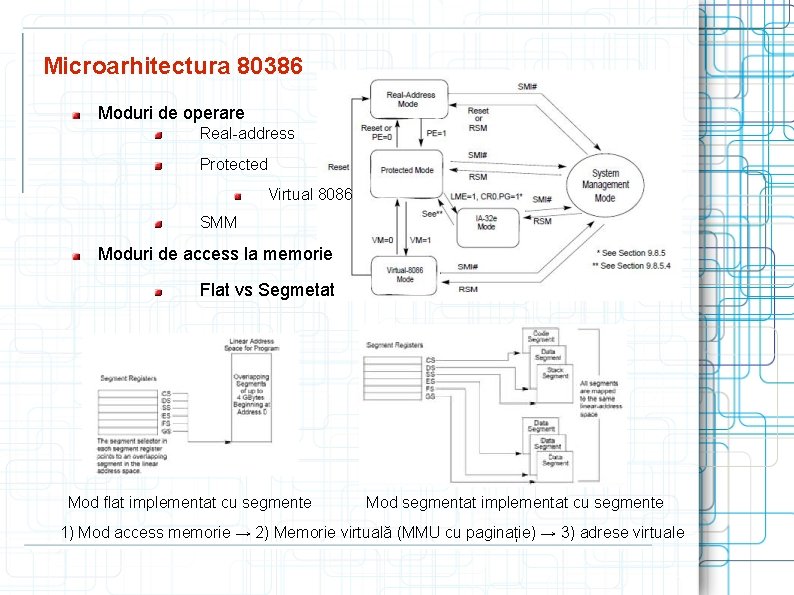

Microarhitectura 80386 Moduri de operare Real-address Protected Virtual 8086 SMM Moduri de access la memorie Flat vs Segmetat Mod flat implementat cu segmente Mod segmentat implementat cu segmente 1) Mod access memorie → 2) Memorie virtuală (MMU cu paginație) → 3) adrese virtuale

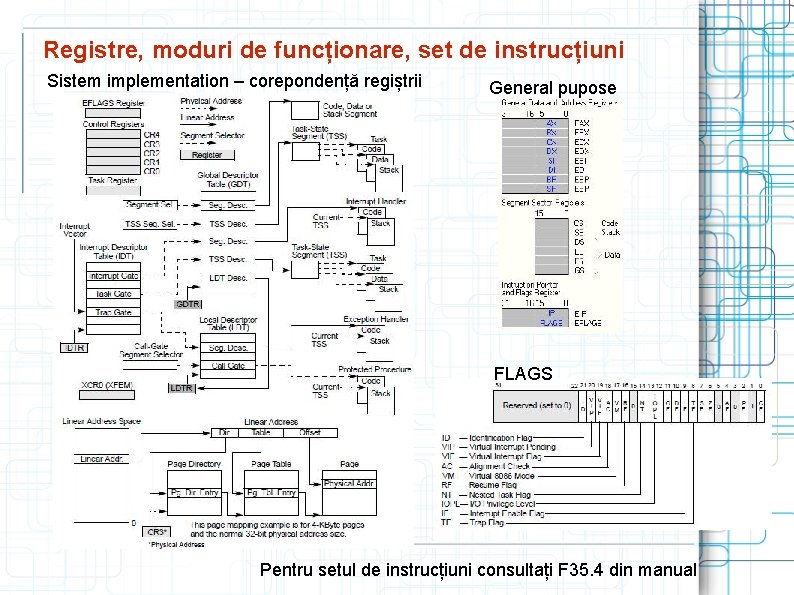

Registre, moduri de funcționare, set de instrucțiuni Sistem implementation – corepondență regiștrii General pupose FLAGS Pentru setul de instrucțiuni consultați F 35. 4 din manual

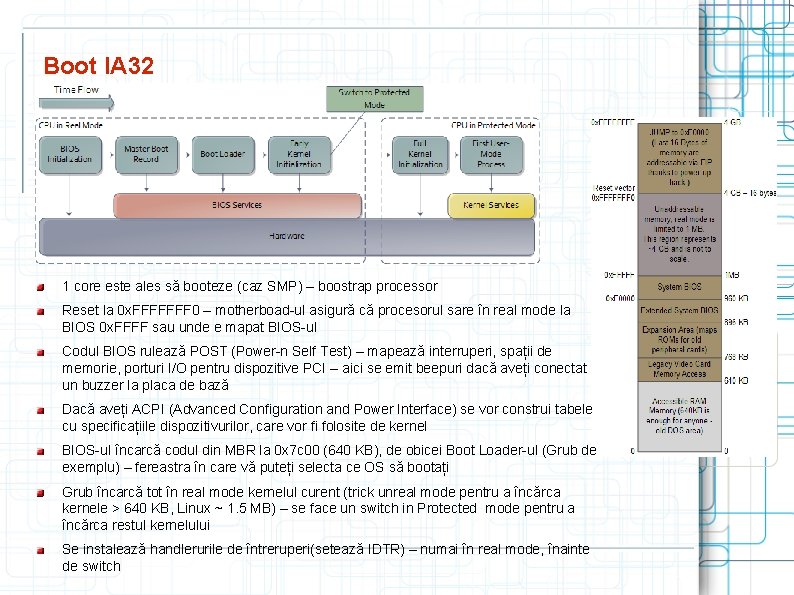

Boot IA 32 1 core este ales să booteze (caz SMP) – boostrap processor Reset la 0 x. FFFFFFF 0 – motherboad-ul asigură că procesorul sare în real mode la BIOS 0 x. FFFF sau unde e mapat BIOS-ul Codul BIOS rulează POST (Power-n Self Test) – mapează interruperi, spații de memorie, porturi I/O pentru dispozitive PCI – aici se emit beepuri dacă aveți conectat un buzzer la placa de bază Dacă aveți ACPI (Advanced Configuration and Power Interface) se vor construi tabele cu specificațiile dispozitivurilor, care vor fi folosite de kernel BIOS-ul încarcă codul din MBR la 0 x 7 c 00 (640 KB), de obicei Boot Loader-ul (Grub de exemplu) – fereastra în care vă puteți selecta ce OS să bootați Grub încarcă tot în real mode kernelul curent (trick unreal mode pentru a încărca kernele > 640 KB, Linux ~ 1. 5 MB) – se face un switch in Protected mode pentru a încărca restul kernelului Se instalează handlerurile de întreruperi(setează IDTR) – numai în real mode, înainte de switch

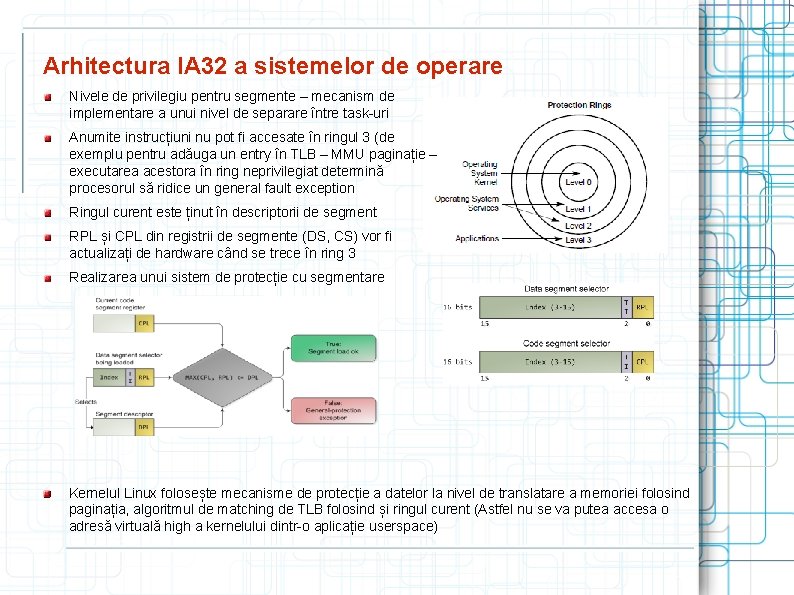

Arhitectura IA 32 a sistemelor de operare Nivele de privilegiu pentru segmente – mecanism de implementare a unui nivel de separare între task-uri Anumite instrucțiuni nu pot fi accesate în ringul 3 (de exemplu pentru adăuga un entry în TLB – MMU paginație – executarea acestora în ring neprivilegiat determină procesorul să ridice un general fault exception Ringul curent este ținut în descriptorii de segment RPL și CPL din registrii de segmente (DS, CS) vor fi actualizați de hardware când se trece în ring 3 Realizarea unui sistem de protecție cu segmentare Kernelul Linux folosește mecanisme de protecție a datelor la nivel de translatare a memoriei folosind paginația, algoritmul de matching de TLB folosind și ringul curent (Astfel nu se va putea accesa o adresă virtuală high a kernelului dintr-o aplicație userspace)

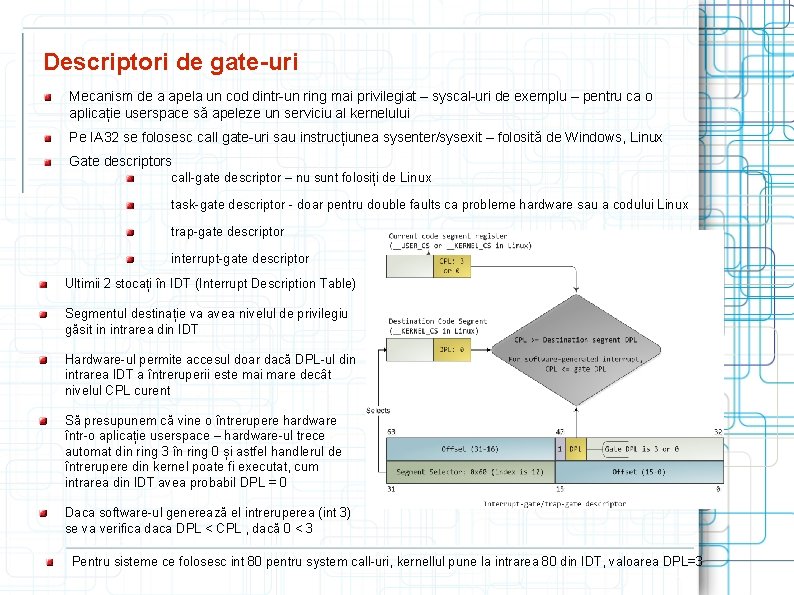

Descriptori de gate-uri Mecanism de a apela un cod dintr-un ring mai privilegiat – syscal-uri de exemplu – pentru ca o aplicație userspace să apeleze un serviciu al kernelului Pe IA 32 se folosesc call gate-uri sau instrucțiunea sysenter/sysexit – folosită de Windows, Linux Gate descriptors call-gate descriptor – nu sunt folosiți de Linux task-gate descriptor - doar pentru double faults ca probleme hardware sau a codului Linux trap-gate descriptor interrupt-gate descriptor Ultimii 2 stocați în IDT (Interrupt Description Table) Segmentul destinație va avea nivelul de privilegiu găsit in intrarea din IDT Hardware-ul permite accesul doar dacă DPL-ul din intrarea IDT a întreruperii este mai mare decât nivelul CPL curent Să presupunem că vine o întrerupere hardware într-o aplicație userspace – hardware-ul trece automat din ring 3 în ring 0 și astfel handlerul de întrerupere din kernel poate fi executat, cum intrarea din IDT avea probabil DPL = 0 Daca software-ul generează el intreruperea (int 3) se va verifica daca DPL < CPL , dacă 0 < 3 Pentru sisteme ce folosesc int 80 pentru system call-uri, kernellul pune la intrarea 80 din IDT, valoarea DPL=3

- Slides: 9