Universit degli studi di Roma Tor Vergata Facolt

- Slides: 24

Università degli studi di Roma Tor Vergata Facoltà di Ingegneria Corso di Laurea in Ingegneria Gestionale Tesi di Laurea in Controlli Automatici TOR VERGATA PROGETTAZIONE E REALIZZAZIONE DI UNA UNITÀ DI POTENZA MULTIUSO PER IL CONTROLLO DI MOTORI A RILUTTANZA VARIABILE Relatore: Candidato: Prof. Salvatore Nicosia Enrico Maria Rossi Correlatore: Ing. Luca Zaccarian

INDICE DELLA PRESENTAZIONE 1. PRELIMINARI 2. PROGETTAZIONE 3. REALIZZAZIONE DEL PROTOTIPO 4. SISTEMA DI INTERFACCIAMENTO 5. APPLICAZIONI SPERIMENTALI

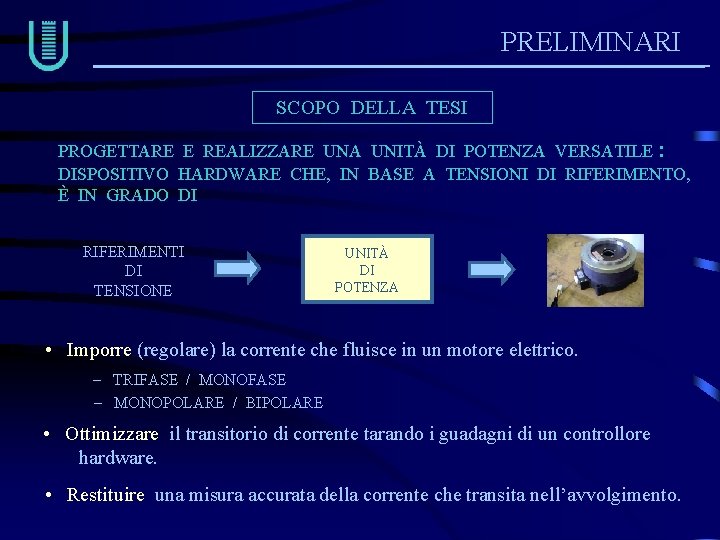

PRELIMINARI SCOPO DELLA TESI PROGETTARE E REALIZZARE UNA UNITÀ DI POTENZA VERSATILE : DISPOSITIVO HARDWARE CHE, IN BASE A TENSIONI DI RIFERIMENTO, È IN GRADO DI RIFERIMENTI DI TENSIONE UNITÀ DI POTENZA • Imporre (regolare) la corrente che fluisce in un motore elettrico. – TRIFASE / MONOFASE – MONOPOLARE / BIPOLARE • Ottimizzare il transitorio di corrente tarando i guadagni di un controllore hardware. • Restituire una misura accurata della corrente che transita nell’avvolgimento.

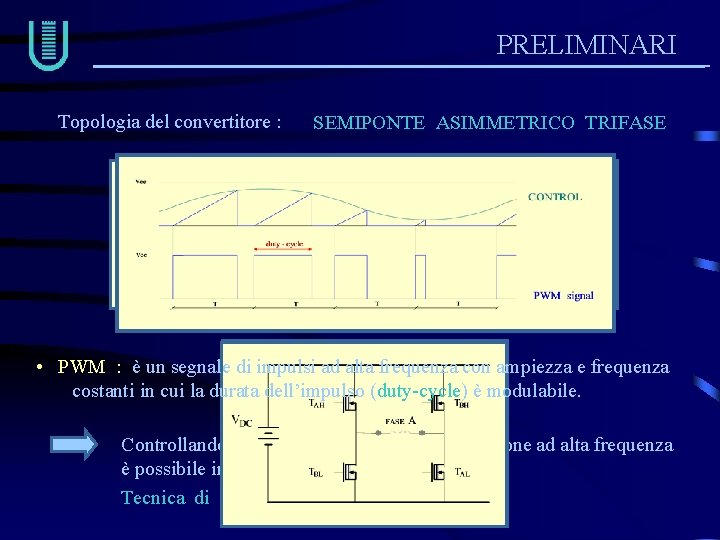

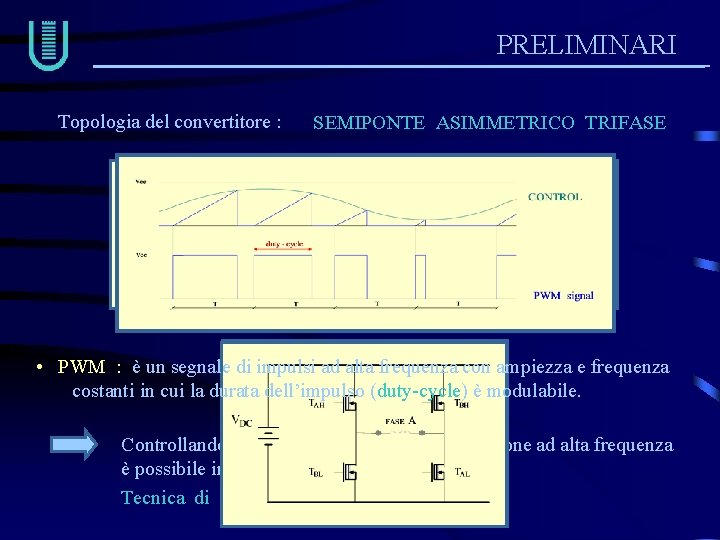

PRELIMINARI Topologia del convertitore : SEMIPONTE ASIMMETRICO TRIFASE MONOPOLARE MONOFASE BIPOLARE • PWM : è un segnale di impulsi ad alta frequenza con ampiezza e frequenza costanti in cui la durata dell’impulso (duty-cycle) è modulabile. Controllando il duty-cycle di questa commutazione ad alta frequenza è possibile imporre l’andamento della corrente. Tecnica di VOLTAGE CHOPPING

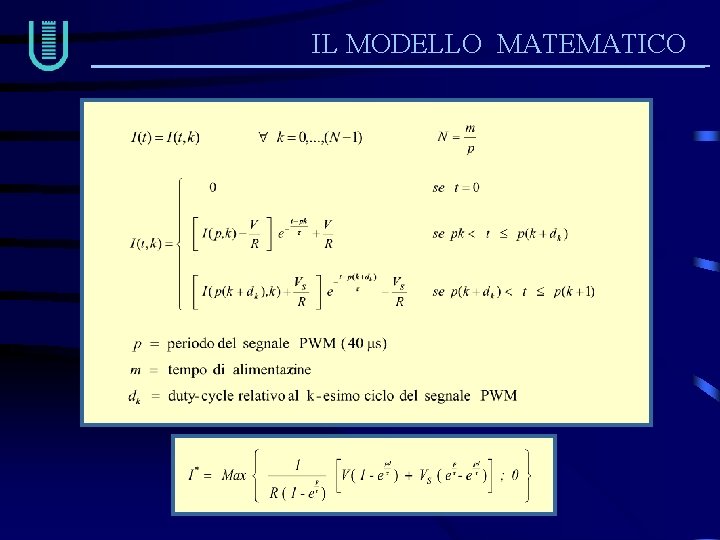

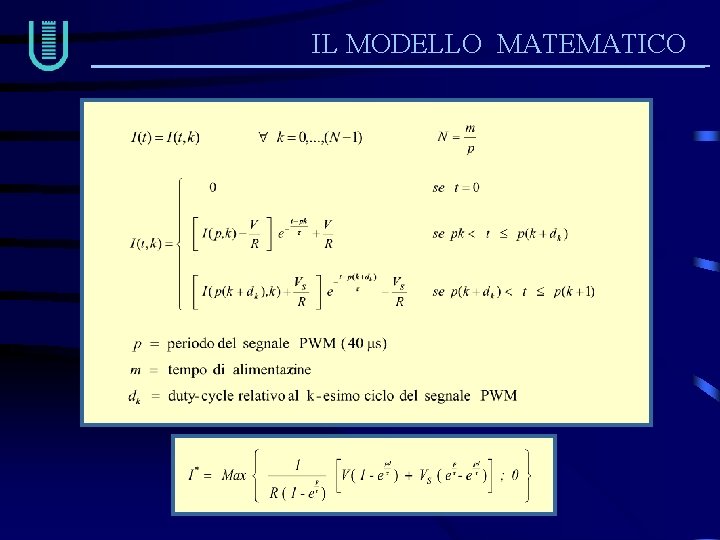

IL MODELLO MATEMATICO

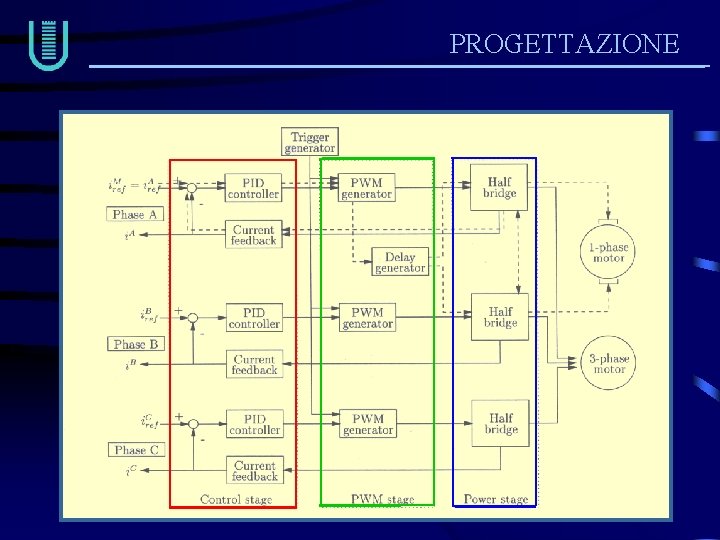

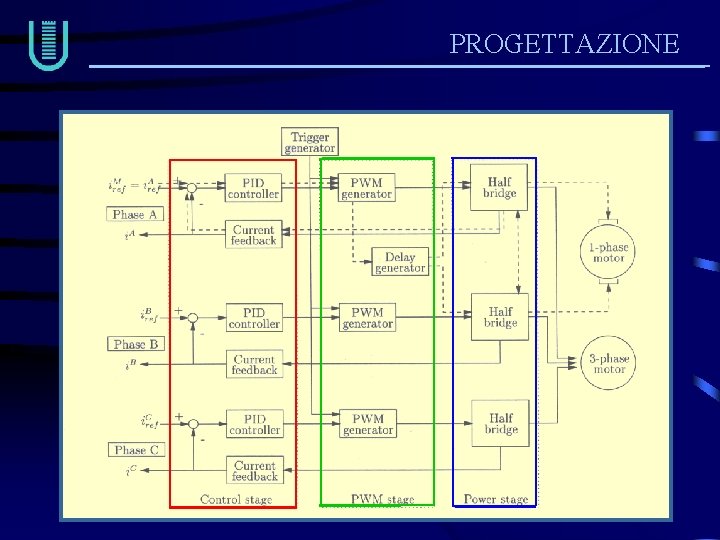

PROGETTAZIONE

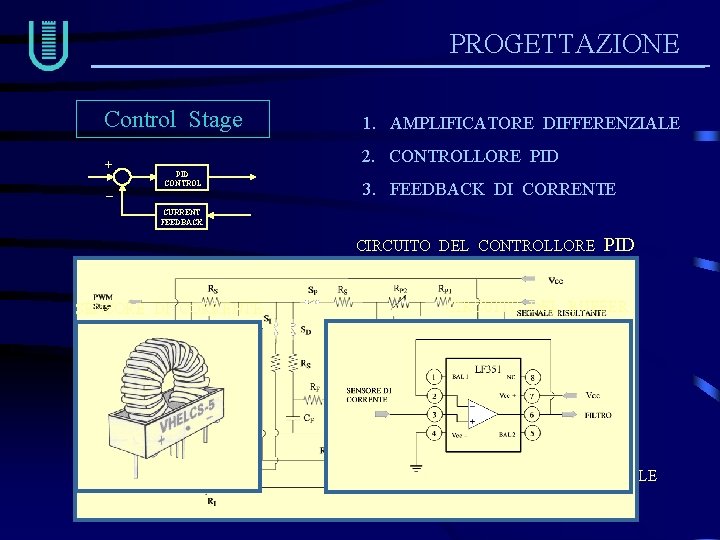

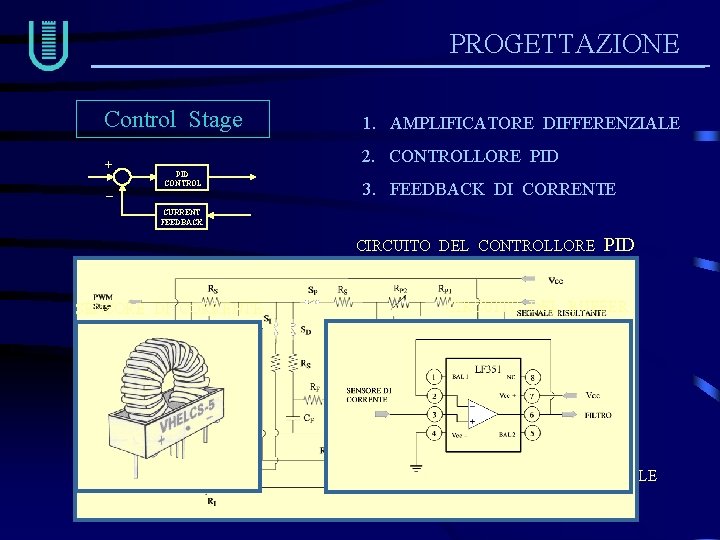

PROGETTAZIONE Control Stage + _ 1. AMPLIFICATORE DIFFERENZIALE 2. CONTROLLORE PID CONTROL 3. FEEDBACK DI CORRENTE CURRENT FEEDBACK CIRCUITO DEL CONTROLLORE SENSORE DI CORRENTE PID CIRCUITO DEL BUFFER CIRCUITO DELL AMPLIFICATORE DIFFERENZIALE

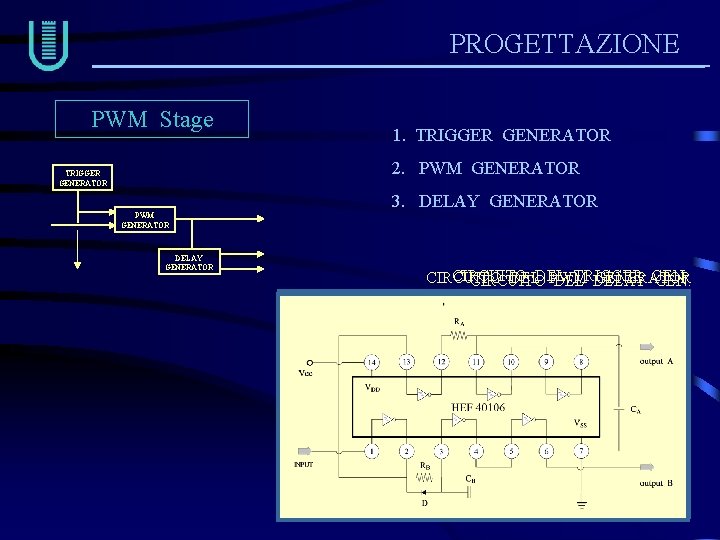

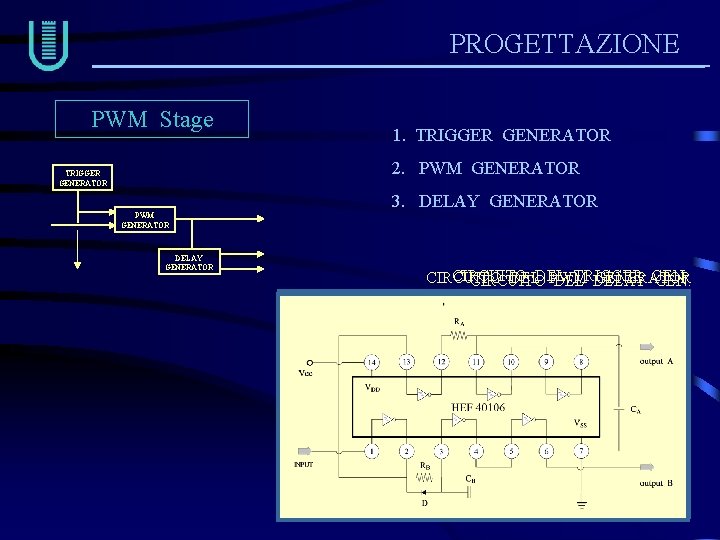

PROGETTAZIONE PWM Stage 1. TRIGGER GENERATOR 2. PWM GENERATOR TRIGGER GENERATOR 3. DELAY GENERATOR PWM GENERATOR DELAY GENERATOR CIRCUITO TRIGGER GEN. CIRCUITO DELDEL PWM GENERATOR CIRCUITO DELAY GEN.

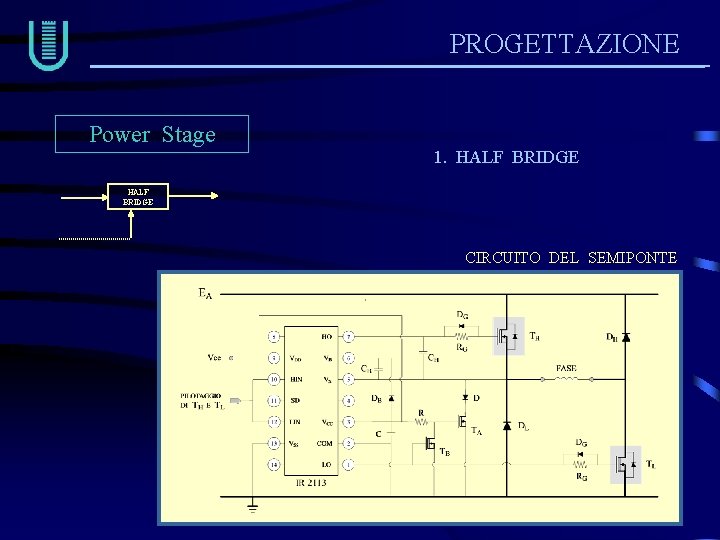

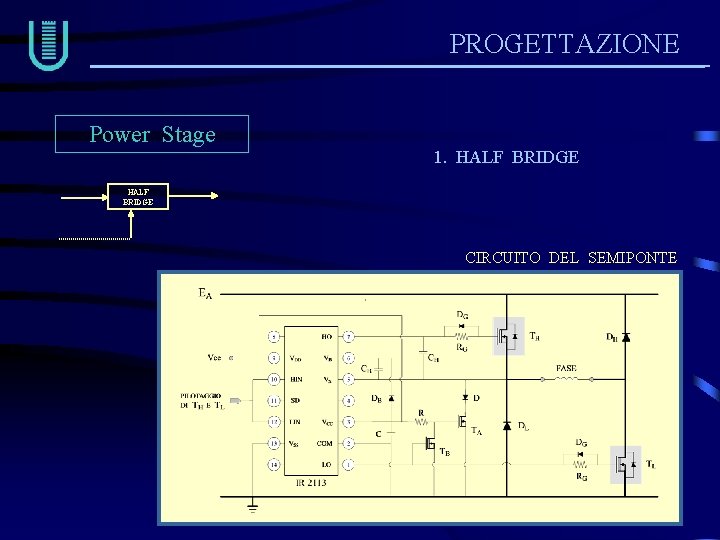

PROGETTAZIONE Power Stage 1. HALF BRIDGE CIRCUITO DEL SEMIPONTE

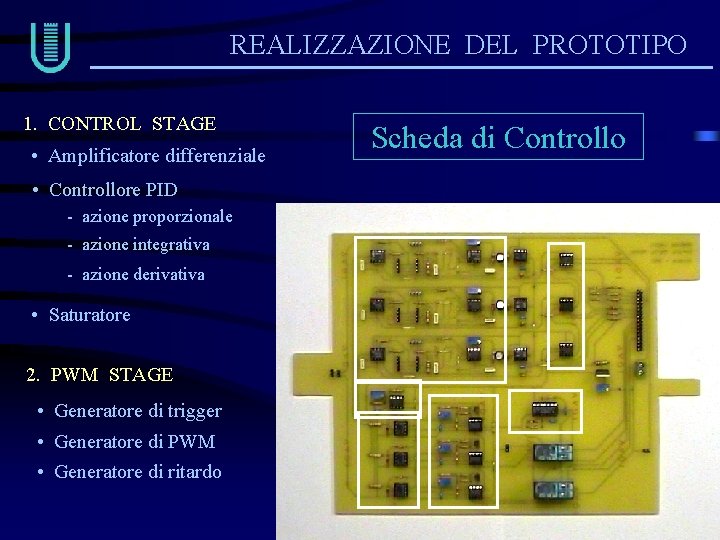

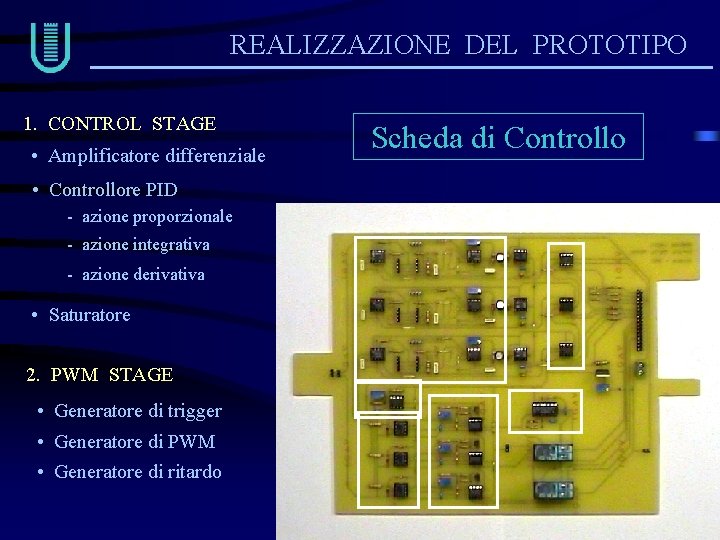

REALIZZAZIONE DEL PROTOTIPO 1. CONTROL STAGE • Amplificatore differenziale • Controllore PID - azione proporzionale - azione integrativa - azione derivativa • Saturatore 2. PWM STAGE • Generatore di trigger • Generatore di PWM • Generatore di ritardo Scheda di Controllo

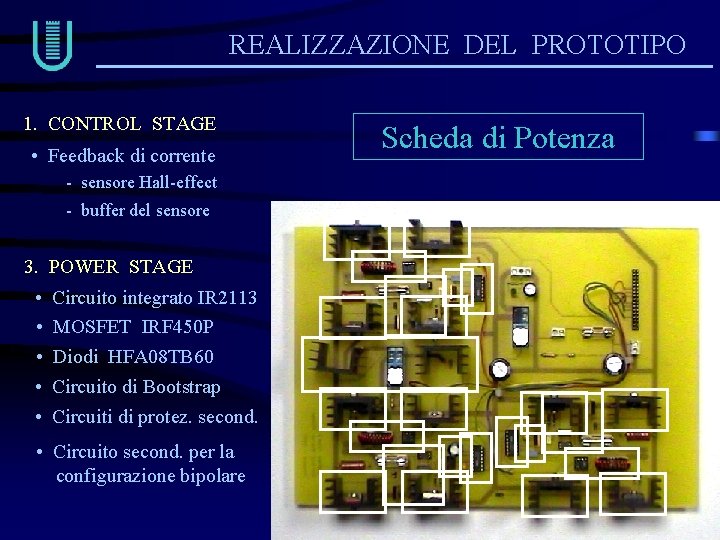

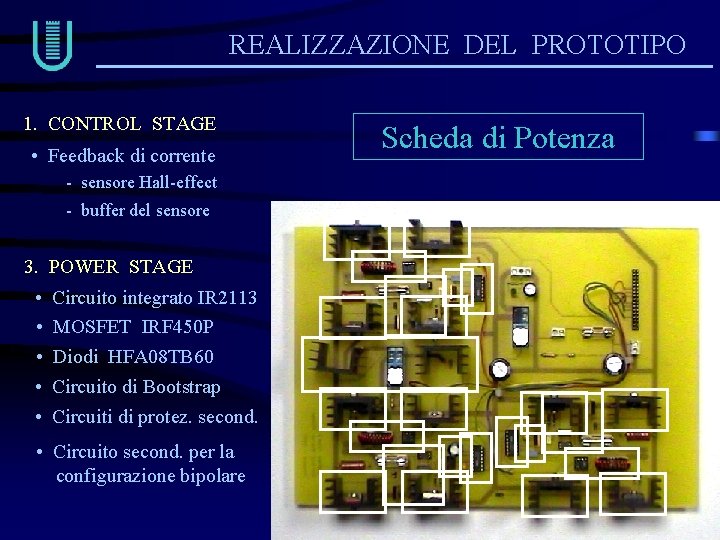

REALIZZAZIONE DEL PROTOTIPO 1. CONTROL STAGE • Feedback di corrente - sensore Hall-effect - buffer del sensore 3. POWER STAGE • • • Circuito integrato IR 2113 MOSFET IRF 450 P Diodi HFA 08 TB 60 Circuito di Bootstrap Circuiti di protez. second. • Circuito second. per la configurazione bipolare Scheda di Potenza

REALIZZAZIONE DEL PROTOTIPO Prototipo completo

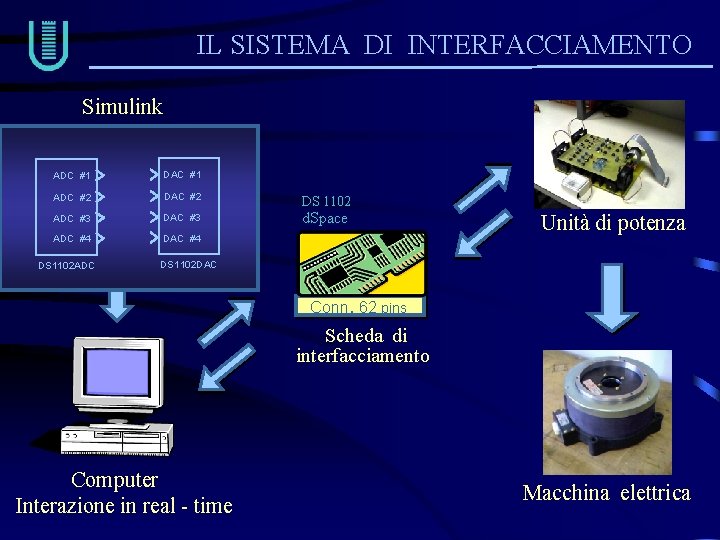

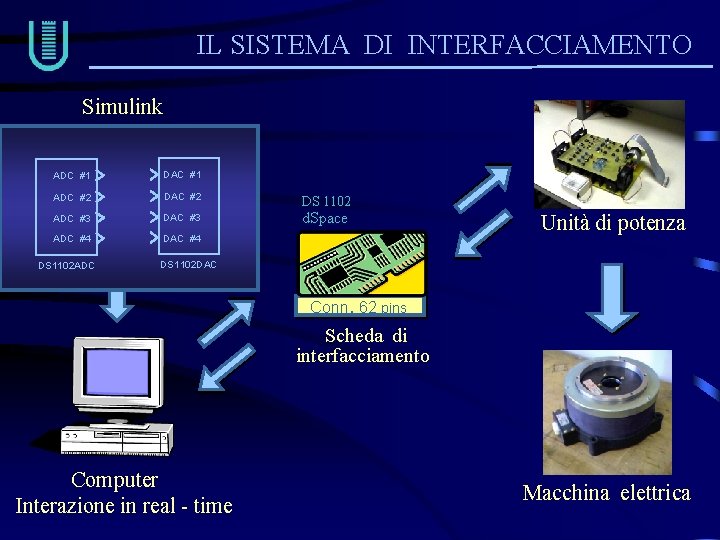

IL SISTEMA DI INTERFACCIAMENTO Simulink ADC #1 DAC #1 ADC #2 DAC #2 ( Matlab )DAC #3 ADC #4 DS 1102 ADC DS 1102 d. Space DAC #4 Unità di potenza DS 1102 DAC Conn. 62 pins Scheda di interfacciamento Computer Interazione in real - time Macchina elettrica

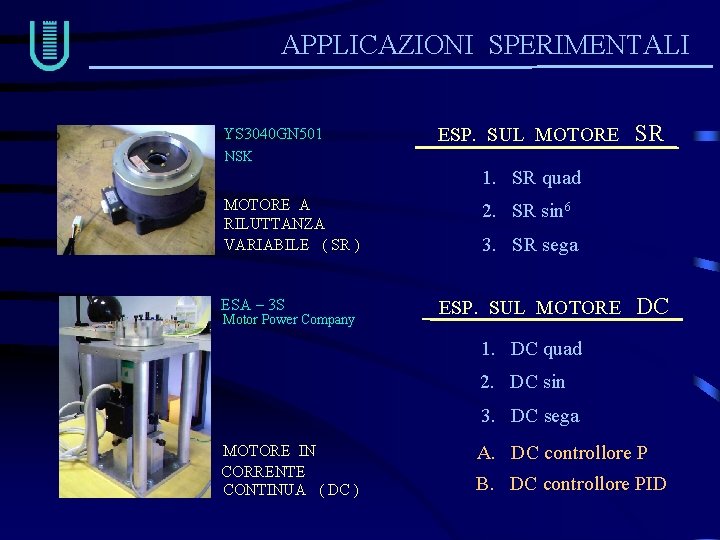

APPLICAZIONI SPERIMENTALI YS 3040 GN 501 ESP. SUL MOTORE SR NSK 1. SR quad MOTORE A RILUTTANZA VARIABILE ( SR ) ESA – 3 S Motor Power Company 2. SR sin 6 3. SR sega ESP. SUL MOTORE DC 1. DC quad 2. DC sin 3. DC sega MOTORE IN CORRENTE CONTINUA ( DC ) A. DC controllore P B. DC controllore PID

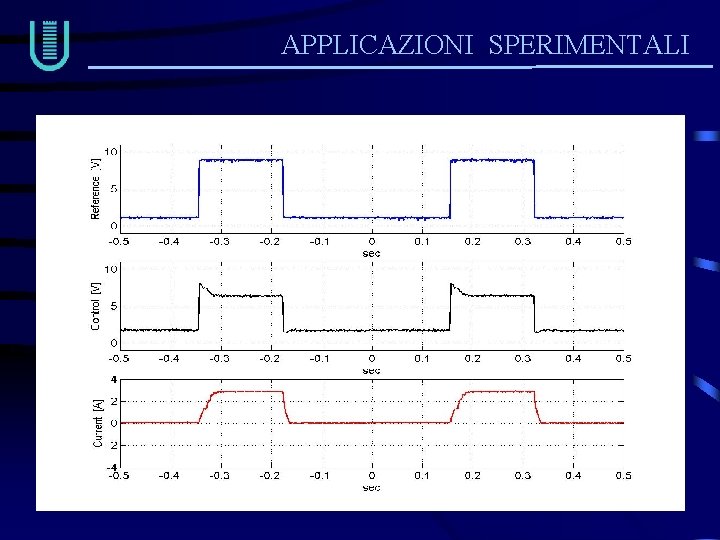

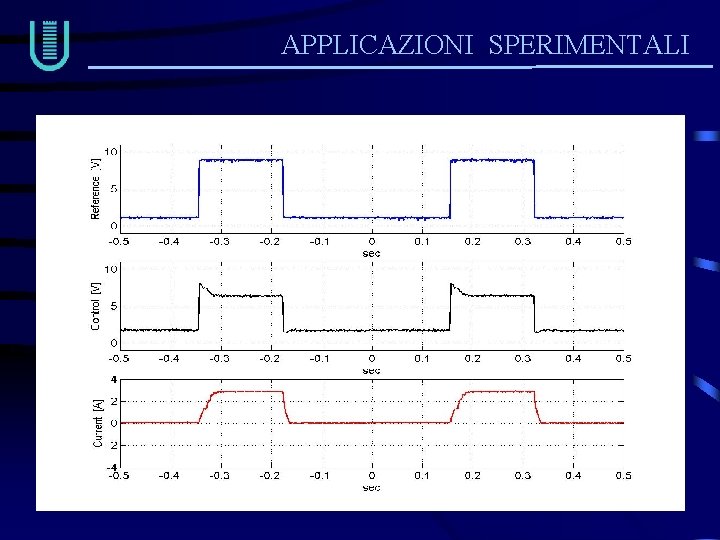

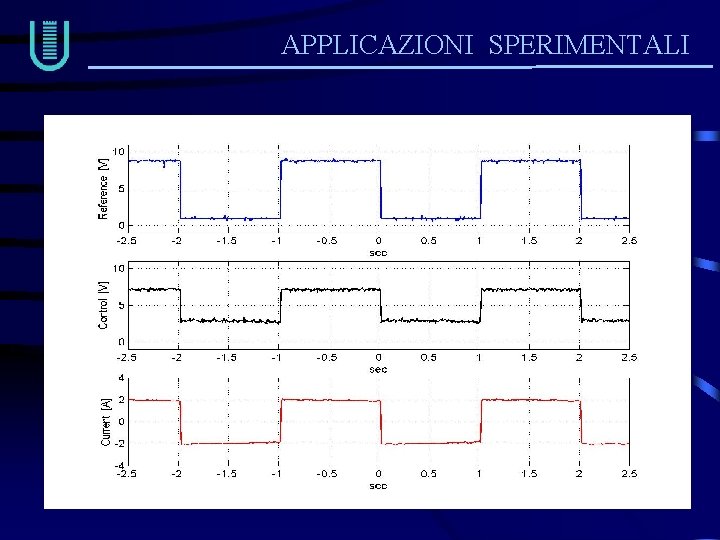

APPLICAZIONI SPERIMENTALI 1. ESPERIMENTO SR quad

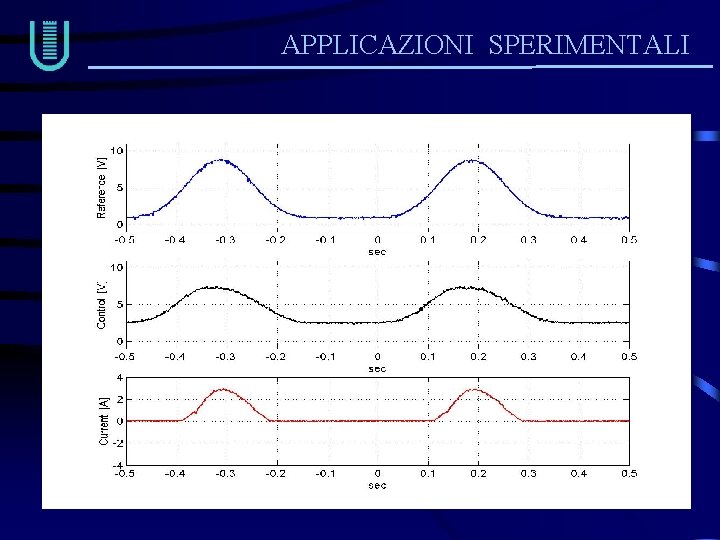

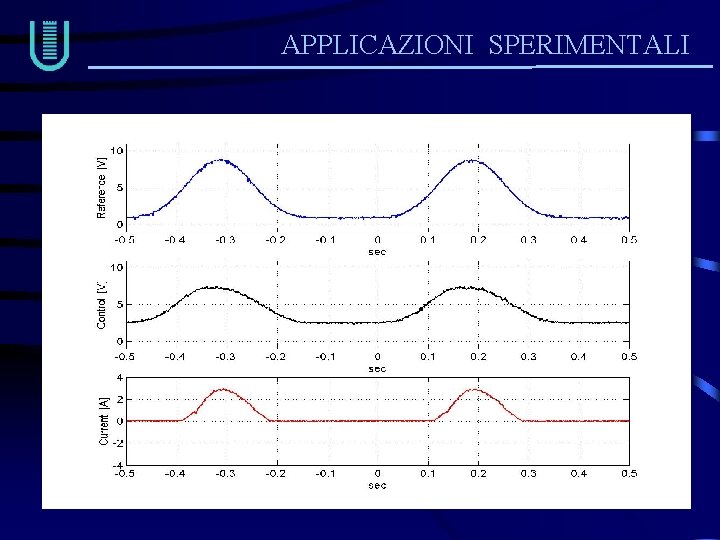

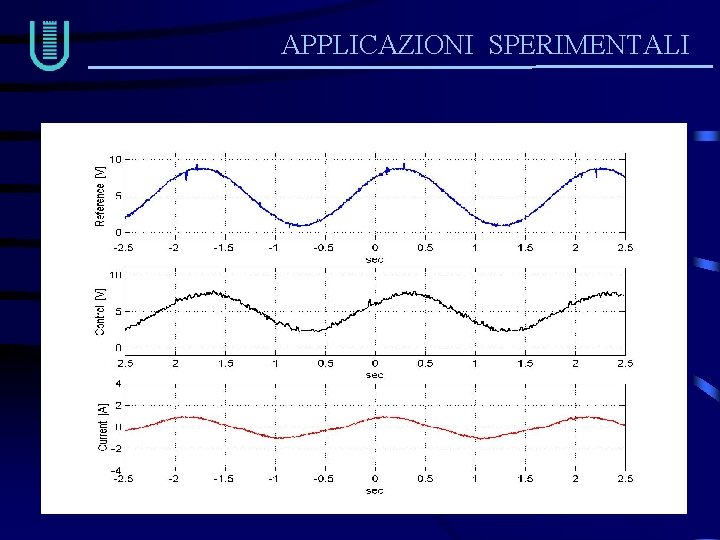

APPLICAZIONI SPERIMENTALI 2. ESPERIMENTO SR sin 6

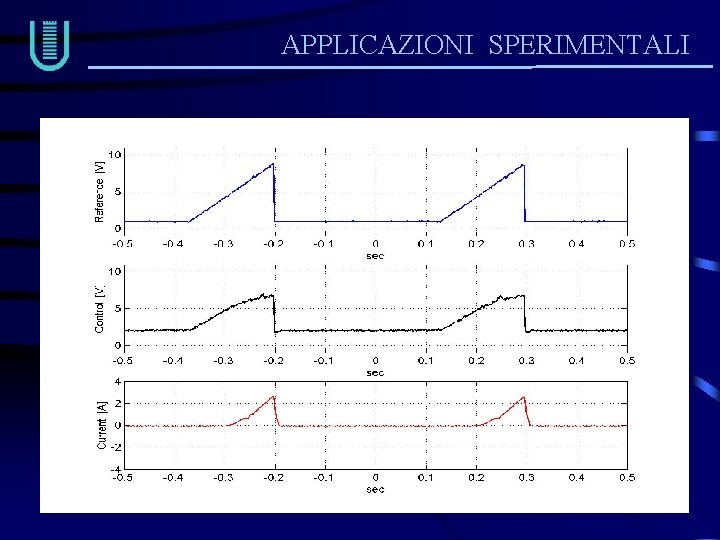

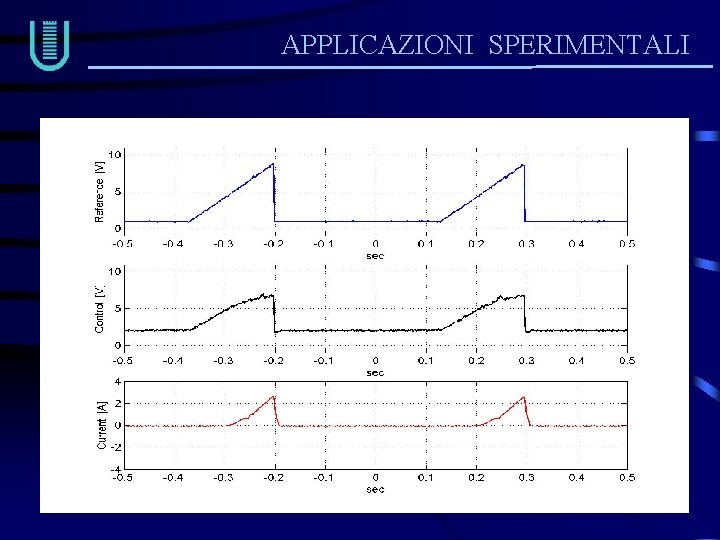

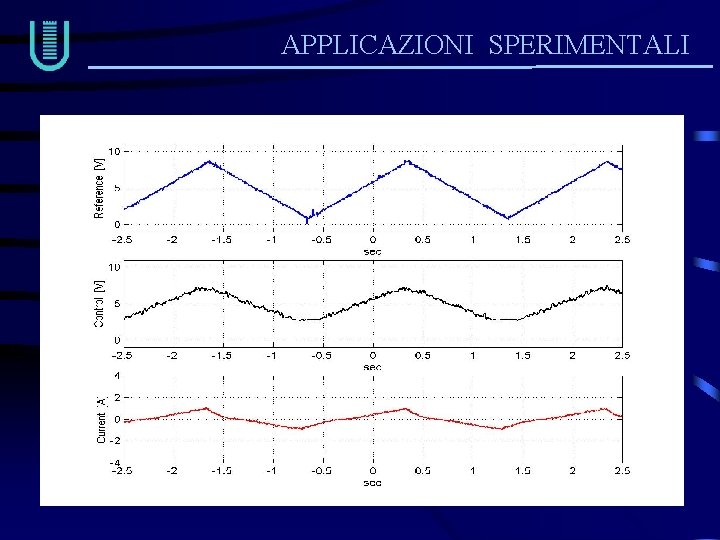

APPLICAZIONI SPERIMENTALI 3. ESPERIMENTO SR sega

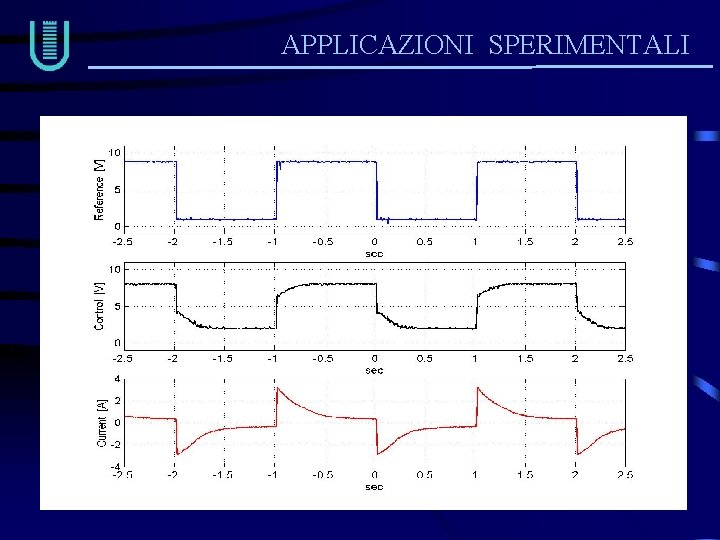

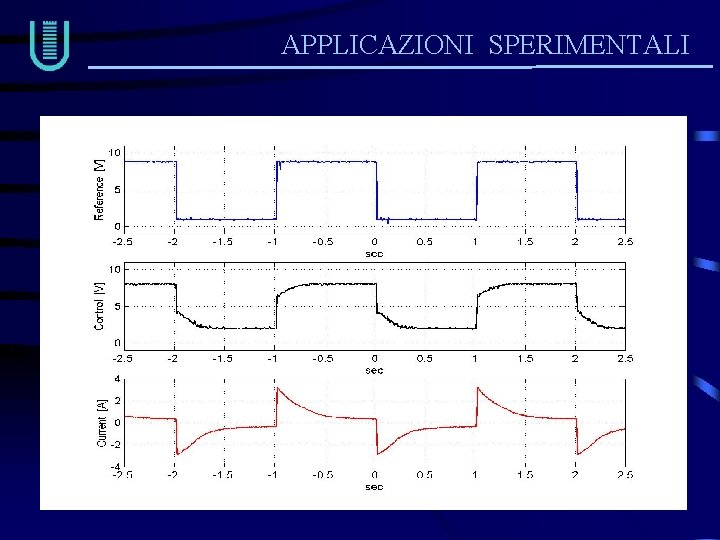

APPLICAZIONI SPERIMENTALI 1 b. ESPERIMENTO DC quad

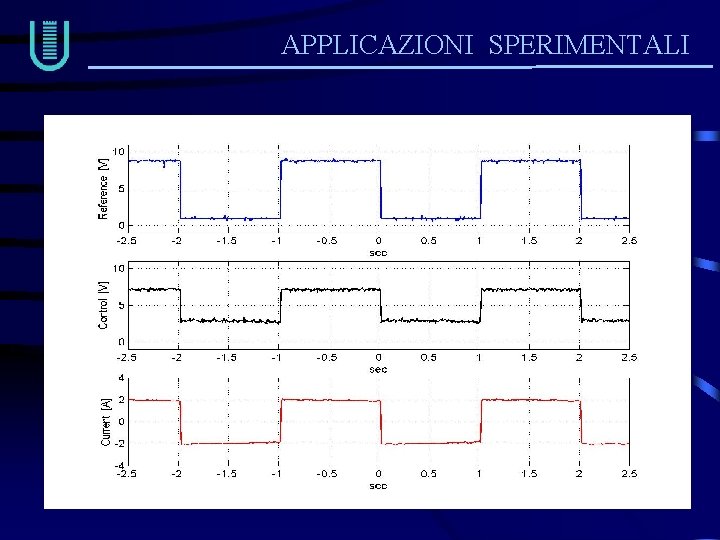

APPLICAZIONI SPERIMENTALI 1 b. ESPERIMENTO DC quad CON CARICO INERZIALE

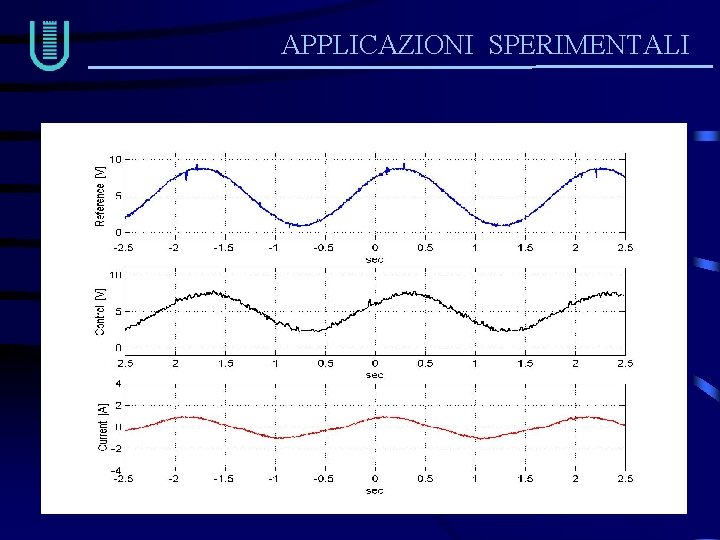

APPLICAZIONI SPERIMENTALI 2. ESPERIMENTO DC sin

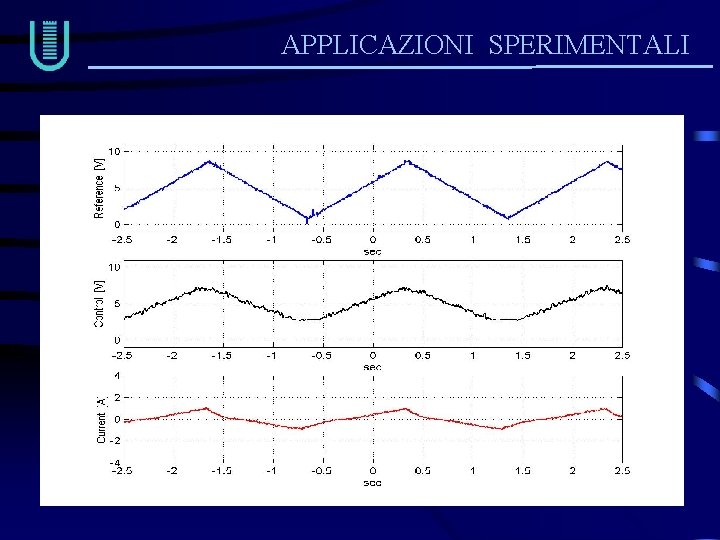

APPLICAZIONI SPERIMENTALI 3. ESPERIMENTO DC sega

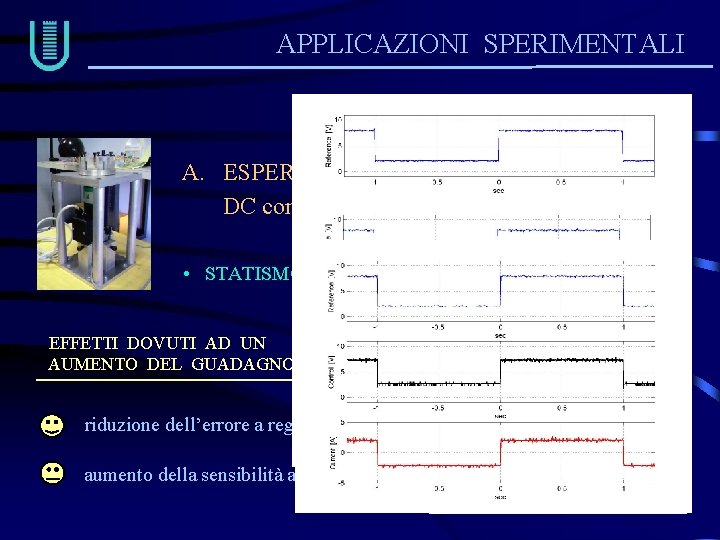

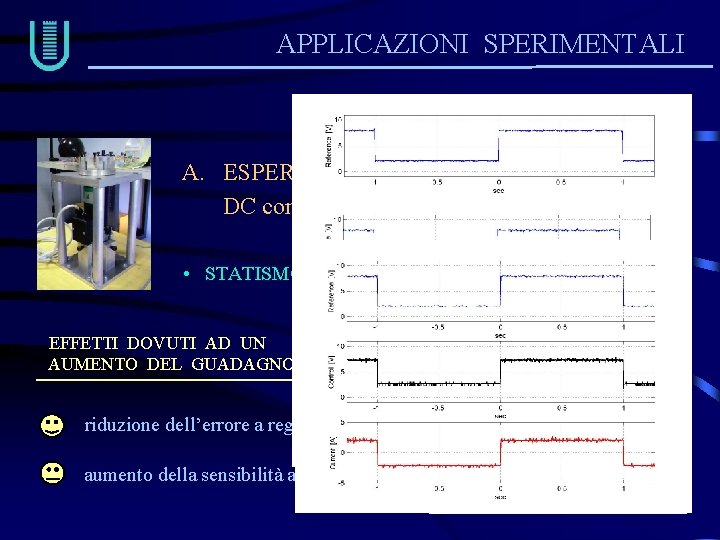

APPLICAZIONI SPERIMENTALI A. ESPERIMENTO DC controllore P • STATISMO a regime EFFETTI DOVUTI AD UN AUMENTO DEL GUADAGNO k P riduzione dell’errore a regime aumento della sensibilità al rumore

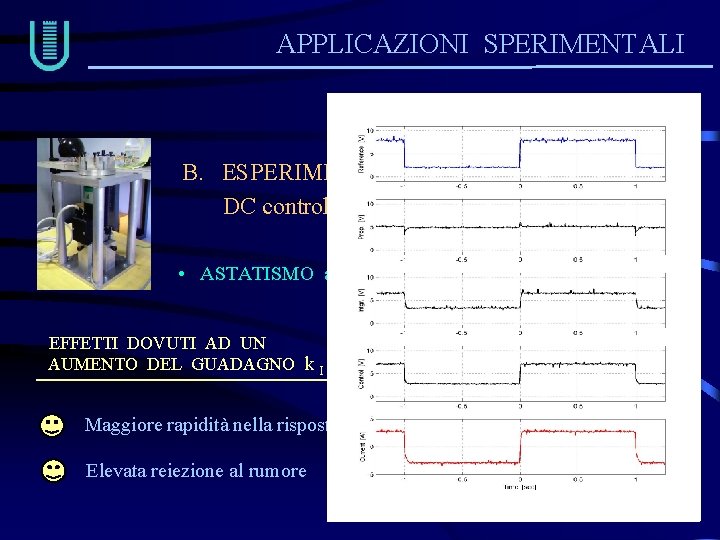

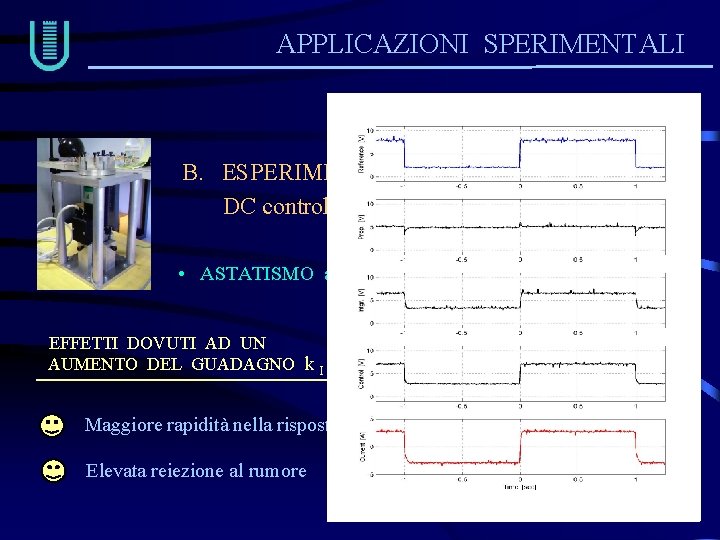

APPLICAZIONI SPERIMENTALI B. ESPERIMENTO DC controllore PID • ASTATISMO a regime EFFETTI DOVUTI AD UN AUMENTO DEL GUADAGNO k I Maggiore rapidità nella risposta Elevata reiezione al rumore

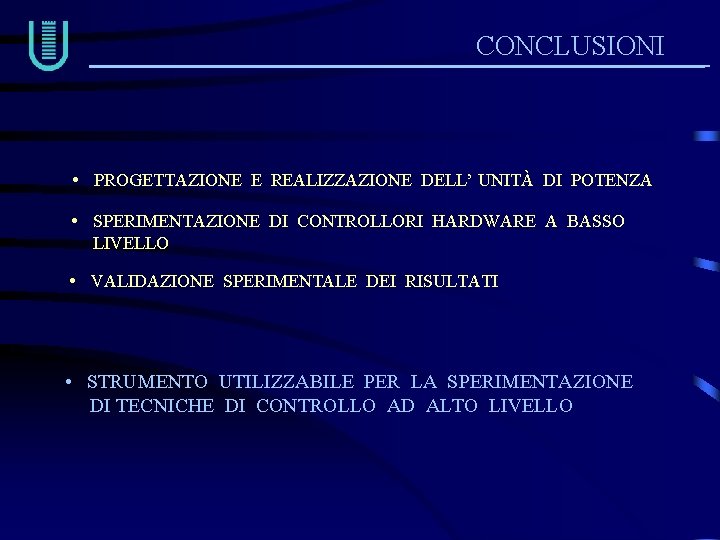

CONCLUSIONI • PROGETTAZIONE E REALIZZAZIONE DELL’ UNITÀ DI POTENZA • SPERIMENTAZIONE DI CONTROLLORI HARDWARE A BASSO LIVELLO • VALIDAZIONE SPERIMENTALE DEI RISULTATI • STRUMENTO UTILIZZABILE PER LA SPERIMENTAZIONE DI TECNICHE DI CONTROLLO AD ALTO LIVELLO