Universit degli Studi di Napoli Federico II Scuola

- Slides: 30

Università degli Studi di Napoli “Federico II” Scuola Politecnica e delle Scienze di Base Area Didattica di Scienze Matematiche Fisiche e Naturali Tesi magistrale in Fisica Development of High-speed Digital Links for the ATLAS Experiment at CERN Relatori: Prof. Alberto Aloisio Dott. Vincenzo Izzo Dott. Raffaele Giordano Candidato: Noemi Marino matr. N 94/166

Sommario • LHC, rivelatore ATLAS e futuri Upgrades • New Small Wheel (NSW), s. TGC ed Elettronica • Progetto di un Link seriale in Latenza fissa • Misure e Risultati

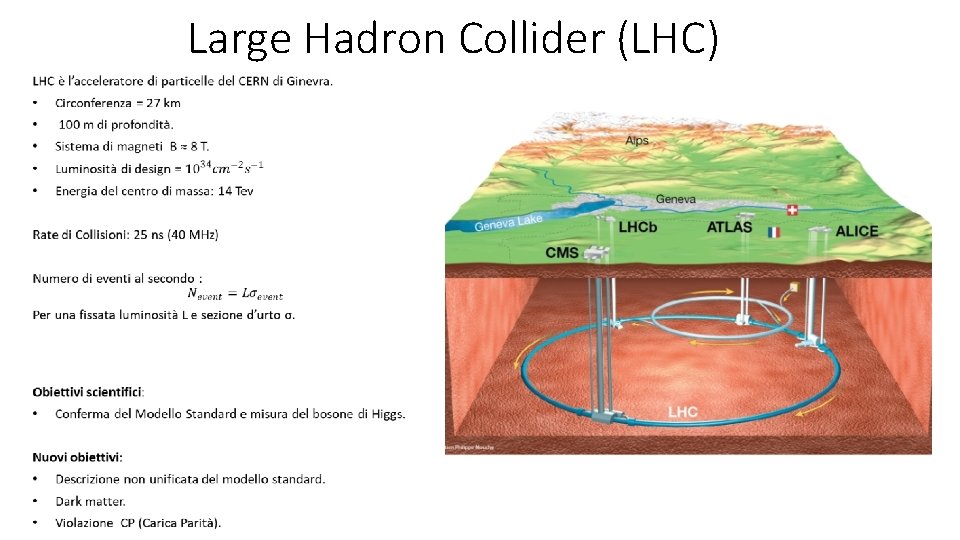

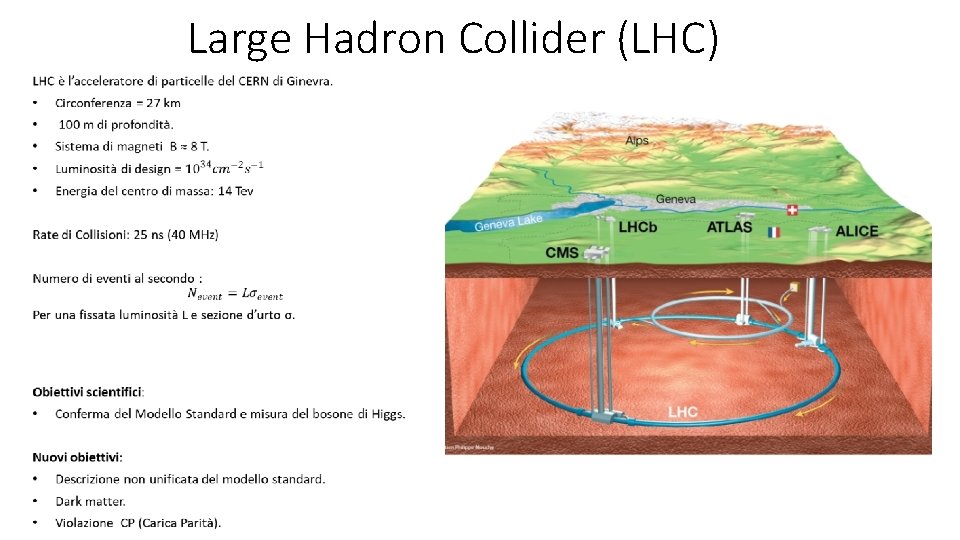

Large Hadron Collider (LHC)

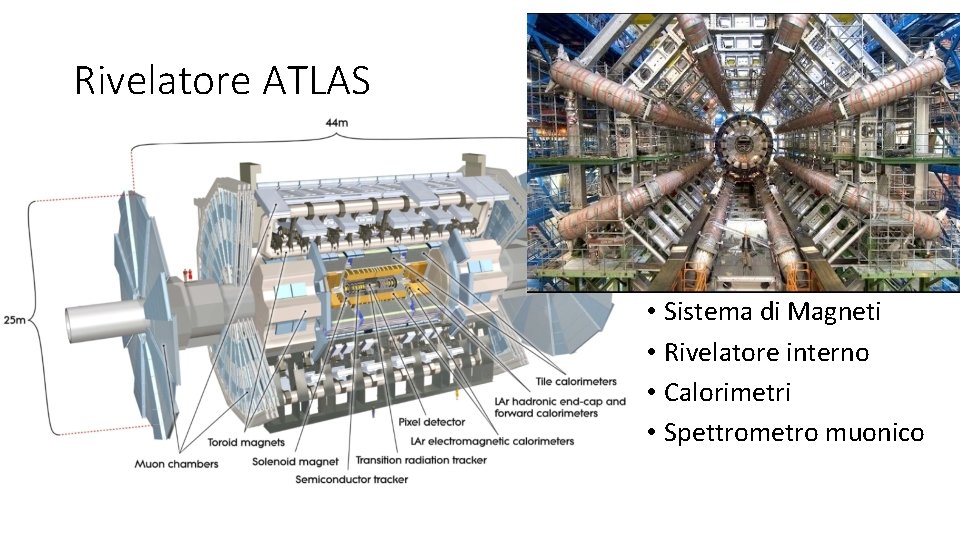

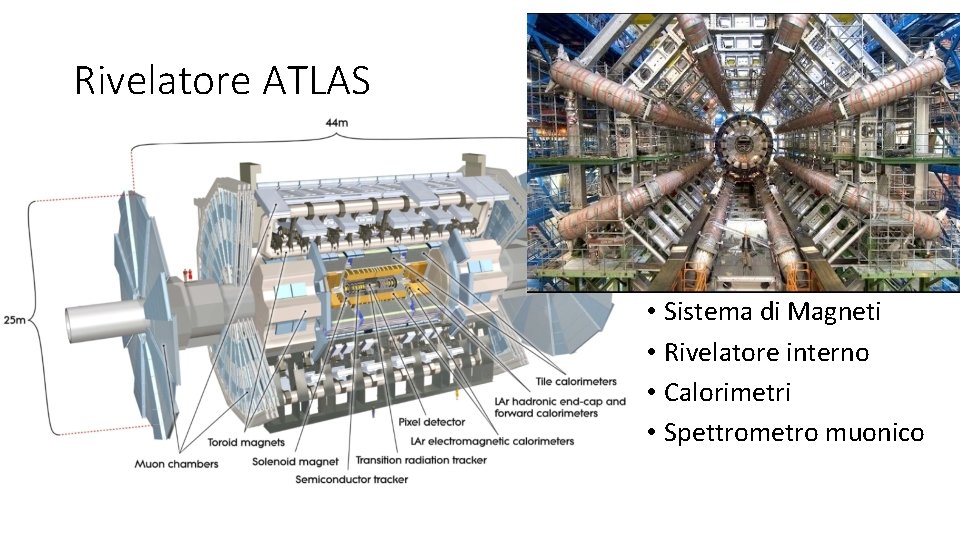

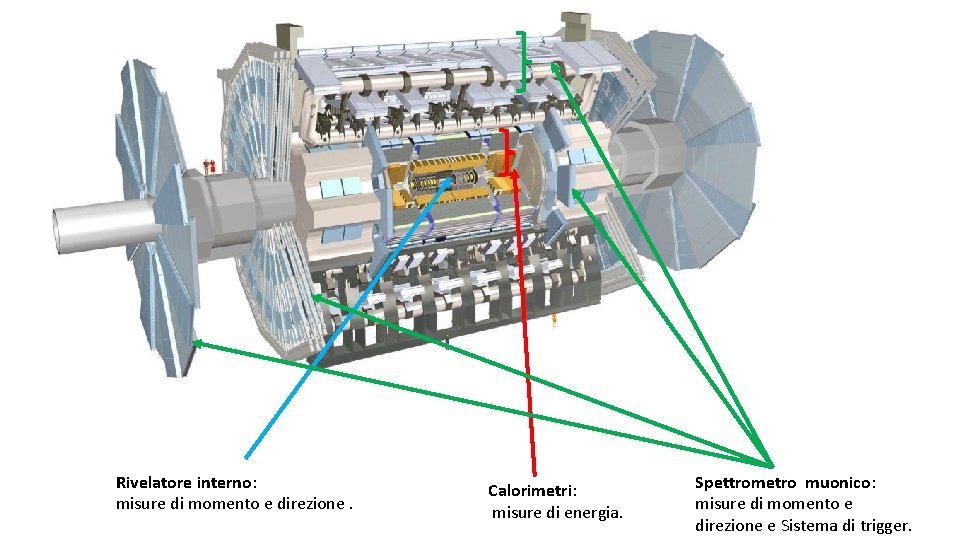

Rivelatore ATLAS • Sistema di Magneti • Rivelatore interno • Calorimetri • Spettrometro muonico

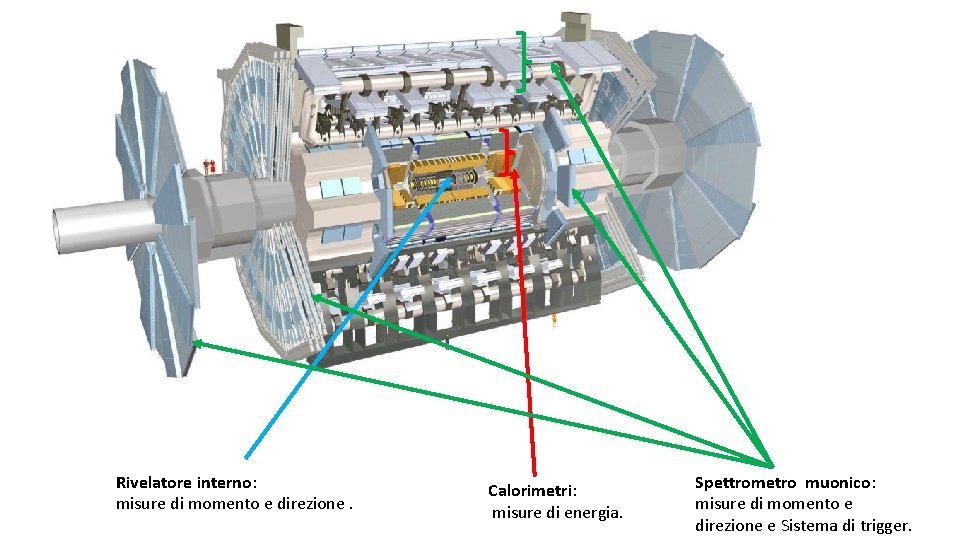

Rivelatore interno: misure di momento e direzione. Calorimetri: misure di energia. Spettrometro muonico: misure di momento e direzione e Sistema di trigger.

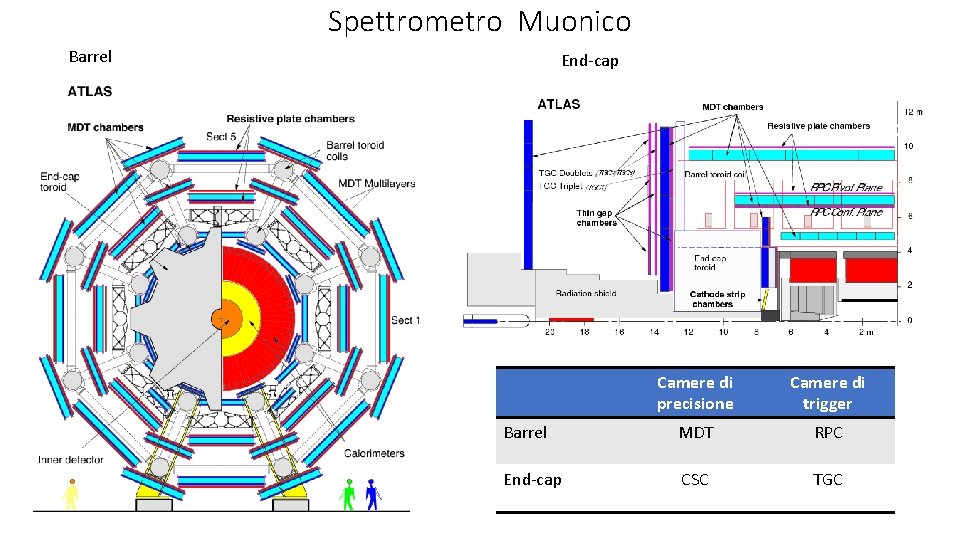

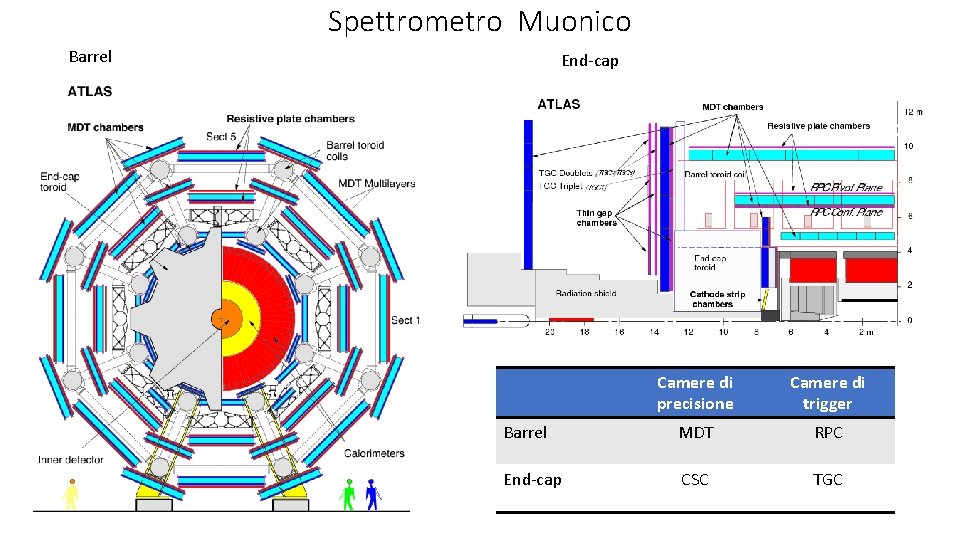

Spettrometro Muonico Barrel End-cap Camere di precisione Camere di trigger Barrel MDT RPC End-cap CSC TGC

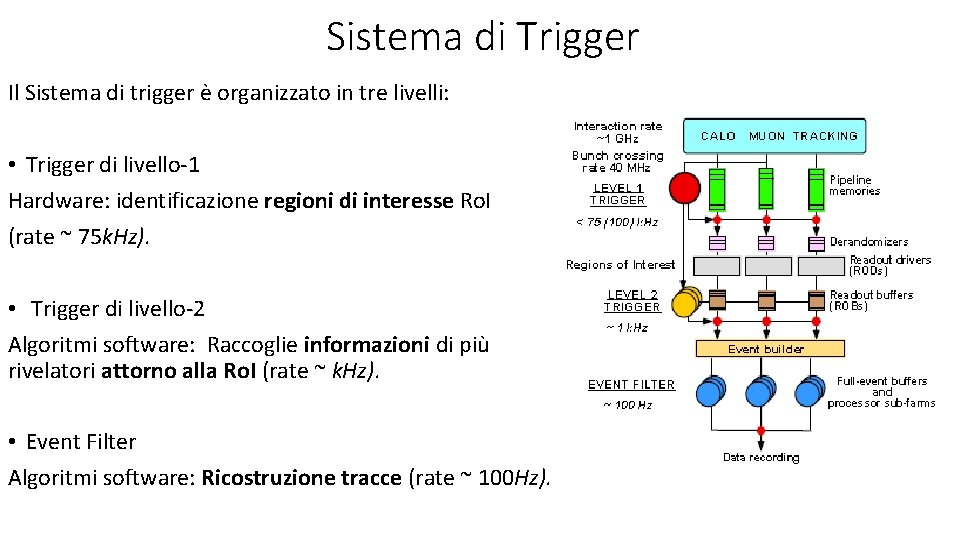

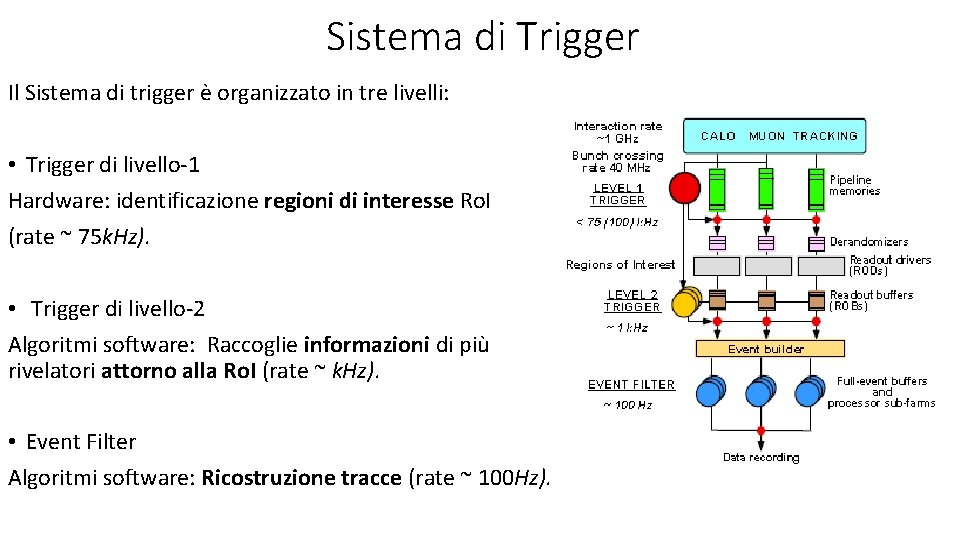

Sistema di Trigger Il Sistema di trigger è organizzato in tre livelli: • Trigger di livello-1 Hardware: identificazione regioni di interesse Ro. I (rate ~ 75 k. Hz). • Trigger di livello-2 Algoritmi software: Raccoglie informazioni di più rivelatori attorno alla Ro. I (rate ~ k. Hz). • Event Filter Algoritmi software: Ricostruzione tracce (rate ~ 100 Hz).

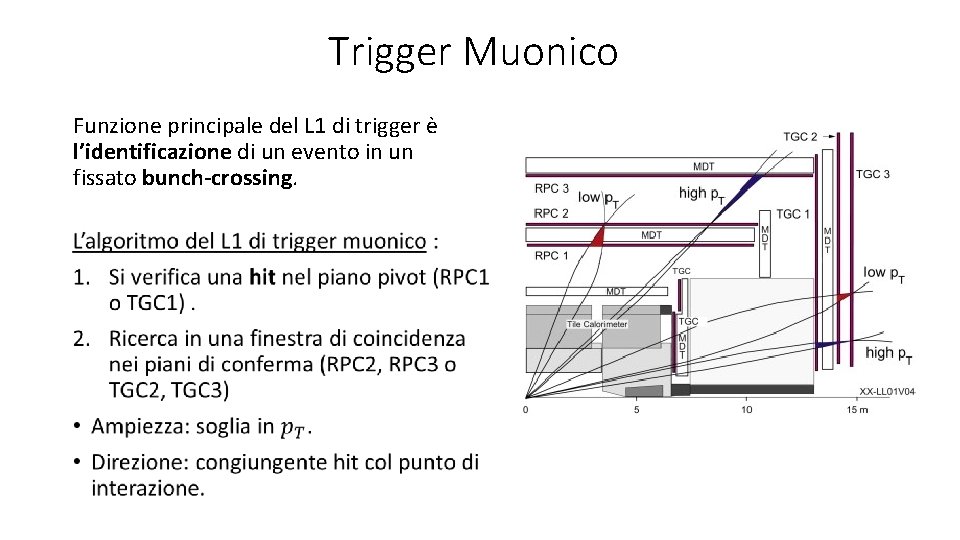

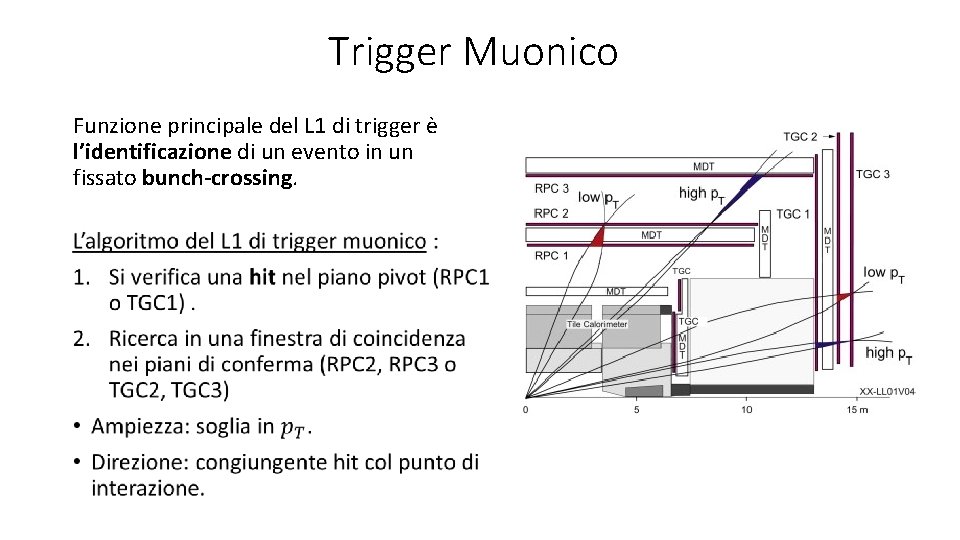

Trigger Muonico Funzione principale del L 1 di trigger è l’identificazione di un evento in un fissato bunch-crossing. •

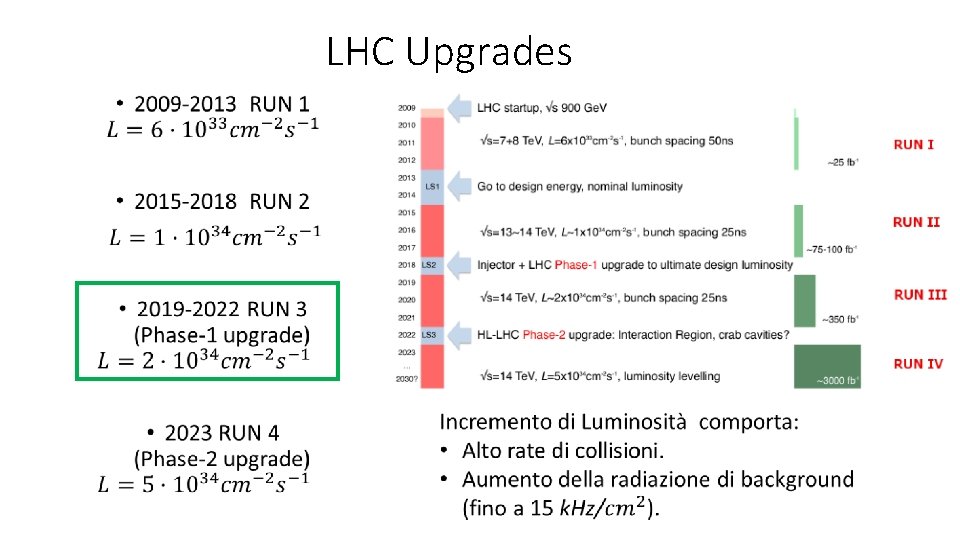

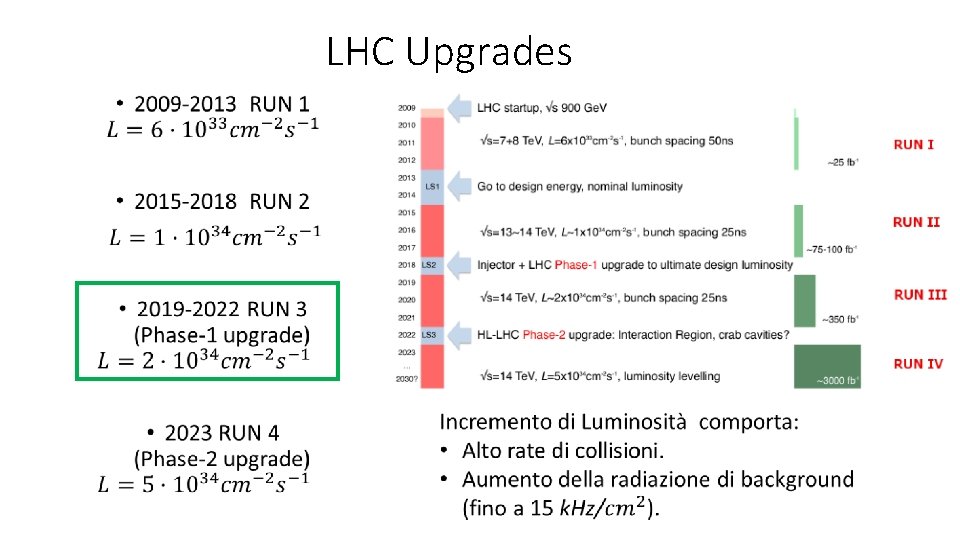

LHC Upgrades •

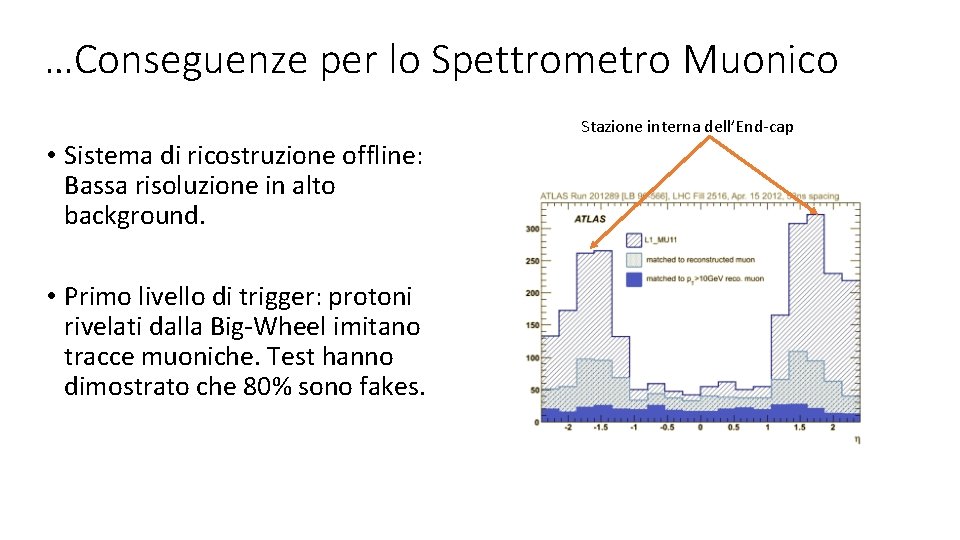

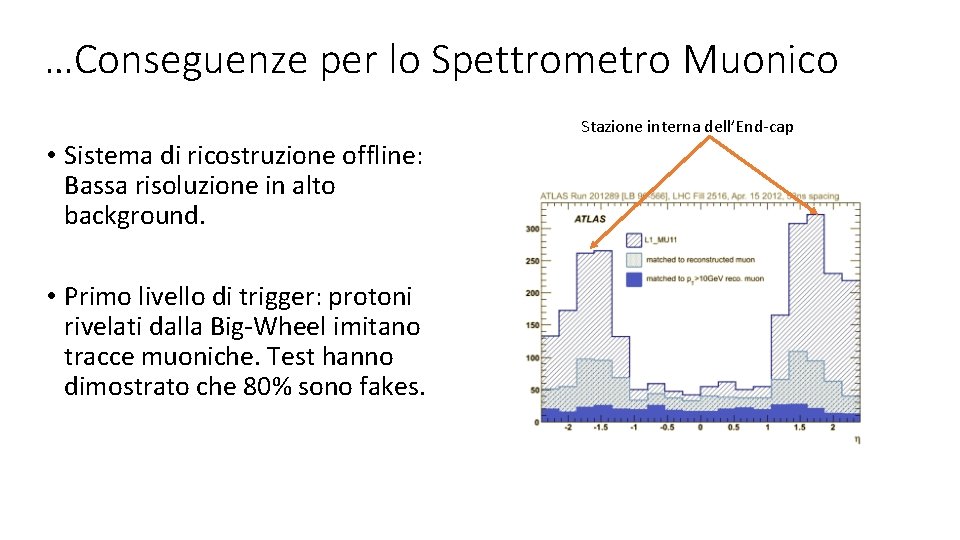

…Conseguenze per lo Spettrometro Muonico • Sistema di ricostruzione offline: Bassa risoluzione in alto background. • Primo livello di trigger: protoni rivelati dalla Big-Wheel imitano tracce muoniche. Test hanno dimostrato che 80% sono fakes. Stazione interna dell’End-cap

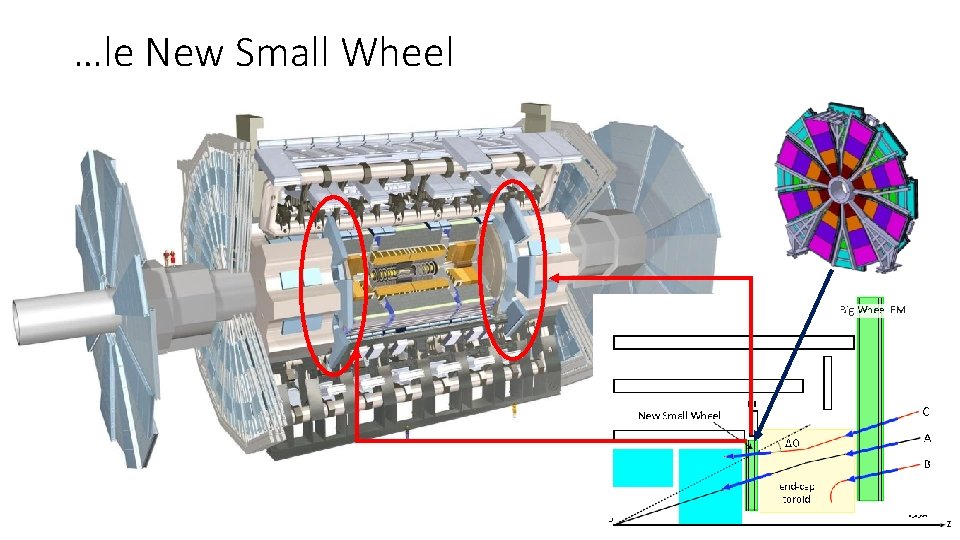

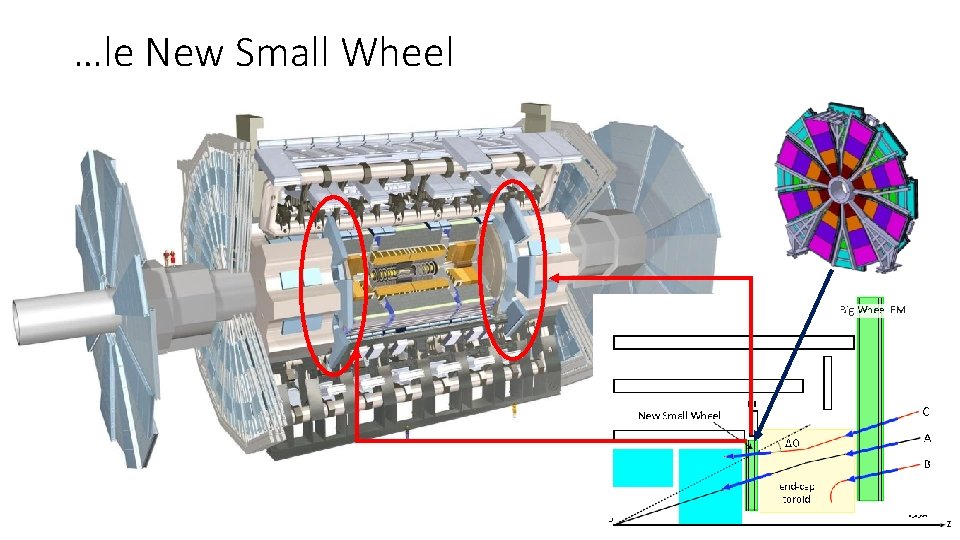

…le New Small Wheel

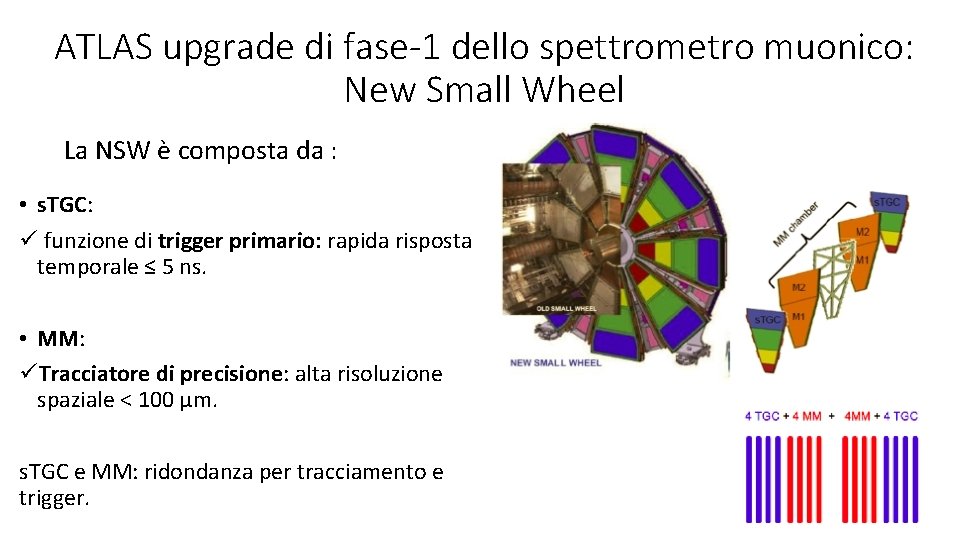

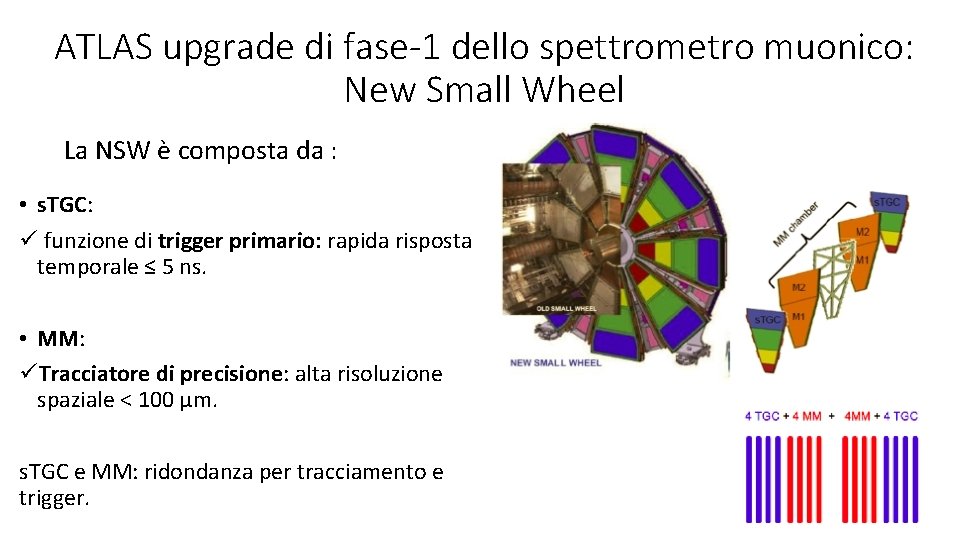

ATLAS upgrade di fase-1 dello spettrometro muonico: New Small Wheel La NSW è composta da : • s. TGC: ü funzione di trigger primario: rapida risposta temporale ≤ 5 ns. • MM: üTracciatore di precisione: alta risoluzione spaziale < 100 µm. s. TGC e MM: ridondanza per tracciamento e trigger.

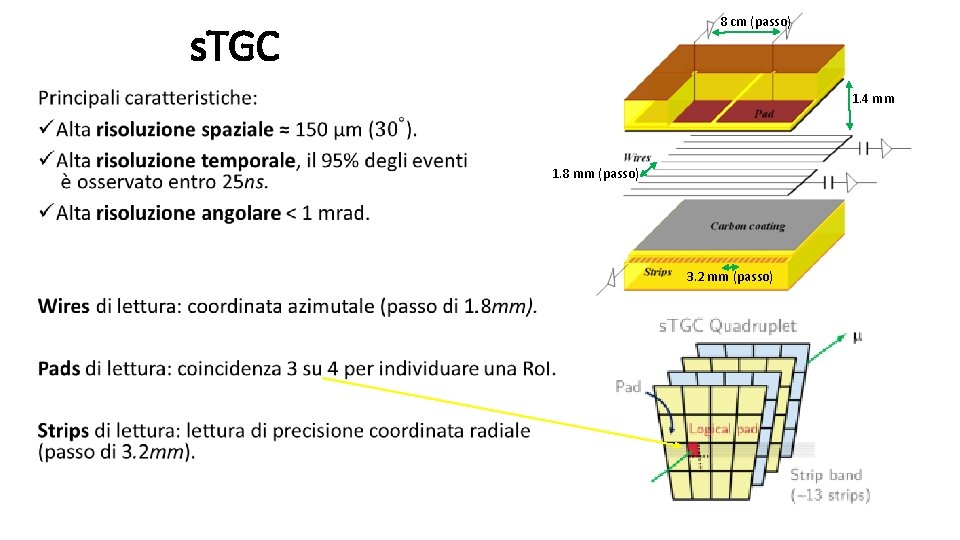

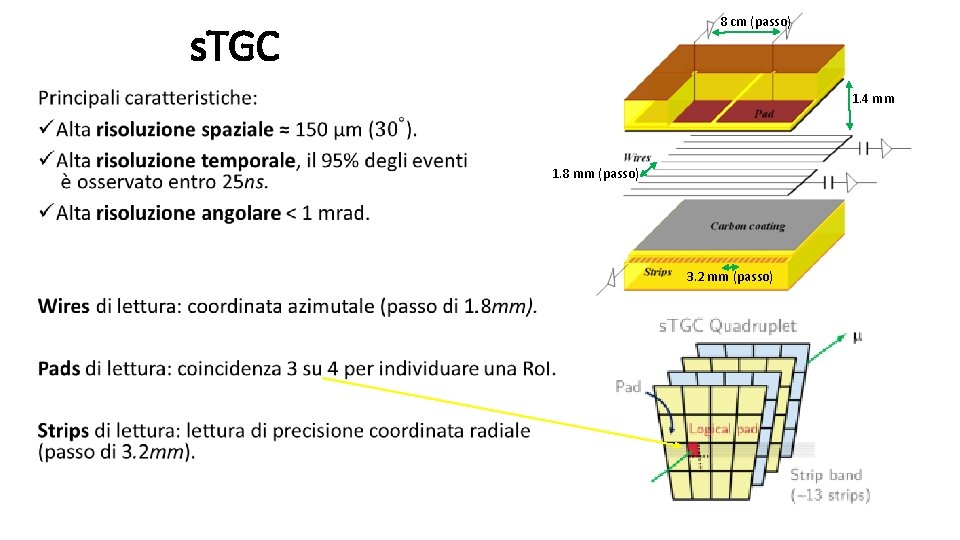

8 cm (passo) s. TGC • 1. 4 mm 1. 8 mm (passo) 3. 2 mm (passo)

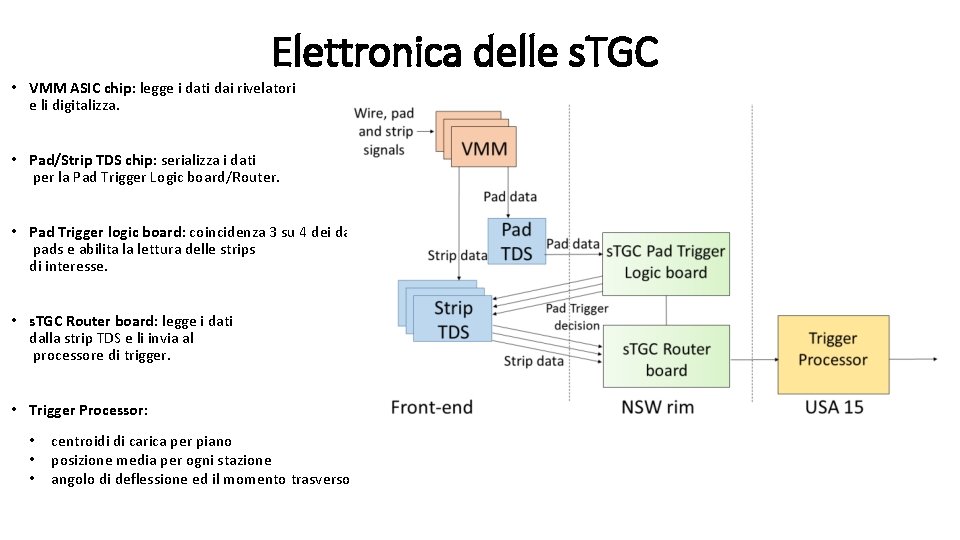

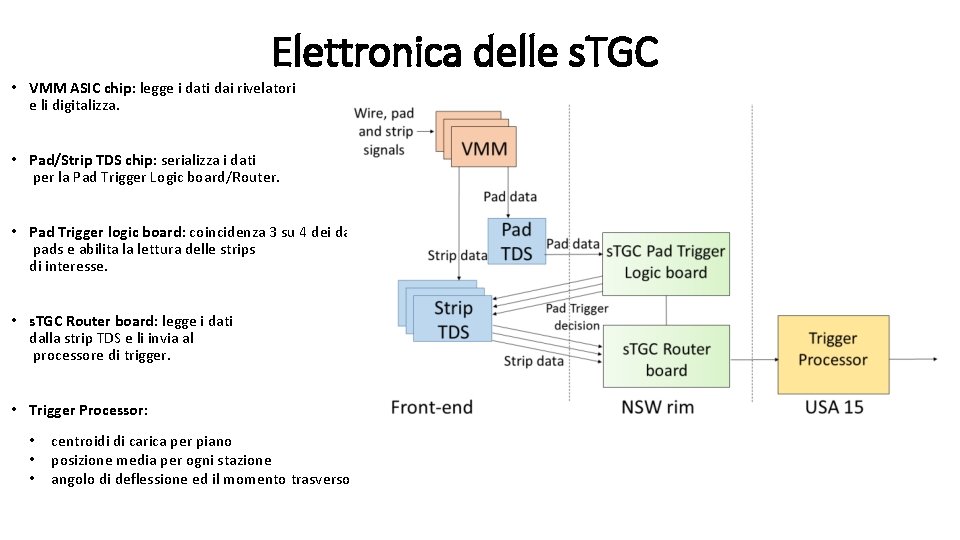

Elettronica delle s. TGC • VMM ASIC chip: legge i dati dai rivelatori e li digitalizza. • Pad/Strip TDS chip: serializza i dati per la Pad Trigger Logic board/Router. • Pad Trigger logic board: coincidenza 3 su 4 dei dati delle pads e abilita la lettura delle strips di interesse. • s. TGC Router board: legge i dati dalla strip TDS e li invia al processore di trigger. • Trigger Processor: • • • centroidi di carica per piano posizione media per ogni stazione angolo di deflessione ed il momento trasverso

Pad Trigger Logic board Situata sul bordo della NSW • 1 pad trigger board per settore 32 in totale OUTPUTs: 168 outputs: 24 Twin. Ax con 7 linee seriali. INPUTs: 24 inputs: 6 Twin. Ax da 4 linee seriali per Twin. Ax. Altri IO per il monitoring, configurazione e slow control. PRINCIPALE COMPONENTE: • Xilinx Kintex-7 FPGA 24 MINISAS 6 MINISAS

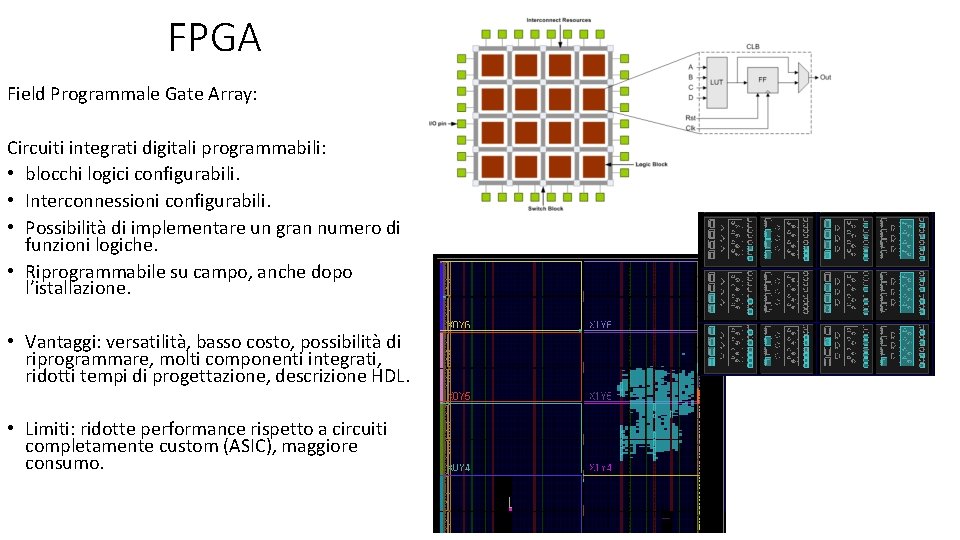

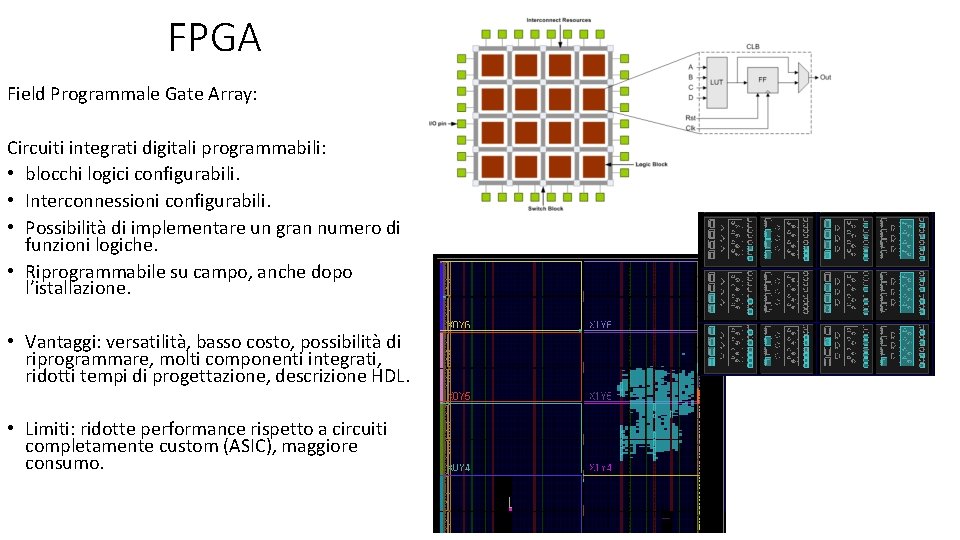

FPGA Field Programmale Gate Array: Circuiti integrati digitali programmabili: • blocchi logici configurabili. • Interconnessioni configurabili. • Possibilità di implementare un gran numero di funzioni logiche. • Riprogrammabile su campo, anche dopo l’istallazione. • Vantaggi: versatilità, basso costo, possibilità di riprogrammare, molti componenti integrati, ridotti tempi di progettazione, descrizione HDL. • Limiti: ridotte performance rispetto a circuiti completamente custom (ASIC), maggiore consumo.

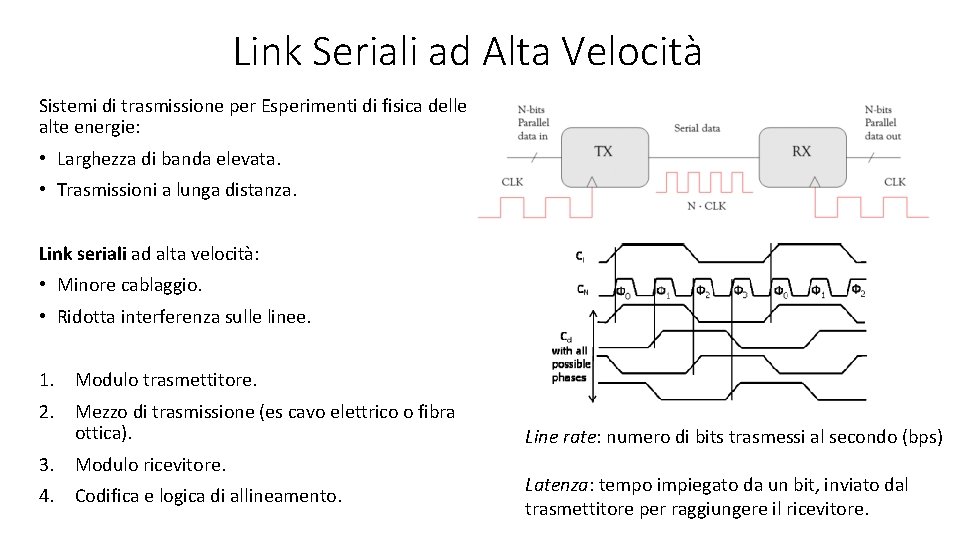

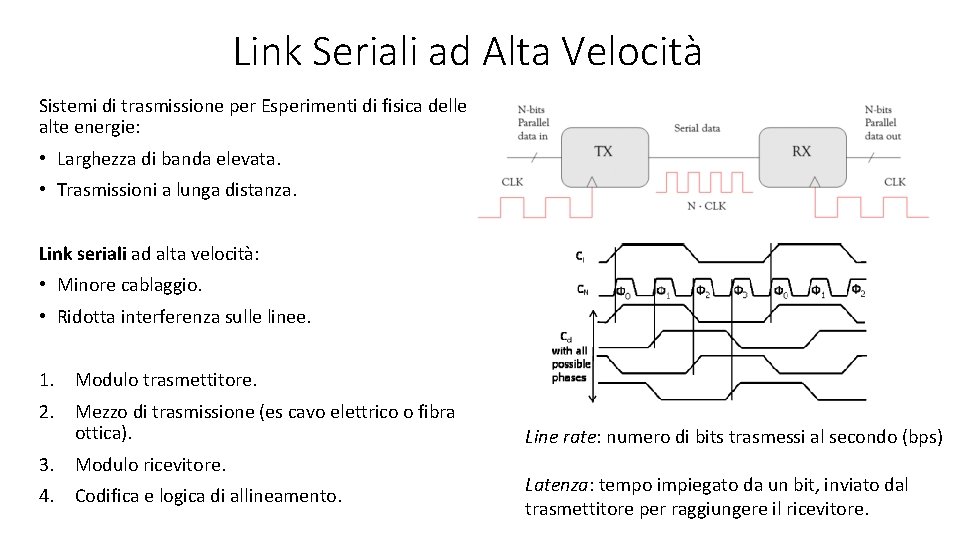

Link Seriali ad Alta Velocità Sistemi di trasmissione per Esperimenti di fisica delle alte energie: • Larghezza di banda elevata. • Trasmissioni a lunga distanza. Link seriali ad alta velocità: • Minore cablaggio. • Ridotta interferenza sulle linee. 1. Modulo trasmettitore. 2. Mezzo di trasmissione (es cavo elettrico o fibra ottica). 3. Modulo ricevitore. 4. Codifica e logica di allineamento. Line rate: numero di bits trasmessi al secondo (bps) Latenza: tempo impiegato da un bit, inviato dal trasmettitore per raggiungere il ricevitore.

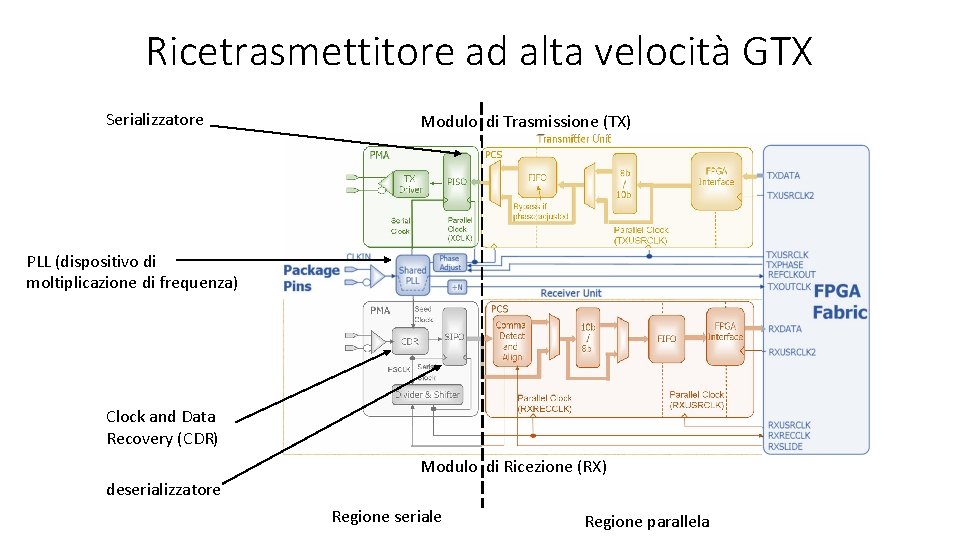

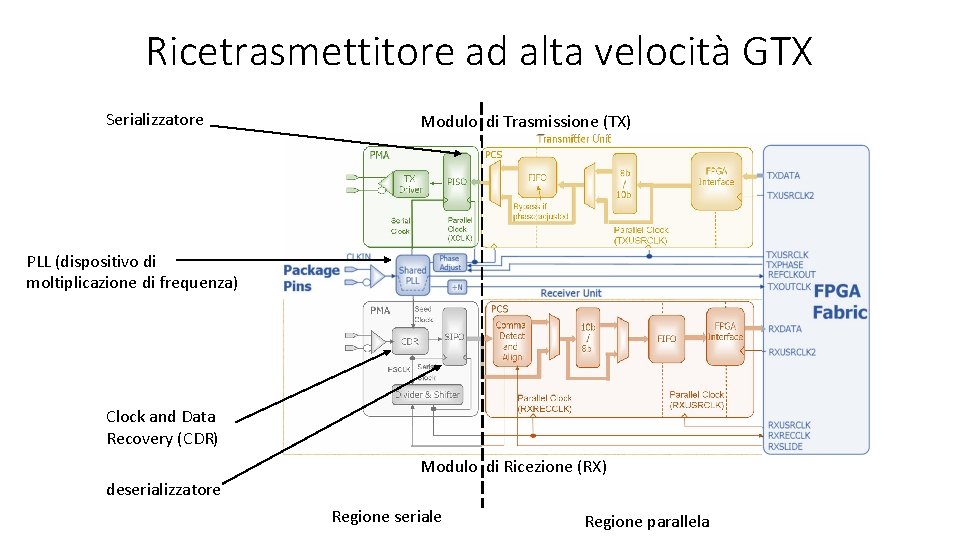

Ricetrasmettitore ad alta velocità GTX Serializzatore Modulo di Trasmissione (TX) PLL (dispositivo di moltiplicazione di frequenza) Clock and Data Recovery (CDR) Modulo di Ricezione (RX) deserializzatore Regione seriale Regione parallela

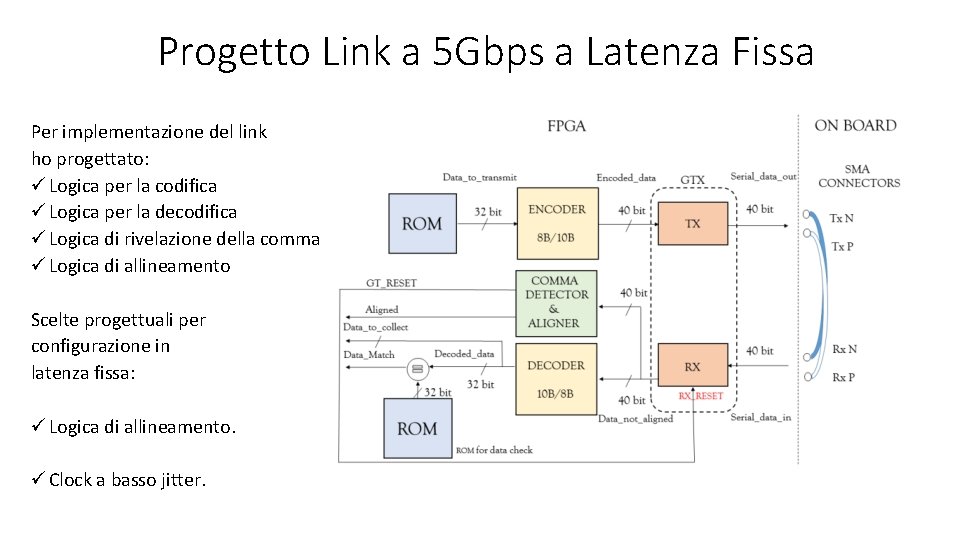

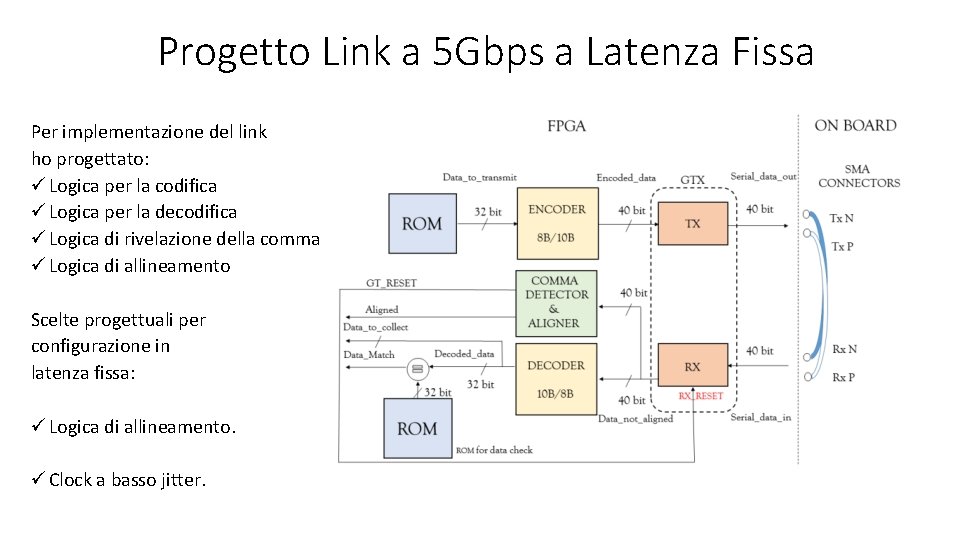

Progetto Link a 5 Gbps a Latenza Fissa Per implementazione del link ho progettato: ü Logica per la codifica ü Logica per la decodifica ü Logica di rivelazione della comma ü Logica di allineamento Scelte progettuali per configurazione in latenza fissa: ü Logica di allineamento. ü Clock a basso jitter.

MISURE E RISULTATI

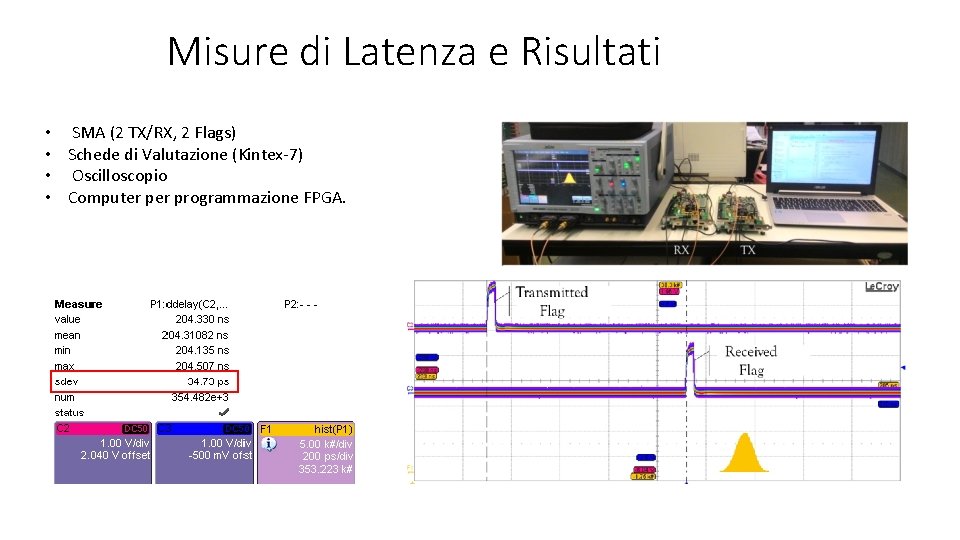

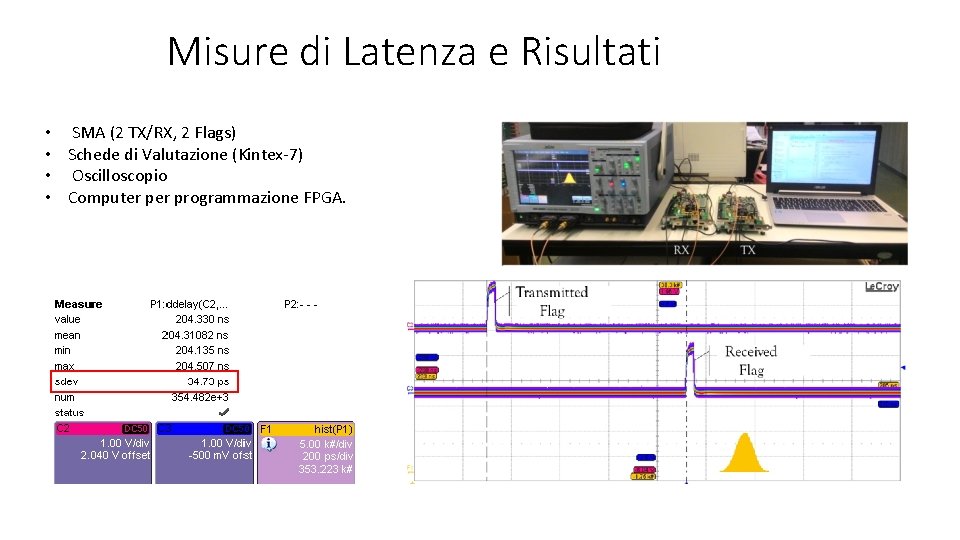

Misure di Latenza e Risultati • • SMA (2 TX/RX, 2 Flags) Schede di Valutazione (Kintex-7) Oscilloscopio Computer programmazione FPGA.

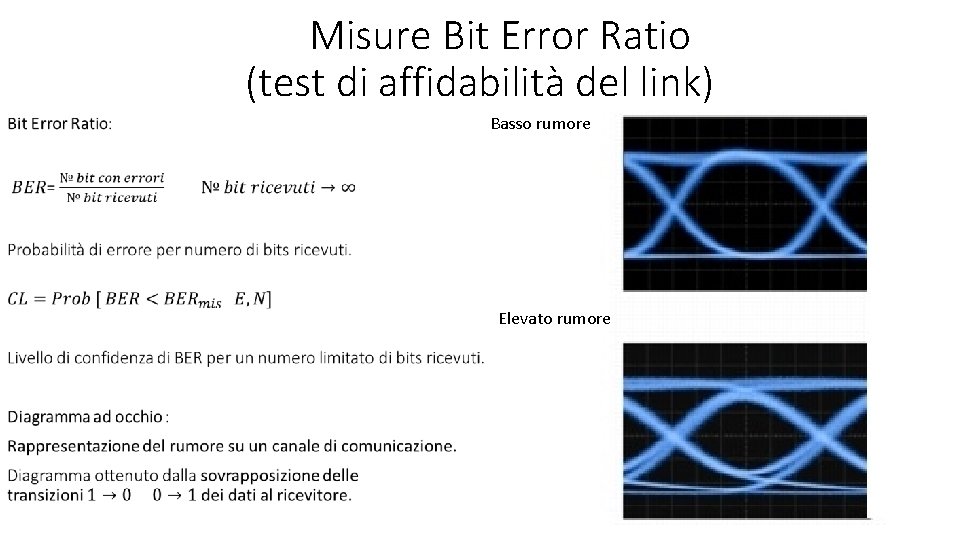

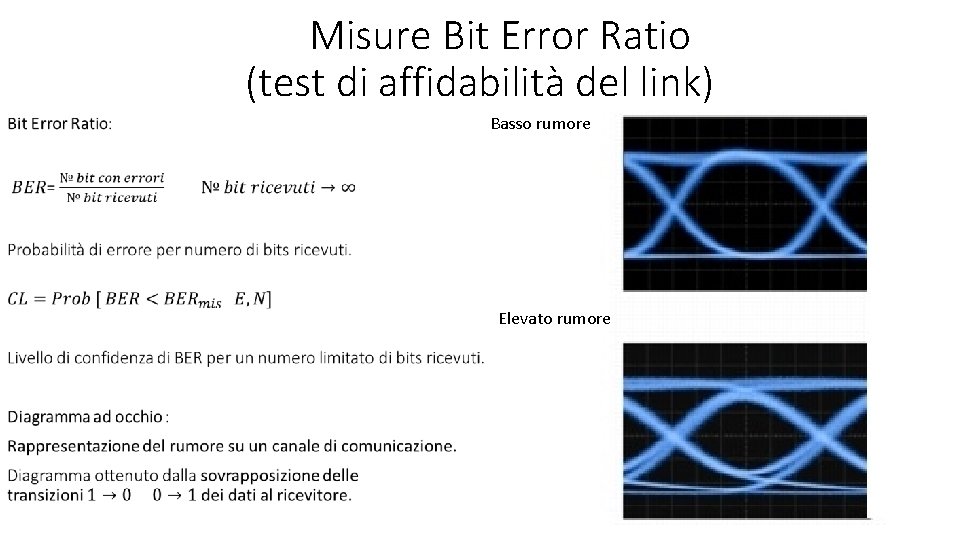

Misure Bit Error Ratio (test di affidabilità del link) • Basso rumore Elevato rumore

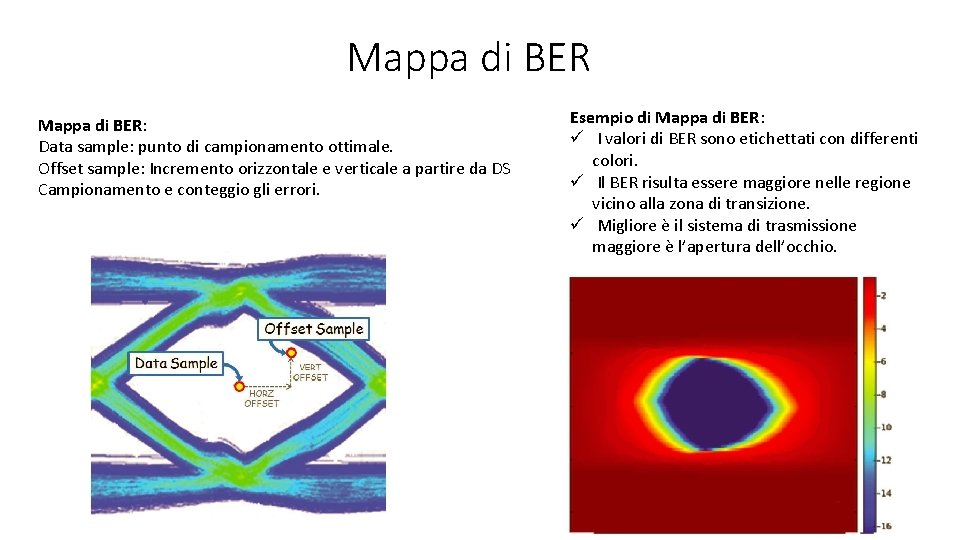

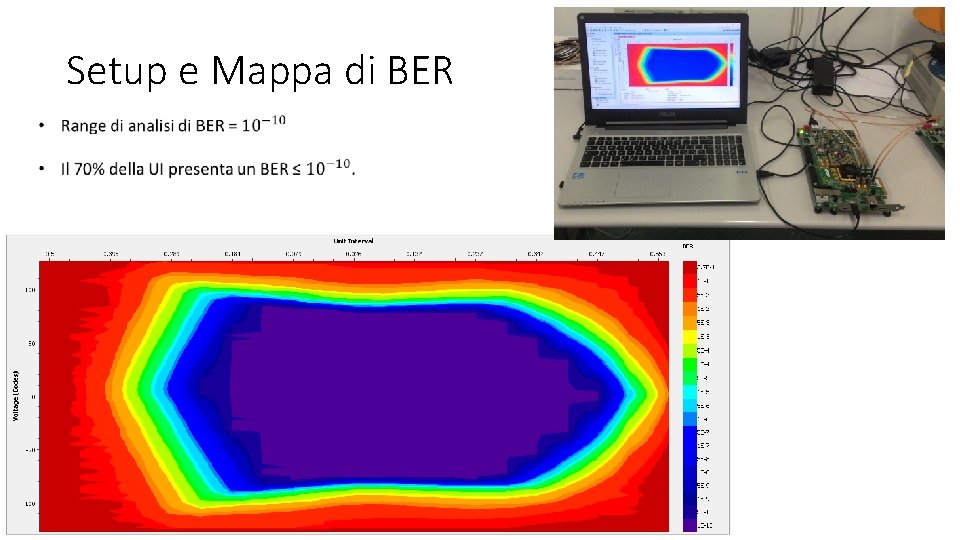

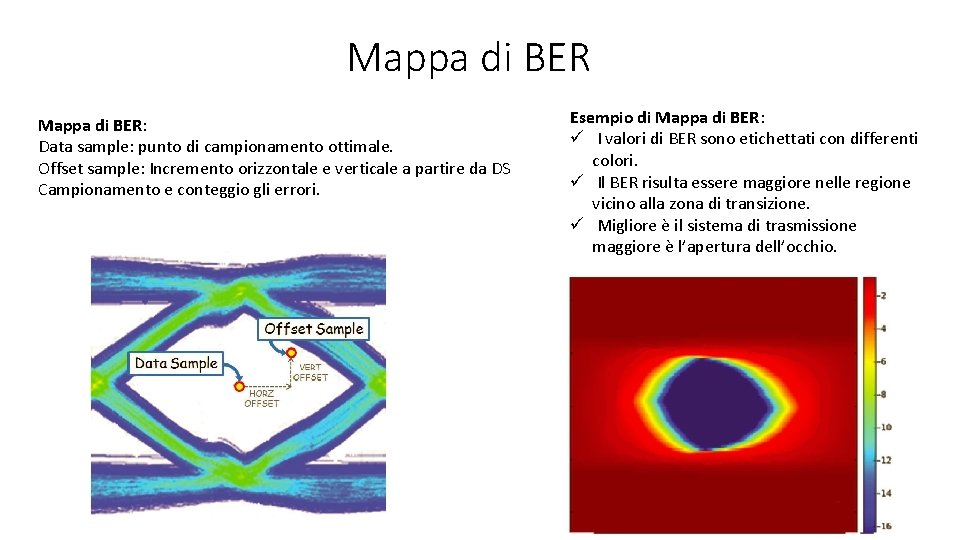

Mappa di BER: Data sample: punto di campionamento ottimale. Offset sample: Incremento orizzontale e verticale a partire da DS Campionamento e conteggio gli errori. Esempio di Mappa di BER: ü I valori di BER sono etichettati con differenti colori. ü Il BER risulta essere maggiore nelle regione vicino alla zona di transizione. ü Migliore è il sistema di trasmissione maggiore è l’apertura dell’occhio.

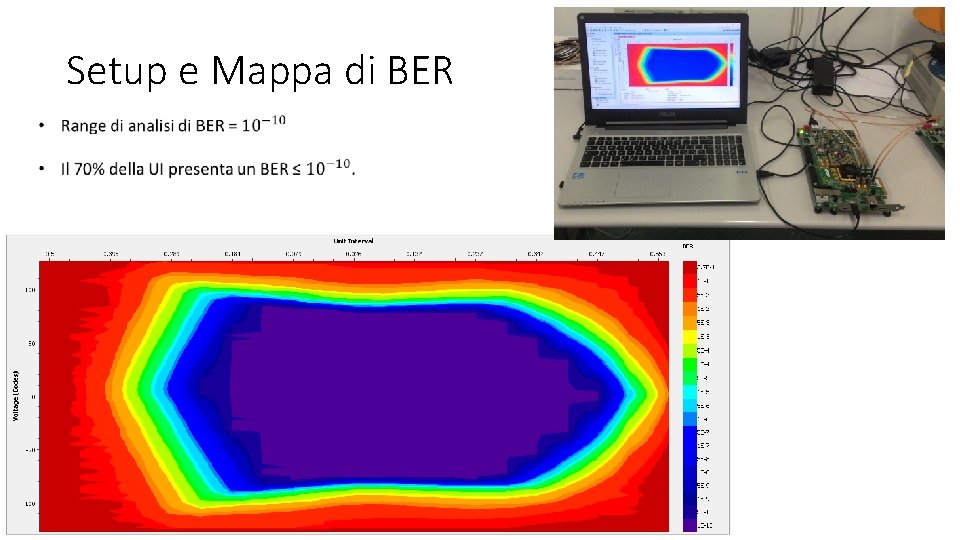

Setup e Mappa di BER

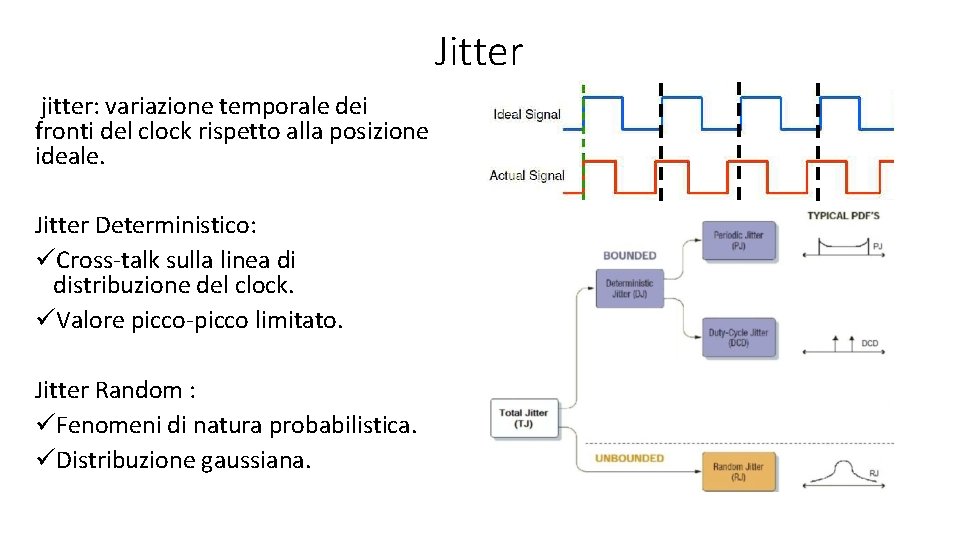

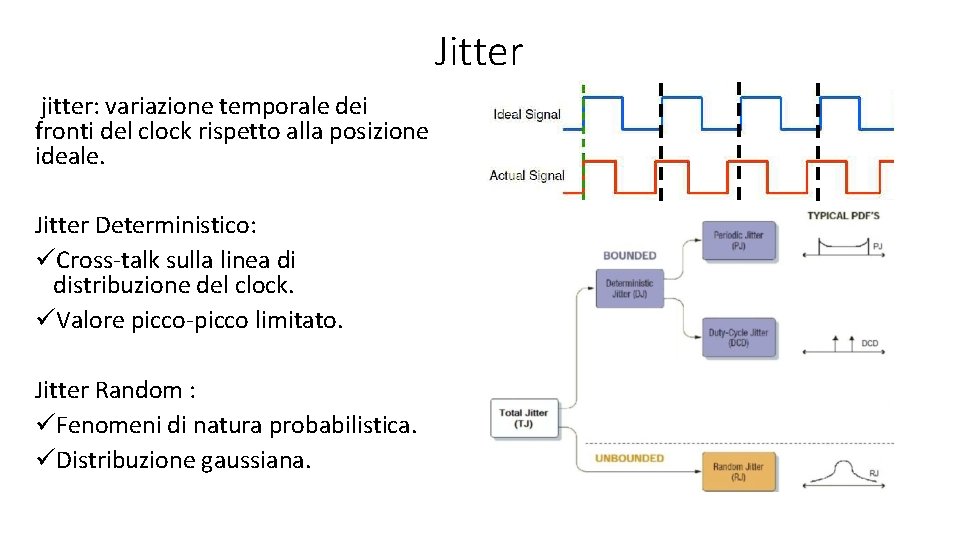

Jitter jitter: variazione temporale dei fronti del clock rispetto alla posizione ideale. Jitter Deterministico: üCross-talk sulla linea di distribuzione del clock. üValore picco-picco limitato. Jitter Random : üFenomeni di natura probabilistica. üDistribuzione gaussiana.

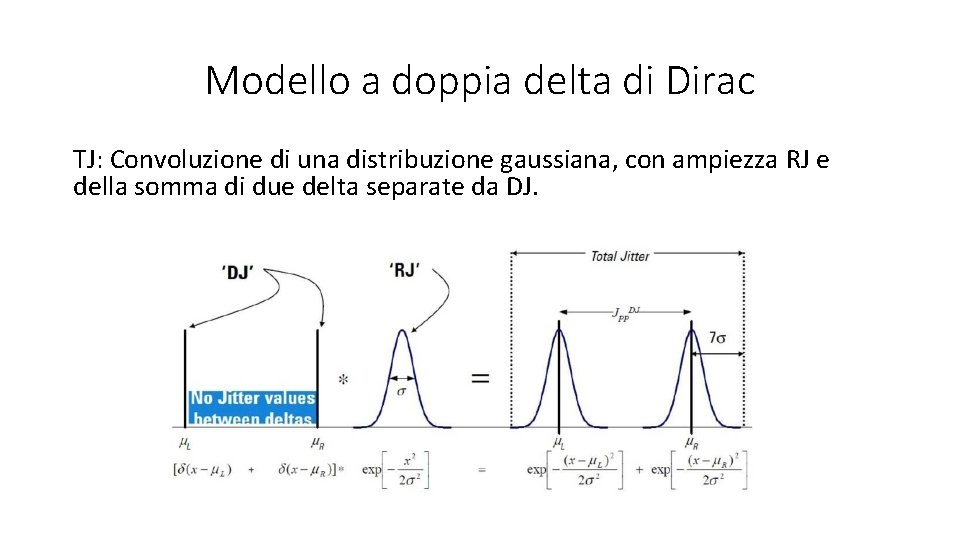

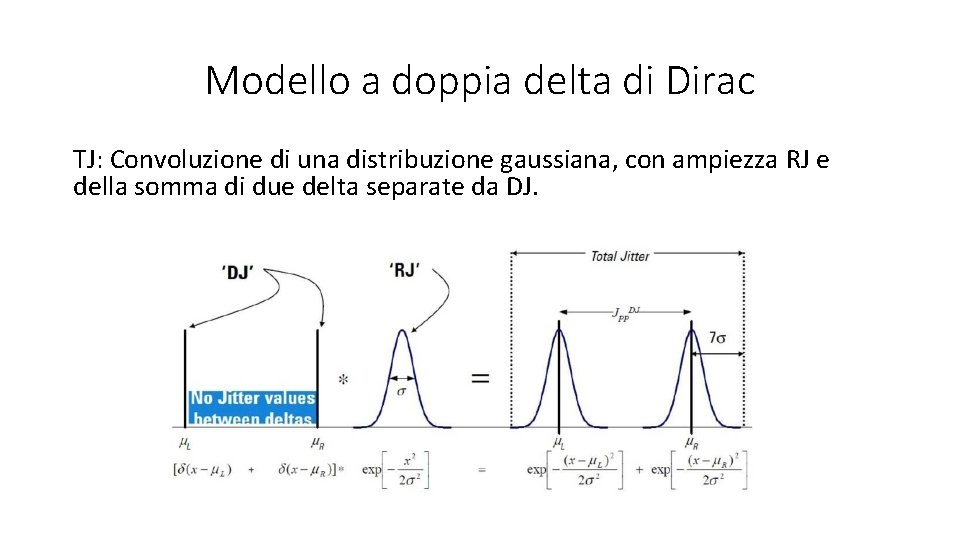

Modello a doppia delta di Dirac TJ: Convoluzione di una distribuzione gaussiana, con ampiezza RJ e della somma di due delta separate da DJ.

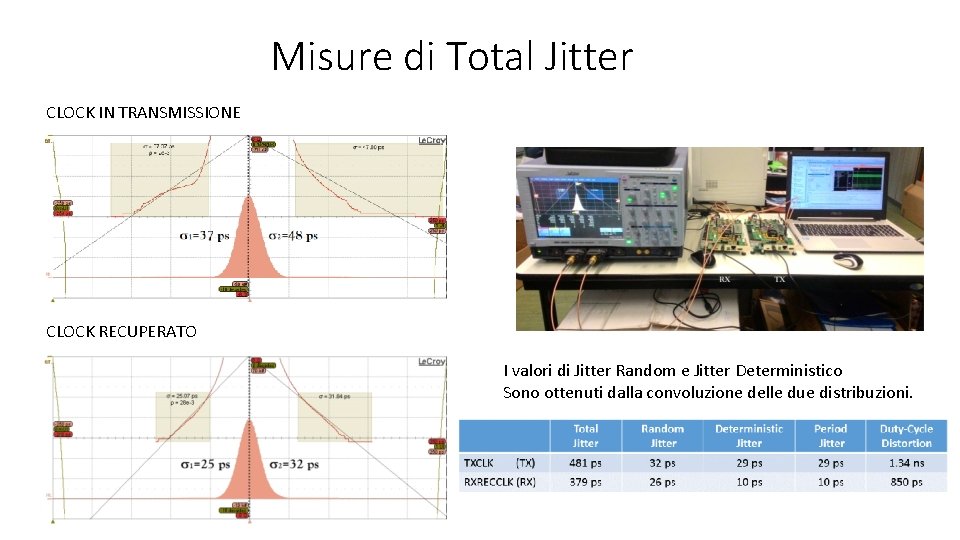

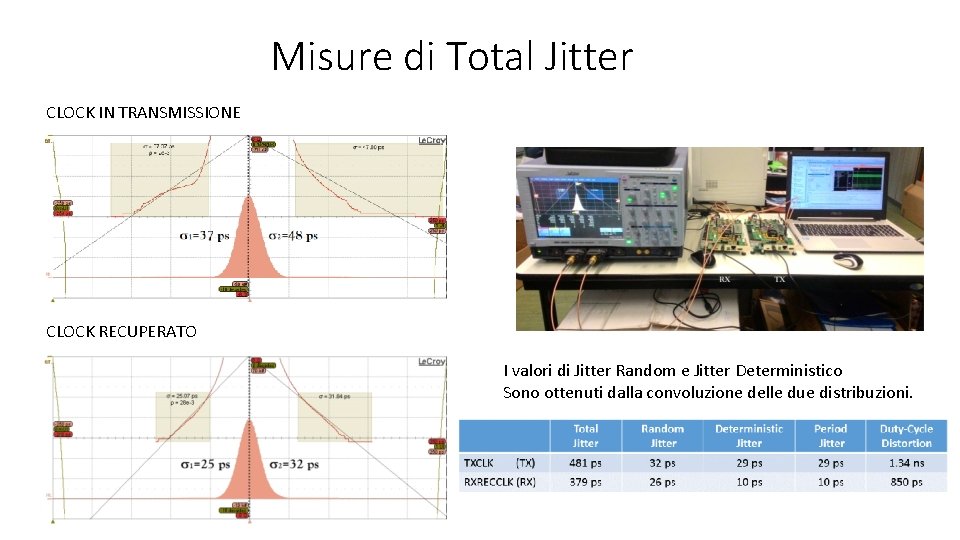

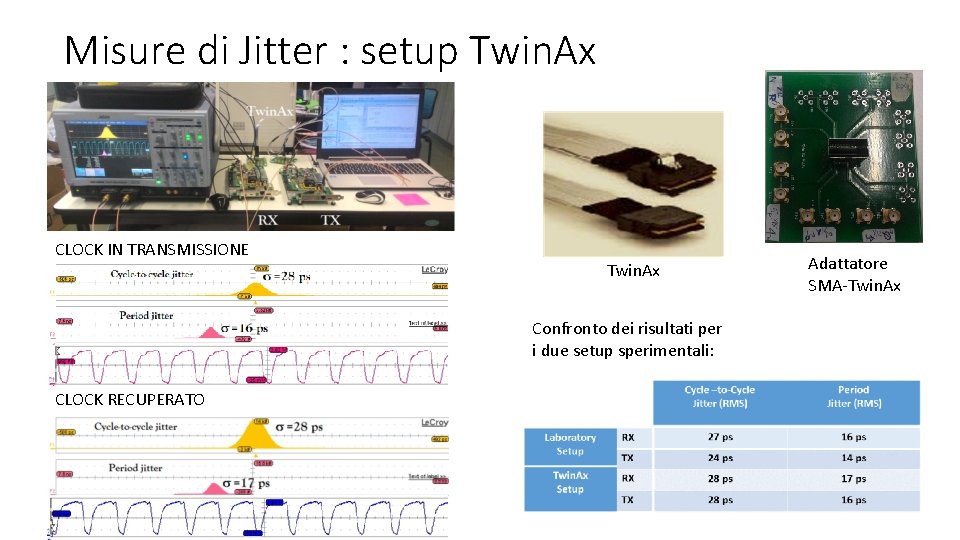

Misure di Total Jitter CLOCK IN TRANSMISSIONE CLOCK RECUPERATO I valori di Jitter Random e Jitter Deterministico Sono ottenuti dalla convoluzione delle due distribuzioni.

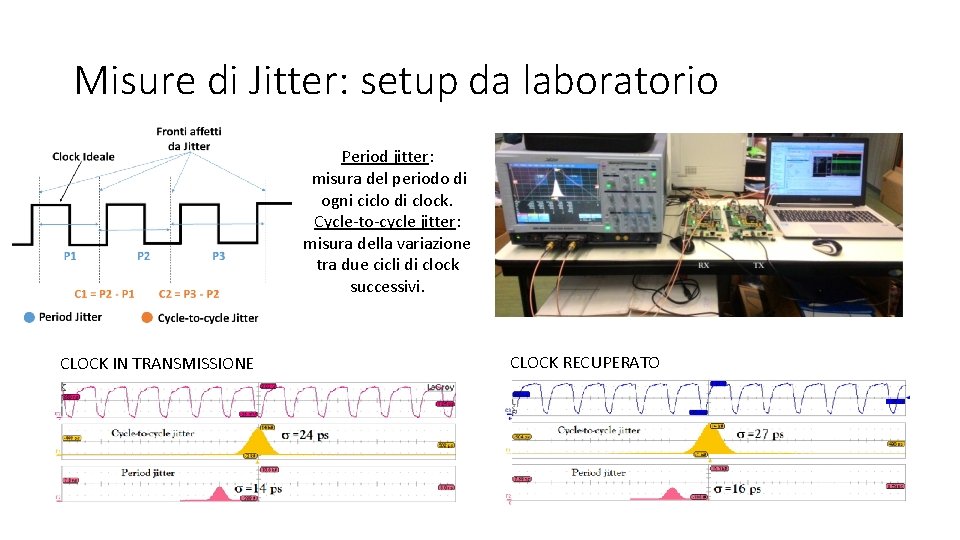

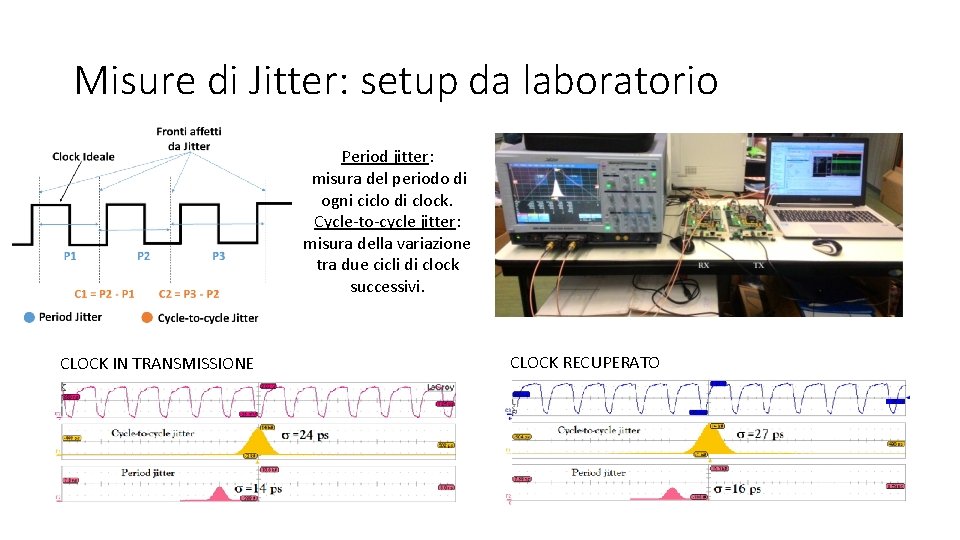

Misure di Jitter: setup da laboratorio Period jitter: misura del periodo di ogni ciclo di clock. Cycle-to-cycle jitter: misura della variazione tra due cicli di clock successivi. CLOCK IN TRANSMISSIONE CLOCK RECUPERATO

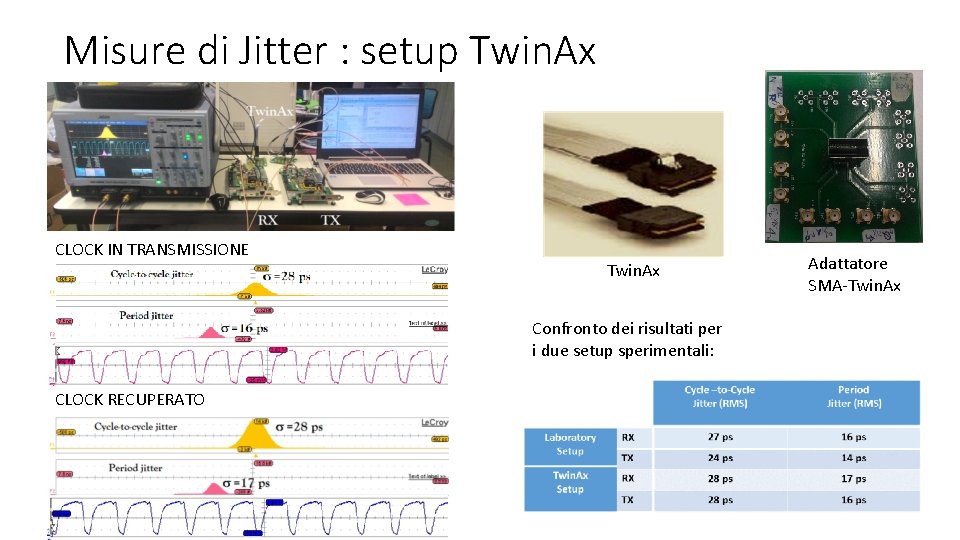

Misure di Jitter : setup Twin. Ax CLOCK IN TRANSMISSIONE Twin. Ax Confronto dei risultati per i due setup sperimentali: CLOCK RECUPERATO Adattatore SMA-Twin. Ax

Conclusione • Ho effettuato uno studio di fattibilità di un link a 5 Gbps in configurazione a latenza per il modulo ricevitore della Pad Trigger Logic board. • Ho progettato e testato la logica di codifica, decodifica, rivelazione della comma e logica di allineamento. • Ho effettuato misure dell’affidabilità del link: Latenza, jitter, Bit Error Rate. • Ho valutato le condizioni di jitter per trasmissione su Twin. Ax