UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO

- Slides: 29

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA CMP 237 – Arquitetura e Organização de Processadores Xtensa LX Processador Configurável Tensilica Emilena Specht 2006/1 jun. 2006 Xtensa LX 1

Introdução • Sistemas embarcados: – potência – energia – área – desempenho jun. 2006 Xtensa LX 2

Introdução • Sistemas embarcados: – aplicações conhecidas – propósitos diferentes – time-to-market • Solução: ASIPs (Application Specific Instruction Processors) jun. 2006 Xtensa LX 3

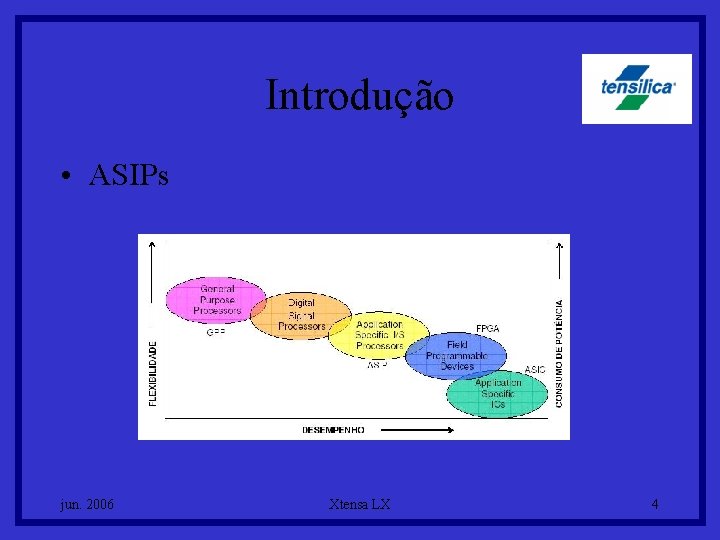

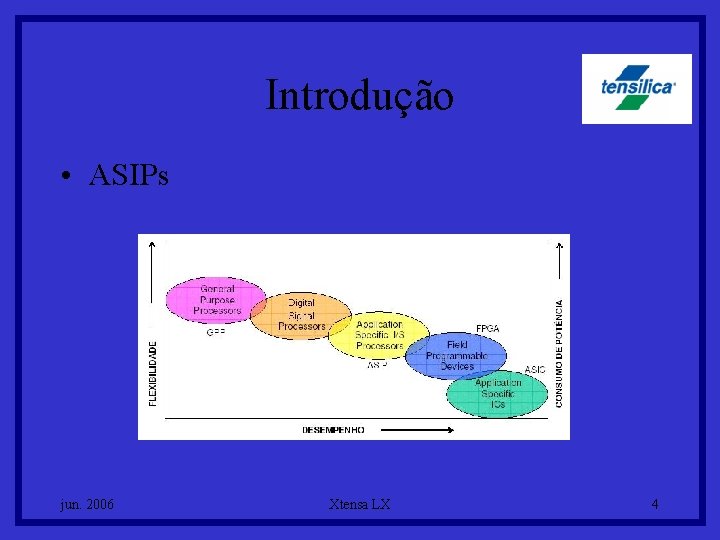

Introdução • ASIPs jun. 2006 Xtensa LX 4

Introdução • Xtensa LX • • • jun. 2006 ASIP da Tensilica Inc. Lançado em 2004 Sintetizável Extensível Configurável Xtensa LX 5

Introdução • Xtensa LX • • • jun. 2006 ASIP da Tensilica Inc. Lançado em 2004 Sintetizável Extensível Configurável =/= Reconfigurável Xtensa LX 6

Introdução • Xtensa LX • • jun. 2006 Aplicações DSP Data-intensive Controle Low-power Xtensa LX 7

Sumário • • • Overview Funções Básicas Funções Configuráveis Funções Opcionais Funções Estendidas Ambientes jun. 2006 Xtensa LX 8

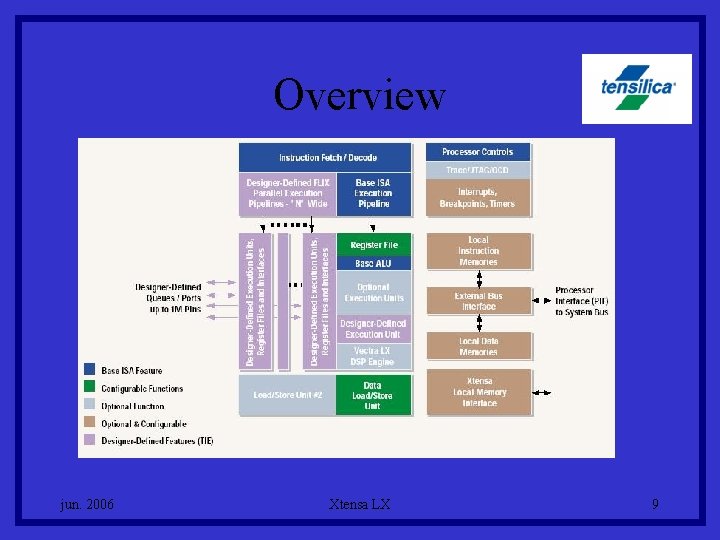

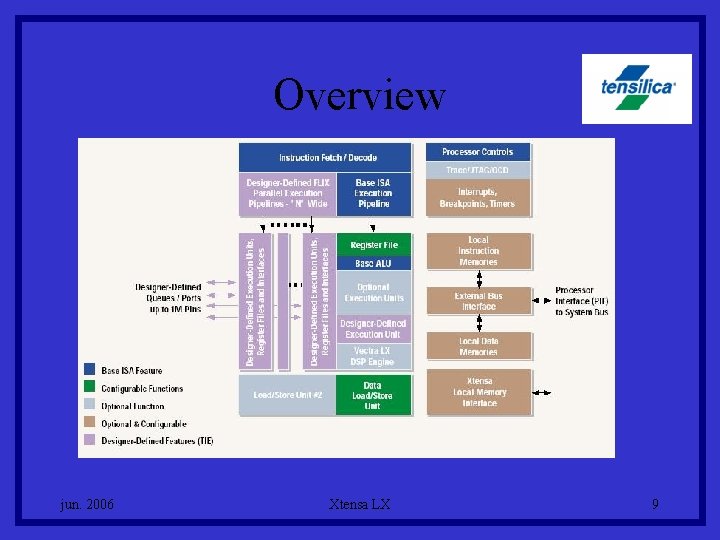

Overview jun. 2006 Xtensa LX 9

Funções Básicas • • RISC 32 -bits ULA 32 -bits Pipeline de 5 ou 7 estágios Conjunto básico de 80 instruções – Instruções convencionais RISC – Compare-and-branch – Tamanho da instrução: 16 -bits e 24 -bits jun. 2006 Xtensa LX 10

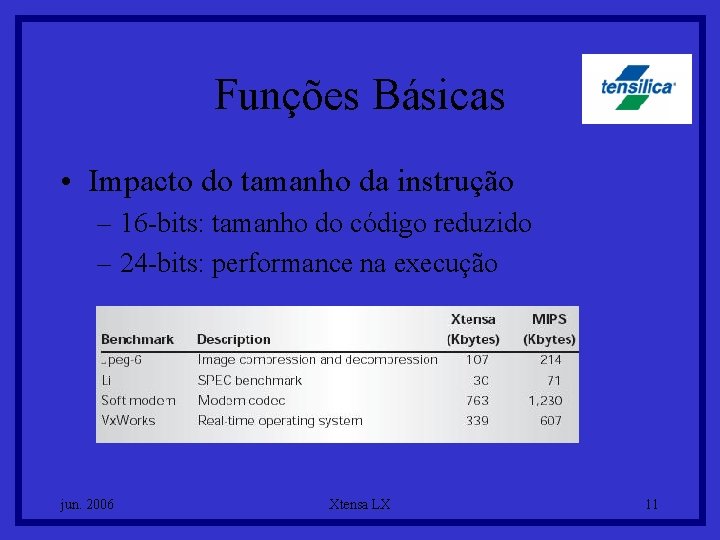

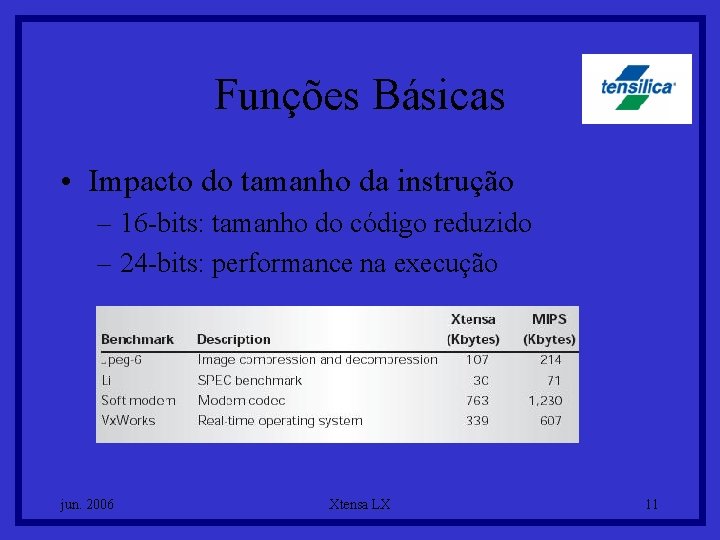

Funções Básicas • Impacto do tamanho da instrução – 16 -bits: tamanho do código reduzido – 24 -bits: performance na execução jun. 2006 Xtensa LX 11

Funções Básicas • Formato das instruções jun. 2006 Xtensa LX 12

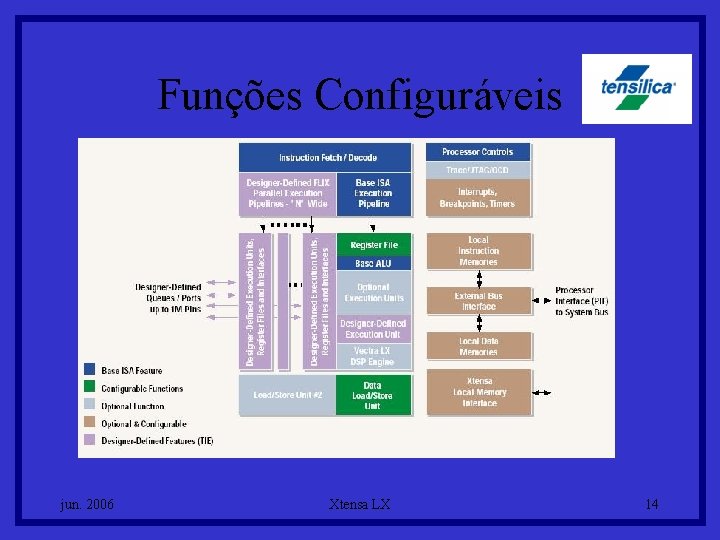

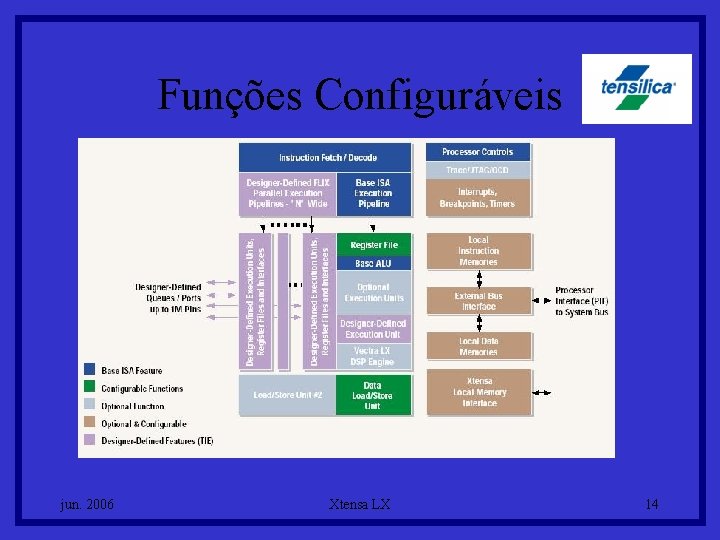

Funções Configuráveis • Banco de registradores – Máx 64 para propósito geral – Máx 6 para propósitos especiais • Unidade de load/store – Ciclos para acesso à memória jun. 2006 Xtensa LX 13

Funções Configuráveis jun. 2006 Xtensa LX 14

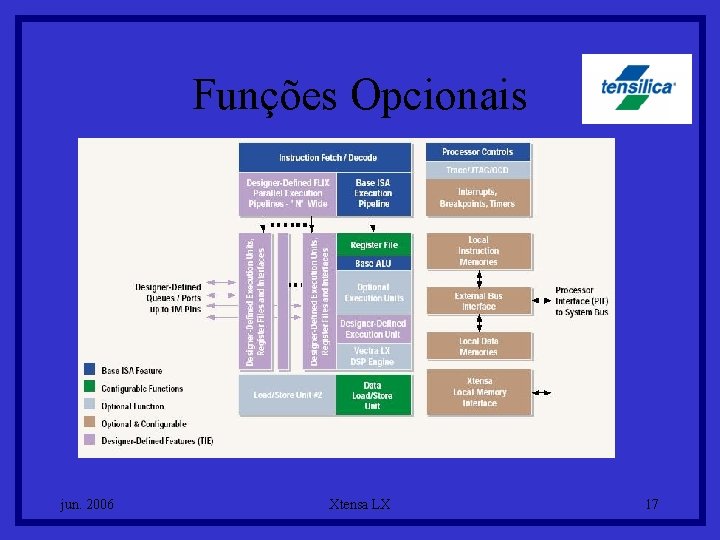

Funções Opcionais • Multiplicador 32 -bits • Unidade de ponto-flutuante • Instruções opcionais – MAC 16 -bits – Vectra LX DSP Engine jun. 2006 Xtensa LX 15

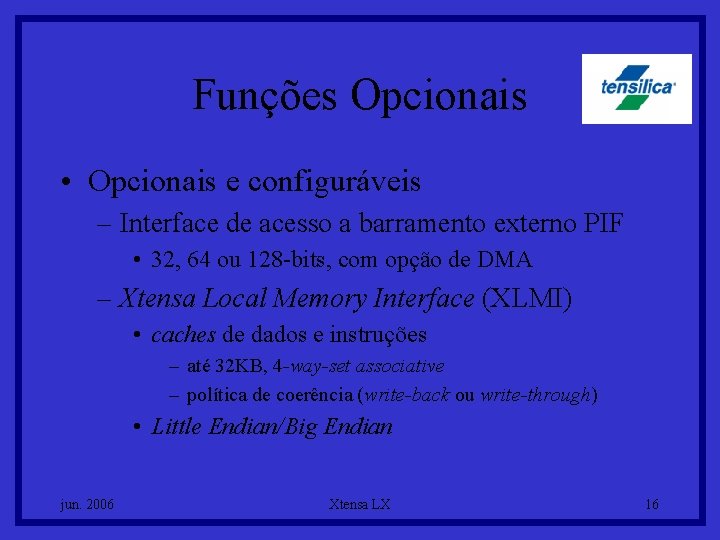

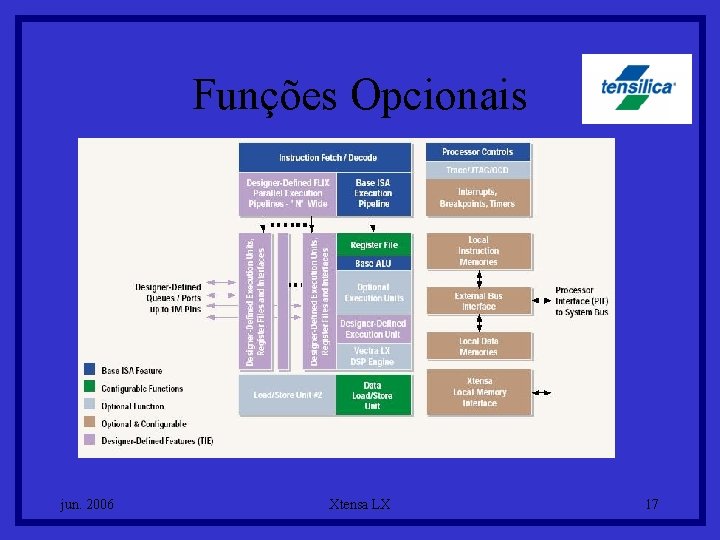

Funções Opcionais • Opcionais e configuráveis – Interface de acesso a barramento externo PIF • 32, 64 ou 128 -bits, com opção de DMA – Xtensa Local Memory Interface (XLMI) • caches de dados e instruções – até 32 KB, 4 -way-set associative – política de coerência (write-back ou write-through) • Little Endian/Big Endian jun. 2006 Xtensa LX 16

Funções Opcionais jun. 2006 Xtensa LX 17

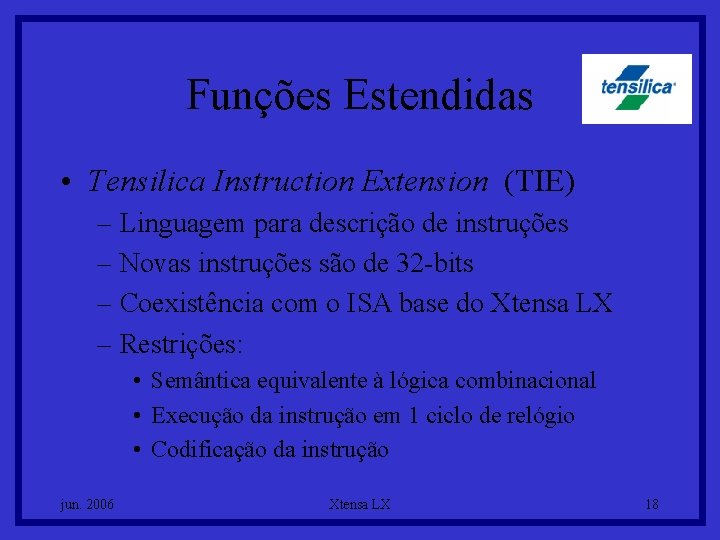

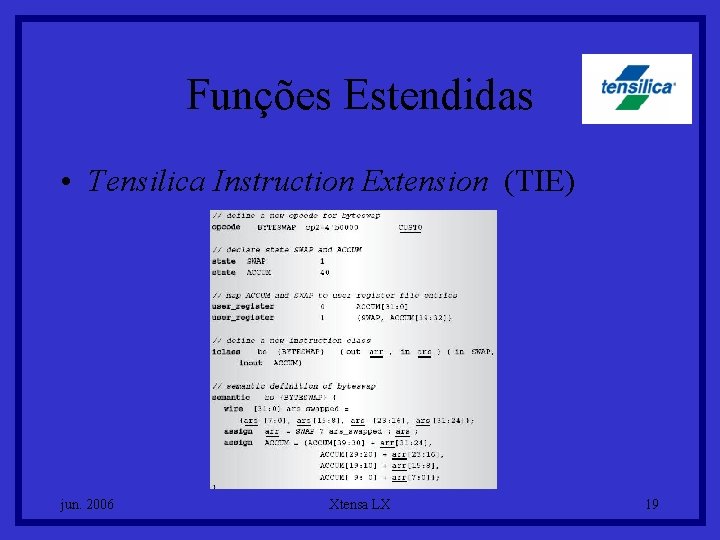

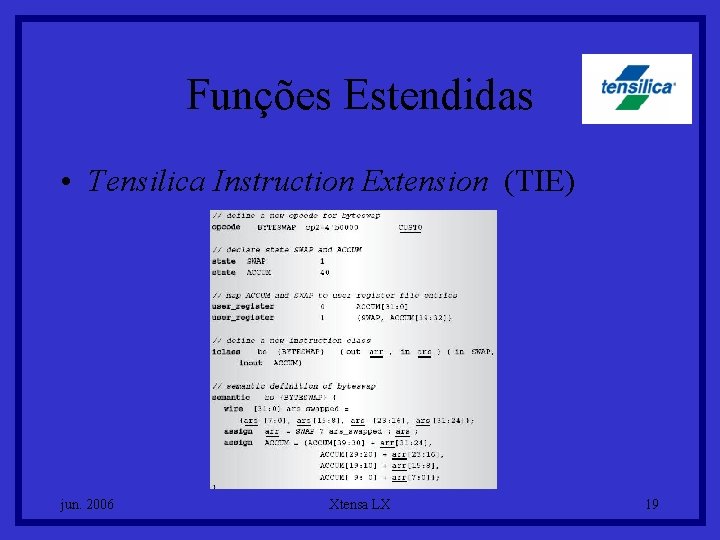

Funções Estendidas • Tensilica Instruction Extension (TIE) – Linguagem para descrição de instruções – Novas instruções são de 32 -bits – Coexistência com o ISA base do Xtensa LX – Restrições: • Semântica equivalente à lógica combinacional • Execução da instrução em 1 ciclo de relógio • Codificação da instrução jun. 2006 Xtensa LX 18

Funções Estendidas • Tensilica Instruction Extension (TIE) jun. 2006 Xtensa LX 19

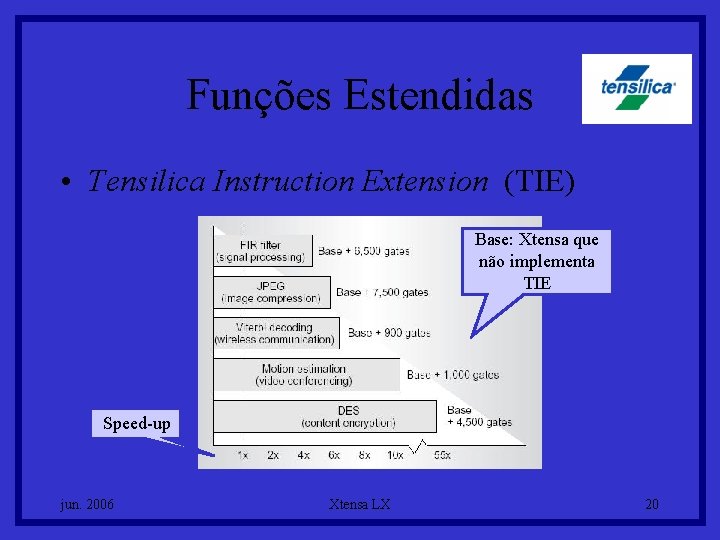

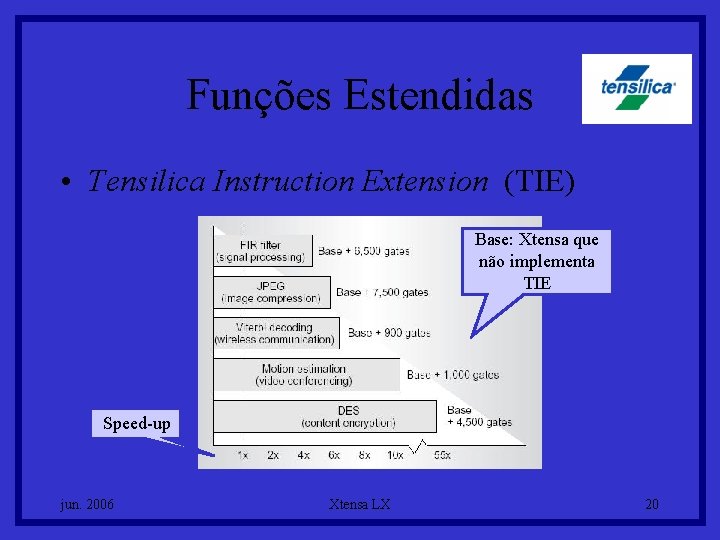

Funções Estendidas • Tensilica Instruction Extension (TIE) Base: Xtensa que não implementa TIE Speed-up jun. 2006 Xtensa LX 20

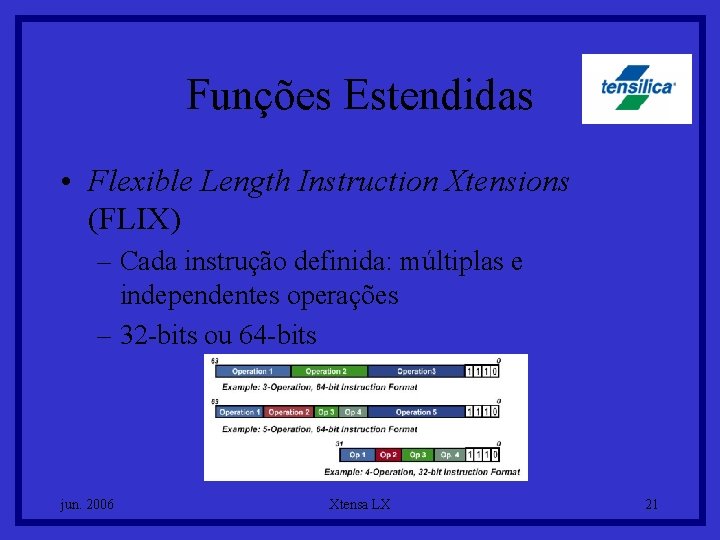

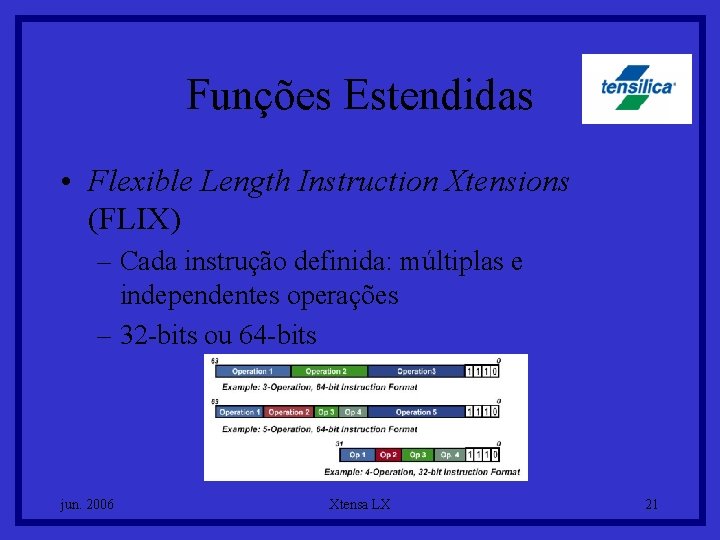

Funções Estendidas • Flexible Length Instruction Xtensions (FLIX) – Cada instrução definida: múltiplas e independentes operações – 32 -bits ou 64 -bits jun. 2006 Xtensa LX 21

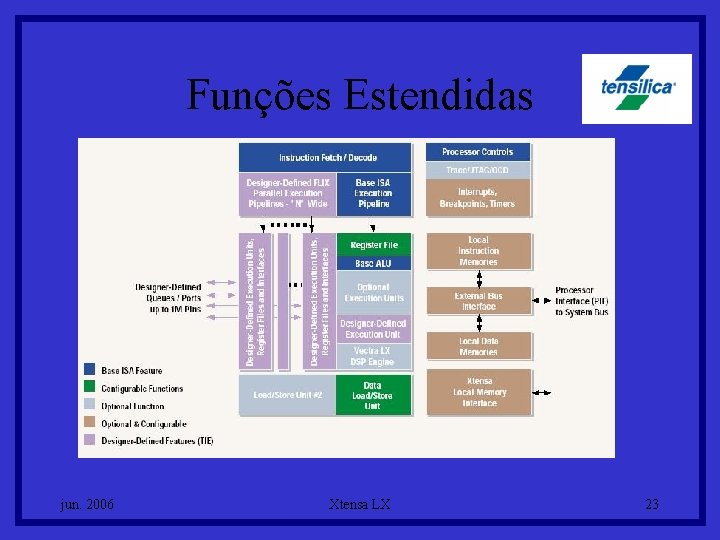

Funções Estendidas • Flexible Length Instruction Xtensions (FLIX) – paralelismo – 2 a 15 pipelines – Filas e portas de I/O para comunicação externa – Custo no controle: 2 mil gates jun. 2006 Xtensa LX 22

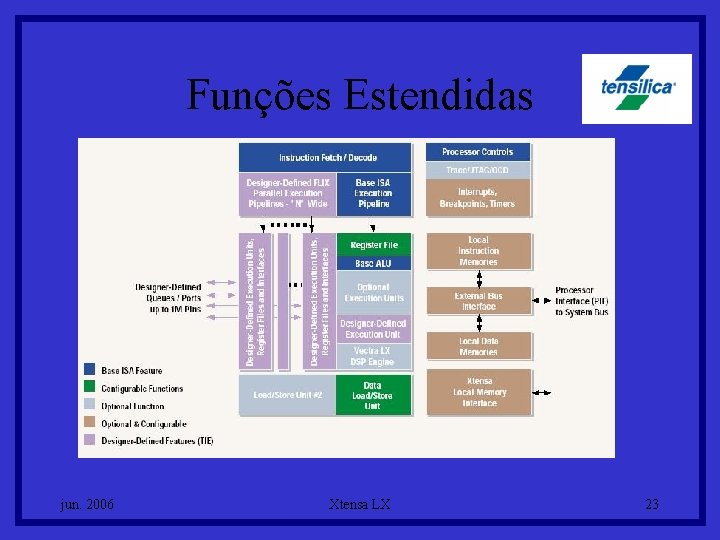

Funções Estendidas jun. 2006 Xtensa LX 23

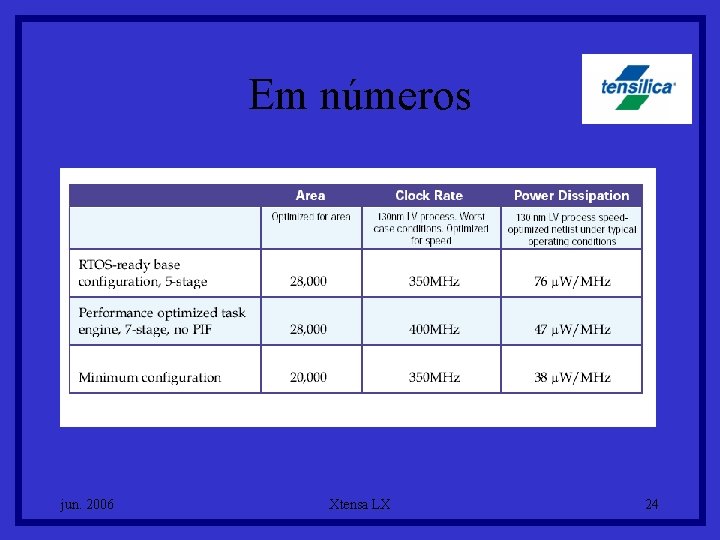

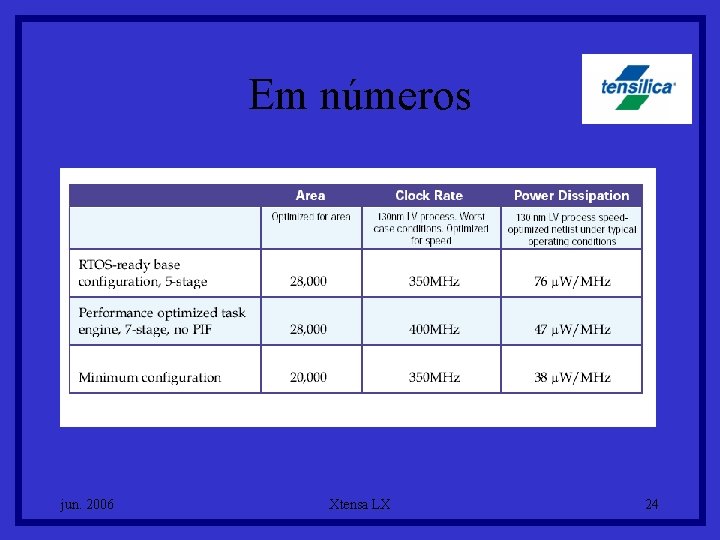

Em números jun. 2006 Xtensa LX 24

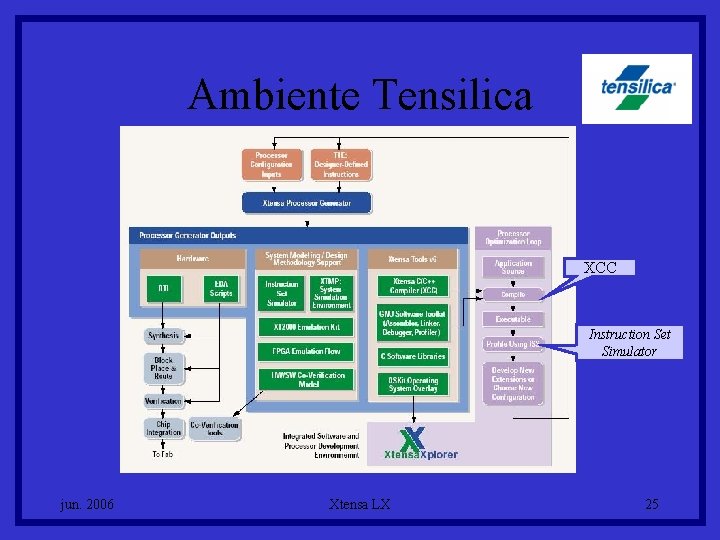

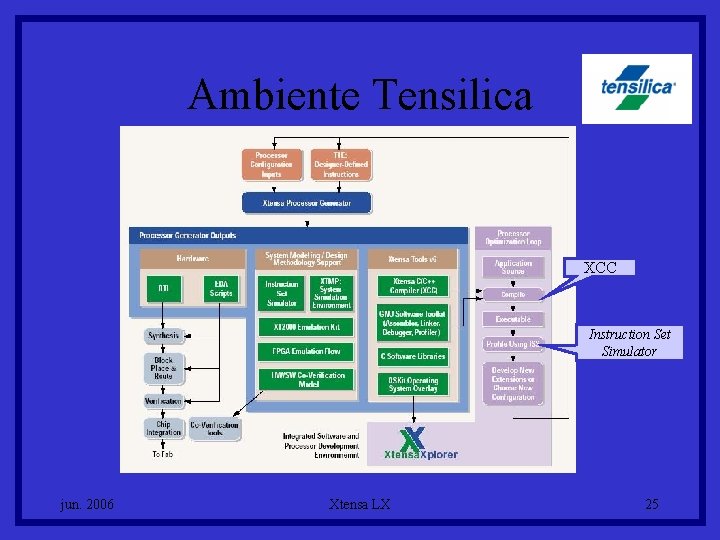

Ambiente Tensilica XCC Instruction Set Simulator jun. 2006 Xtensa LX 25

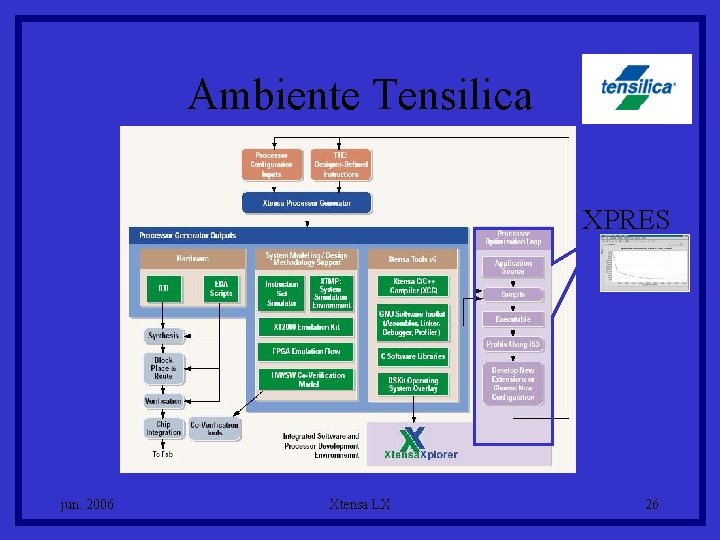

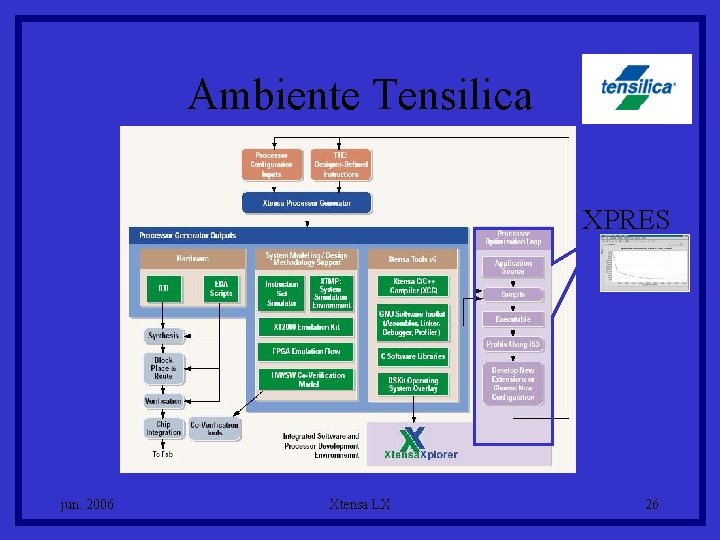

Ambiente Tensilica XPRES jun. 2006 Xtensa LX 26

Ambiente Tensilica • Custo: – Licenciamento para um único projeto: US$550. 000 (2004) – Inclui as ferramentas padrão de desenvolvimento – Compilador C/C++, Simulador do conjunto de instruções, compilador TIE e XPRES são cobrados separadamente jun. 2006 Xtensa LX 27

Referências • Tensilica Inc. Xtensa LX Product Brief. 2004. Disponível em http: //www. tensilica. com (2006). • Tensilica Inc. FLIX: Flast Relief for Performance. Hungry Embedded Applications. Tensilica White Paper. Fev, 2005. • Berkeley Design Technology, Inc. An Independent Analysis of the Tensilica Xtensa LX Processor with Vectra LX. 2005 • Gonzalez, Ricardo E. Xtensa: a Configurable and Extensible Processor. IEEE Micro, Mar-Abr 2000, p. 6070. • Eclipse home page. http: //www. eclipse. org/ jun. 2006 Xtensa LX 28

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA CMP 237 – Arquitetura e Organização de Processadores Xtensa LX Processador Configurável Tensilica Emilena Specht emilenas@inf. ufrgs. br 2006/1 jun. 2006 Xtensa LX 29