UNITIII GATELEVEL DESIGN Topics Logic gates and other

- Slides: 21

UNIT-III GATELEVEL DESIGN Topics • Logic gates and other complex gates • Switch logic • Alternate gate circuits • Time delays • Driving large capacitive loads • Wiring capacitances • Fan-in and fan-out, Choice of layers 6/3/2015 274

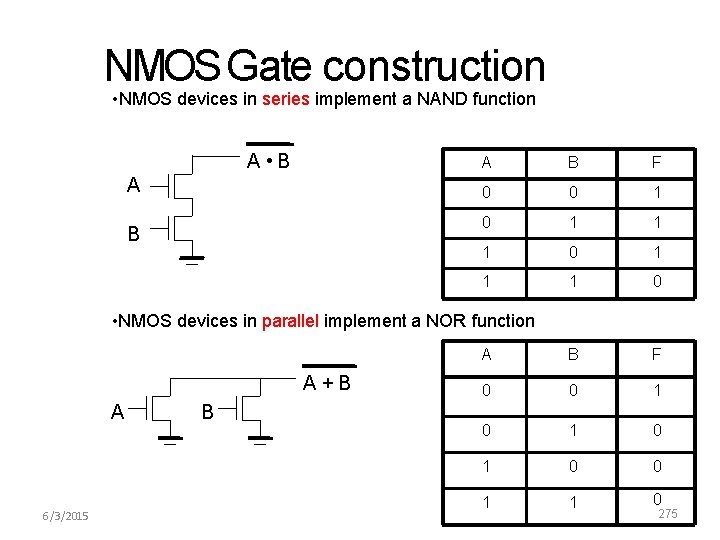

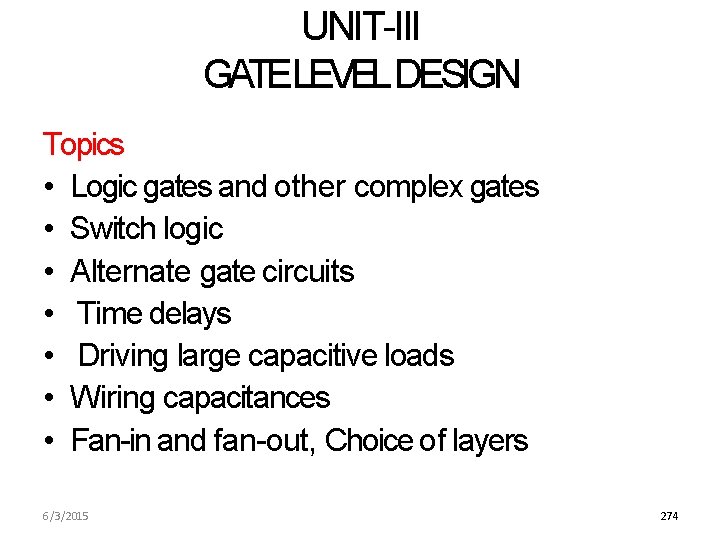

NMOS Gate construction • NMOS devices in series implement a NAND function A • B A B F 0 0 1 1 1 0 A B F 0 0 1 0 1 0 0 1 1 0 • NMOS devices in parallel implement a NOR function A+B A 6/3/2015 B 275

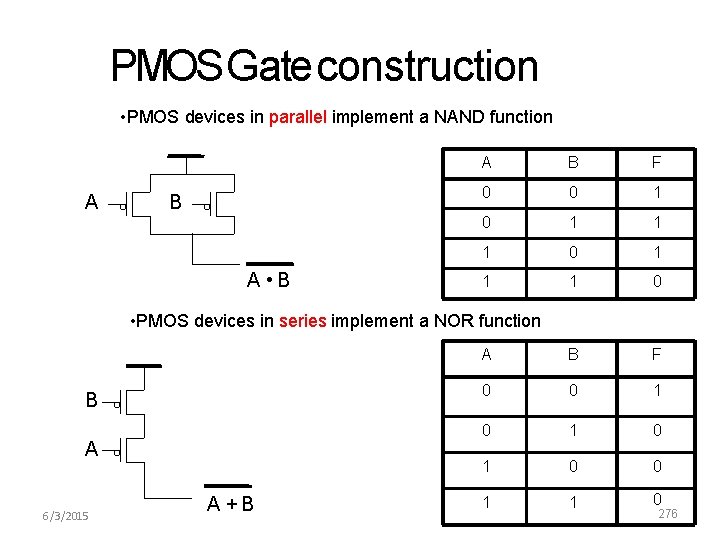

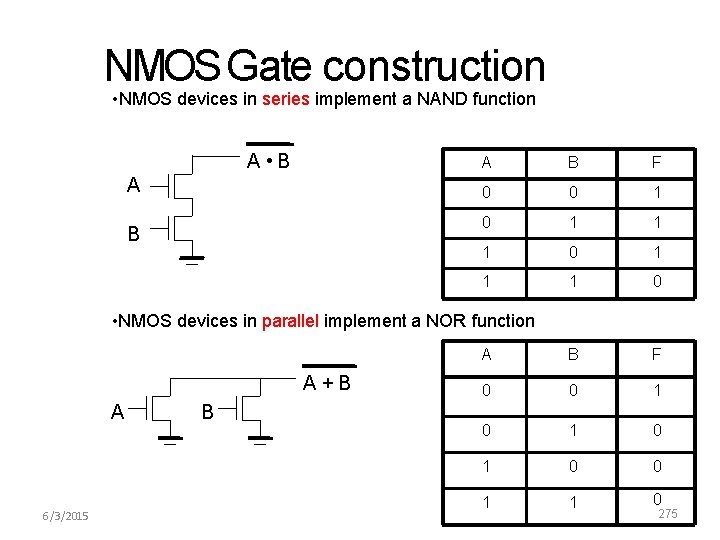

PMOS Gate construction • PMOS devices in parallel implement a NAND function A B A • B A B F 0 0 1 1 1 0 A B F 0 0 1 0 1 0 0 1 1 0 • PMOS devices in series implement a NOR function B A 6/3/2015 A +B 276

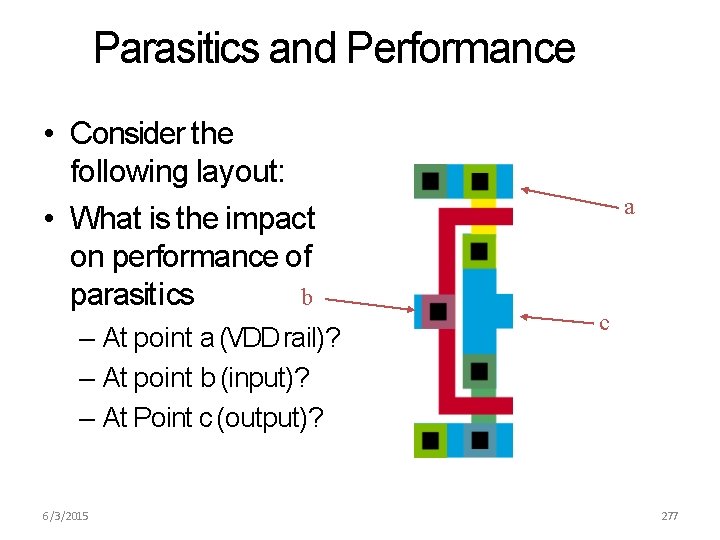

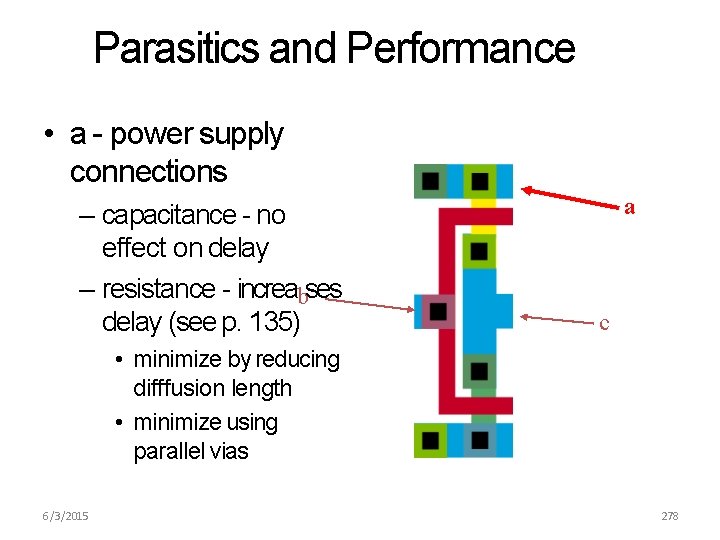

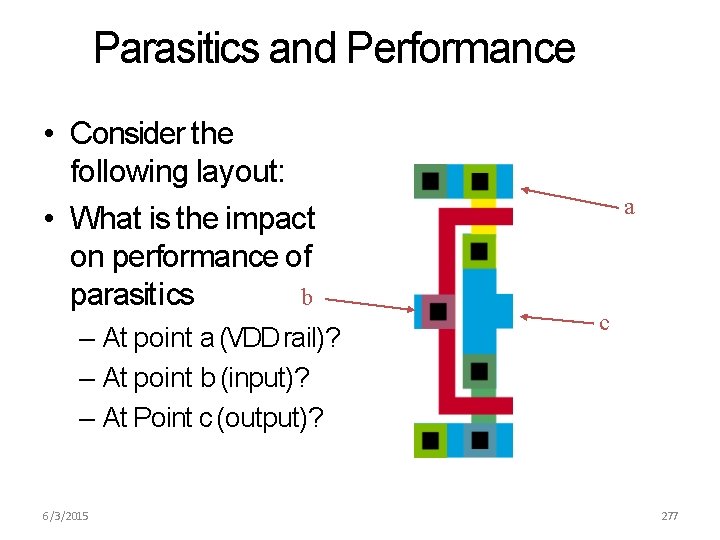

Parasitics and Performance • Consider the following layout: • What is the impact on performance of parasitics b – At point a (VDD rail)? – At point b (input)? – At Point c (output)? 6/3/2015 a c 277

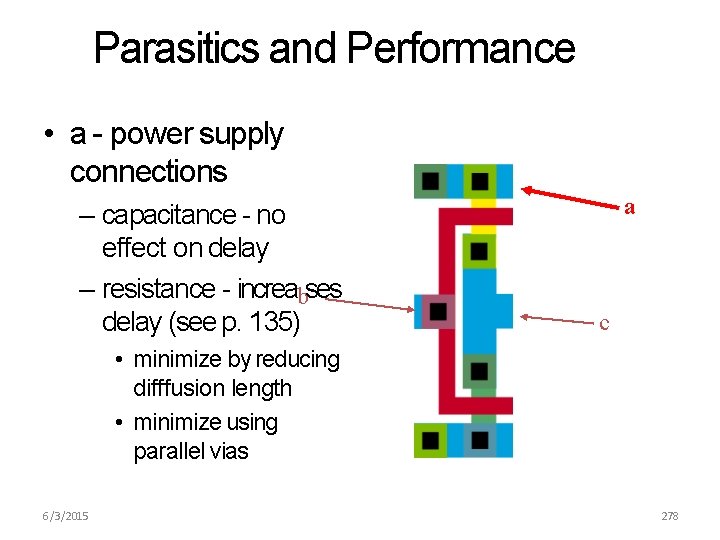

Parasitics and Performance • a - power supply connections – capacitance - no effect on delay – resistance - increabses delay (see p. 135) a c • minimize by reducing difffusion length • minimize using parallel vias 6/3/2015 278

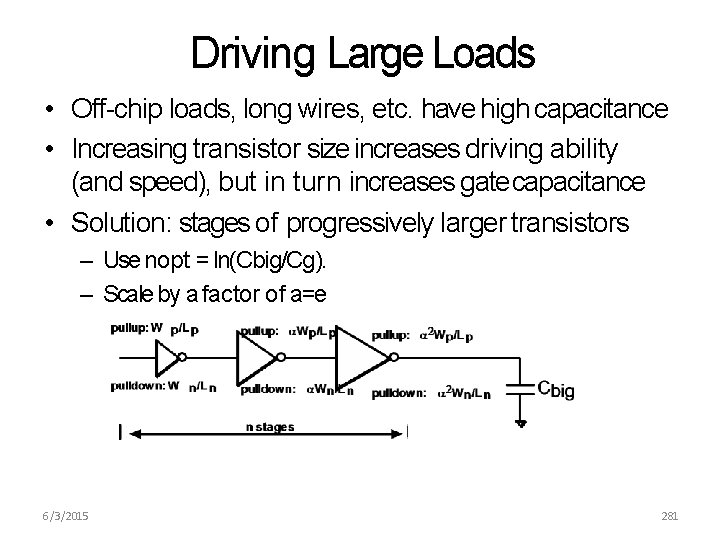

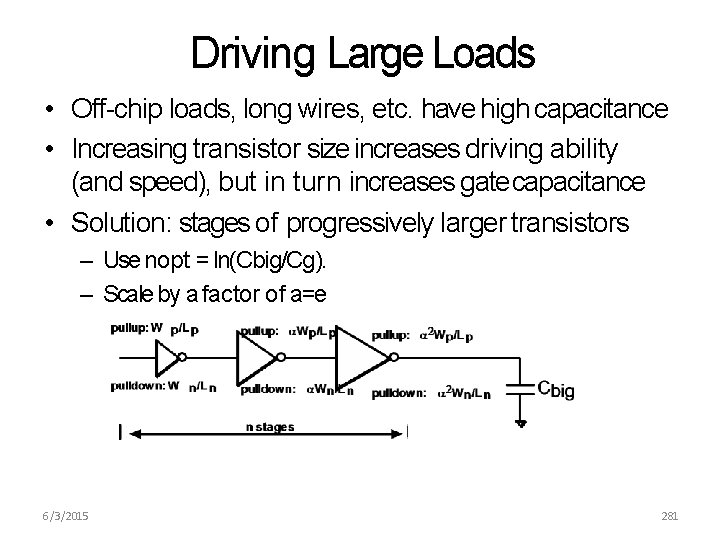

Driving Large Loads • Off-chip loads, long wires, etc. have high capacitance • Increasing transistor size increases driving ability (and speed), but in turn increases gate capacitance • Solution: stages of progressively larger transistors – Use nopt = ln(Cbig/Cg). – Scale by a factor of a=e 6/3/2015 281

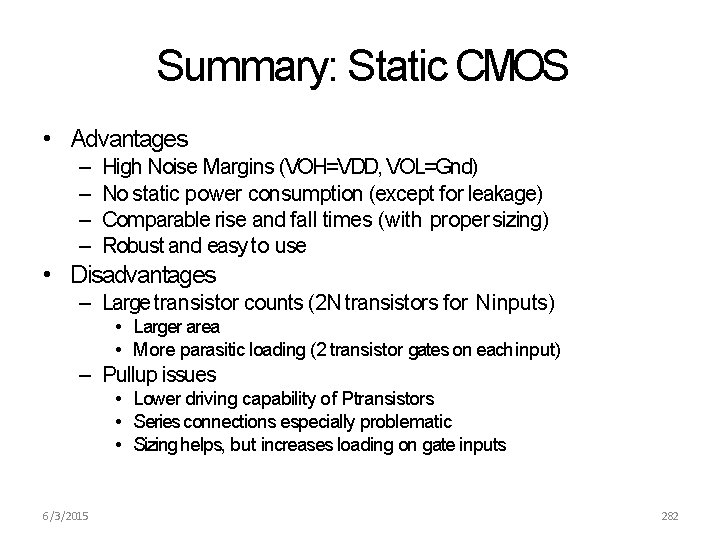

Summary: Static CMOS • Advantages – – High Noise Margins (VOH=VDD, VOL=Gnd) No static power consumption (except for leakage) Comparable rise and fall times (with proper sizing) Robust and easy to use • Disadvantages – Large transistor counts (2 N transistors for N inputs) • Larger area • More parasitic loading (2 transistor gates on each input) – Pullup issues • Lower driving capability of Ptransistors • Series connections especially problematic • Sizing helps, but increases loading on gate inputs 6/3/2015 282

Alternatives to Static CMOS • • • Switch Logic nmos Pseudo-nmos Dynamic Logic Low-Power Gates 6/3/2015 283

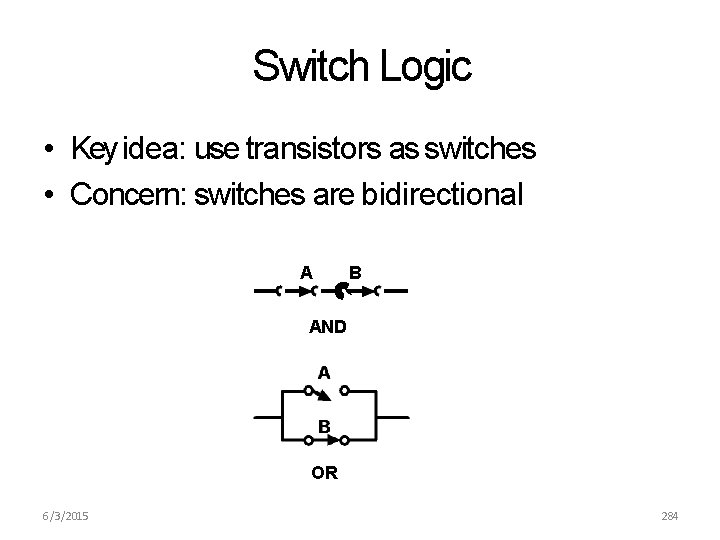

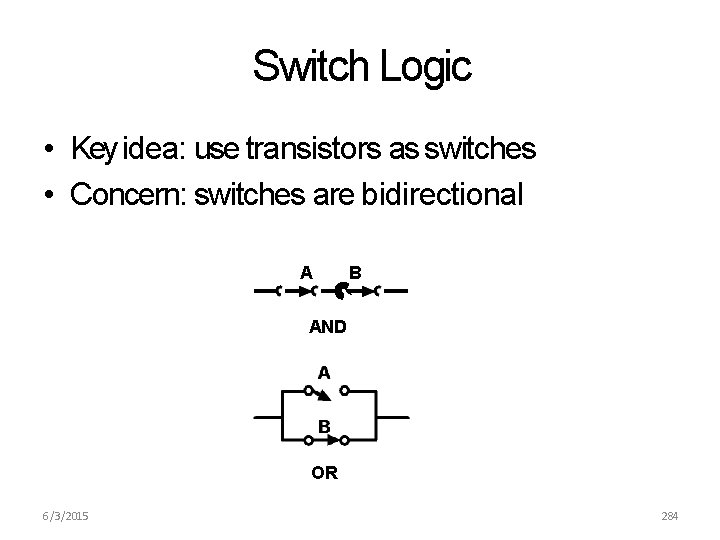

Switch Logic • Key idea: use transistors as switches • Concern: switches are bidirectional A B AND OR 6/3/2015 284

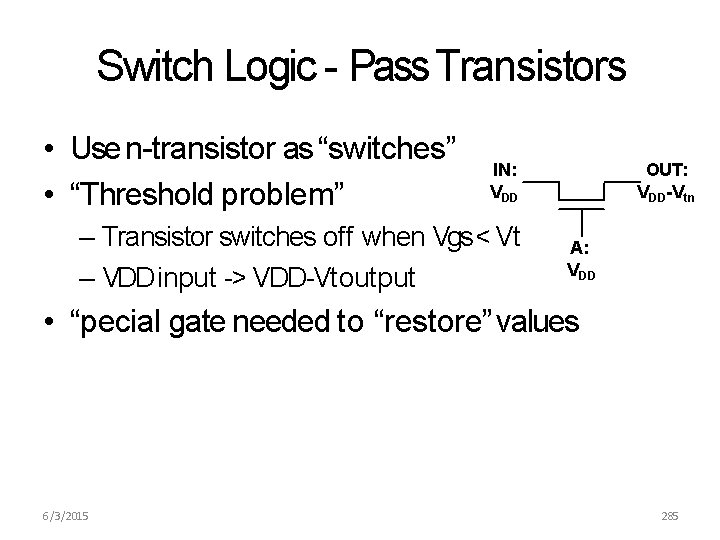

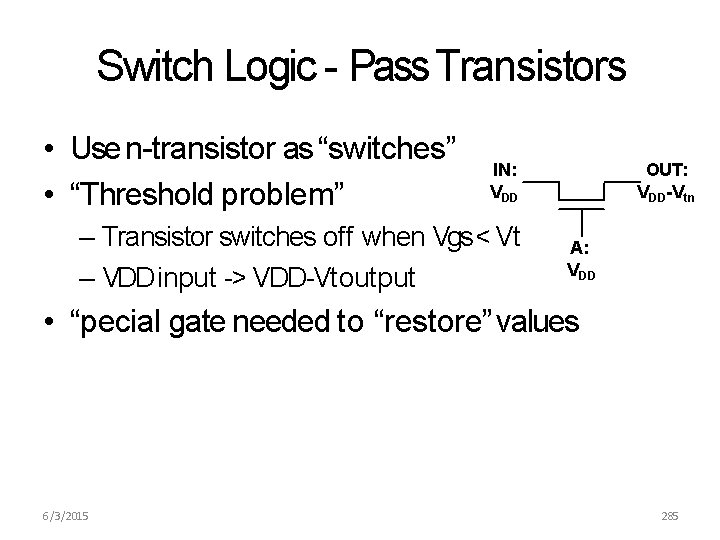

Switch Logic - Pass Transistors • Use n-transistor as “switches” • “Threshold problem” IN: VDD – Transistor switches off when Vgs < Vt – VDD input -> VDD-Vt output OUT: VDD-Vtn A: VDD • “pecial gate needed to “restore” values 6/3/2015 285

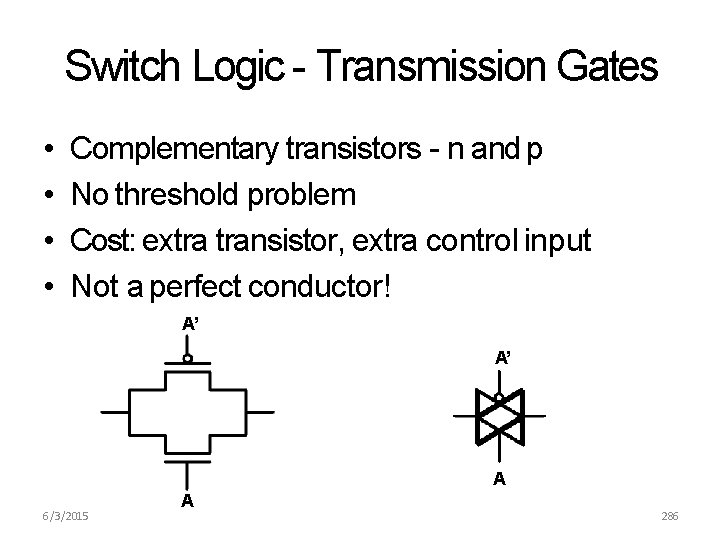

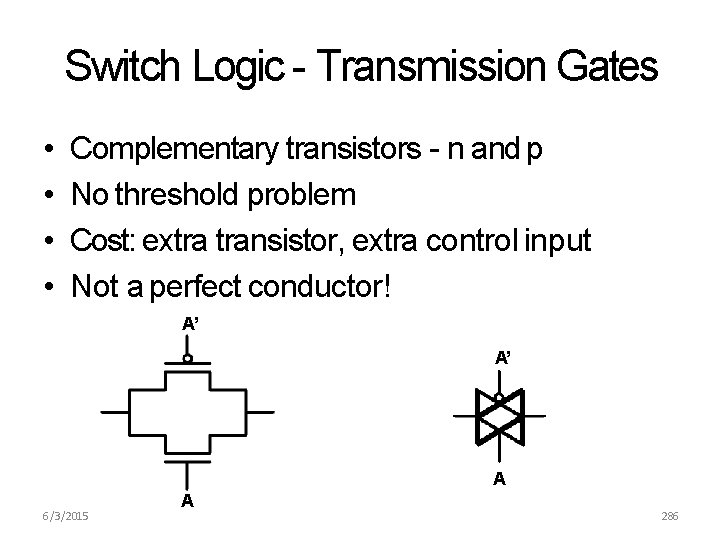

Switch Logic - Transmission Gates • • Complementary transistors - n and p No threshold problem Cost: extra transistor, extra control input Not a perfect conductor! A’ A’ A 6/3/2015 A 286

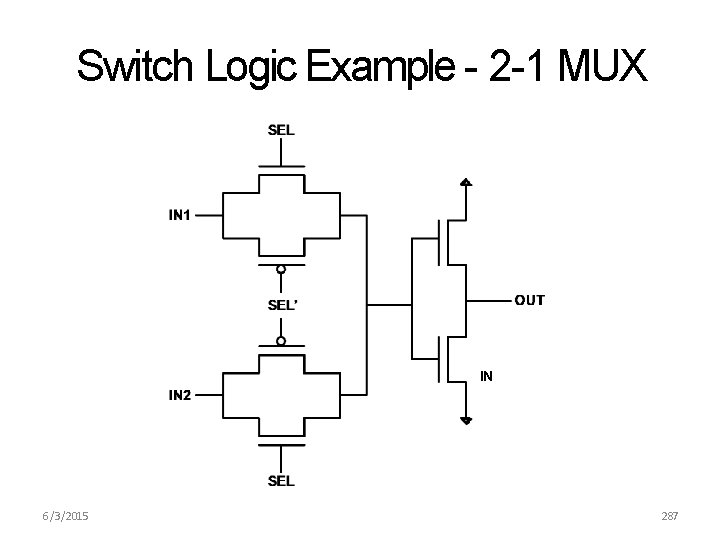

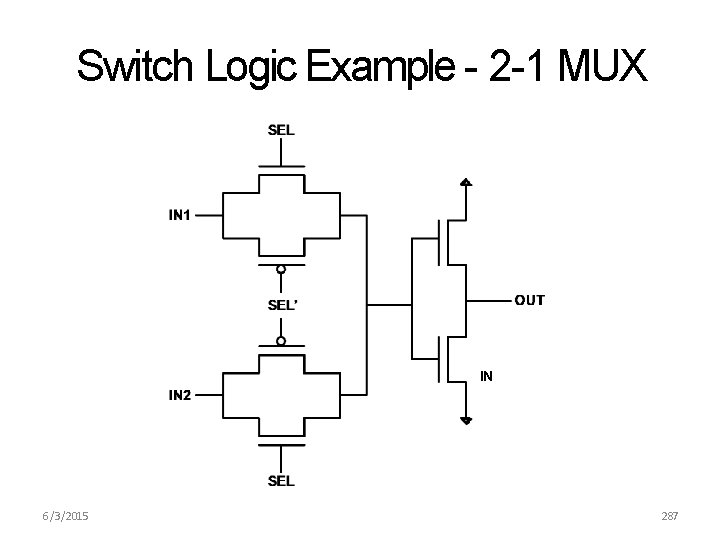

Switch Logic Example - 2 -1 MUX IN 6/3/2015 287

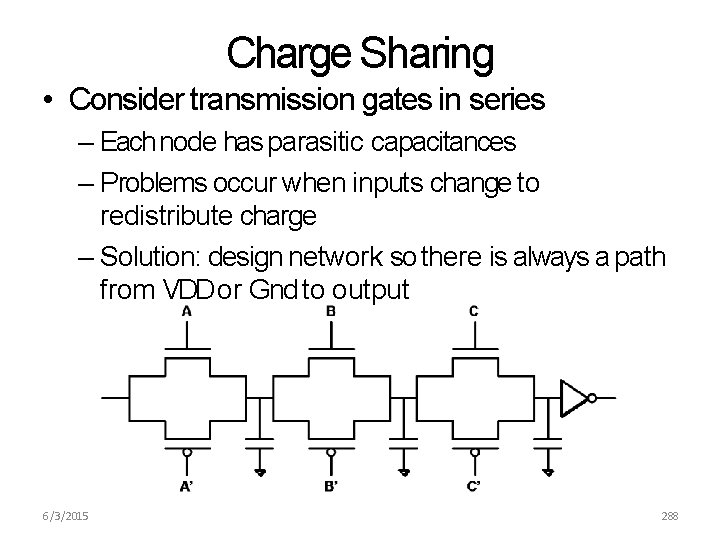

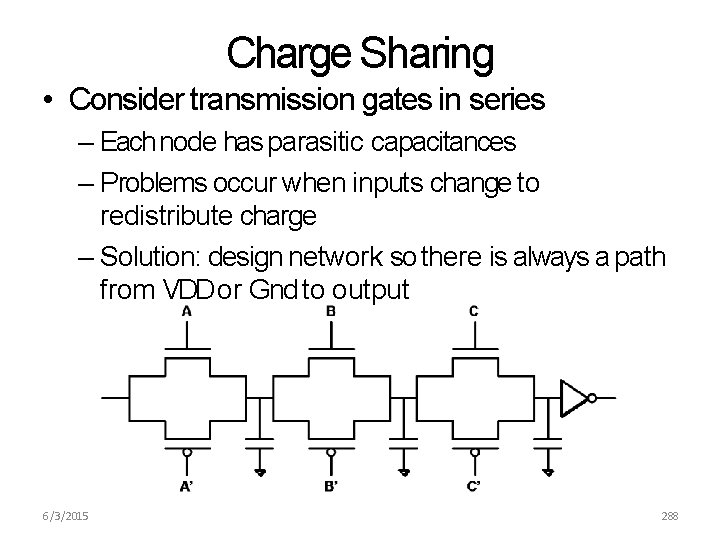

Charge Sharing • Consider transmission gates in series – Each node has parasitic capacitances – Problems occur when inputs change to redistribute charge – Solution: design network so there is always a path from VDD or Gnd to output 6/3/2015 288

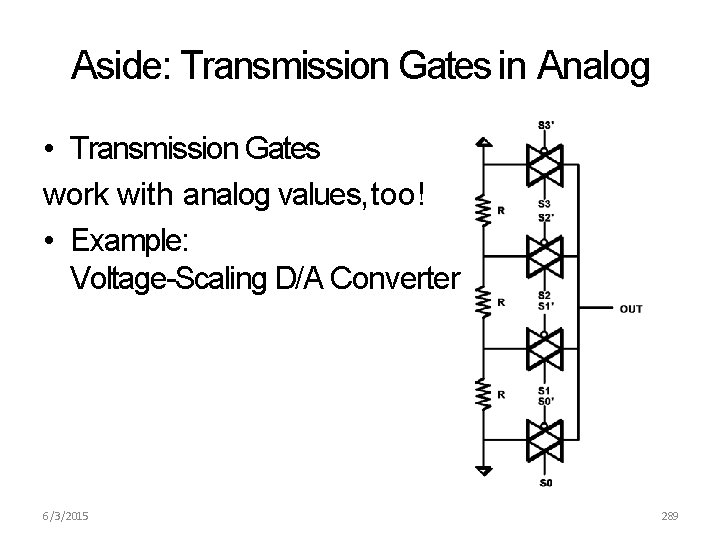

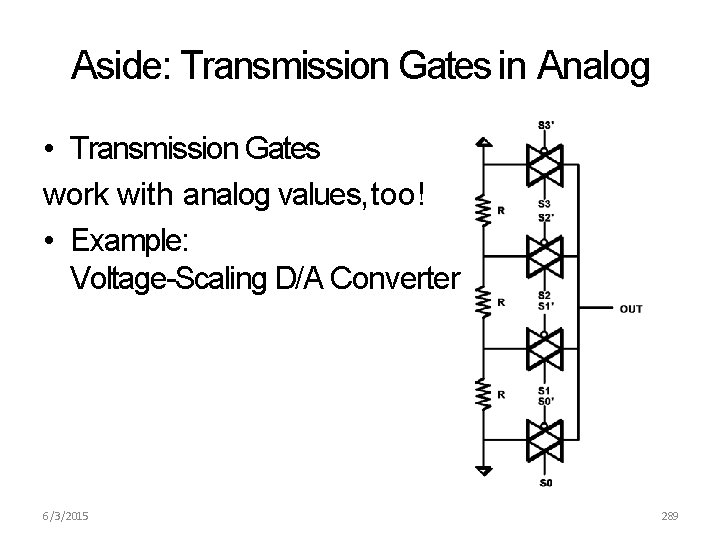

Aside: Transmission Gates in Analog • Transmission Gates work with analog values, too! • Example: Voltage-Scaling D/A Converter 6/3/2015 289

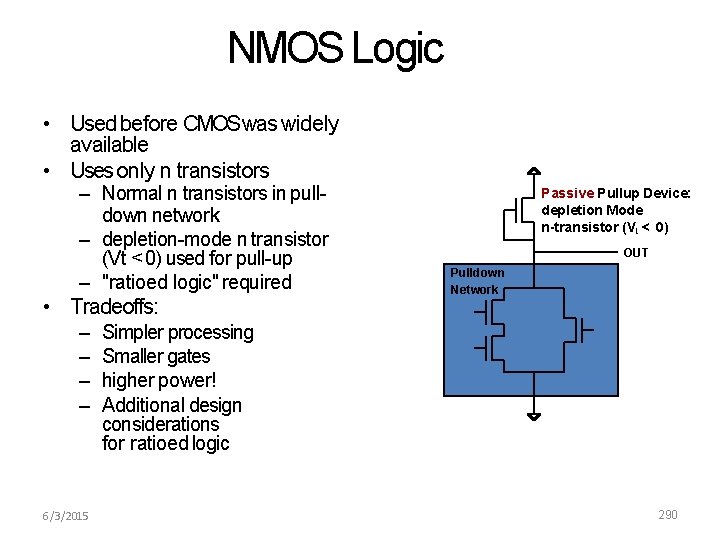

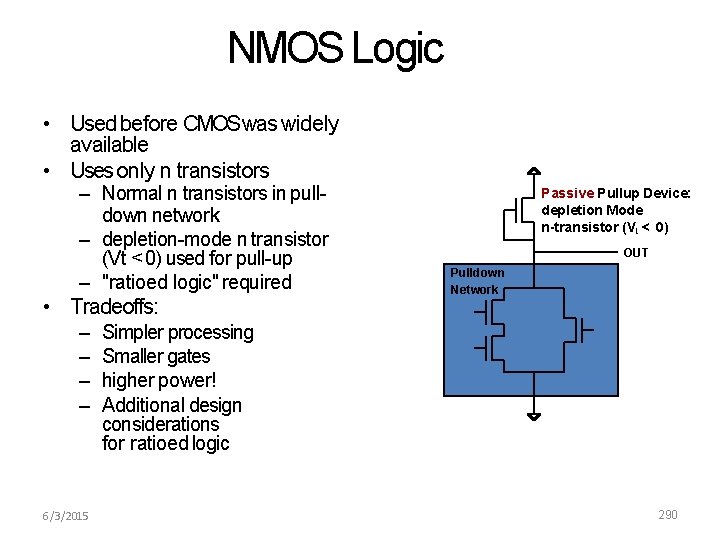

NMOS Logic • Used before CMOSwas widely available • Uses only n transistors – Normal n transistors in pulldown network – depletion-mode n transistor (Vt < 0) used for pull-up – "ratioed logic" required • Tradeoffs: – – 6/3/2015 Passive Pullup Device: depletion Mode n-transistor (Vt < 0) OUT Pulldown Network Simpler processing Smaller gates higher power! Additional design considerations for ratioed logic 290

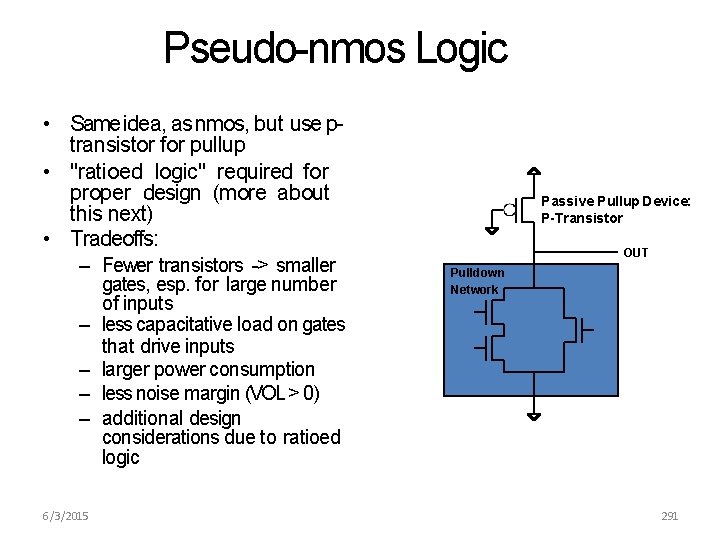

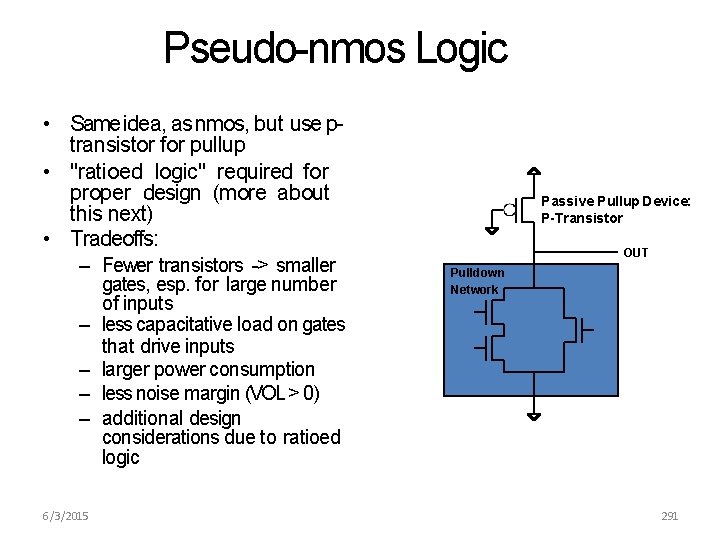

Pseudo-nmos Logic • Same idea, as nmos, but use ptransistor for pullup • "ratioed logic" required for proper design (more about this next) • Tradeoffs: – Fewer transistors -> smaller gates, esp. for large number of inputs – less capacitative load on gates that drive inputs – larger power consumption – less noise margin (VOL > 0) – additional design considerations due to ratioed logic 6/3/2015 Passive Pullup Device: P-Transistor OUT Pulldown Network 291

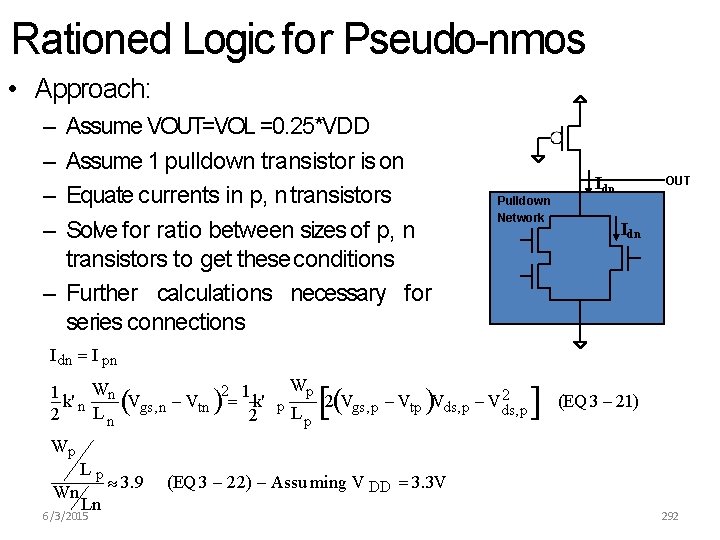

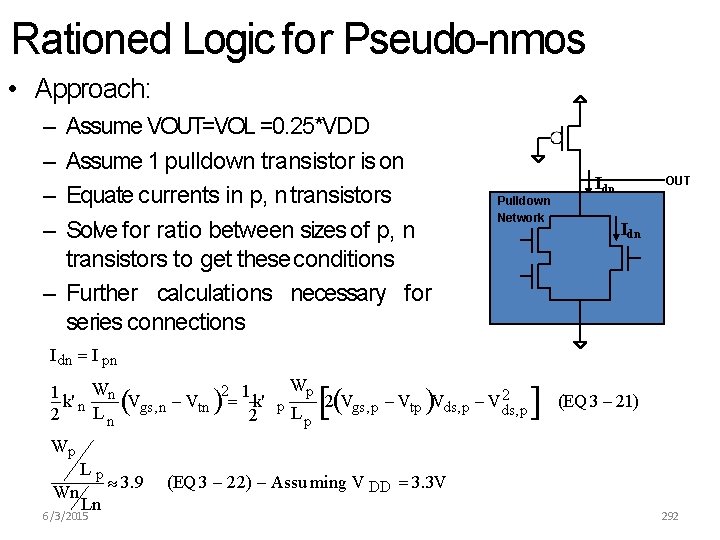

Rationed Logic for Pseudo-nmos • Approach: – – Assume VOUT=VOL =0. 25*VDD Assume 1 pulldown transistor is on Equate currents in p, n transistors Solve for ratio between sizes of p, n transistors to get these conditions – Further calculations necessary for series connections Pulldown Network Idp OUT Idn I pn Wp Wn 2 1 1 2 Vgs, n Vtn k' p 2 Vgs, p Vtp Vds, p k' n Ln Lp 2 2 Wp Lp 3. 9 (EQ 3 22) Assu min g V DD 3. 3 V Wn Ln 6/3/2015 (EQ 3 21) 292

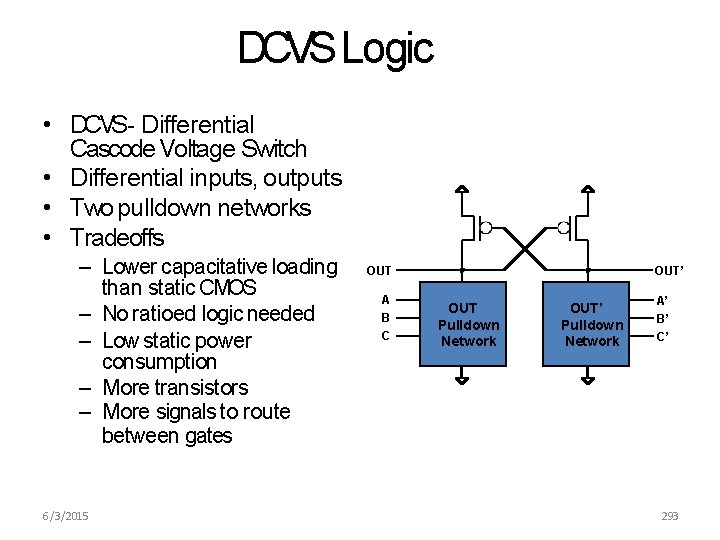

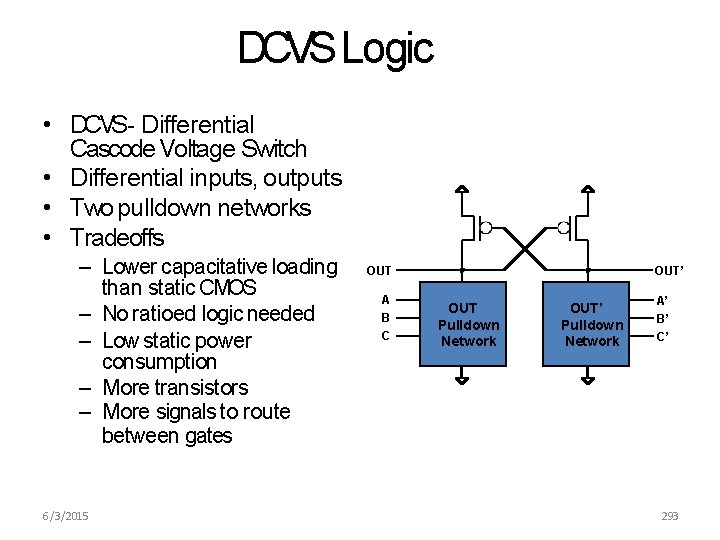

DCVS Logic • DCVS- Differential Cascode Voltage Switch • Differential inputs, outputs • Two pulldown networks • Tradeoffs – Lower capacitative loading than static CMOS – No ratioed logic needed – Low static power consumption – More transistors – More signals to route between gates 6/3/2015 OUT A B C OUT’ OUT Pulldown Network OUT’ Pulldown Network A’ B’ C’ 293

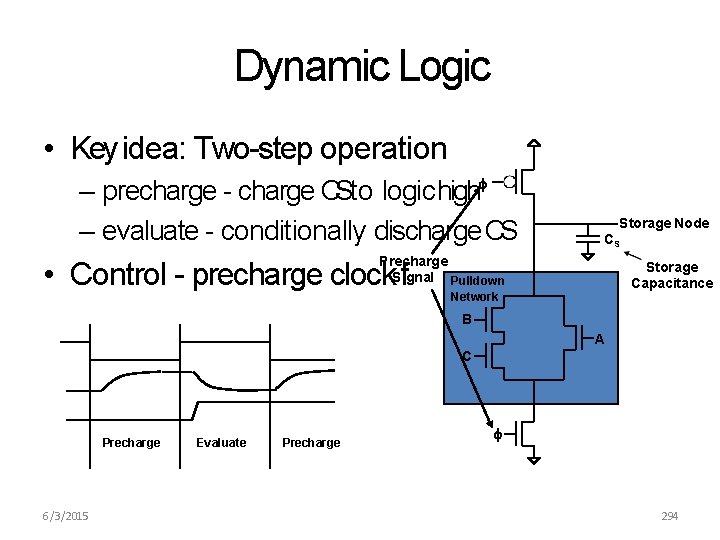

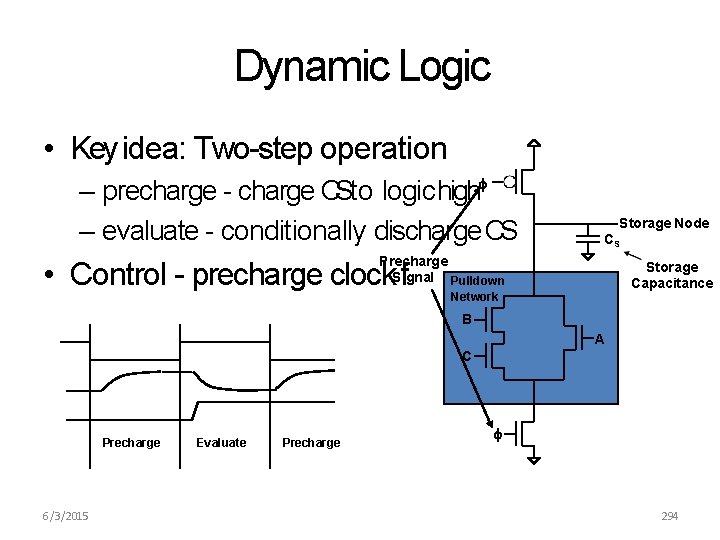

Dynamic Logic • Key idea: Two-step operation – precharge - charge CSto logic high – evaluate - conditionally discharge CS Storage Node CS Precharge Signal Pulldown • Control - precharge clock f Storage Capacitance Network B A C Precharge 6/3/2015 Evaluate Precharge 294

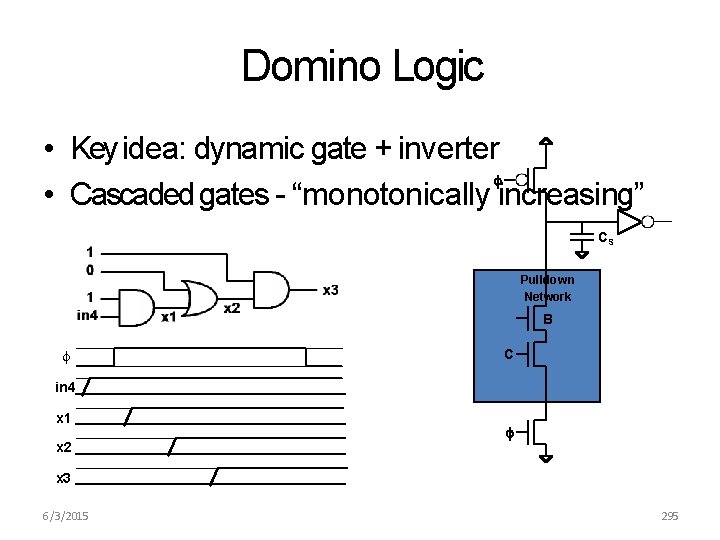

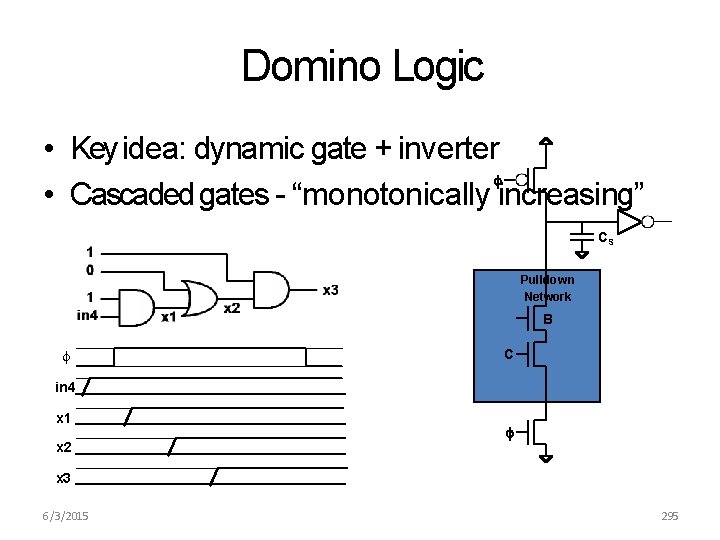

Domino Logic • Key idea: dynamic gate + inverter • Cascaded gates - “monotonically increasing” CS Pulldown Network B C in 4 x 1 x 2 x 3 6/3/2015 295

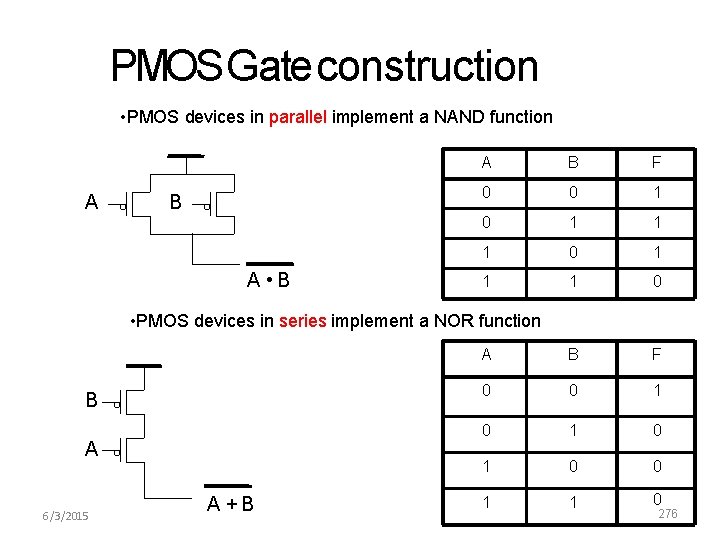

Domino Logic Tradeoffs • • Fewer transistors -> smaller gates Lower power consumption than pseudo-nmos Clocking required Logic not complete (AND, OR, but no NOT) 6/3/2015 296