Unitati fundamentale de proiectare in VHDL Design units

![Exemplu [EKP 98] • Vom descrie un circuit generator de paritate, avand patru intrari Exemplu [EKP 98] • Vom descrie un circuit generator de paritate, avand patru intrari](https://slidetodoc.com/presentation_image_h/db2a4c8220634daa59a5c3d076dba6ad/image-10.jpg)

- Slides: 28

Unitati fundamentale de proiectare in VHDL (Design units) Capitolul 2

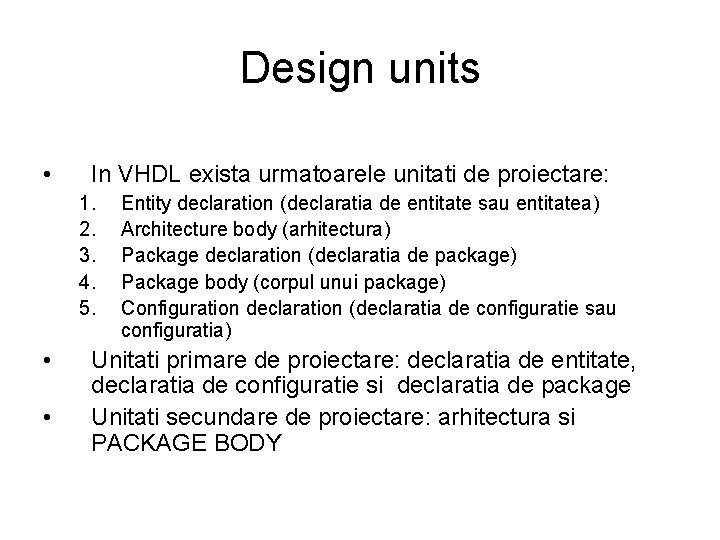

Design units • Un sistem digital poate fi modelat in VHDL ca o entitate (entity): – entitatea este unitatea fundamentala a unui proiect (design) – O entitate poate fi o componenta a unui alt proiect sau poate fi modulul de pe nivelul cel mai inalt al proiectului (top level module of the design) • O entitate e descrisa ca un set de unitati de proiectare VHDL (design units). • Aceste unitati de proiectare pot fi compilate separat

Design units • In VHDL exista urmatoarele unitati de proiectare: 1. 2. 3. 4. 5. • • Entity declaration (declaratia de entitate sau entitatea) Architecture body (arhitectura) Package declaration (declaratia de package) Package body (corpul unui package) Configuration declaration (declaratia de configuratie sau configuratia) Unitati primare de proiectare: declaratia de entitate, declaratia de configuratie si declaratia de package Unitati secundare de proiectare: arhitectura si PACKAGE BODY

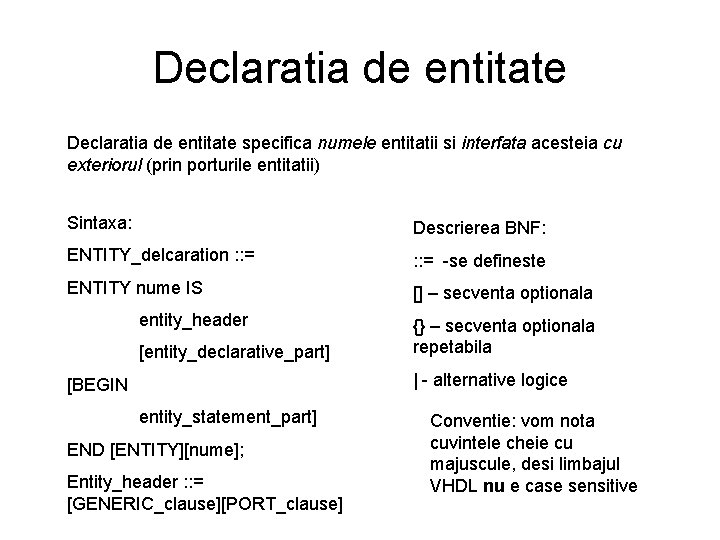

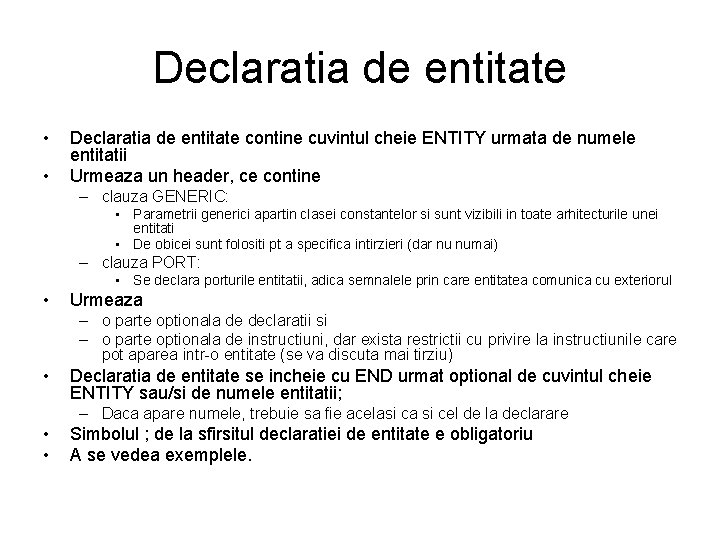

Declaratia de entitate specifica numele entitatii si interfata acesteia cu exteriorul (prin porturile entitatii) Sintaxa: Descrierea BNF: ENTITY_delcaration : : = -se defineste ENTITY nume IS [] – secventa optionala entity_header [entity_declarative_part] {} – secventa optionala repetabila | - alternative logice [BEGIN entity_statement_part] END [ENTITY][nume]; Entity_header : : = [GENERIC_clause][PORT_clause] Conventie: vom nota cuvintele cheie cu majuscule, desi limbajul VHDL nu e case sensitive

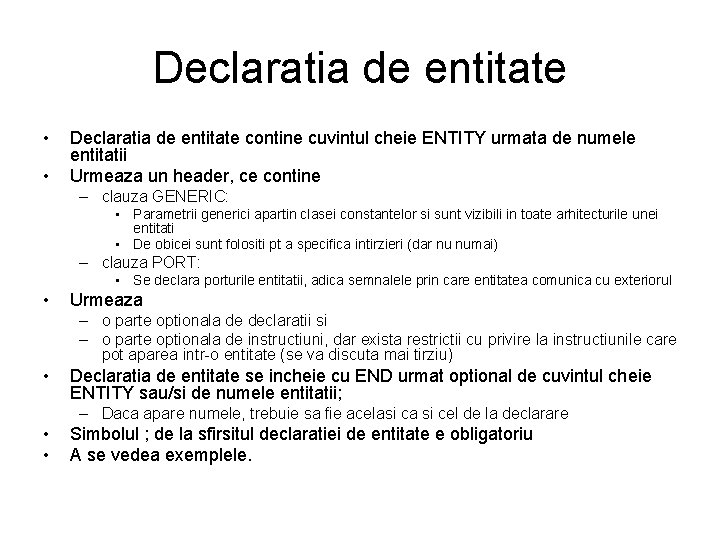

Declaratia de entitate • • Declaratia de entitate contine cuvintul cheie ENTITY urmata de numele entitatii Urmeaza un header, ce contine – clauza GENERIC: • Parametrii generici apartin clasei constantelor si sunt vizibili in toate arhitecturile unei entitati • De obicei sunt folositi pt a specifica intirzieri (dar nu numai) – clauza PORT: • Se declara porturile entitatii, adica semnalele prin care entitatea comunica cu exteriorul • Urmeaza – o parte optionala de declaratii si – o parte optionala de instructiuni, dar exista restrictii cu privire la instructiunile care pot aparea intr-o entitate (se va discuta mai tirziu) • Declaratia de entitate se incheie cu END urmat optional de cuvintul cheie ENTITY sau/si de numele entitatii; – Daca apare numele, trebuie sa fie acelasi ca si cel de la declarare • • Simbolul ; de la sfirsitul declaratiei de entitate e obligatoriu A se vedea exemplele.

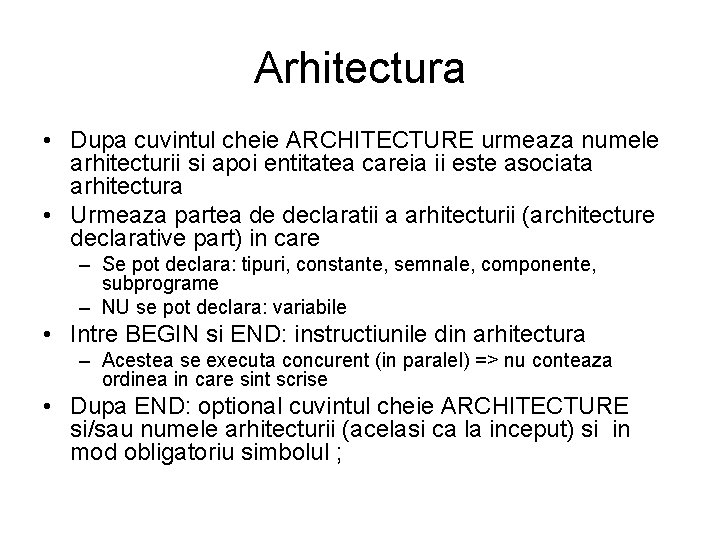

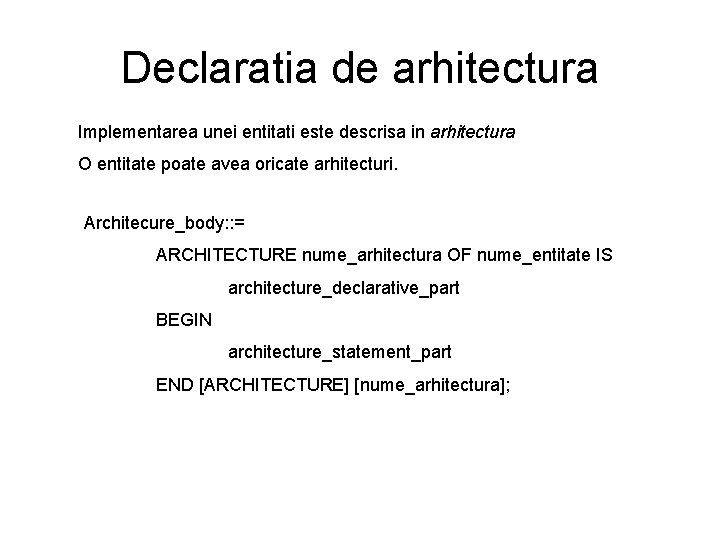

Declaratia de arhitectura Implementarea unei entitati este descrisa in arhitectura O entitate poate avea oricate arhitecturi. Architecure_body: : = ARCHITECTURE nume_arhitectura OF nume_entitate IS architecture_declarative_part BEGIN architecture_statement_part END [ARCHITECTURE] [nume_arhitectura];

Arhitectura • Dupa cuvintul cheie ARCHITECTURE urmeaza numele arhitecturii si apoi entitatea careia ii este asociata arhitectura • Urmeaza partea de declaratii a arhitecturii (architecture declarative part) in care – Se pot declara: tipuri, constante, semnale, componente, subprograme – NU se pot declara: variabile • Intre BEGIN si END: instructiunile din arhitectura – Acestea se executa concurent (in paralel) => nu conteaza ordinea in care sint scrise • Dupa END: optional cuvintul cheie ARCHITECTURE si/sau numele arhitecturii (acelasi ca la inceput) si in mod obligatoriu simbolul ;

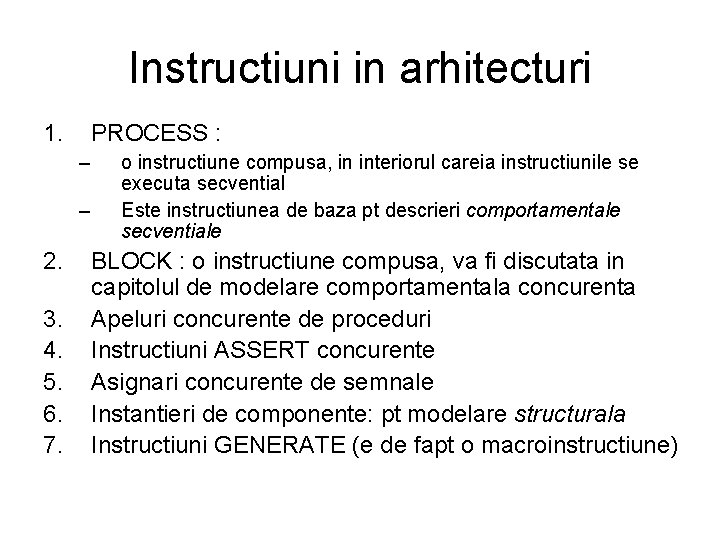

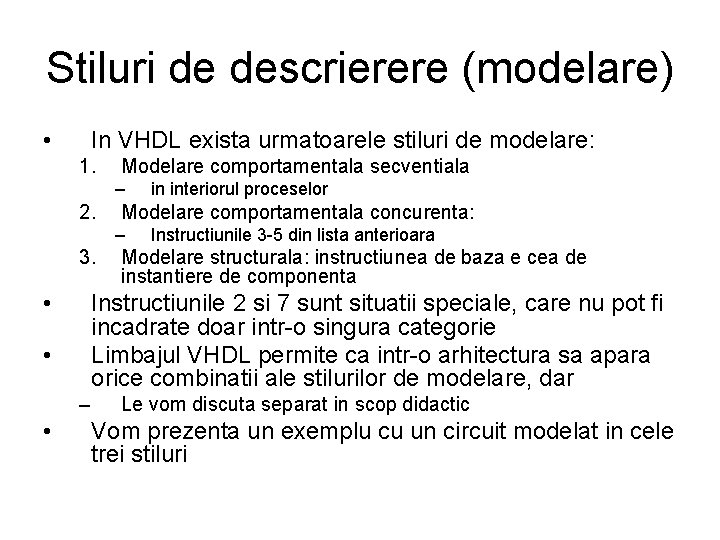

Instructiuni in arhitecturi 1. PROCESS : – – 2. 3. 4. 5. 6. 7. o instructiune compusa, in interiorul careia instructiunile se executa secvential Este instructiunea de baza pt descrieri comportamentale secventiale BLOCK : o instructiune compusa, va fi discutata in capitolul de modelare comportamentala concurenta Apeluri concurente de proceduri Instructiuni ASSERT concurente Asignari concurente de semnale Instantieri de componente: pt modelare structurala Instructiuni GENERATE (e de fapt o macroinstructiune)

Stiluri de descrierere (modelare) • In VHDL exista urmatoarele stiluri de modelare: 1. Modelare comportamentala secventiala – 2. Modelare comportamentala concurenta: – 3. • Instructiunile 3 -5 din lista anterioara Modelare structurala: instructiunea de baza e cea de instantiere de componenta Instructiunile 2 si 7 sunt situatii speciale, care nu pot fi incadrate doar intr-o singura categorie Limbajul VHDL permite ca intr-o arhitectura sa apara orice combinatii ale stilurilor de modelare, dar • – • in interiorul proceselor Le vom discuta separat in scop didactic Vom prezenta un exemplu cu un circuit modelat in cele trei stiluri

![Exemplu EKP 98 Vom descrie un circuit generator de paritate avand patru intrari Exemplu [EKP 98] • Vom descrie un circuit generator de paritate, avand patru intrari](https://slidetodoc.com/presentation_image_h/db2a4c8220634daa59a5c3d076dba6ad/image-10.jpg)

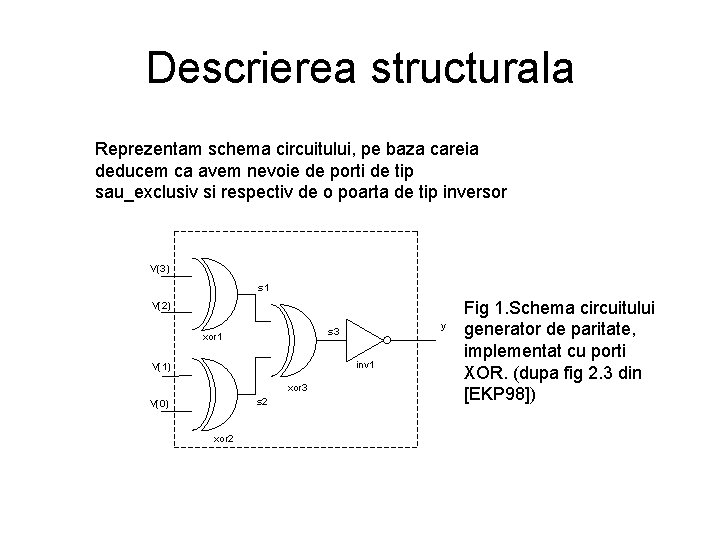

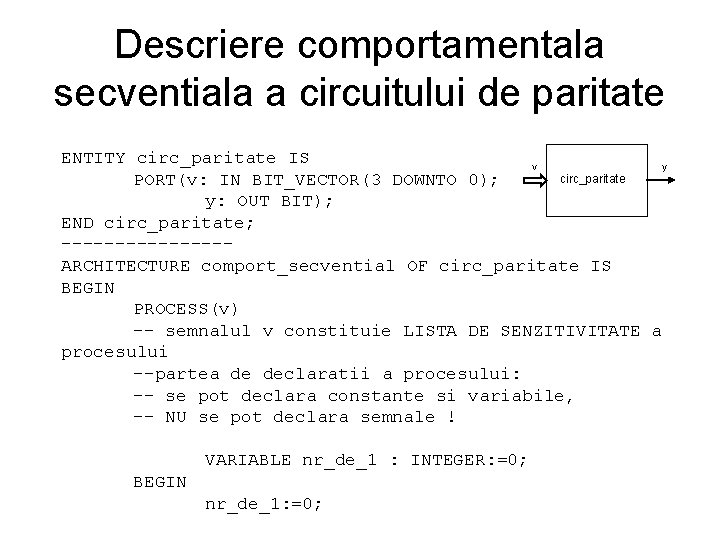

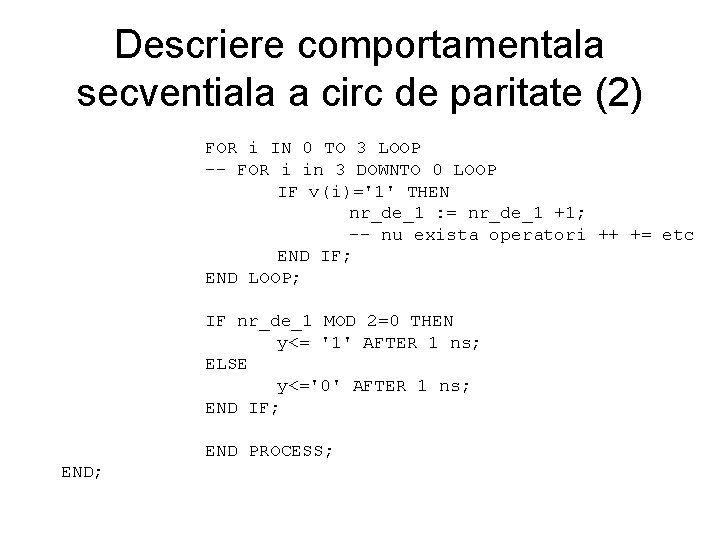

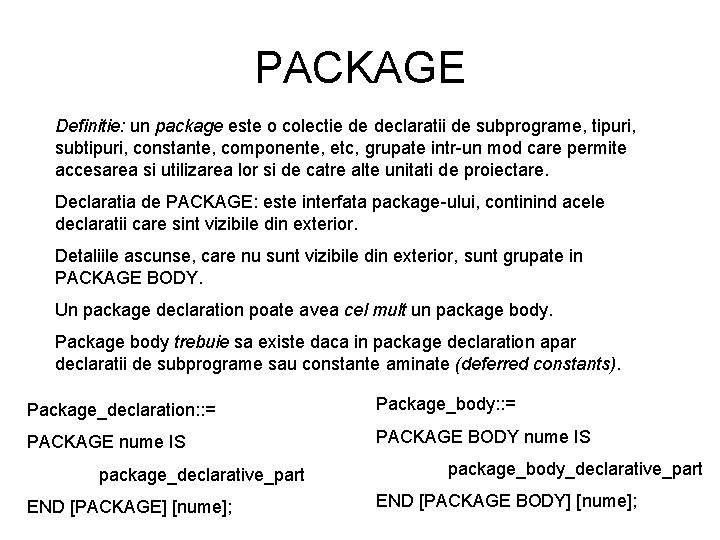

Exemplu [EKP 98] • Vom descrie un circuit generator de paritate, avand patru intrari de tip BIT si o iesire care se activeaza (ia valoarea 1) cind combinatia de la intrare contine un nr par de ‘ 1’ • Aceasta este o specificare a circuitului, care ne poate servi pt descrierea comportamentala secventiala • Nu avem nevoie de schema circuitului pentru descrierea comportamentala secventiala !

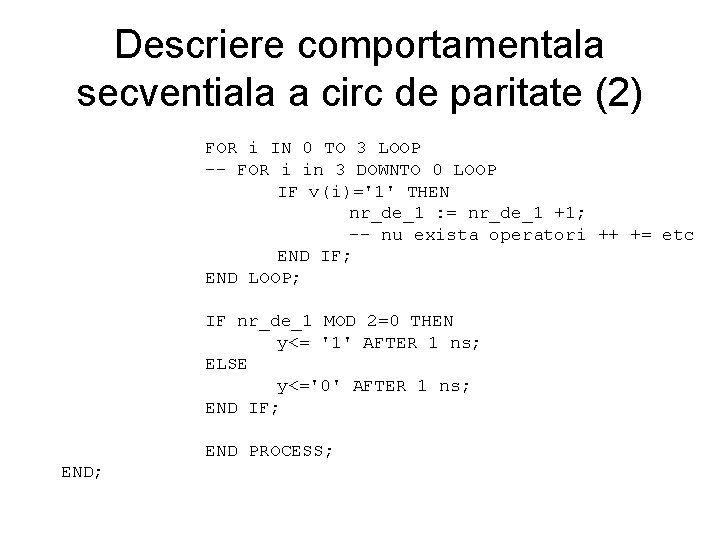

Descriere comportamentala secventiala a circuitului de paritate ENTITY circ_paritate IS v y circ_paritate PORT(v: IN BIT_VECTOR(3 DOWNTO 0); y: OUT BIT); END circ_paritate; --------ARCHITECTURE comport_secvential OF circ_paritate IS BEGIN PROCESS(v) -- semnalul v constituie LISTA DE SENZITIVITATE a procesului --partea de declaratii a procesului: -- se pot declara constante si variabile, -- NU se pot declara semnale ! VARIABLE nr_de_1 : INTEGER: =0; BEGIN nr_de_1: =0;

Descriere comportamentala secventiala a circ de paritate (2) FOR i IN 0 TO 3 LOOP -- FOR i in 3 DOWNTO 0 LOOP IF v(i)='1' THEN nr_de_1 : = nr_de_1 +1; -- nu exista operatori ++ += etc END IF; END LOOP; IF nr_de_1 MOD 2=0 THEN y<= '1' AFTER 1 ns; ELSE y<='0' AFTER 1 ns; END IF; END PROCESS; END;

Descrierea comportamentala secventiala comentarii • Entitatea: – Se numeste circ_paritate – Are o intrare v care e un vector de 4 biti – Are o iesire y de tip BIT • BIT e un tip predefinit in limbaj, avind valorile ‘ 0’ si ‘ 1’ • Si BIT_VECTOR e predefinit in limbaj, ca ARRAY de BIT (tablou de biti) • Arhitectura – Nu contine declaratii in partea de declaratii – Contine o singura instructiune (PROCESS)

Comentarii (continuare) • PROCESS – Are o lista de senzitivitate, continind semnalul v, adica procesul se activeaza (se executa) de fiecare data cind se modifica v (are loc un eveniment pt semnalul v) – In general lista de senzitivitate poate contine mai multe semnale; de fiecare data cind se modifica oricare din semnale, procesul isi reia executia – Partea de declaratii a procesului contine declararea unei variabile, nr_de_1, de tip intreg (un contor). Variabila e initializata cu 0 la declarare. – In procese se pot declara constante, variabile, subprograme, tipuri, dar – In procese NU se pot declara semnale si nici componente ! – Instructiunile din interiorul procesului se executa secvential (in ordinea in care sint scrise) – Se parcurge vectorul de intrare si se incrementeaza contorul atunci cind se gaseste o valoare ‘ 1’ – Daca s-a gasit un nr par de biti de ‘ 1’ atunci iesirea y va avea valoarea ‘ 1’ dupa o intirziere de 1 ns (o nano secunda) – Procesul e o bulca infinita: dupa END PROCESS se merge din nou la BEGIN

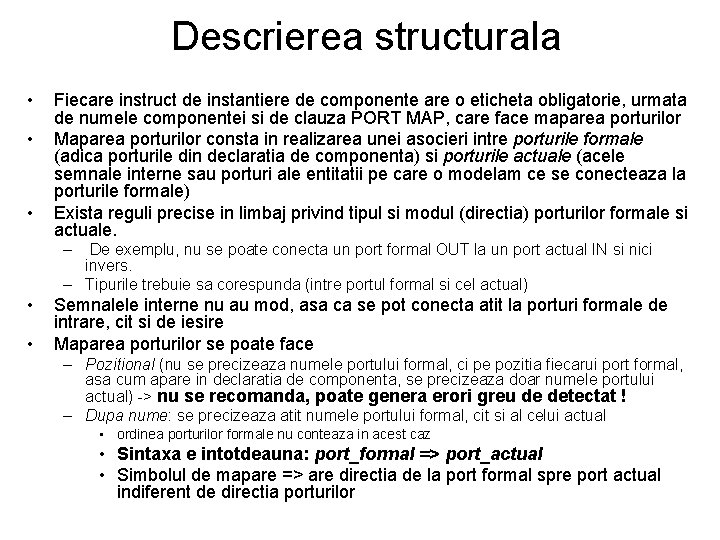

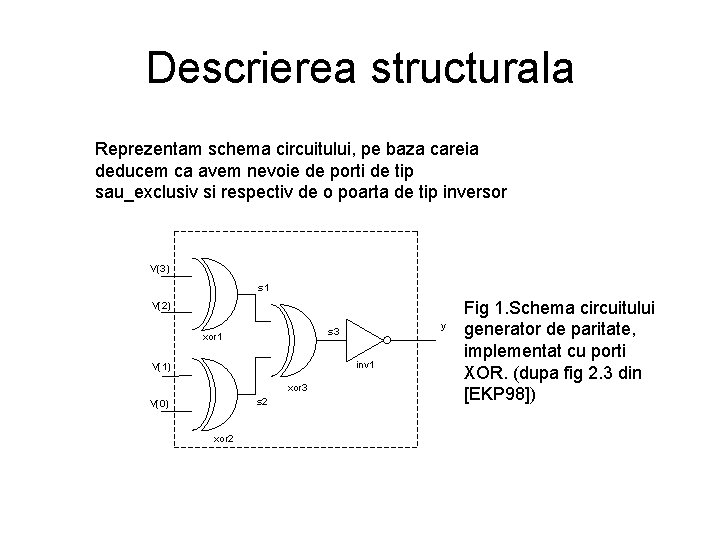

Descrierea structurala Reprezentam schema circuitului, pe baza careia deducem ca avem nevoie de porti de tip sau_exclusiv si respectiv de o poarta de tip inversor V(3) s 1 V(2) y s 3 xor 1 inv 1 V(1) xor 3 s 2 V(0) xor 2 Fig 1. Schema circuitului generator de paritate, implementat cu porti XOR. (dupa fig 2. 3 din [EKP 98])

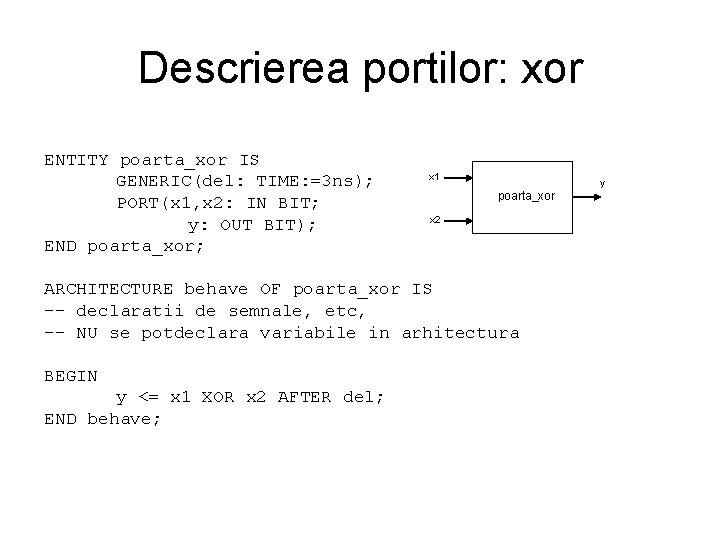

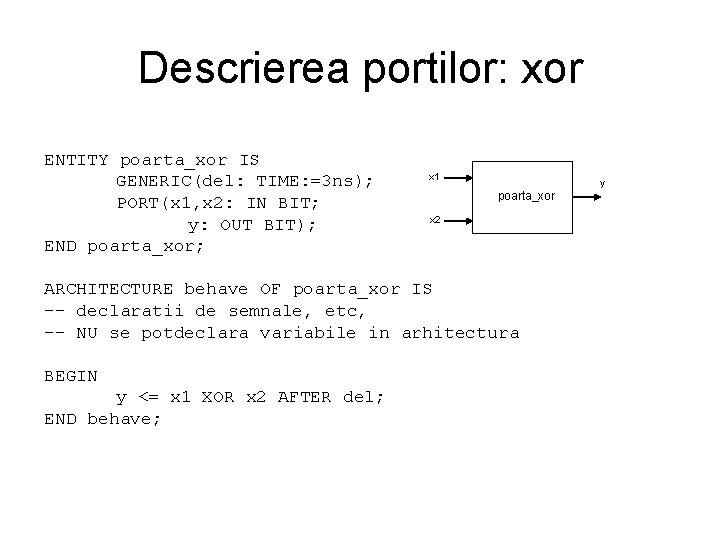

Descrierea portilor: xor ENTITY poarta_xor IS GENERIC(del: TIME: =3 ns); PORT(x 1, x 2: IN BIT; y: OUT BIT); END poarta_xor; x 1 y poarta_xor x 2 ARCHITECTURE behave OF poarta_xor IS -- declaratii de semnale, etc, -- NU se potdeclara variabile in arhitectura BEGIN y <= x 1 XOR x 2 AFTER del; END behave;

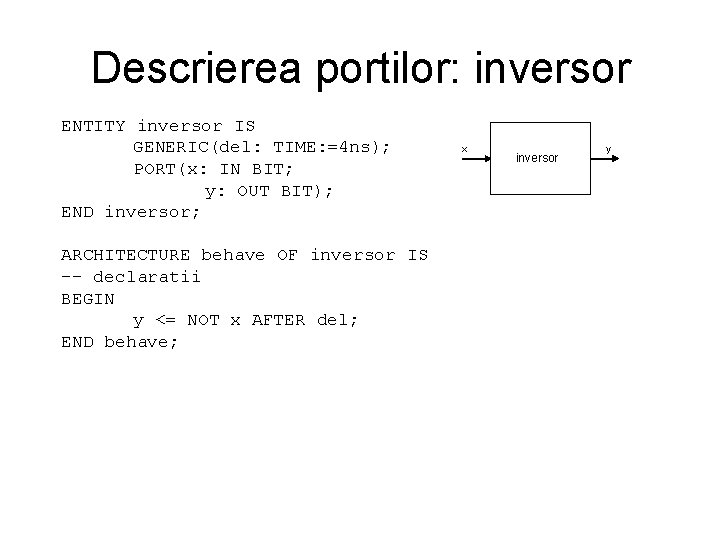

Descrierea portilor: inversor ENTITY inversor IS GENERIC(del: TIME: =4 ns); PORT(x: IN BIT; y: OUT BIT); END inversor; ARCHITECTURE behave OF inversor IS -- declaratii BEGIN y <= NOT x AFTER del; END behave; x inversor y

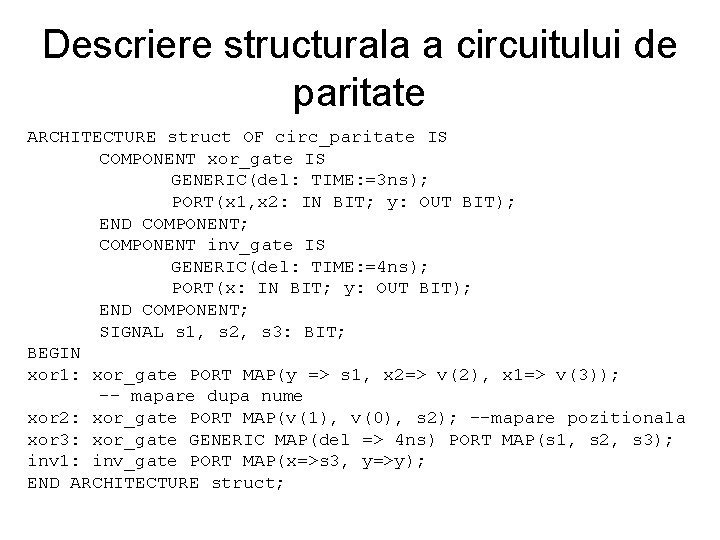

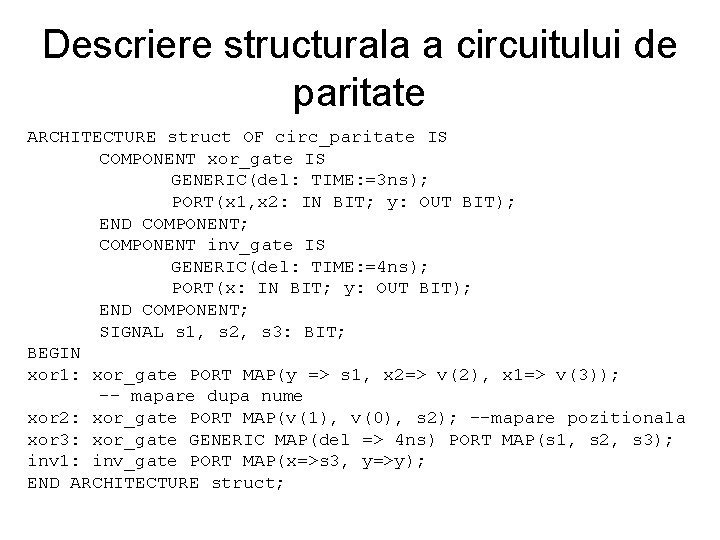

Descriere structurala a circuitului de paritate ARCHITECTURE struct OF circ_paritate IS COMPONENT xor_gate IS GENERIC(del: TIME: =3 ns); PORT(x 1, x 2: IN BIT; y: OUT BIT); END COMPONENT; COMPONENT inv_gate IS GENERIC(del: TIME: =4 ns); PORT(x: IN BIT; y: OUT BIT); END COMPONENT; SIGNAL s 1, s 2, s 3: BIT; BEGIN xor 1: xor_gate PORT MAP(y => s 1, x 2=> v(2), x 1=> v(3)); -- mapare dupa nume xor 2: xor_gate PORT MAP(v(1), v(0), s 2); --mapare pozitionala xor 3: xor_gate GENERIC MAP(del => 4 ns) PORT MAP(s 1, s 2, s 3); inv 1: inv_gate PORT MAP(x=>s 3, y=>y); END ARCHITECTURE struct;

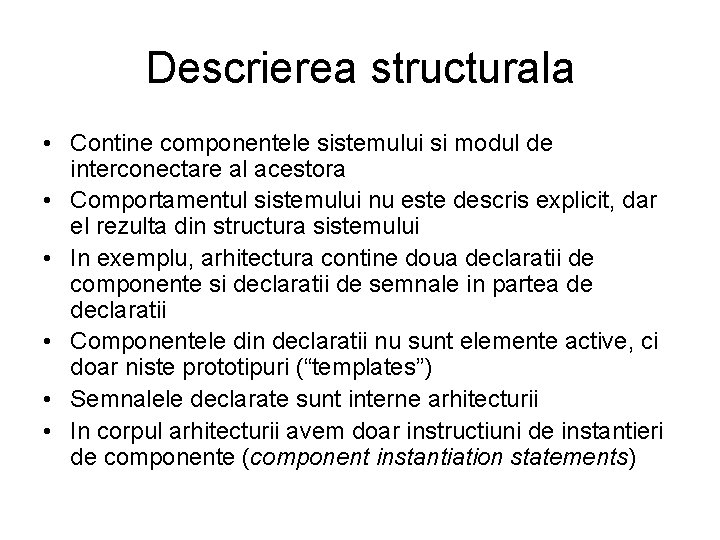

Descrierea structurala • Contine componentele sistemului si modul de interconectare al acestora • Comportamentul sistemului nu este descris explicit, dar el rezulta din structura sistemului • In exemplu, arhitectura contine doua declaratii de componente si declaratii de semnale in partea de declaratii • Componentele din declaratii nu sunt elemente active, ci doar niste prototipuri (“templates”) • Semnalele declarate sunt interne arhitecturii • In corpul arhitecturii avem doar instructiuni de instantieri de componente (component instantiation statements)

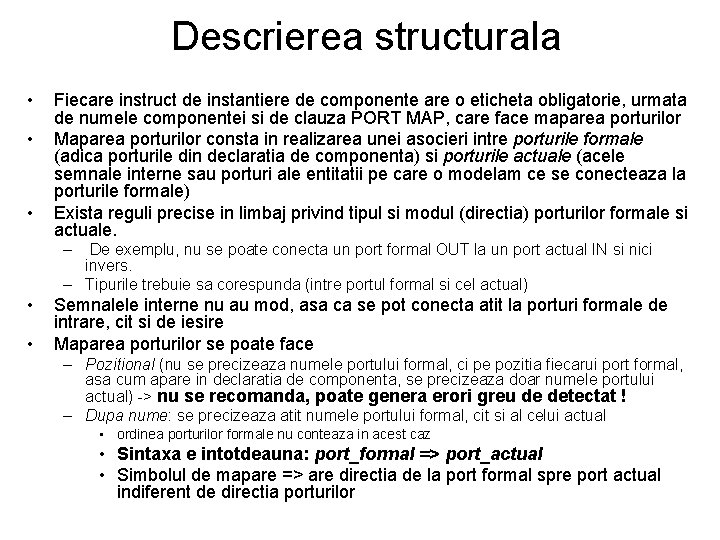

Descrierea structurala • • • Fiecare instruct de instantiere de componente are o eticheta obligatorie, urmata de numele componentei si de clauza PORT MAP, care face maparea porturilor Maparea porturilor consta in realizarea unei asocieri intre porturile formale (adica porturile din declaratia de componenta) si porturile actuale (acele semnale interne sau porturi ale entitatii pe care o modelam ce se conecteaza la porturile formale) Exista reguli precise in limbaj privind tipul si modul (directia) porturilor formale si actuale. – De exemplu, nu se poate conecta un port formal OUT la un port actual IN si nici invers. – Tipurile trebuie sa corespunda (intre portul formal si cel actual) • • Semnalele interne nu au mod, asa ca se pot conecta atit la porturi formale de intrare, cit si de iesire Maparea porturilor se poate face – Pozitional (nu se precizeaza numele portului formal, ci pe pozitia fiecarui port formal, asa cum apare in declaratia de componenta, se precizeaza doar numele portului actual) -> nu se recomanda, poate genera erori greu de detectat ! – Dupa nume: se precizeaza atit numele portului formal, cit si al celui actual • ordinea porturilor formale nu conteaza in acest caz • Sintaxa e intotdeauna: port_formal => port_actual • Simbolul de mapare => are directia de la port formal spre port actual indiferent de directia porturilor

Descrierea structurala • Poate exista si clauza GENERIC MAP, atunci cind se doreste modificarea valorii implicite a unuia sau mai multor parametri generici pentru o anumita instantiere de componenta • Pentru a putea simula descrierea structurala e nevoie sa descriem si entitatile si arhitecturile corespunzatoare componentelor (xor_gate si inv_gate in exemplu). • A se vedea descrierea portilor in exemplul studiat • Daca entitatile asociate lor au acelasi nume ca si componentele si daca exista si o corespondenta intre porturile lor (ca nume, tip si mod) atunci se poate face asanumita legare implicita (default binding) • Daca, la fel ca in exemplul nostru, entitatile au alt nume decit componentele, atunci avem nevoie de o configuratie, care sa faca legarea lor

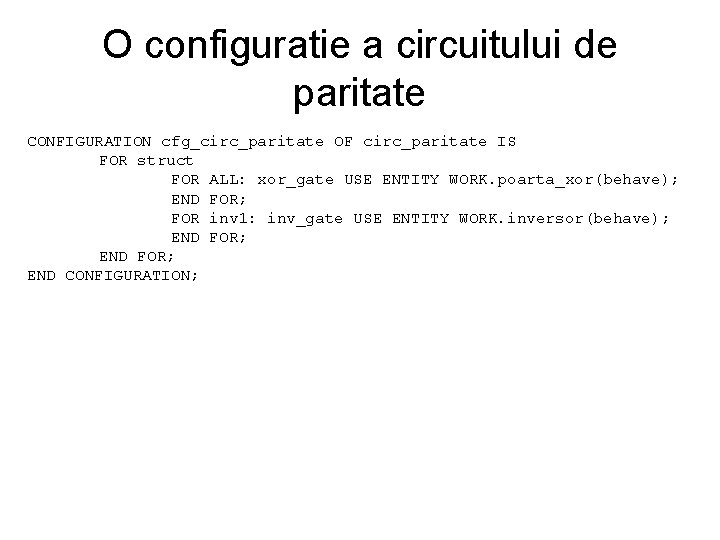

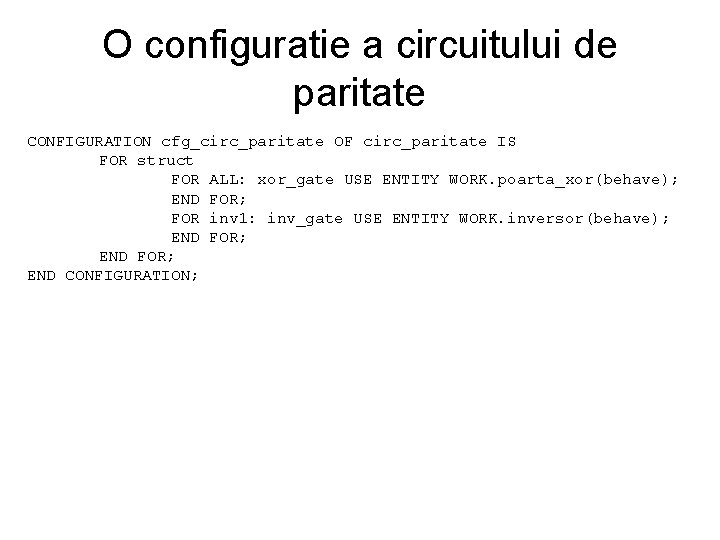

O configuratie a circuitului de paritate CONFIGURATION cfg_circ_paritate OF circ_paritate IS FOR struct FOR ALL: xor_gate USE ENTITY WORK. poarta_xor(behave); END FOR; FOR inv 1: inv_gate USE ENTITY WORK. inversor(behave); END FOR; END CONFIGURATION;

Configuratia • In exemplu avem configuration declaration • Declaratia de configuratia specifica numele configuratiei si entitatea careia configuratia ii este asociata • Apoi se precizeaza arhitectura pentru care se face configuratia • Dupa care loc legarea intre instantierile fiecareia din componentele declarate in arhitectura si o pereche entitate(arhitectura), in acest caz din biblioteca de lucru curenta (avind numele logic WORK) • Daca ar fi diferit numele porturilor componentelor si ale entitatilor asociate lor, ar fi avut loc si o asociere intre aceste nume • Configuratiile se vor studia intr-un capitol ulterior • Limbajul VHDL prezinta o mare varietate de posibilitati in ce priveste aceste asocieri cu ajutorul configuratiilor

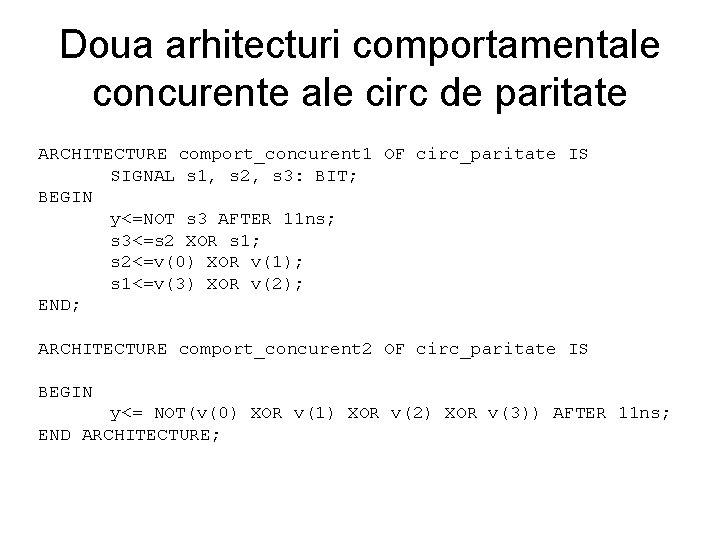

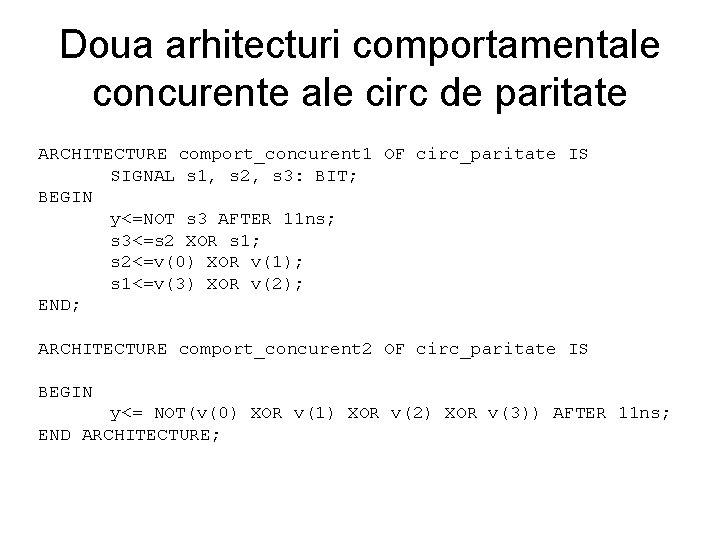

Doua arhitecturi comportamentale concurente ale circ de paritate ARCHITECTURE comport_concurent 1 OF circ_paritate IS SIGNAL s 1, s 2, s 3: BIT; BEGIN y<=NOT s 3 AFTER 11 ns; s 3<=s 2 XOR s 1; s 2<=v(0) XOR v(1); s 1<=v(3) XOR v(2); END; ARCHITECTURE comport_concurent 2 OF circ_paritate IS BEGIN y<= NOT(v(0) XOR v(1) XOR v(2) XOR v(3)) AFTER 11 ns; END ARCHITECTURE;

Descrieri comportamentale concurente • Ambele arhitecturi din exemplu contin doar instructiuni de asignare concurenta de semnal (concurrent signal assignment) • Prima arhitectura e foarte apropiata de descrierea structurala • Instructiunile din corpul arhitecturii sunt concurente, deci ordinea instructiunilor nu conteaza ! • A doua arhitectura e mai simpla (are o singura instructiune) • Modelarea comportmentala concurenta va fi discutata intr-un capitol ulterior

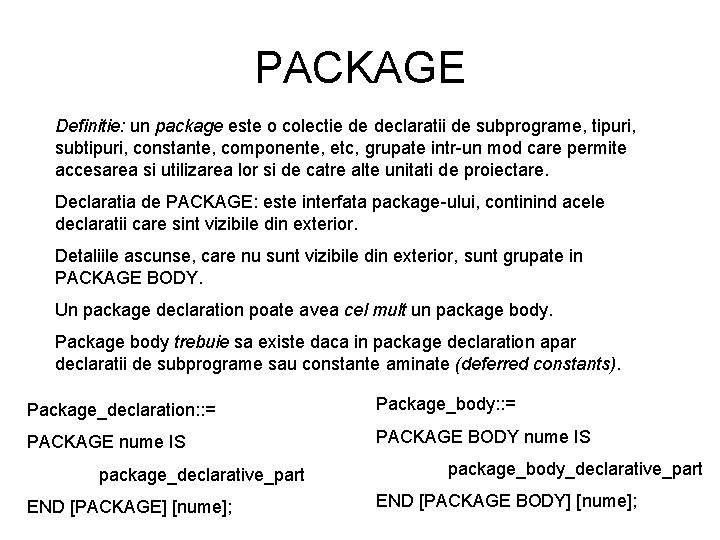

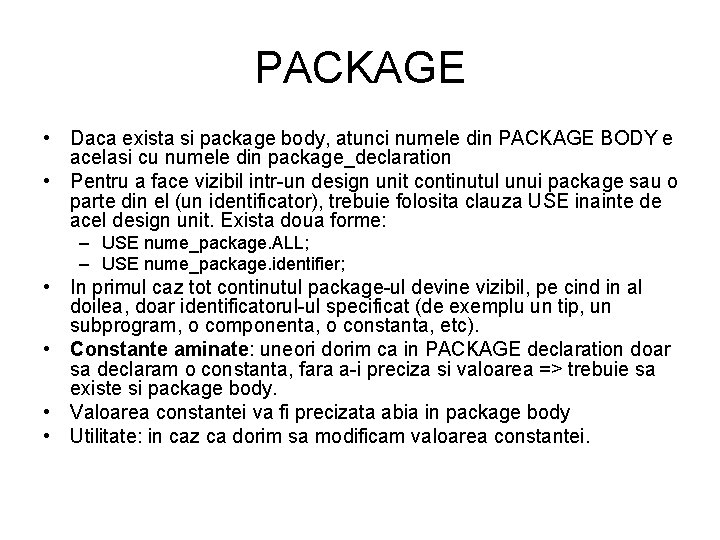

PACKAGE Definitie: un package este o colectie de declaratii de subprograme, tipuri, subtipuri, constante, componente, etc, grupate intr-un mod care permite accesarea si utilizarea lor si de catre alte unitati de proiectare. Declaratia de PACKAGE: este interfata package-ului, continind acele declaratii care sint vizibile din exterior. Detaliile ascunse, care nu sunt vizibile din exterior, sunt grupate in PACKAGE BODY. Un package declaration poate avea cel mult un package body. Package body trebuie sa existe daca in package declaration apar declaratii de subprograme sau constante aminate (deferred constants). Package_declaration: : = Package_body: : = PACKAGE nume IS PACKAGE BODY nume IS package_declarative_part END [PACKAGE] [nume]; package_body_declarative_part END [PACKAGE BODY] [nume];

PACKAGE • Daca exista si package body, atunci numele din PACKAGE BODY e acelasi cu numele din package_declaration • Pentru a face vizibil intr-un design unit continutul unui package sau o parte din el (un identificator), trebuie folosita clauza USE inainte de acel design unit. Exista doua forme: – USE nume_package. ALL; – USE nume_package. identifier; • In primul caz tot continutul package-ul devine vizibil, pe cind in al doilea, doar identificatorul-ul specificat (de exemplu un tip, un subprogram, o componenta, o constanta, etc). • Constante aminate: uneori dorim ca in PACKAGE declaration doar sa declaram o constanta, fara a-i preciza si valoarea => trebuie sa existe si package body. • Valoarea constantei va fi precizata abia in package body • Utilitate: in caz ca dorim sa modificam valoarea constantei.

PACKAGE • Daca valoarea constantei e precizata in package declaration si o modificam, atunci trebuie re-compilat package declaration SI TOATE unitatile de proiectare care il utilizeaza (folosind USE). • Daca valoarea constantei se da doar in package body, atunci la modificarea acesteia NU mai trebuiesc re-compilate unitatile de proiectare care utilizeaza package declaration-ul folosind clauza USE • Ce se pune in package body: – Constante aminate – Definitia subprogramelor declarate in package declaration: un subprogram este doar declarat in package declaration, corpul sau fiind dar in package body. Acesta NU e vizibil in exterior – Alte item-uri ajutatoare: de ex functii sau tipuri ajutatoare, pe care nu vrem sa le facem vizibile in exterior. Exemplu: declaram o functie care aduna doi vectori de biti si returneaza tot un vector de biti. Ca sa realizam functia avem nevoie de functii de conversie de la vectori de biti la intregi si de la intregi la vectori de biti, pe care le consideram auxiliare si le punem doar in package body.