Unit 9 Multiplexers Decoders and Programmable Logic Devices

Unit 9 Multiplexers, Decoders, and Programmable Logic Devices Ku-Yaw Chang canseco@mail. dyu. edu. tw Assistant Professor, Department of Computer Science and Information Engineering Da-Yeh University 2004/03/17 Fundamentals of Logic Design

Contents 9. 1 Introduction 9. 2 9. 3 9. 4 9. 5 9. 6 9. 7 9. 8 2004/03/17 Multiplexers Three-State Buffers Decoders and Encoders Read-Only Memories Programmable Logic Devices Complex Programmable Logic Devices Field Programmable Gate Arrays Fundamentals of Logic Design 2

Introduction Integrated Circuits (ICs) n n SSI : Small-scale integration MSI : Medium-scale integration LSI : Large-scale integration VLSI : Very-large-scale integration 2004/03/17 Fundamentals of Logic Design 3

Introduction SSI n n NAND, NOR, AND, OR, inverters, flip-flops 1 to 4 gates, six inverters, 1 or 2 flip-flops MSI n n adders, multiplexers, decoders, register, counters 12 to 100 gates LSI n 100 to a few thousand gates VLSI : Very-large-scale integration n Several thousand gates or more 2004/03/17 Fundamentals of Logic Design 4

IC classification According to how many transistors were integrated on one single chip: n n n SSI (Small Scale Integration) : 64 MSI (Medium Scale Integration): 1, 024 LSI (Large Scale Integration) : 65, 000 VLSI (Very Large Scale Integration) more than 65000 SVLSI (Super Very Large Scale Integration) : > 500, 000 2004/03/17 Fundamentals of Logic Design 5

Introduction Multiplexers Decoders/Encoders Three-state buffers ROMs PLDs PLAs PALs CPLDs FPGAs 2004/03/17 Fundamentals of Logic Design 6

Contents 9. 1 Introduction 9. 2 Multiplexers 9. 3 9. 4 9. 5 9. 6 9. 7 9. 8 2004/03/17 Three-State Buffers Decoders and Encoders Read-Only Memories Programmable Logic Devices Complex Programmable Logic Devices Field Programmable Gate Arrays Fundamentals of Logic Design 7

Multiplexers Also called data selector Abbreviated as MUX Consist of n n A group of data inputs A group of control inputs To select one of the data inputs and connect it to the output terminal 2004/03/17 Fundamentals of Logic Design 8

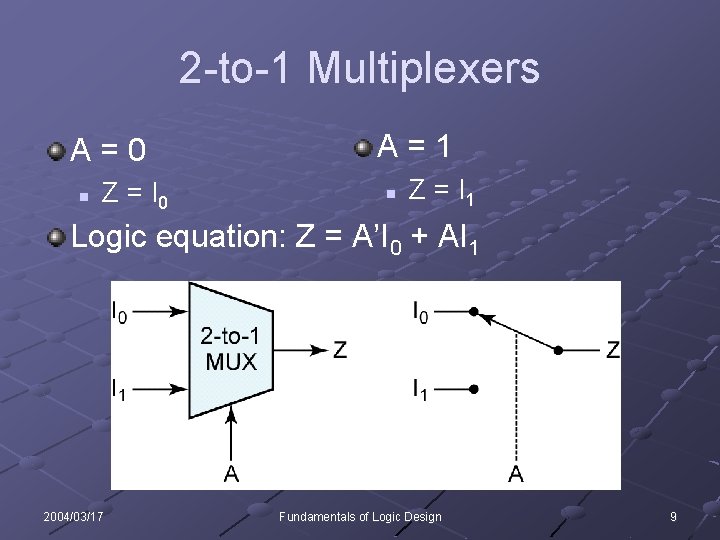

2 -to-1 Multiplexers A=0 n Z = I 0 A=1 n Z = I 1 Logic equation: Z = A’I 0 + AI 1 2004/03/17 Fundamentals of Logic Design 9

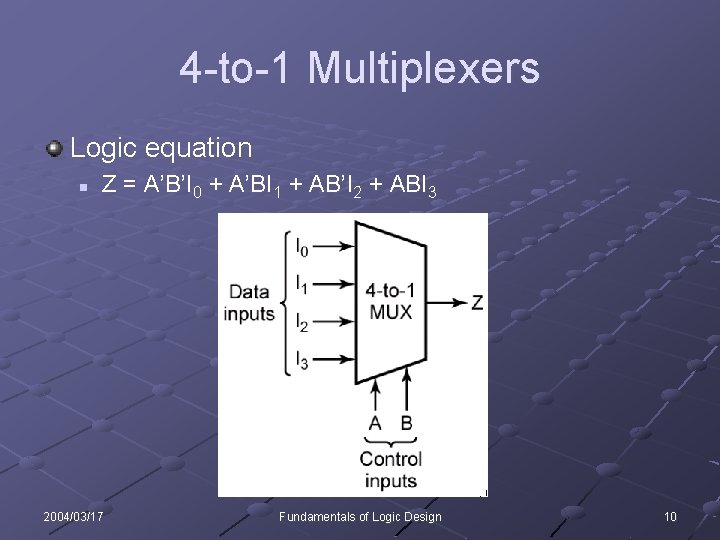

4 -to-1 Multiplexers Logic equation n Z = A’B’I 0 + A’BI 1 + AB’I 2 + ABI 3 2004/03/17 Fundamentals of Logic Design 10

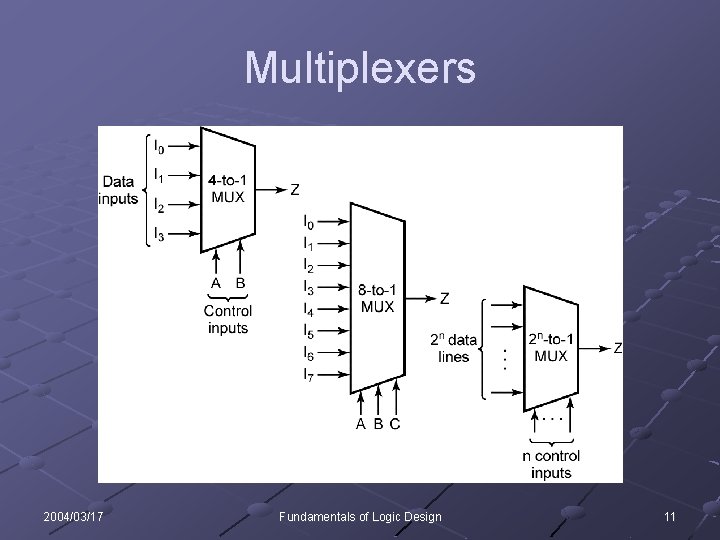

Multiplexers 2004/03/17 Fundamentals of Logic Design 11

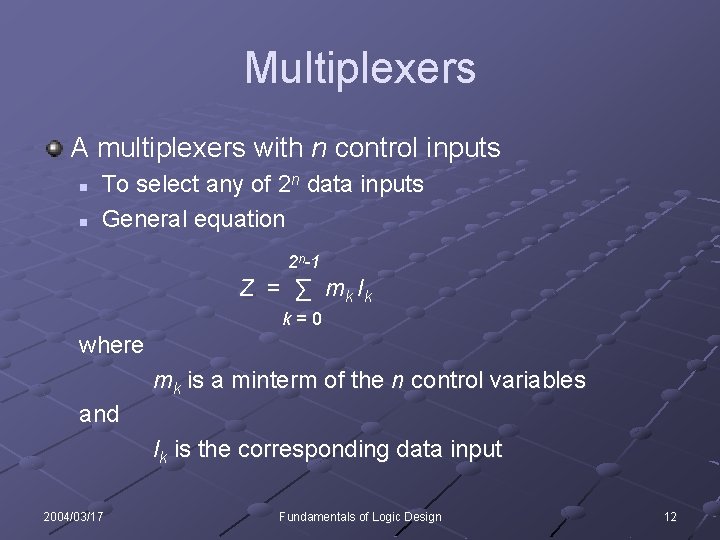

Multiplexers A multiplexers with n control inputs n n To select any of 2 n data inputs General equation 2 n-1 Z = ∑ mk I k k=0 where mk is a minterm of the n control variables and Ik is the corresponding data input 2004/03/17 Fundamentals of Logic Design 12

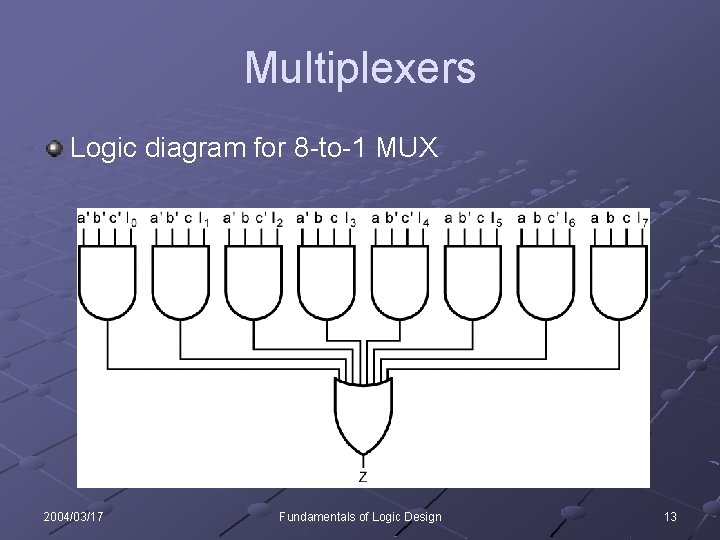

Multiplexers Logic diagram for 8 -to-1 MUX 2004/03/17 Fundamentals of Logic Design 13

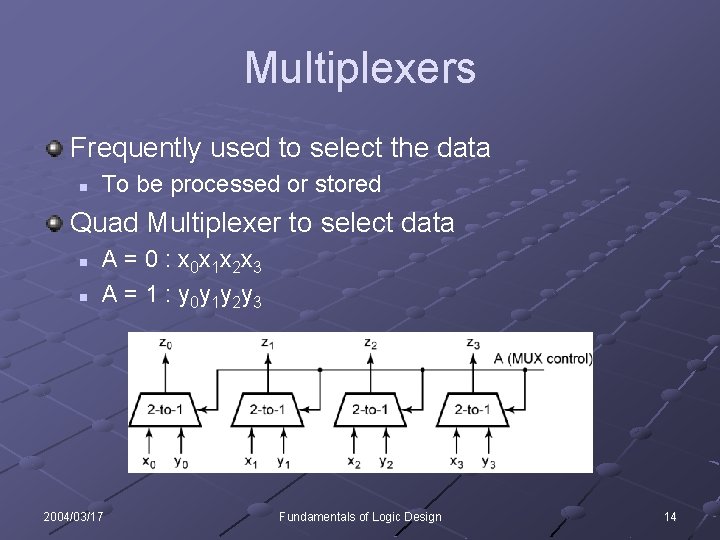

Multiplexers Frequently used to select the data n To be processed or stored Quad Multiplexer to select data n n A = 0 : x 0 x 1 x 2 x 3 A = 1 : y 0 y 1 y 2 y 3 2004/03/17 Fundamentals of Logic Design 14

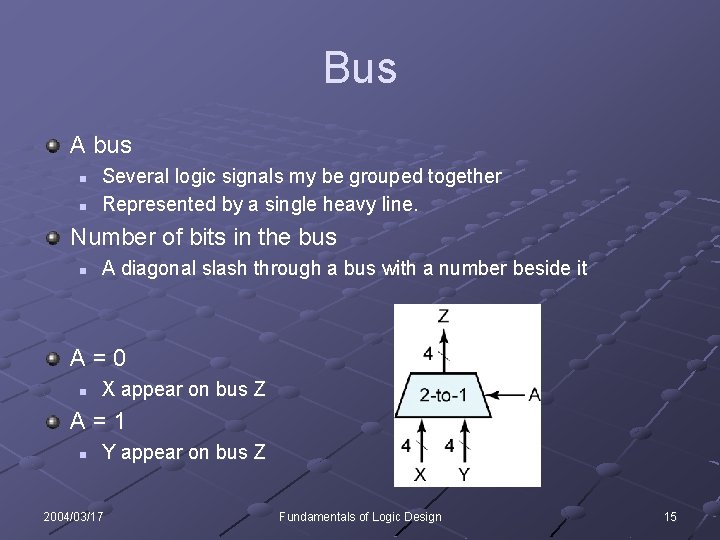

Bus A bus n n Several logic signals my be grouped together Represented by a single heavy line. Number of bits in the bus n A diagonal slash through a bus with a number beside it A=0 n X appear on bus Z A=1 n Y appear on bus Z 2004/03/17 Fundamentals of Logic Design 15

- Slides: 15