Unit 6 Introduction to Logic Design with Verilog

- Slides: 32

Unit 6 Introduction to Logic Design with Verilog Department of Communication Engineering, NCTU 1

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu The purpose of using hardware description languages (HDLs) q q q Describe the functionality of a circuit with texts Simulate the functionality with the texts Synthesize the texts into circuits n q q Logic, timing and power minimizations Verify for functionality, timing and fault coverage of the circuits Transform the design between different technologies Document the designs Serve as a medium for integrating intellectual property (IP) from a variety of sources Department of Communication Engineering, NCTU 2

Digital CAS n n Unit 3 Introduction to Verilog Sau-Hsuan Wu Verilog primitives and design encapsulation Primitives are the most basic functional objects that can be used to compose a design q There are 26 predefined functional models of common combinational logic gates called Primitives: n n N-input: and, nand, or, nor, xor and xnor and (OUT, IN 1, …, INN); nand (OUT, IN 1, …, INN); … Department of Communication Engineering, NCTU 3

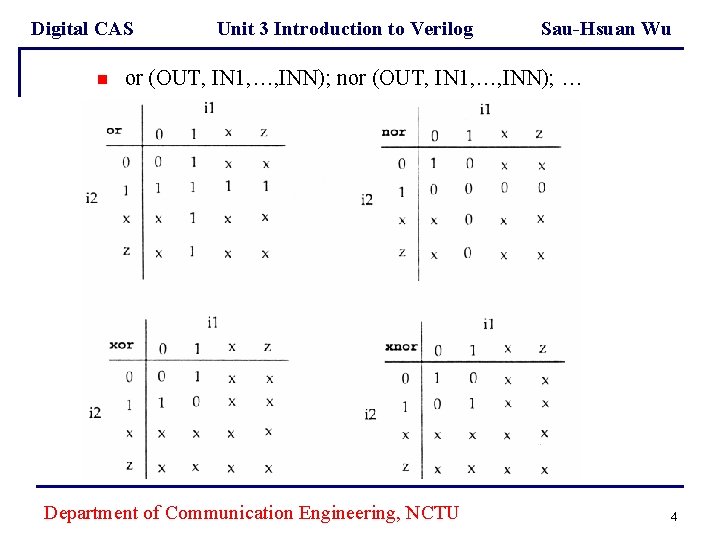

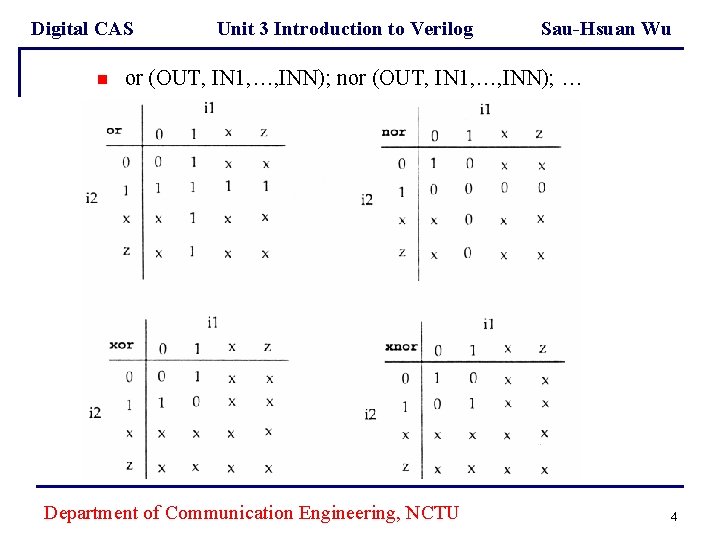

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu or (OUT, IN 1, …, INN); nor (OUT, IN 1, …, INN); … Department of Communication Engineering, NCTU 4

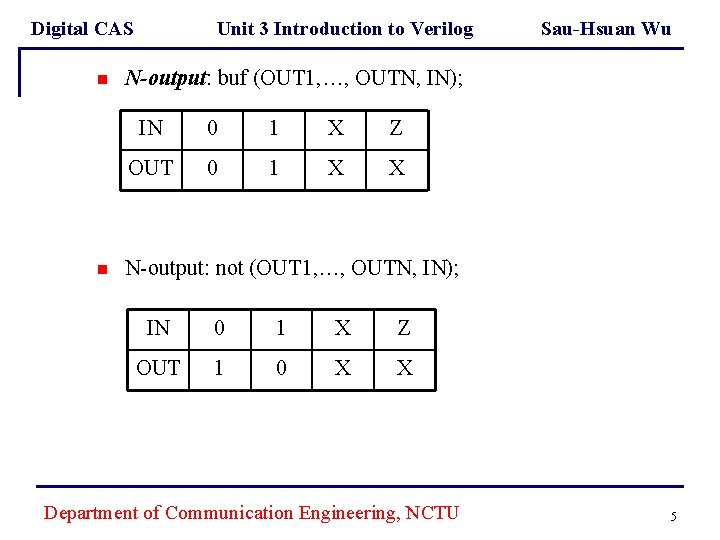

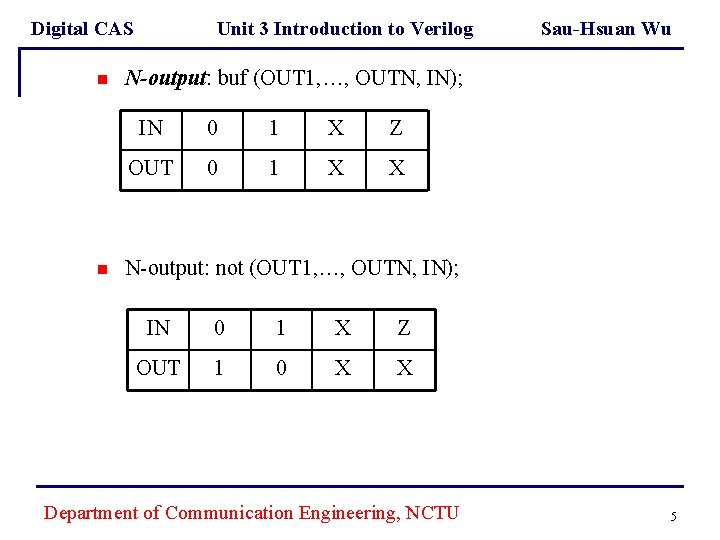

Digital CAS n n Unit 3 Introduction to Verilog Sau-Hsuan Wu N-output: buf (OUT 1, …, OUTN, IN); IN 0 1 X Z OUT 0 1 X X N-output: not (OUT 1, …, OUTN, IN); IN 0 1 X Z OUT 1 0 X X Department of Communication Engineering, NCTU 5

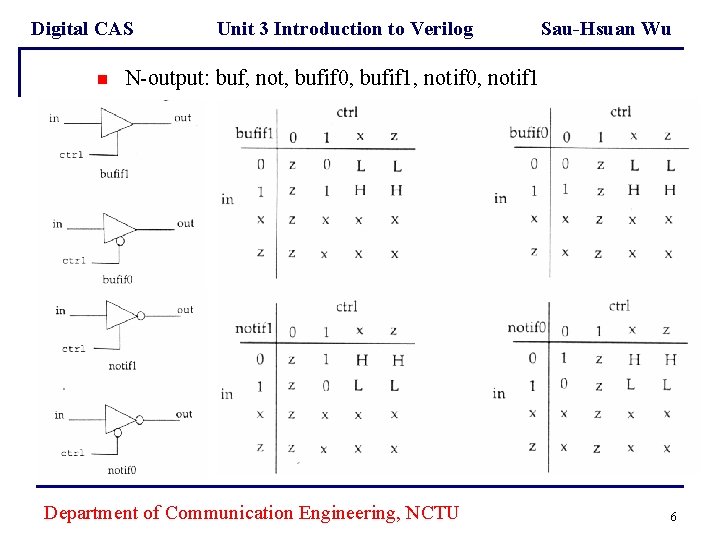

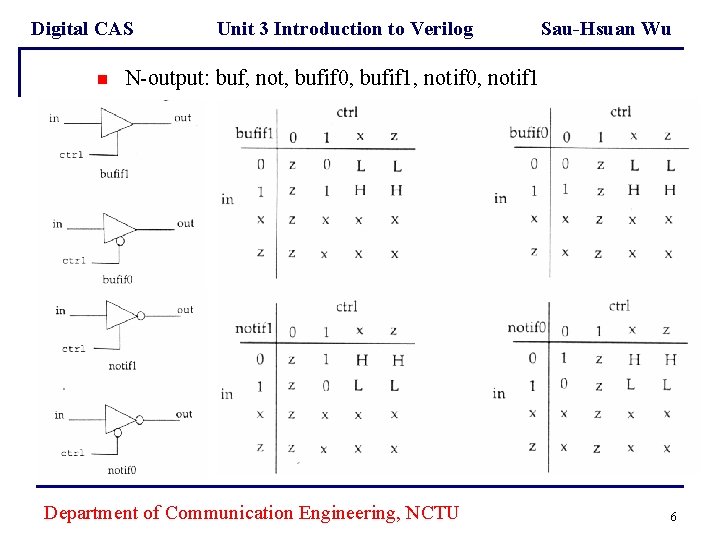

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu N-output: buf, not, bufif 0, bufif 1, notif 0, notif 1 Department of Communication Engineering, NCTU 6

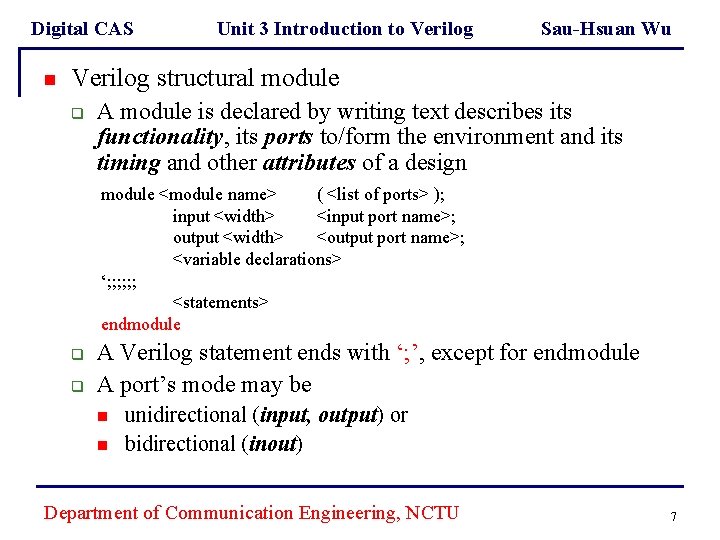

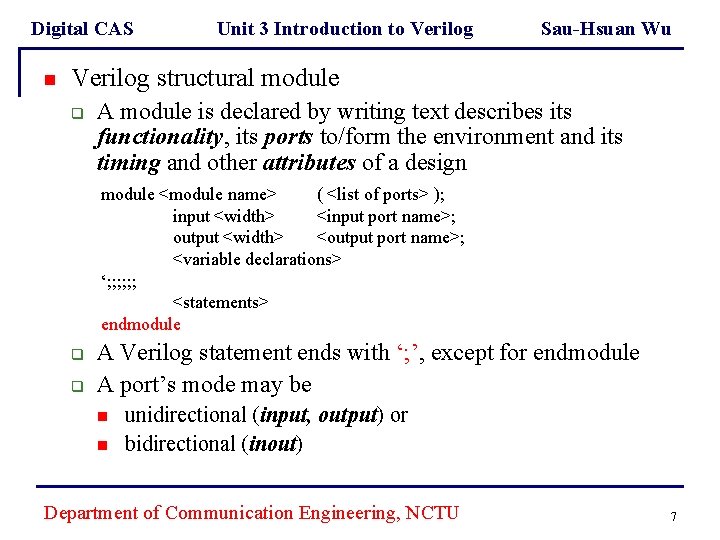

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Verilog structural module q A module is declared by writing text describes its functionality, its ports to/form the environment and its timing and other attributes of a design module <module name> ( <list of ports> ); input <width> <input port name>; output <width> <output port name>; <variable declarations> ‘; ; ; <statements> endmodule q q A Verilog statement ends with ‘; ’, except for endmodule A port’s mode may be n n unidirectional (input, output) or bidirectional (inout) Department of Communication Engineering, NCTU 7

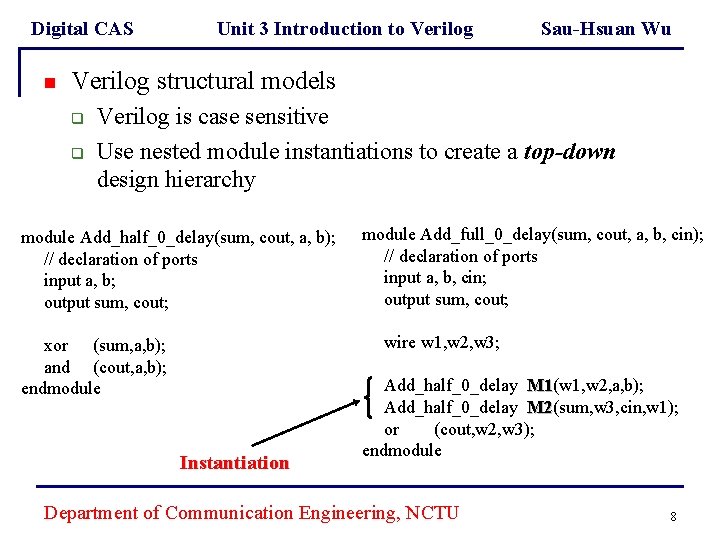

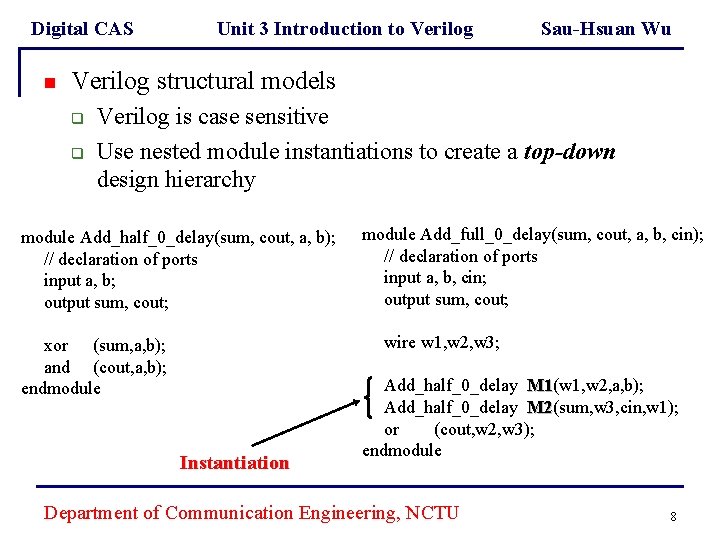

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Verilog structural models q q Verilog is case sensitive Use nested module instantiations to create a top-down design hierarchy module Add_half_0_delay(sum, cout, a, b); // declaration of ports input a, b; output sum, cout; module Add_full_0_delay(sum, cout, a, b, cin); // declaration of ports input a, b, cin; output sum, cout; xor (sum, a, b); and (cout, a, b); endmodule wire w 1, w 2, w 3; Instantiation Add_half_0_delay M 1(w 1, w 2, a, b); M 1 Add_half_0_delay M 2(sum, w 3, cin, w 1); M 2 or (cout, w 2, w 3); endmodule Department of Communication Engineering, NCTU 8

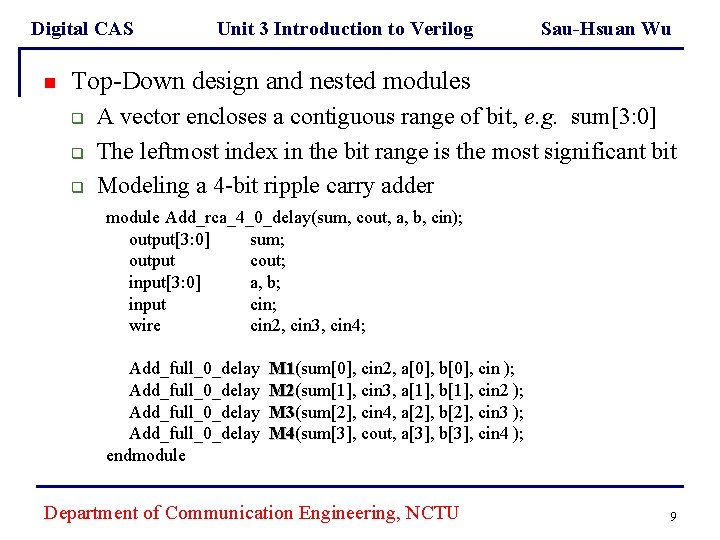

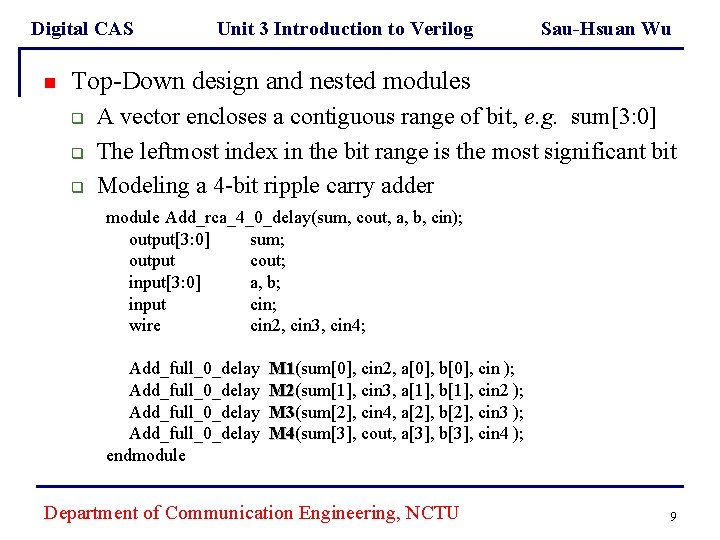

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Top-Down design and nested modules q q q A vector encloses a contiguous range of bit, e. g. sum[3: 0] The leftmost index in the bit range is the most significant bit Modeling a 4 -bit ripple carry adder module Add_rca_4_0_delay(sum, cout, a, b, cin); output[3: 0] sum; output cout; input[3: 0] a, b; input cin; wire cin 2, cin 3, cin 4; Add_full_0_delay M 1(sum[0], cin 2, a[0], b[0], cin ); M 1 Add_full_0_delay M 2(sum[1], cin 3, a[1], b[1], cin 2 ); M 2 Add_full_0_delay M 3(sum[2], cin 4, a[2], b[2], cin 3 ); M 3 Add_full_0_delay M 4(sum[3], cout, a[3], b[3], cin 4 ); M 4 endmodule Department of Communication Engineering, NCTU 9

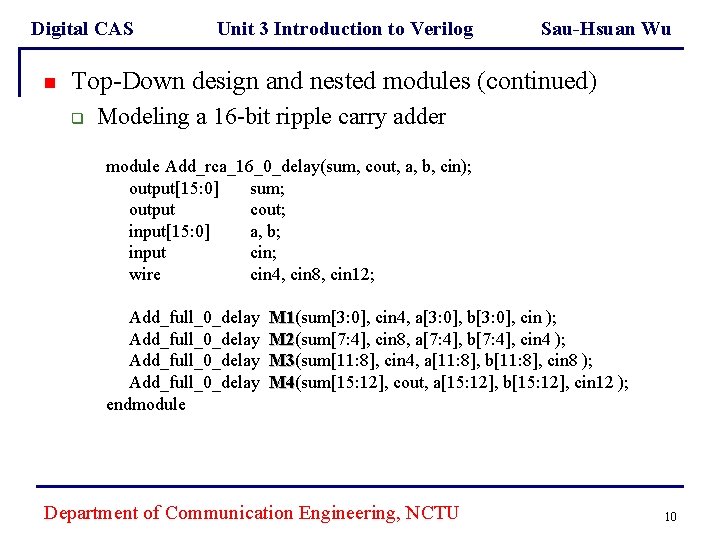

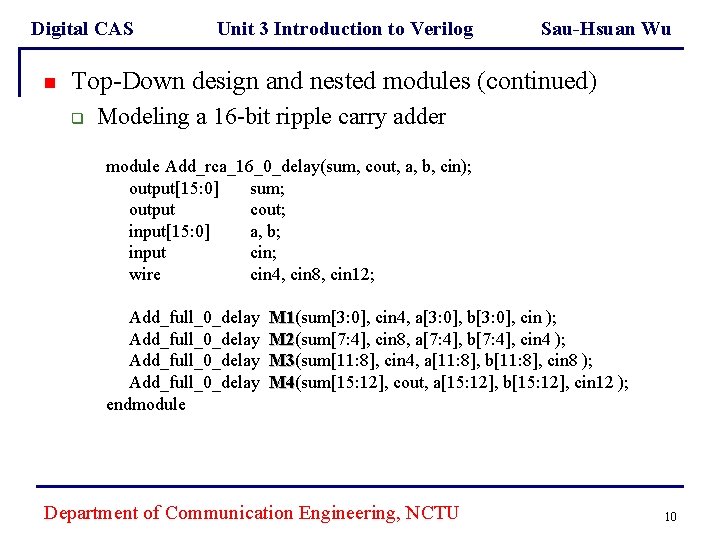

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Top-Down design and nested modules (continued) q Modeling a 16 -bit ripple carry adder module Add_rca_16_0_delay(sum, cout, a, b, cin); output[15: 0] sum; output cout; input[15: 0] a, b; input cin; wire cin 4, cin 8, cin 12; Add_full_0_delay M 1(sum[3: 0], cin 4, a[3: 0], b[3: 0], cin ); M 1 Add_full_0_delay M 2(sum[7: 4], cin 8, a[7: 4], b[7: 4], cin 4 ); M 2 Add_full_0_delay M 3(sum[11: 8], cin 4, a[11: 8], b[11: 8], cin 8 ); M 3 Add_full_0_delay M 4(sum[15: 12], cout, a[15: 12], b[15: 12], cin 12 ); M 4 endmodule Department of Communication Engineering, NCTU 10

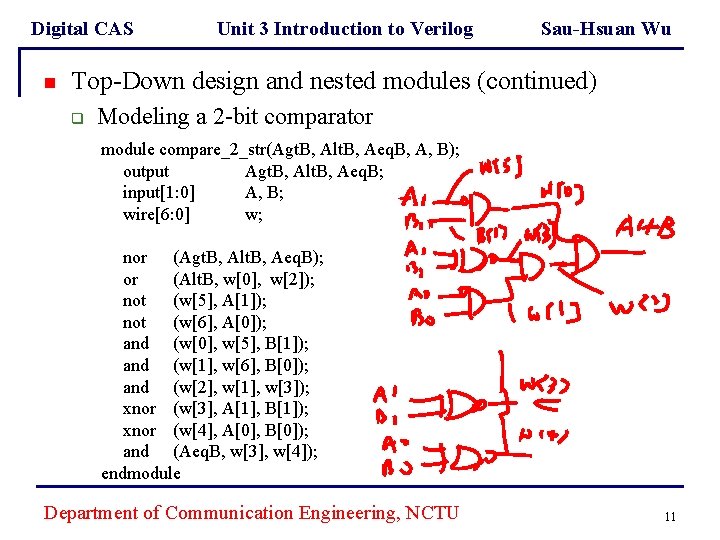

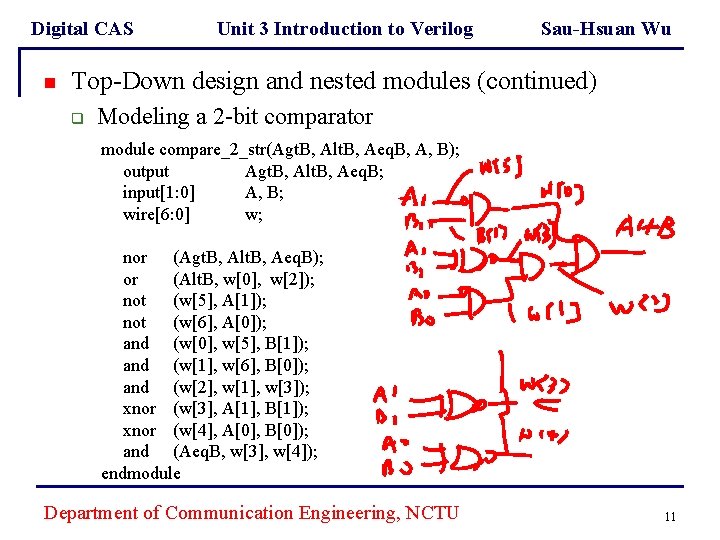

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Top-Down design and nested modules (continued) q Modeling a 2 -bit comparator module compare_2_str(Agt. B, Alt. B, Aeq. B, A, B); output Agt. B, Alt. B, Aeq. B; input[1: 0] A, B; wire[6: 0] w; nor (Agt. B, Alt. B, Aeq. B); or (Alt. B, w[0], w[2]); not (w[5], A[1]); not (w[6], A[0]); and (w[0], w[5], B[1]); and (w[1], w[6], B[0]); and (w[2], w[1], w[3]); xnor (w[3], A[1], B[1]); xnor (w[4], A[0], B[0]); and (Aeq. B, w[3], w[4]); endmodule Department of Communication Engineering, NCTU 11

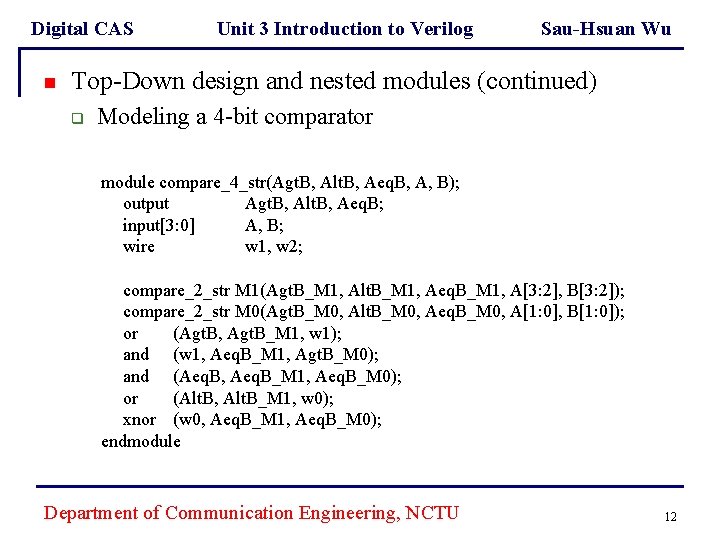

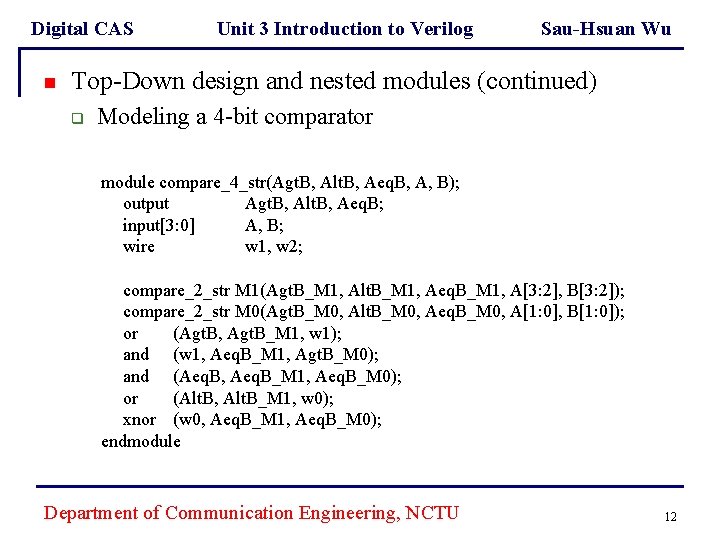

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Top-Down design and nested modules (continued) q Modeling a 4 -bit comparator module compare_4_str(Agt. B, Alt. B, Aeq. B, A, B); output Agt. B, Alt. B, Aeq. B; input[3: 0] A, B; wire w 1, w 2; compare_2_str M 1(Agt. B_M 1, Alt. B_M 1, Aeq. B_M 1, A[3: 2], B[3: 2]); compare_2_str M 0(Agt. B_M 0, Alt. B_M 0, Aeq. B_M 0, A[1: 0], B[1: 0]); or (Agt. B, Agt. B_M 1, w 1); and (w 1, Aeq. B_M 1, Agt. B_M 0); and (Aeq. B, Aeq. B_M 1, Aeq. B_M 0); or (Alt. B, Alt. B_M 1, w 0); xnor (w 0, Aeq. B_M 1, Aeq. B_M 0); endmodule Department of Communication Engineering, NCTU 12

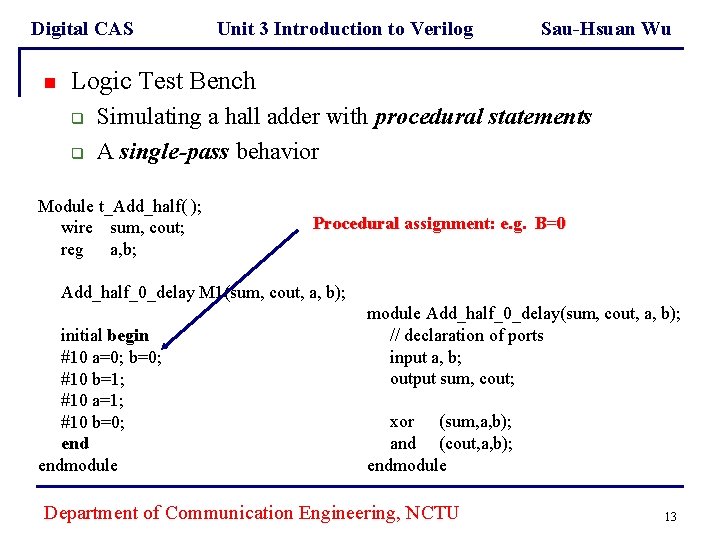

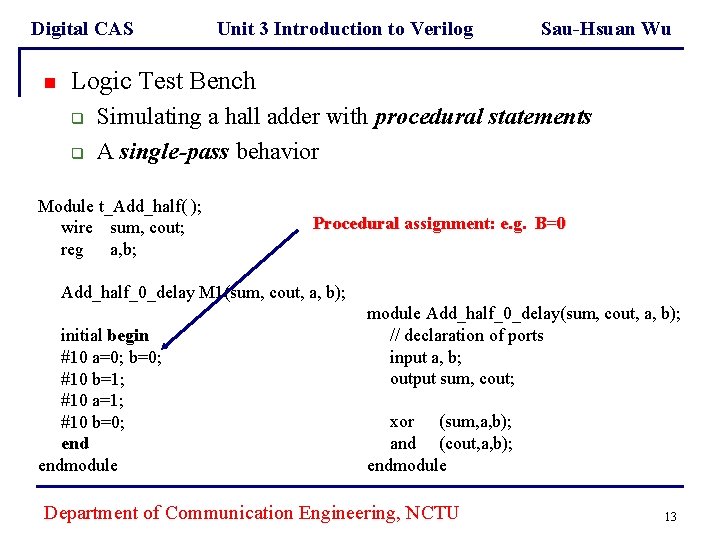

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Logic Test Bench q q Simulating a hall adder with procedural statements A single-pass behavior Module t_Add_half( ); wire sum, cout; reg a, b; Procedural assignment: e. g. B=0 Add_half_0_delay M 1(sum, cout, a, b); initial begin #10 a=0; b=0; #10 b=1; #10 a=1; #10 b=0; endmodule Add_half_0_delay(sum, cout, a, b); // declaration of ports input a, b; output sum, cout; xor (sum, a, b); and (cout, a, b); endmodule Department of Communication Engineering, NCTU 13

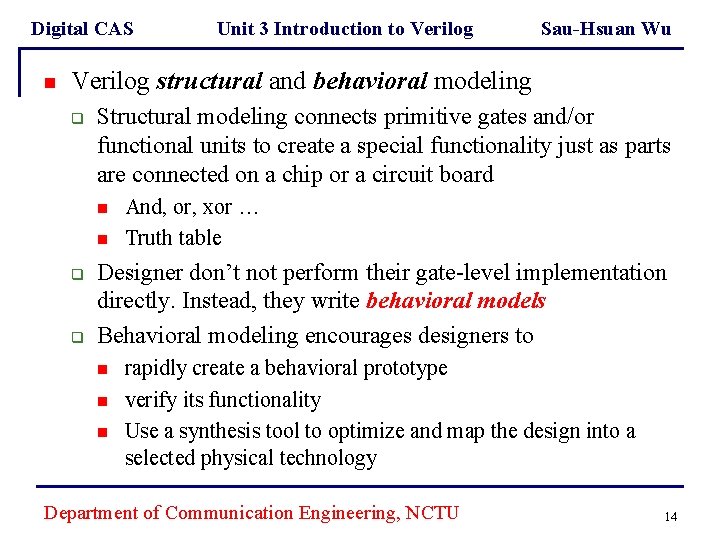

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Verilog structural and behavioral modeling q Structural modeling connects primitive gates and/or functional units to create a special functionality just as parts are connected on a chip or a circuit board n n q q And, or, xor … Truth table Designer don’t not perform their gate-level implementation directly. Instead, they write behavioral models Behavioral modeling encourages designers to n n n rapidly create a behavioral prototype verify its functionality Use a synthesis tool to optimize and map the design into a selected physical technology Department of Communication Engineering, NCTU 14

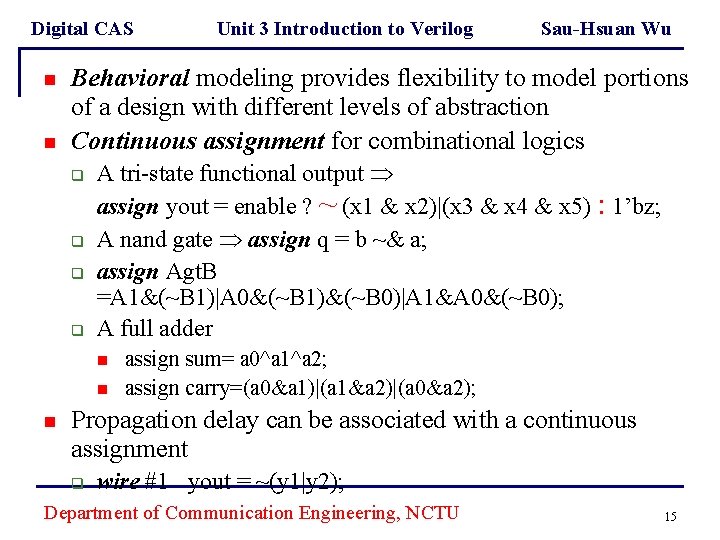

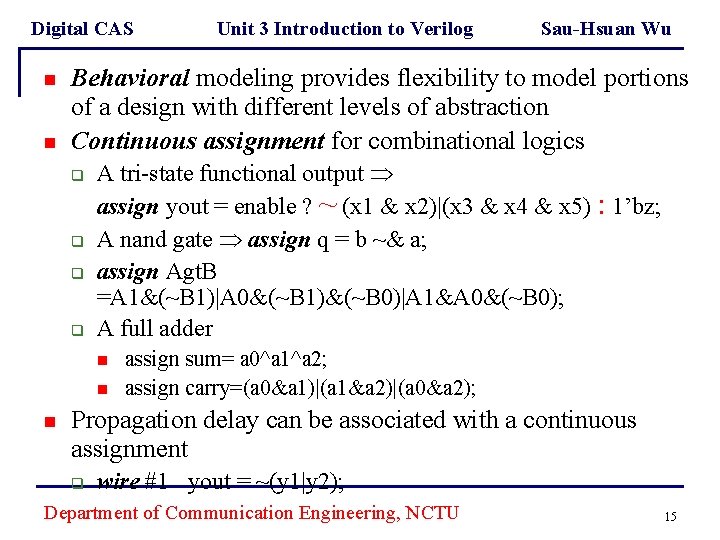

Digital CAS n n Sau-Hsuan Wu Behavioral modeling provides flexibility to model portions of a design with different levels of abstraction Continuous assignment for combinational logics q q A tri-state functional output assign yout = enable ? ~ (x 1 & x 2)|(x 3 & x 4 & x 5) : 1’bz; A nand gate assign q = b ~& a; assign Agt. B =A 1&(~B 1)|A 0&(~B 1)&(~B 0)|A 1&A 0&(~B 0); A full adder n n n Unit 3 Introduction to Verilog assign sum= a 0^a 1^a 2; assign carry=(a 0&a 1)|(a 1&a 2)|(a 0&a 2); Propagation delay can be associated with a continuous assignment q wire #1 yout = ~(y 1|y 2); Department of Communication Engineering, NCTU 15

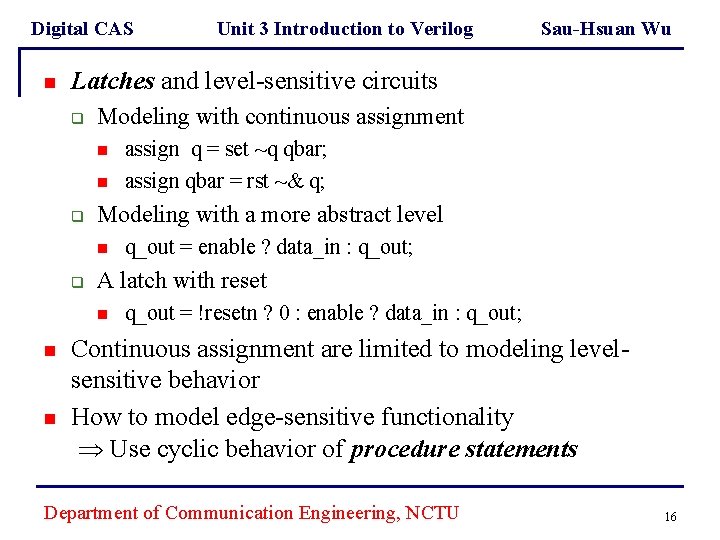

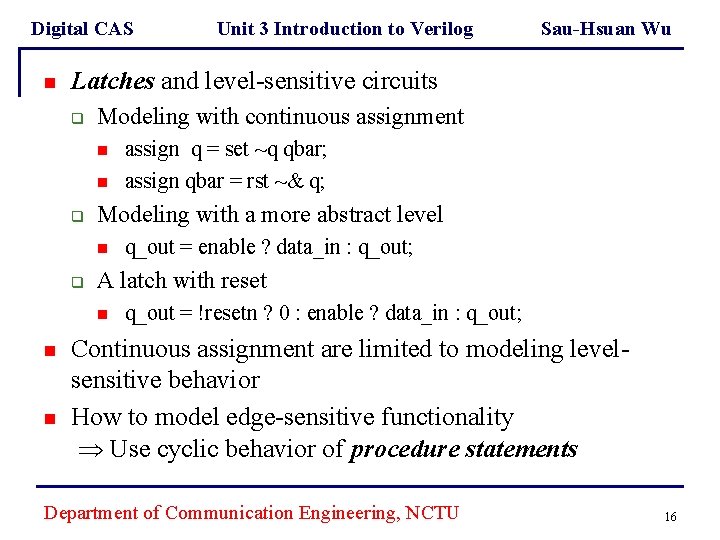

Digital CAS n Modeling with continuous assignment n n q q assign q = set ~q qbar; assign qbar = rst ~& q; Modeling with a more abstract level n q_out = enable ? data_in : q_out; A latch with reset n n Sau-Hsuan Wu Latches and level-sensitive circuits q n Unit 3 Introduction to Verilog q_out = !resetn ? 0 : enable ? data_in : q_out; Continuous assignment are limited to modeling levelsensitive behavior How to model edge-sensitive functionality Use cyclic behavior of procedure statements Department of Communication Engineering, NCTU 16

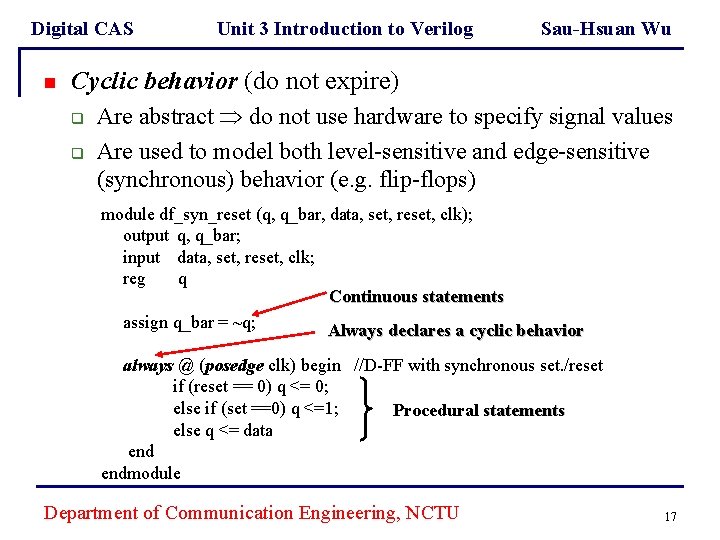

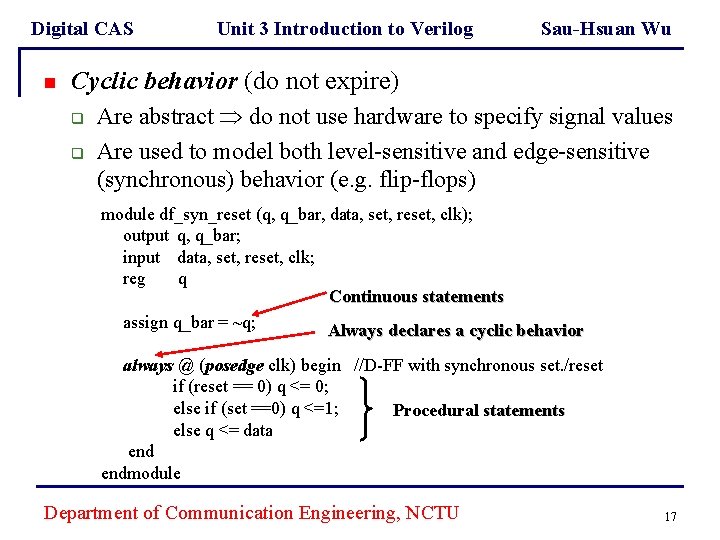

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Cyclic behavior (do not expire) q q Are abstract do not use hardware to specify signal values Are used to model both level-sensitive and edge-sensitive (synchronous) behavior (e. g. flip-flops) module df_syn_reset (q, q_bar, data, set, reset, clk); output q, q_bar; input data, set, reset, clk; reg q Continuous statements assign q_bar = ~q; Always declares a cyclic behavior always @ (posedge clk) begin //D-FF with synchronous set. /reset if (reset == 0) q <= 0; else if (set ==0) q <=1; Procedural statements else q <= data endmodule Department of Communication Engineering, NCTU 17

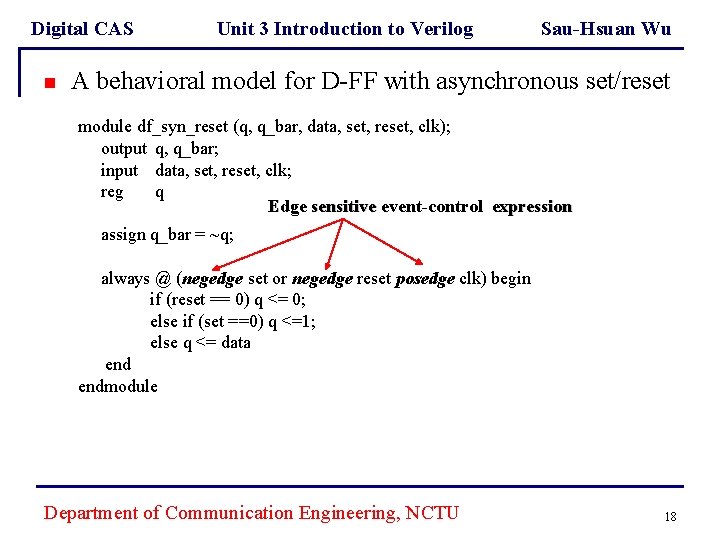

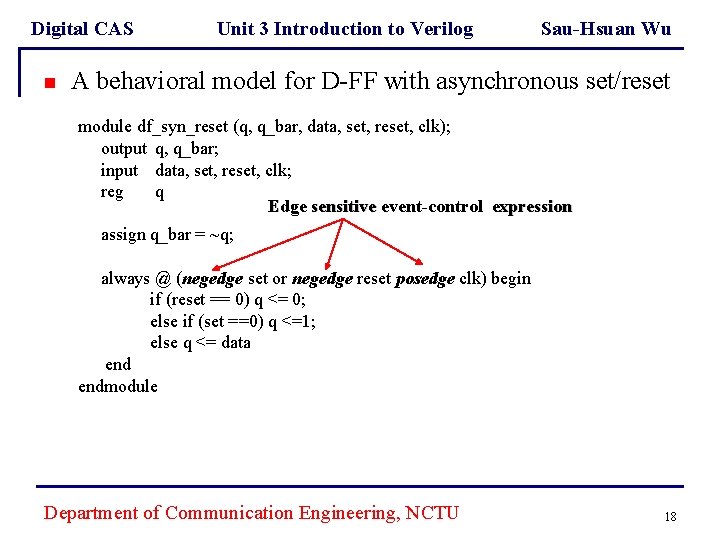

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu A behavioral model for D-FF with asynchronous set/reset module df_syn_reset (q, q_bar, data, set, reset, clk); output q, q_bar; input data, set, reset, clk; reg q Edge sensitive event-control expression assign q_bar = ~q; always @ (negedge set or negedge reset posedge clk) begin if (reset == 0) q <= 0; else if (set ==0) q <=1; else q <= data endmodule Department of Communication Engineering, NCTU 18

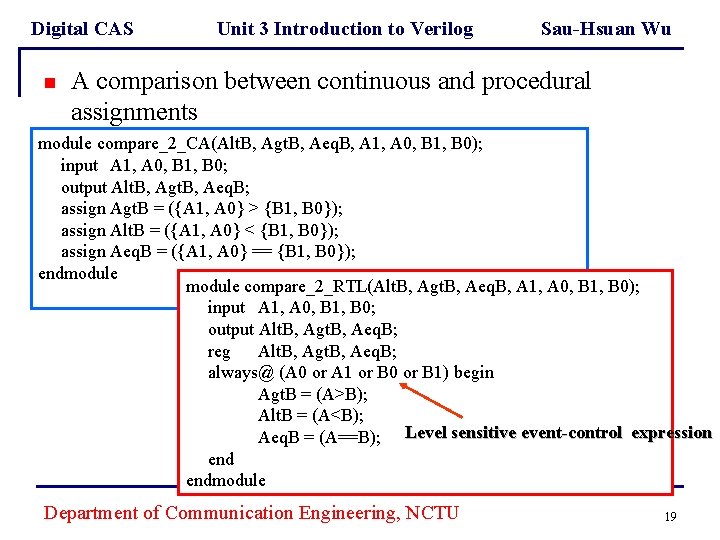

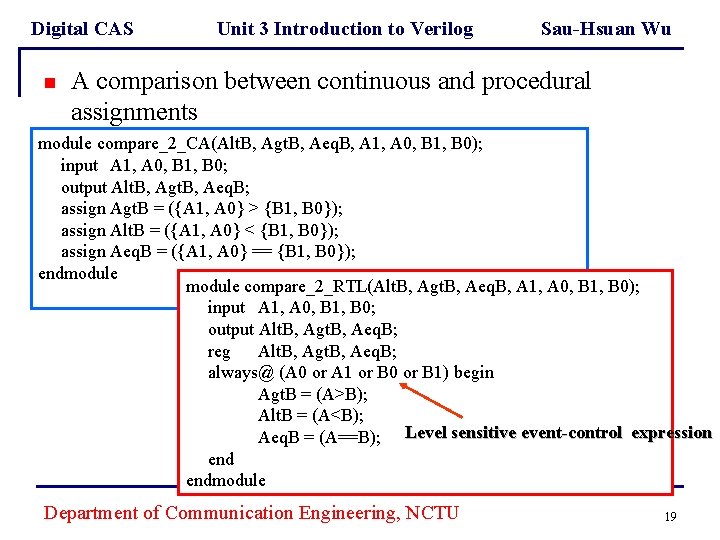

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu A comparison between continuous and procedural assignments module compare_2_CA(Alt. B, Agt. B, Aeq. B, A 1, A 0, B 1, B 0); input A 1, A 0, B 1, B 0; output Alt. B, Agt. B, Aeq. B; assign Agt. B = ({A 1, A 0} > {B 1, B 0}); assign Alt. B = ({A 1, A 0} < {B 1, B 0}); assign Aeq. B = ({A 1, A 0} == {B 1, B 0}); endmodule compare_2_RTL(Alt. B, Agt. B, Aeq. B, A 1, A 0, B 1, B 0); input A 1, A 0, B 1, B 0; output Alt. B, Agt. B, Aeq. B; reg Alt. B, Agt. B, Aeq. B; always@ (A 0 or A 1 or B 0 or B 1) begin Agt. B = (A>B); Alt. B = (A<B); Aeq. B = (A==B); Level sensitive event-control expression endmodule Department of Communication Engineering, NCTU 19

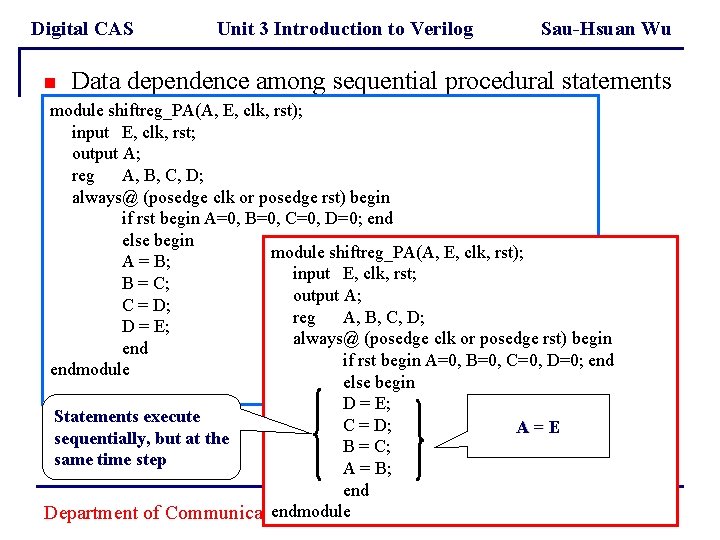

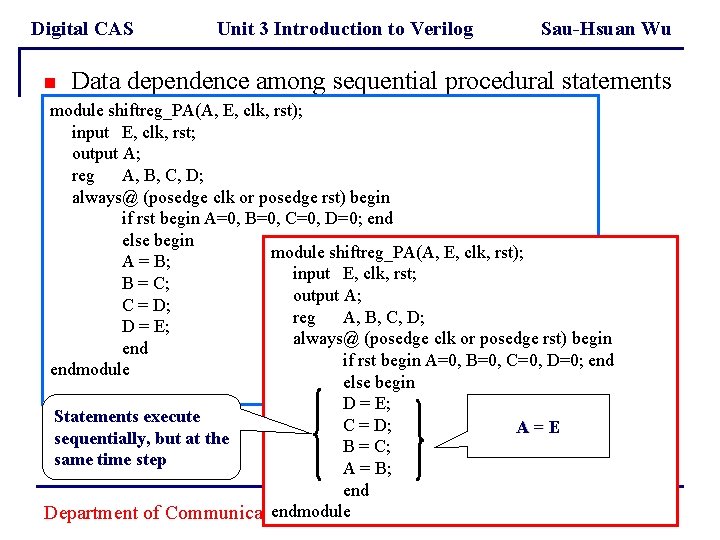

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Data dependence among sequential procedural statements module shiftreg_PA(A, E, clk, rst); input E, clk, rst; output A; reg A, B, C, D; always@ (posedge clk or posedge rst) begin if rst begin A=0, B=0, C=0, D=0; end else begin module shiftreg_PA(A, E, clk, rst); A = B; input E, clk, rst; B = C; output A; C = D; reg A, B, C, D; D = E; always@ (posedge clk or posedge rst) begin end if rst begin A=0, B=0, C=0, D=0; endmodule else begin D = E; Statements execute C = D; A=E sequentially, but at the B = C; same time step A = B; endmodule Department of Communication Engineering, NCTU 20

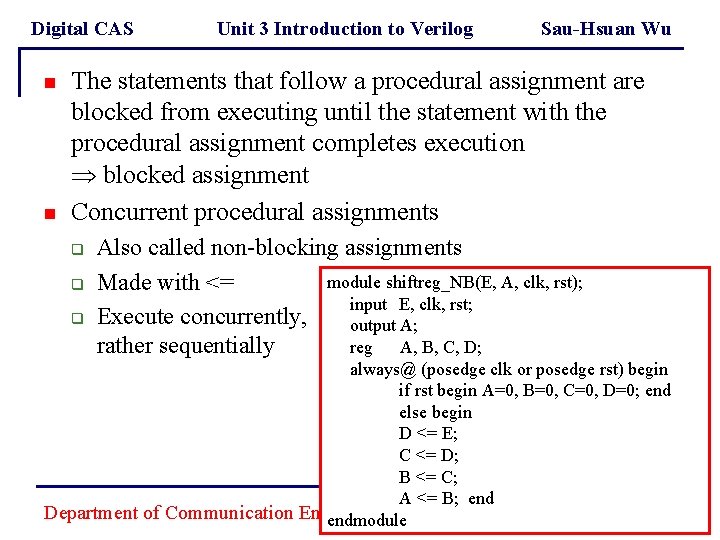

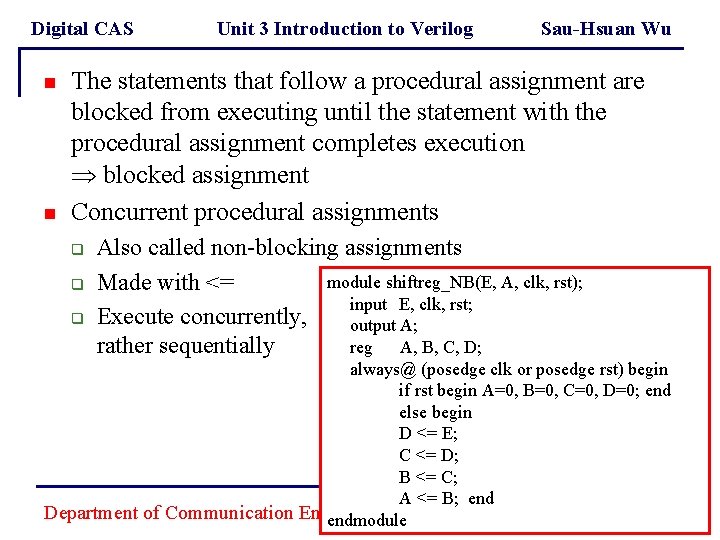

Digital CAS n n Unit 3 Introduction to Verilog Sau-Hsuan Wu The statements that follow a procedural assignment are blocked from executing until the statement with the procedural assignment completes execution blocked assignment Concurrent procedural assignments q q q Also called non-blocking assignments module shiftreg_NB(E, A, clk, rst); Made with <= input E, clk, rst; Execute concurrently, output A; rather sequentially reg A, B, C, D; always@ (posedge clk or posedge rst) begin if rst begin A=0, B=0, C=0, D=0; end else begin D <= E; C <= D; B <= C; A <= B; end Department of Communication Engineering, NCTU 21 endmodule

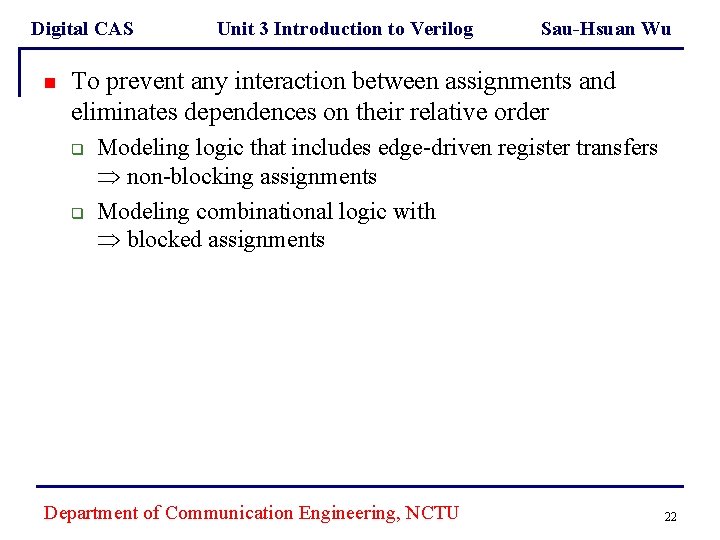

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu To prevent any interaction between assignments and eliminates dependences on their relative order q q Modeling logic that includes edge-driven register transfers non-blocking assignments Modeling combinational logic with blocked assignments Department of Communication Engineering, NCTU 22

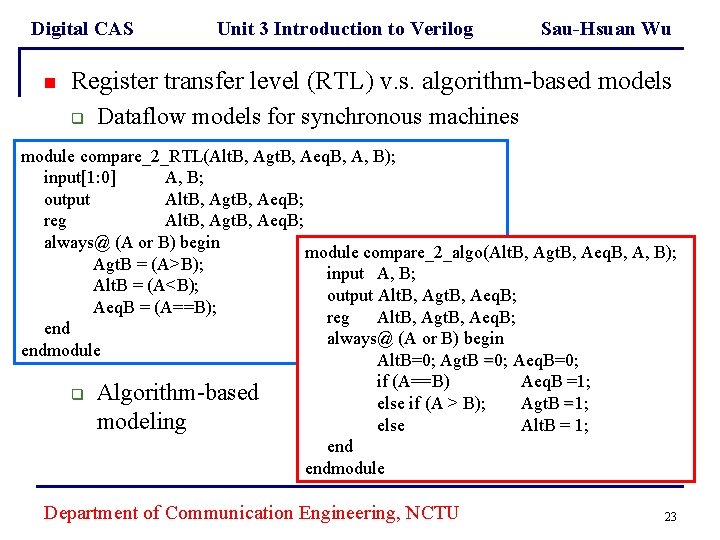

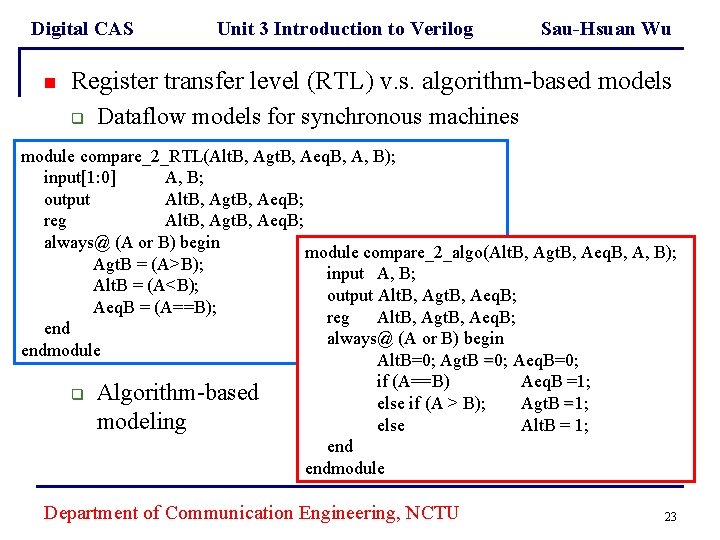

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Register transfer level (RTL) v. s. algorithm-based models q Dataflow models for synchronous machines module compare_2_RTL(Alt. B, Agt. B, Aeq. B, A, B); input[1: 0] A, B; output Alt. B, Agt. B, Aeq. B; reg Alt. B, Agt. B, Aeq. B; always@ (A or B) begin module compare_2_algo(Alt. B, Agt. B, Aeq. B, A, B); Agt. B = (A>B); input A, B; Alt. B = (A<B); output Alt. B, Agt. B, Aeq. B; Aeq. B = (A==B); reg Alt. B, Agt. B, Aeq. B; end always@ (A or B) begin endmodule Alt. B=0; Agt. B =0; Aeq. B=0; = if (A==B) Aeq. B =1; q Algorithm-based else if (A > B); Agt. B =1; = modeling else Alt. B = 1; endmodule Department of Communication Engineering, NCTU 23

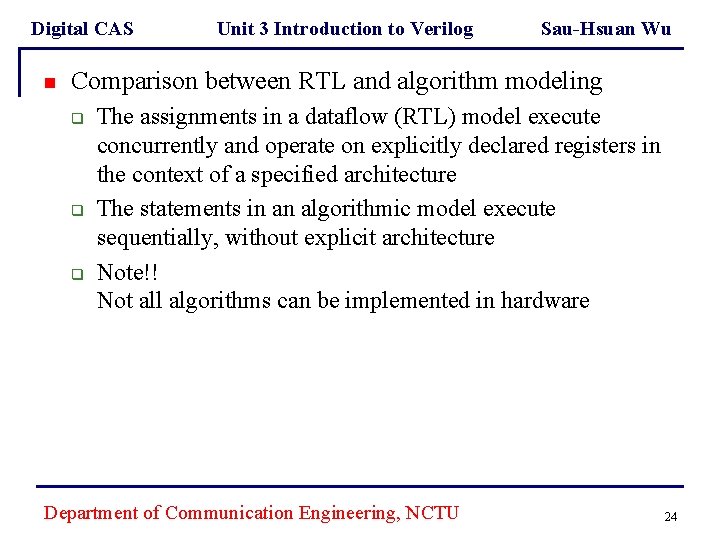

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Comparison between RTL and algorithm modeling q q q The assignments in a dataflow (RTL) model execute concurrently and operate on explicitly declared registers in the context of a specified architecture The statements in an algorithmic model execute sequentially, without explicit architecture Note!! Not all algorithms can be implemented in hardware Department of Communication Engineering, NCTU 24

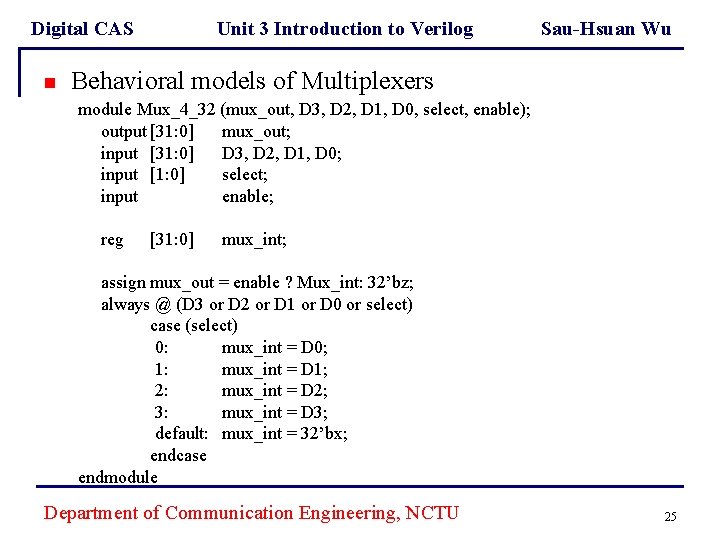

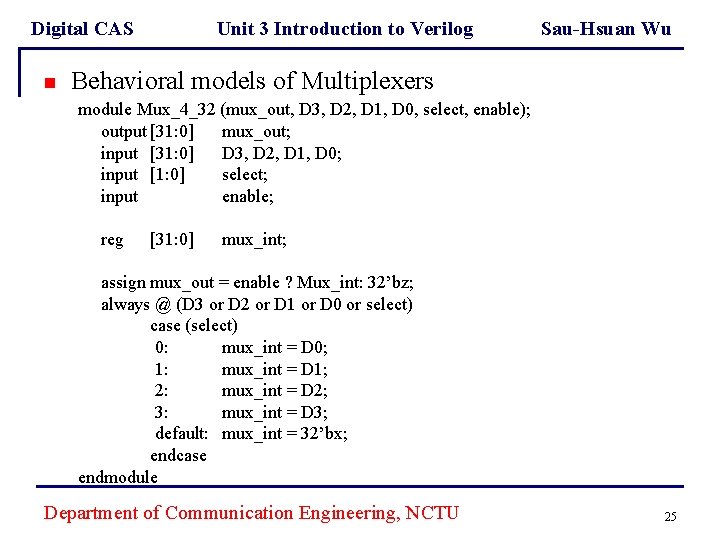

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Behavioral models of Multiplexers module Mux_4_32 (mux_out, D 3, D 2, D 1, D 0, select, enable); output [31: 0] mux_out; input [31: 0] D 3, D 2, D 1, D 0; input [1: 0] select; input enable; reg [31: 0] mux_int; assign mux_out = enable ? Mux_int: 32’bz; always @ (D 3 or D 2 or D 1 or D 0 or select) case (select) 0: mux_int = D 0; 1: mux_int = D 1; 2: mux_int = D 2; 3: mux_int = D 3; default: mux_int = 32’bx; endcase endmodule Department of Communication Engineering, NCTU 25

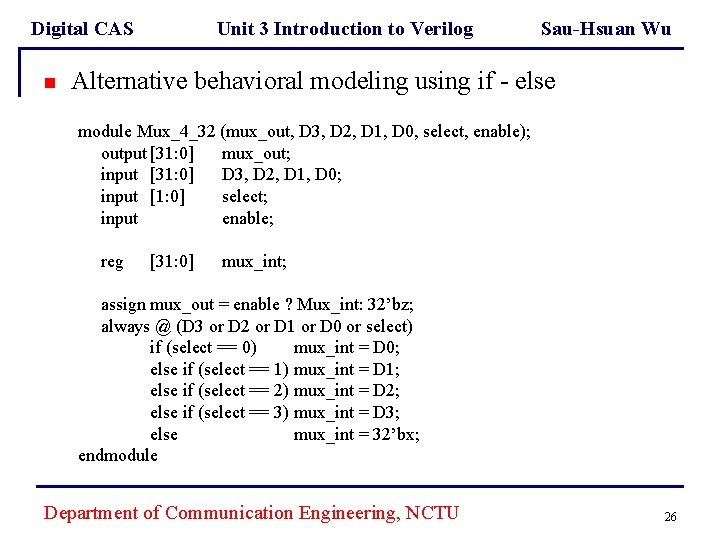

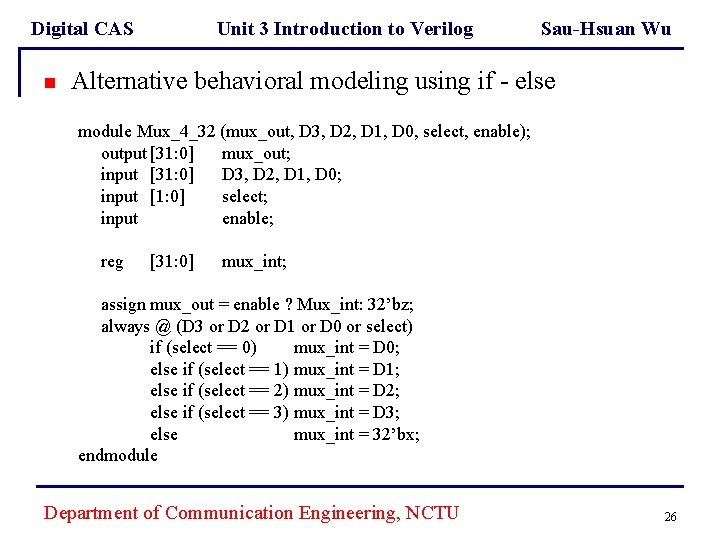

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Alternative behavioral modeling using if - else module Mux_4_32 (mux_out, D 3, D 2, D 1, D 0, select, enable); output [31: 0] mux_out; input [31: 0] D 3, D 2, D 1, D 0; input [1: 0] select; input enable; reg [31: 0] mux_int; assign mux_out = enable ? Mux_int: 32’bz; always @ (D 3 or D 2 or D 1 or D 0 or select) if (select == 0) mux_int = D 0; else if (select == 1) mux_int = D 1; else if (select == 2) mux_int = D 2; else if (select == 3) mux_int = D 3; else mux_int = 32’bx; endmodule Department of Communication Engineering, NCTU 26

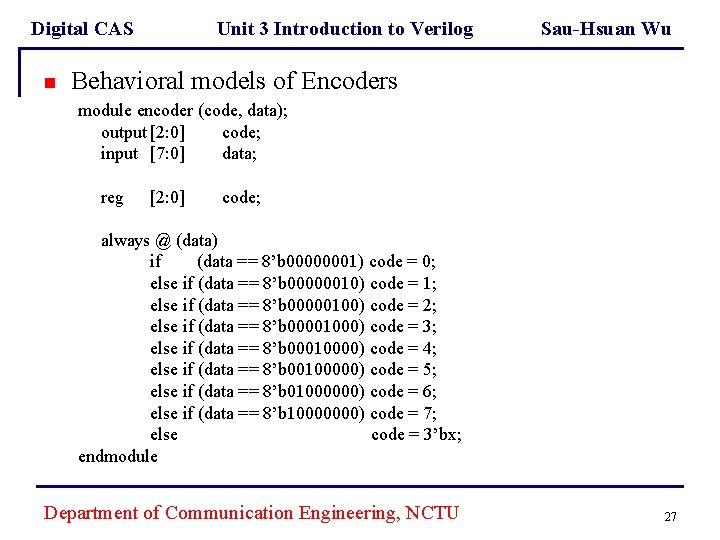

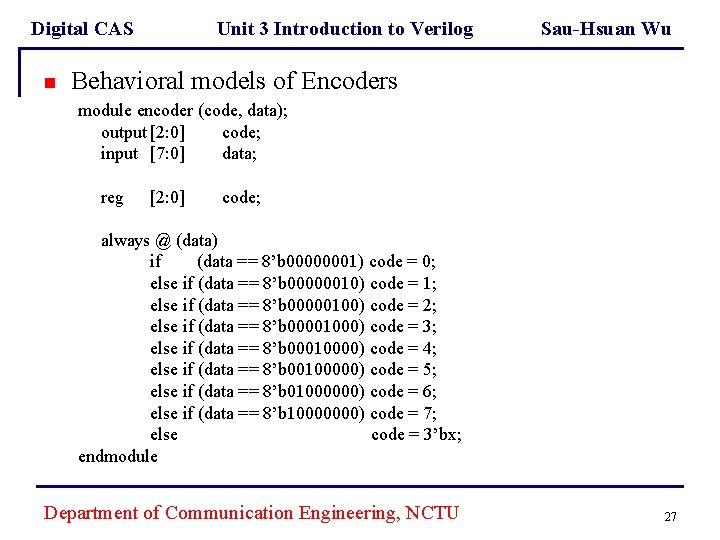

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Behavioral models of Encoders module encoder (code, data); output [2: 0] code; input [7: 0] data; reg [2: 0] code; always @ (data) if (data == 8’b 00000001) code = 0; else if (data == 8’b 00000010) code = 1; else if (data == 8’b 00000100) code = 2; else if (data == 8’b 00001000) code = 3; else if (data == 8’b 00010000) code = 4; else if (data == 8’b 00100000) code = 5; else if (data == 8’b 01000000) code = 6; else if (data == 8’b 10000000) code = 7; else code = 3’bx; endmodule Department of Communication Engineering, NCTU 27

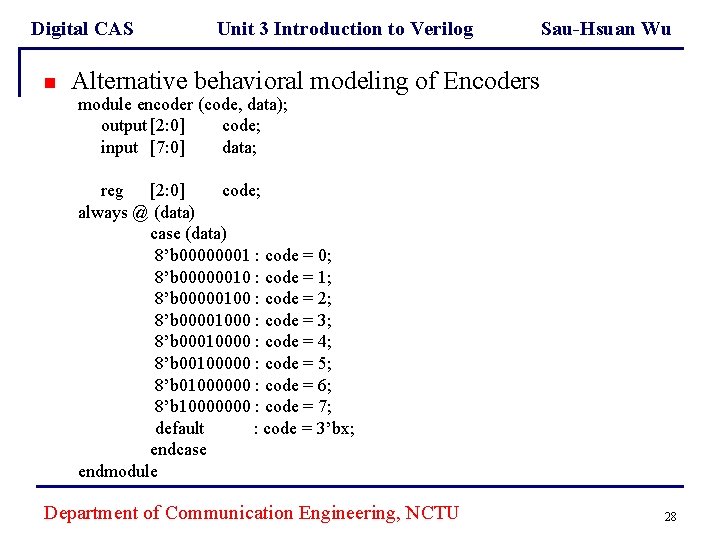

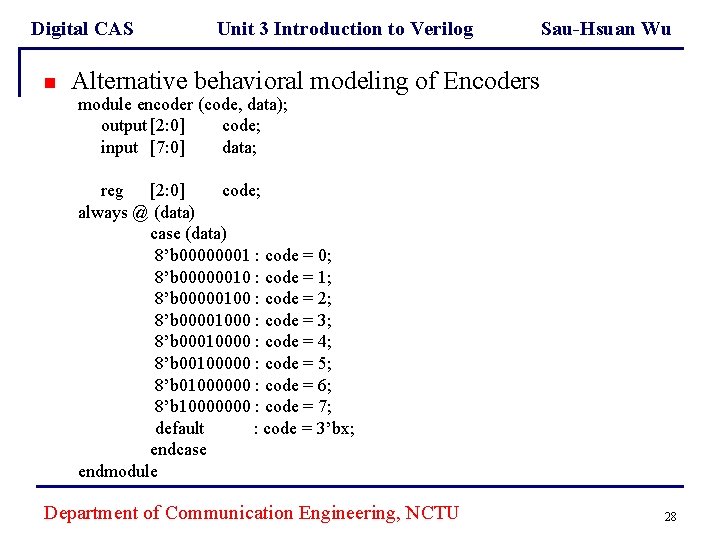

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Alternative behavioral modeling of Encoders module encoder (code, data); output [2: 0] code; input [7: 0] data; reg [2: 0] code; always @ (data) case (data) 8’b 00000001 : code = 0; 8’b 00000010 : code = 1; 8’b 00000100 : code = 2; 8’b 00001000 : code = 3; 8’b 00010000 : code = 4; 8’b 00100000 : code = 5; 8’b 01000000 : code = 6; 8’b 10000000 : code = 7; default : code = 3’bx; endcase endmodule Department of Communication Engineering, NCTU 28

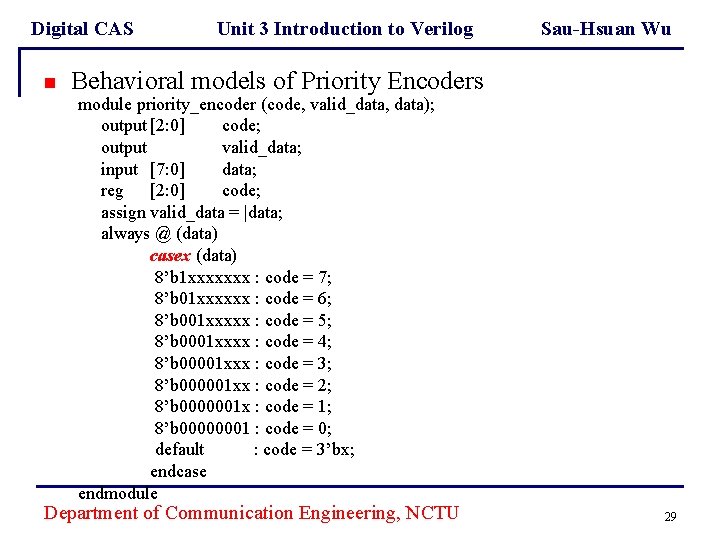

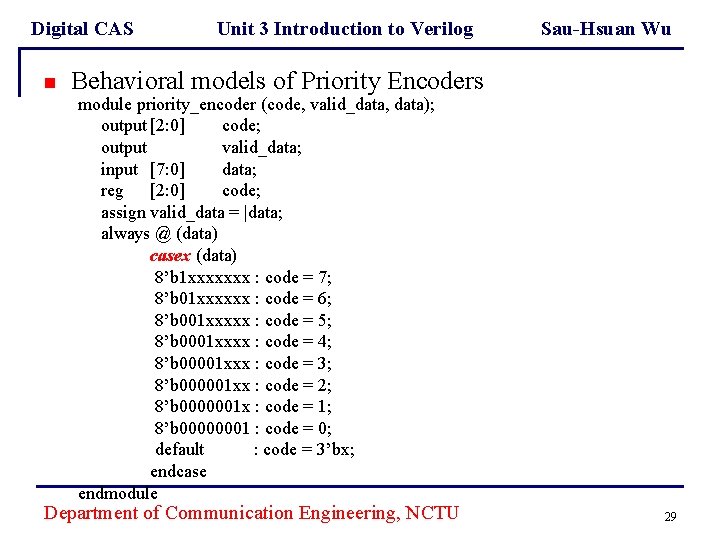

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Behavioral models of Priority Encoders module priority_encoder (code, valid_data, data); output [2: 0] code; output valid_data; input [7: 0] data; reg [2: 0] code; assign valid_data = |data; always @ (data) casex (data) 8’b 1 xxxxxxx : code = 7; 8’b 01 xxxxxx : code = 6; 8’b 001 xxxxx : code = 5; 8’b 0001 xxxx : code = 4; 8’b 00001 xxx : code = 3; 8’b 000001 xx : code = 2; 8’b 0000001 x : code = 1; 8’b 00000001 : code = 0; default : code = 3’bx; endcase endmodule Department of Communication Engineering, NCTU 29

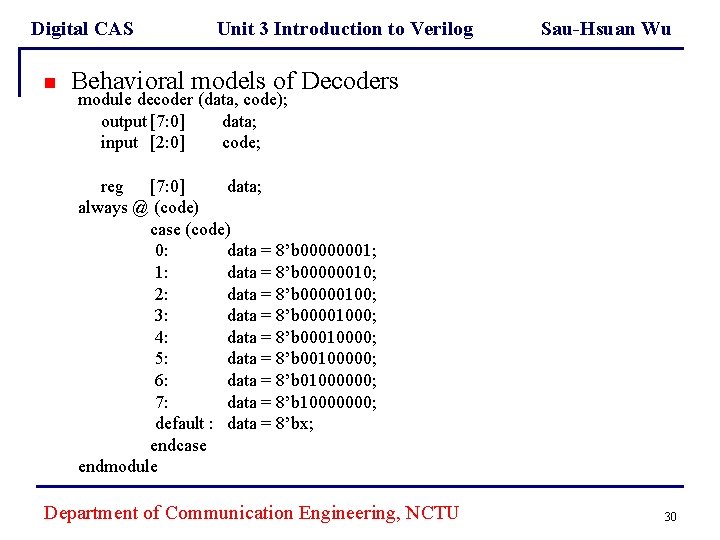

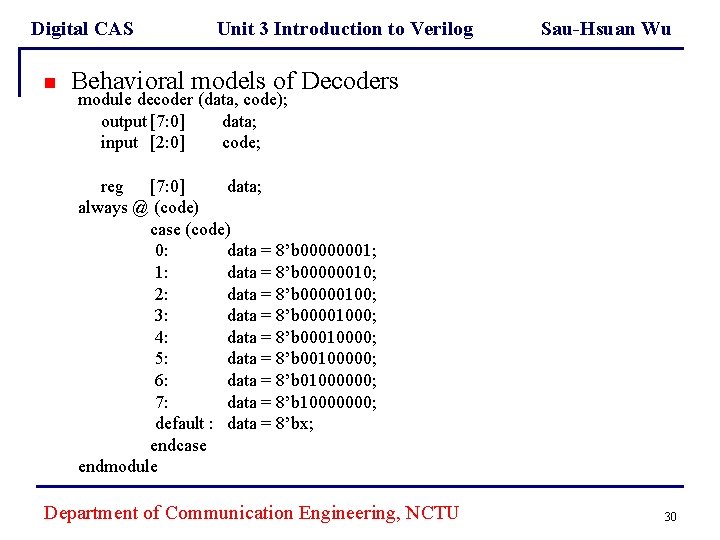

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Behavioral models of Decoders module decoder (data, code); output [7: 0] data; input [2: 0] code; reg [7: 0] data; always @ (code) case (code) 0: data = 8’b 00000001; 1: data = 8’b 00000010; 2: data = 8’b 00000100; 3: data = 8’b 00001000; 4: data = 8’b 00010000; 5: data = 8’b 00100000; 6: data = 8’b 01000000; 7: data = 8’b 10000000; default : data = 8’bx; endcase endmodule Department of Communication Engineering, NCTU 30

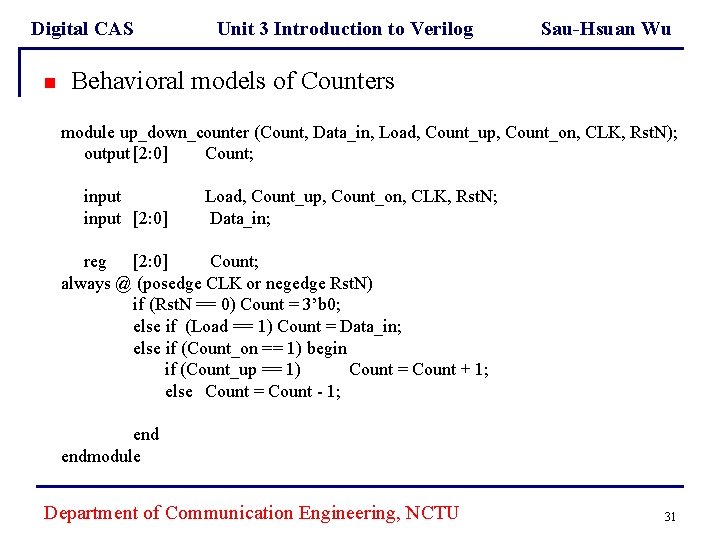

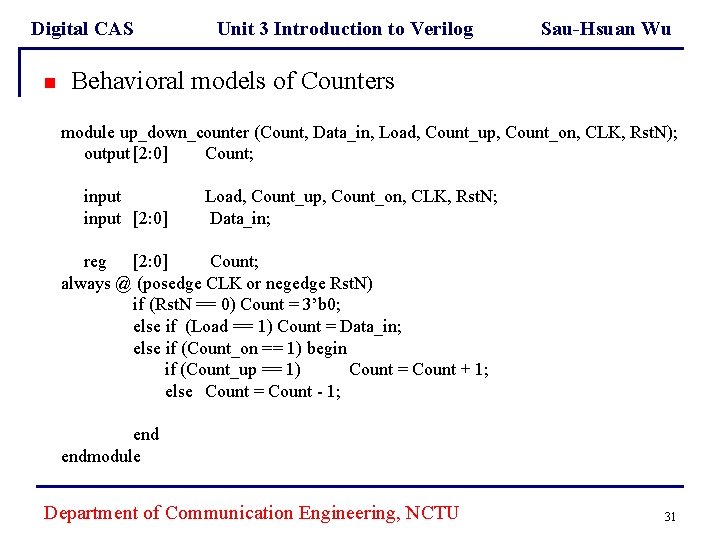

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Behavioral models of Counters module up_down_counter (Count, Data_in, Load, Count_up, Count_on, CLK, Rst. N); output [2: 0] Count; input Load, Count_up, Count_on, CLK, Rst. N; input [2: 0] Data_in; reg [2: 0] Count; always @ (posedge CLK or negedge Rst. N) if (Rst. N == 0) Count = 3’b 0; else if (Load == 1) Count = Data_in; else if (Count_on == 1) begin if (Count_up == 1) Count = Count + 1; else Count = Count - 1; endmodule Department of Communication Engineering, NCTU 31

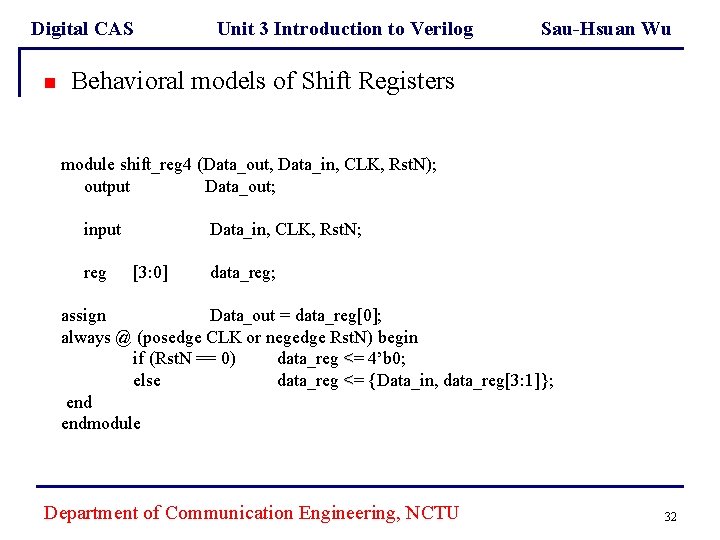

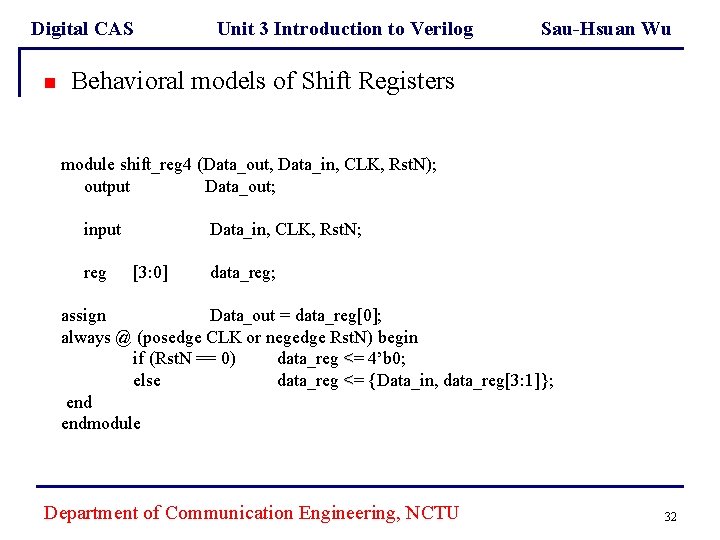

Digital CAS n Unit 3 Introduction to Verilog Sau-Hsuan Wu Behavioral models of Shift Registers module shift_reg 4 (Data_out, Data_in, CLK, Rst. N); output Data_out; input reg [3: 0] Data_in, CLK, Rst. N; data_reg; assign Data_out = data_reg[0]; always @ (posedge CLK or negedge Rst. N) begin if (Rst. N == 0) data_reg <= 4’b 0; < else data_reg <= {Data_in, data_reg[3: 1]}; < endmodule Department of Communication Engineering, NCTU 32