Unit 4 Design and Synthesis of Datapath Controllers

- Slides: 25

Unit 4 Design and Synthesis of Datapath Controllers Department of Communication Engineering, NCTU 1

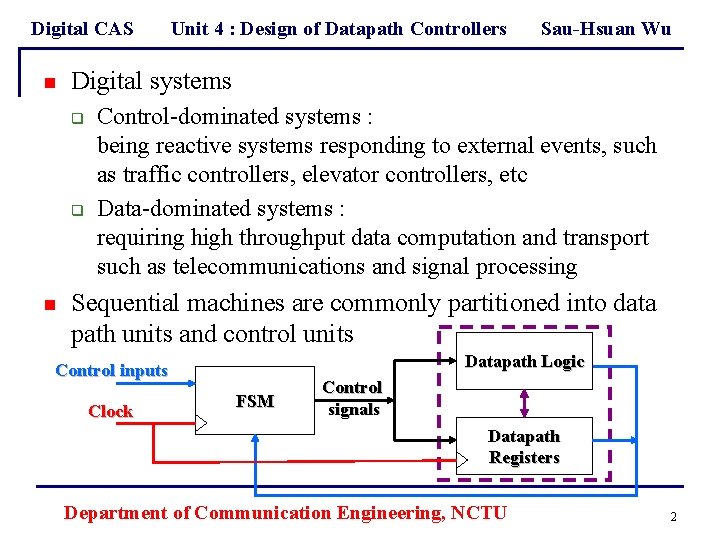

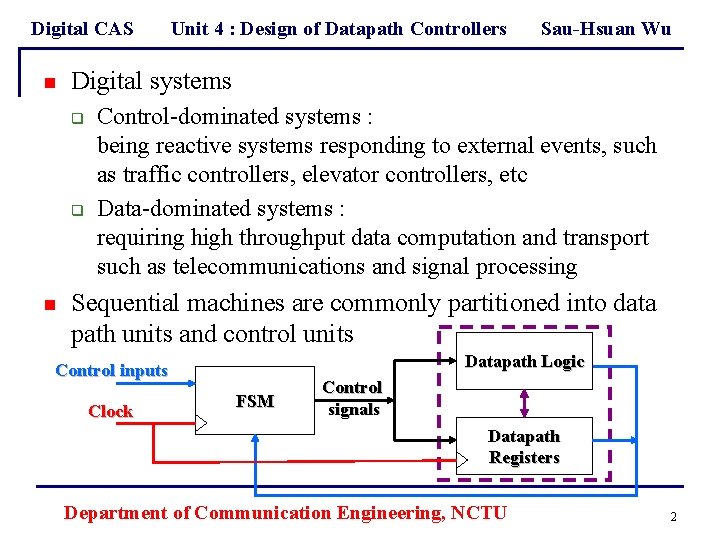

Digital CAS n Sau-Hsuan Wu Digital systems q q n Unit 4 : Design of Datapath Controllers Control-dominated systems : being reactive systems responding to external events, such as traffic controllers, elevator controllers, etc Data-dominated systems : requiring high throughput data computation and transport such as telecommunications and signal processing Sequential machines are commonly partitioned into data path units and control units Datapath Logic Control inputs Clock FSM Control signals Datapath Registers Department of Communication Engineering, NCTU 2

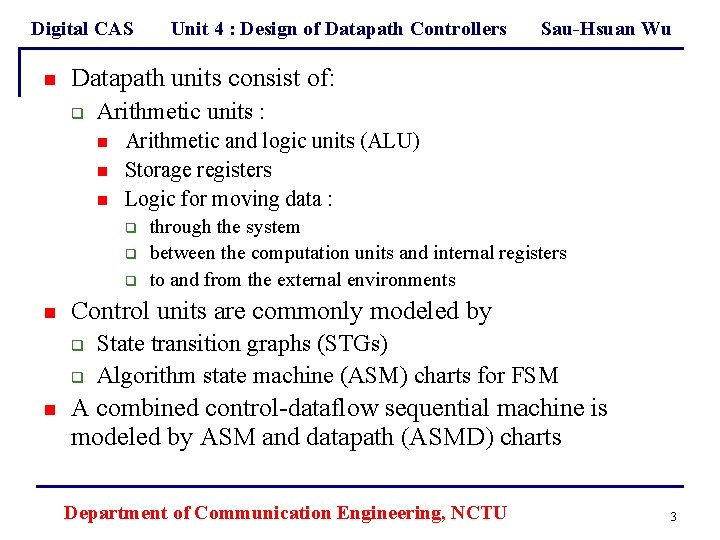

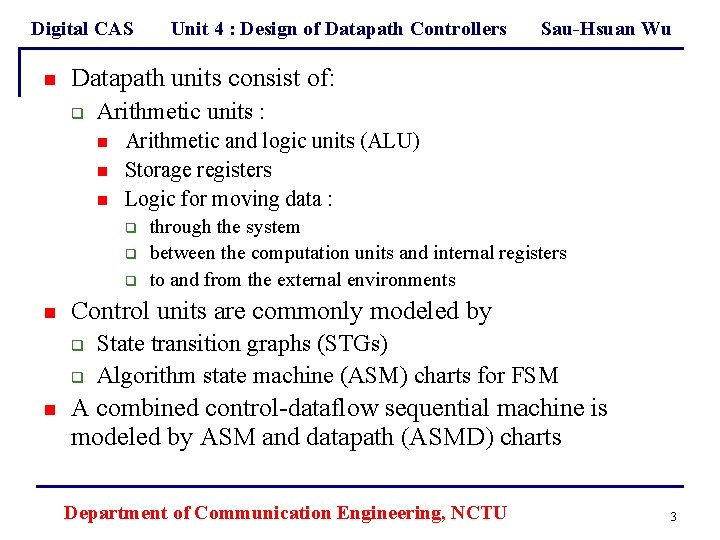

Digital CAS n Arithmetic units : n n n Arithmetic and logic units (ALU) Storage registers Logic for moving data : q q q through the system between the computation units and internal registers to and from the external environments Control units are commonly modeled by q q n Sau-Hsuan Wu Datapath units consist of: q n Unit 4 : Design of Datapath Controllers State transition graphs (STGs) Algorithm state machine (ASM) charts for FSM A combined control-dataflow sequential machine is modeled by ASM and datapath (ASMD) charts Department of Communication Engineering, NCTU 3

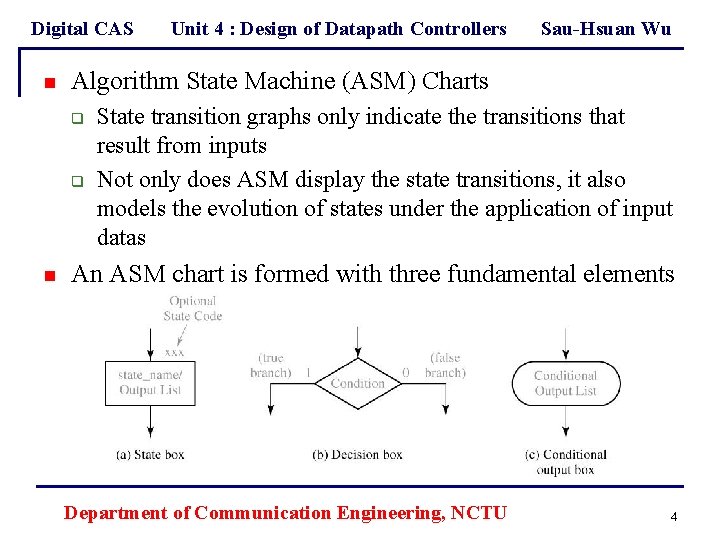

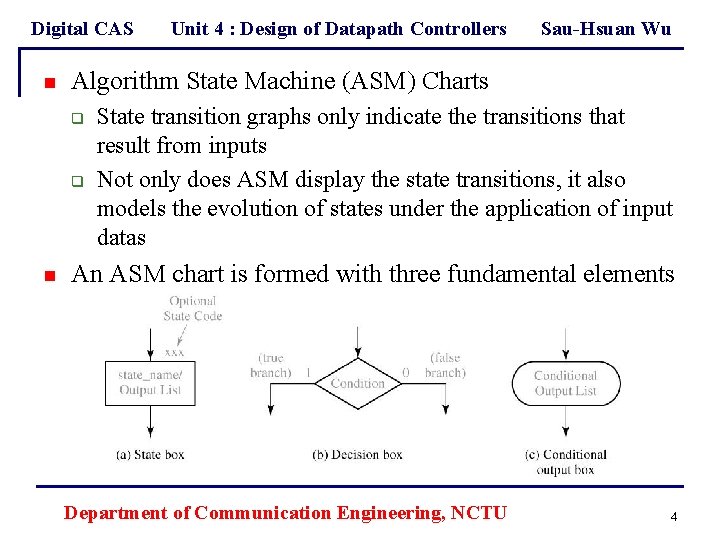

Digital CAS n Sau-Hsuan Wu Algorithm State Machine (ASM) Charts q q n Unit 4 : Design of Datapath Controllers State transition graphs only indicate the transitions that result from inputs Not only does ASM display the state transitions, it also models the evolution of states under the application of input datas An ASM chart is formed with three fundamental elements Department of Communication Engineering, NCTU 4

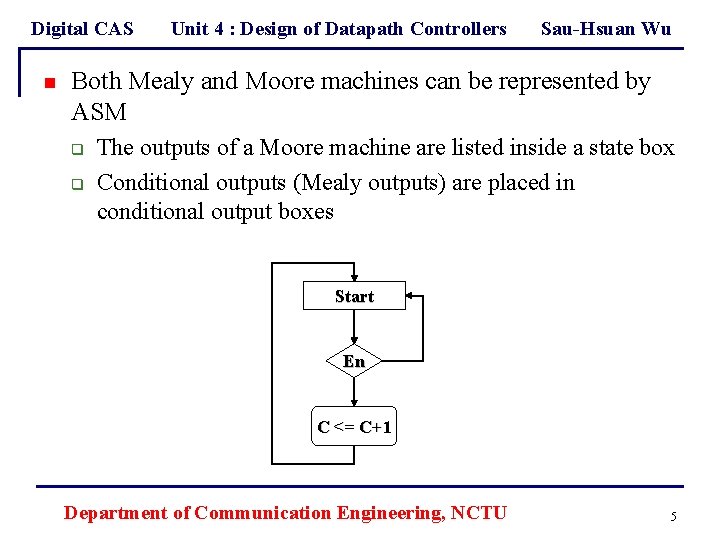

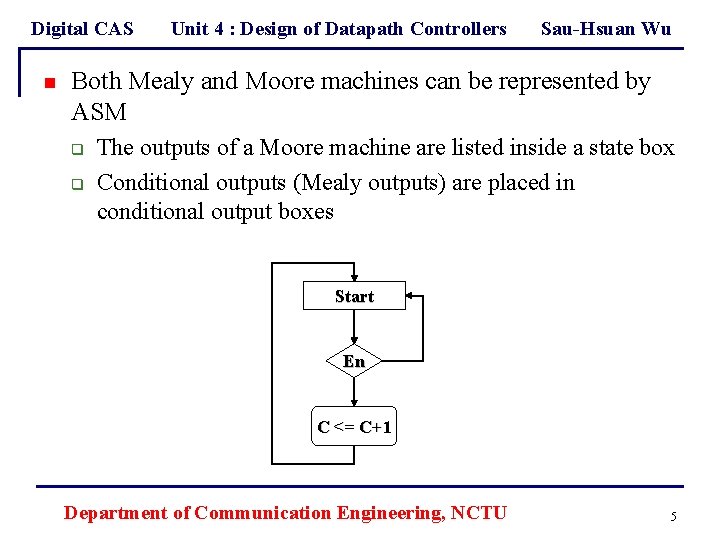

Digital CAS n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu Both Mealy and Moore machines can be represented by ASM q q The outputs of a Moore machine are listed inside a state box Conditional outputs (Mealy outputs) are placed in conditional output boxes Start En C <= C+1 Department of Communication Engineering, NCTU 5

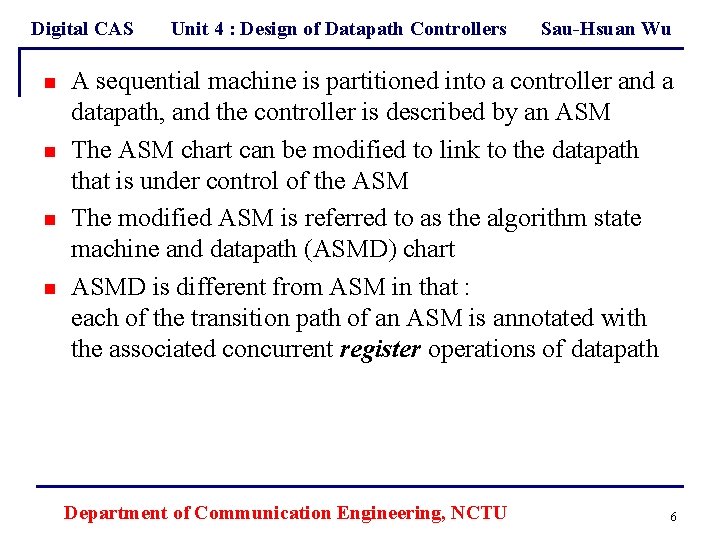

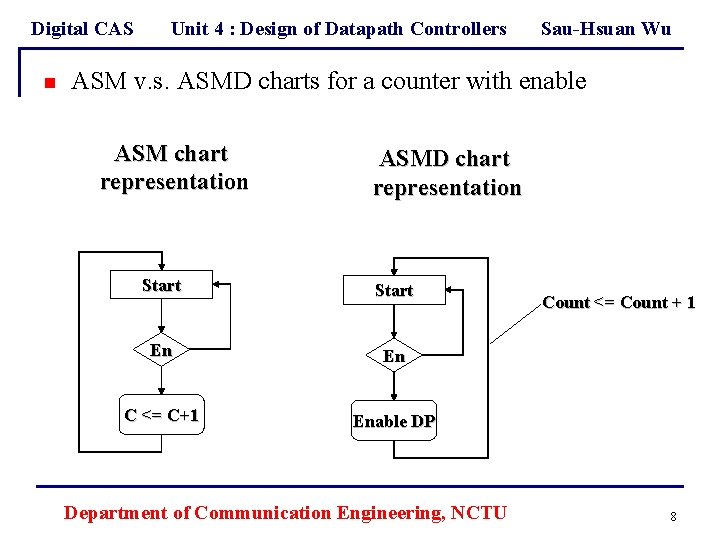

Digital CAS n n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu A sequential machine is partitioned into a controller and a datapath, and the controller is described by an ASM The ASM chart can be modified to link to the datapath that is under control of the ASM The modified ASM is referred to as the algorithm state machine and datapath (ASMD) chart ASMD is different from ASM in that : each of the transition path of an ASM is annotated with the associated concurrent register operations of datapath Department of Communication Engineering, NCTU 6

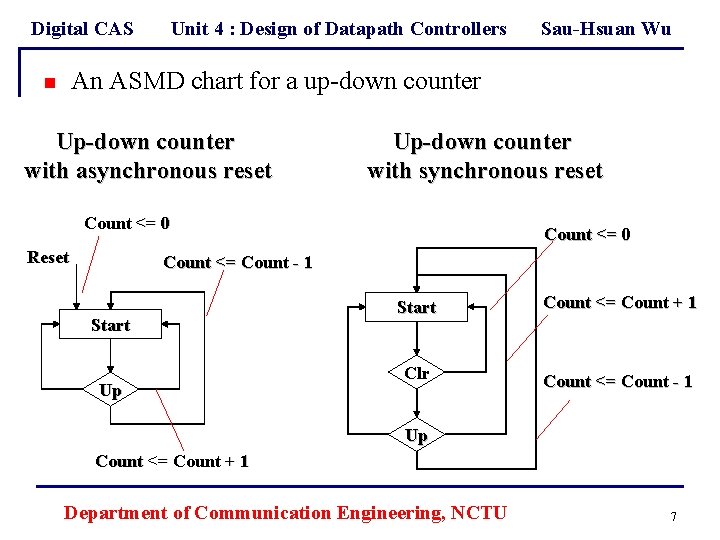

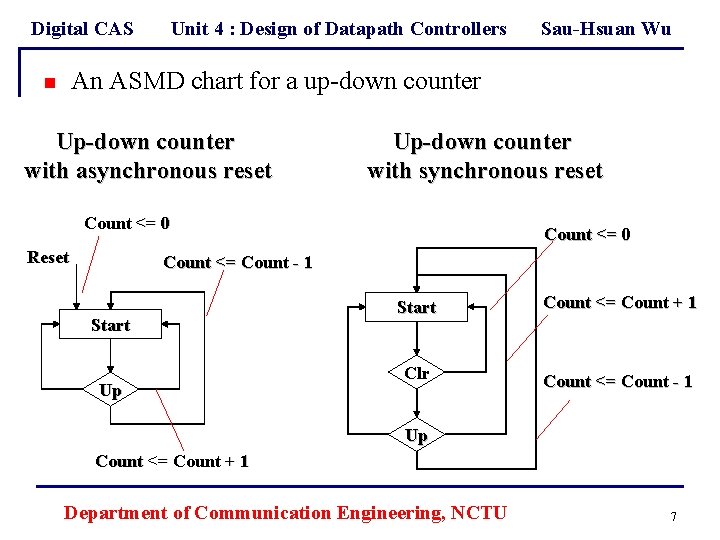

Digital CAS Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu An ASMD chart for a up-down counter n Up-down counter with asynchronous reset Up-down counter with synchronous reset Count <= 0 Reset Count <= 0 Count <= Count - 1 Start Up Start Count <= Count + 1 Clr Count <= Count - 1 Up Count <= Count + 1 Department of Communication Engineering, NCTU 7

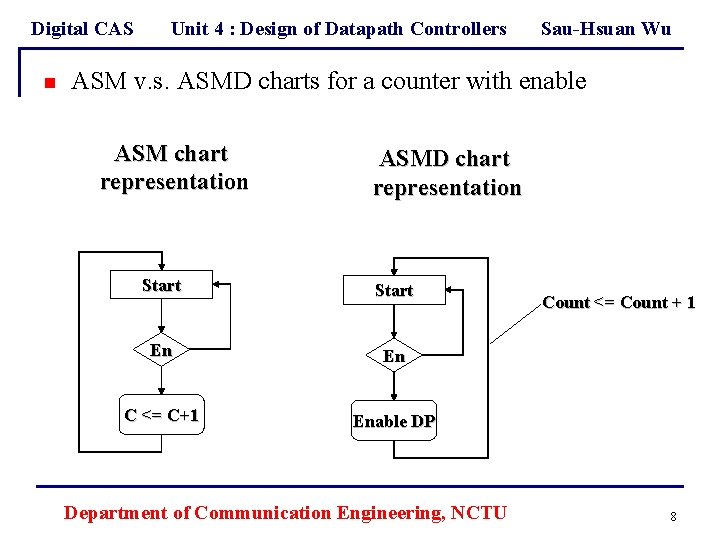

Digital CAS n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu ASM v. s. ASMD charts for a counter with enable ASM chart representation ASMD chart representation Start En En C <= C+1 Enable DP Department of Communication Engineering, NCTU Count <= Count + 1 8

Unit 4 -1 UART Design Department of Communication Engineering, NCTU 9

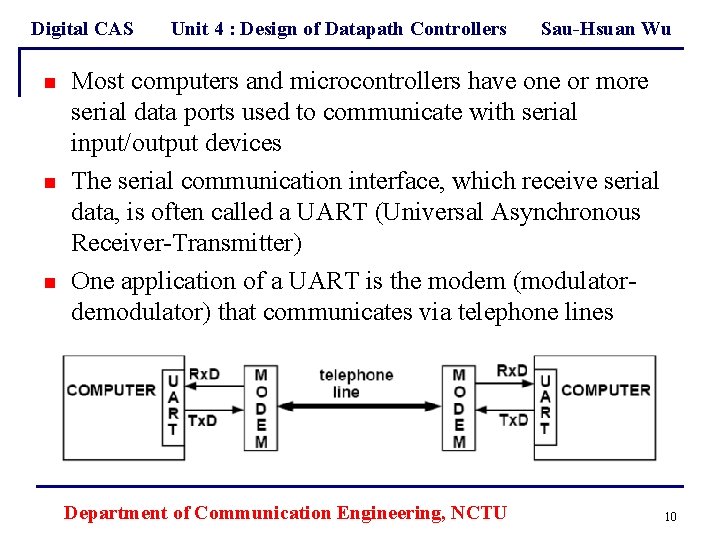

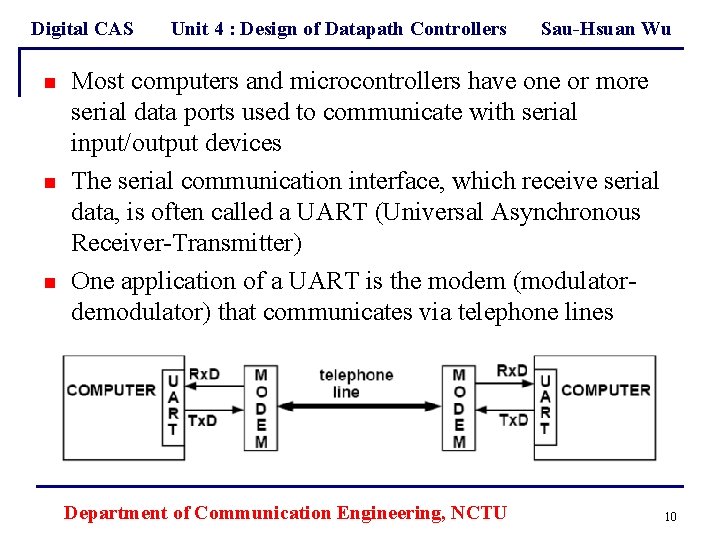

Digital CAS n n n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu Most computers and microcontrollers have one or more serial data ports used to communicate with serial input/output devices The serial communication interface, which receive serial data, is often called a UART (Universal Asynchronous Receiver-Transmitter) One application of a UART is the modem (modulatordemodulator) that communicates via telephone lines Department of Communication Engineering, NCTU 10

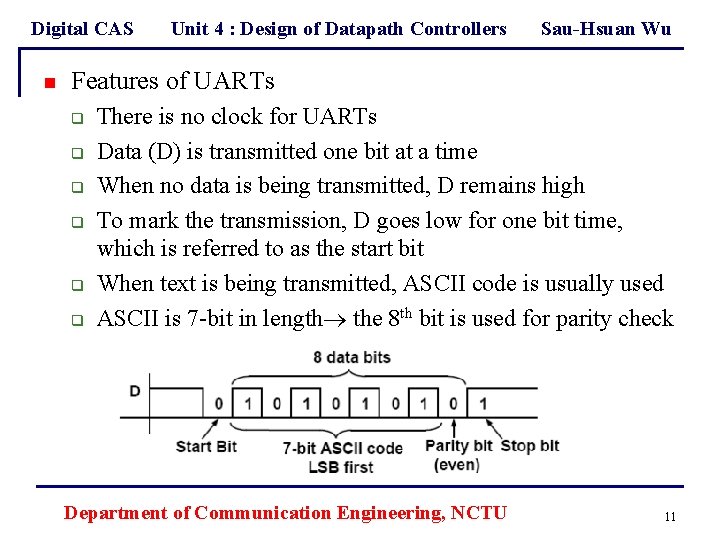

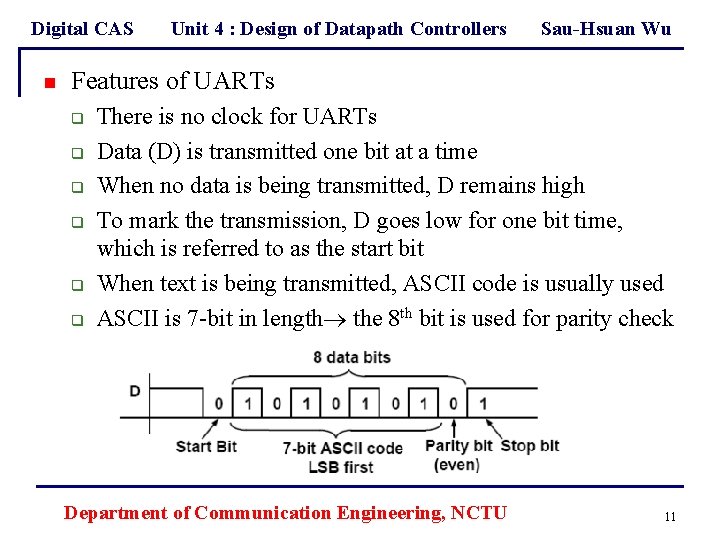

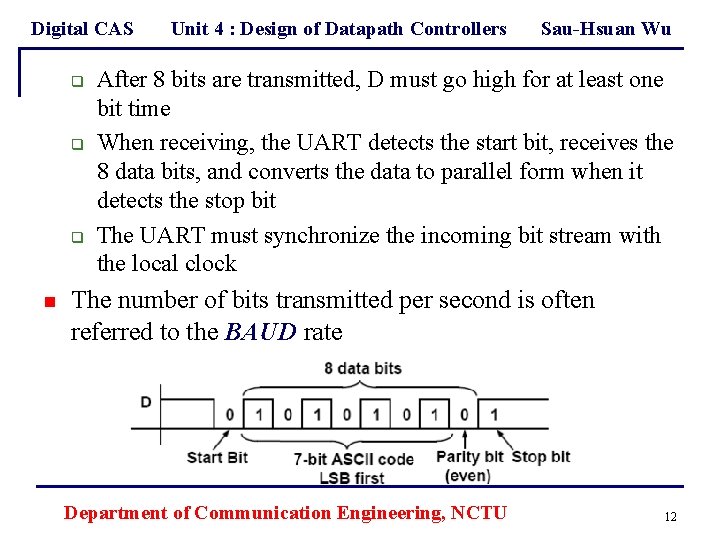

Digital CAS n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu Features of UARTs q q q There is no clock for UARTs Data (D) is transmitted one bit at a time When no data is being transmitted, D remains high To mark the transmission, D goes low for one bit time, which is referred to as the start bit When text is being transmitted, ASCII code is usually used ASCII is 7 -bit in length the 8 th bit is used for parity check Department of Communication Engineering, NCTU 11

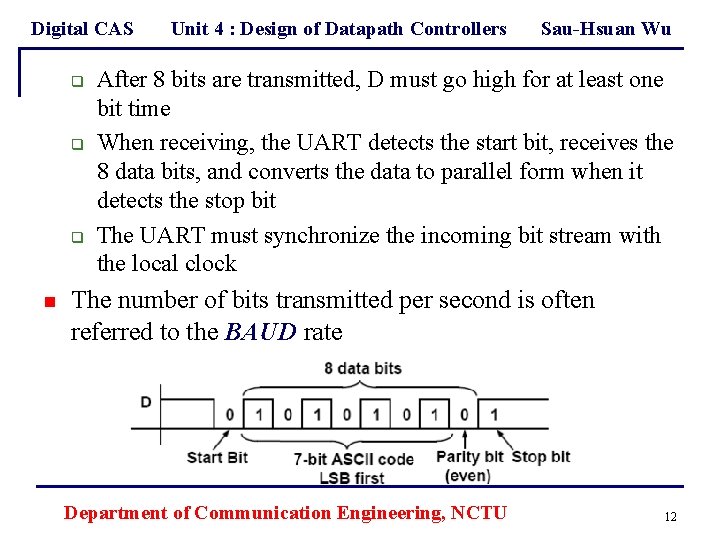

Digital CAS q q q n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu After 8 bits are transmitted, D must go high for at least one bit time When receiving, the UART detects the start bit, receives the 8 data bits, and converts the data to parallel form when it detects the stop bit The UART must synchronize the incoming bit stream with the local clock The number of bits transmitted per second is often referred to the BAUD rate Department of Communication Engineering, NCTU 12

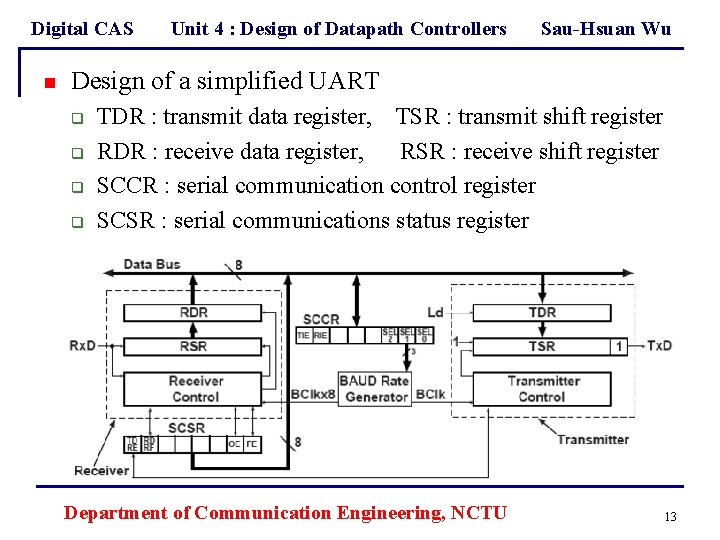

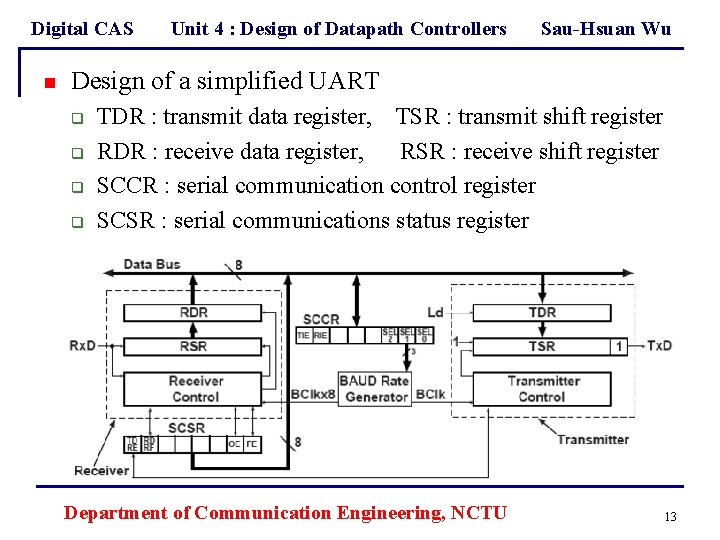

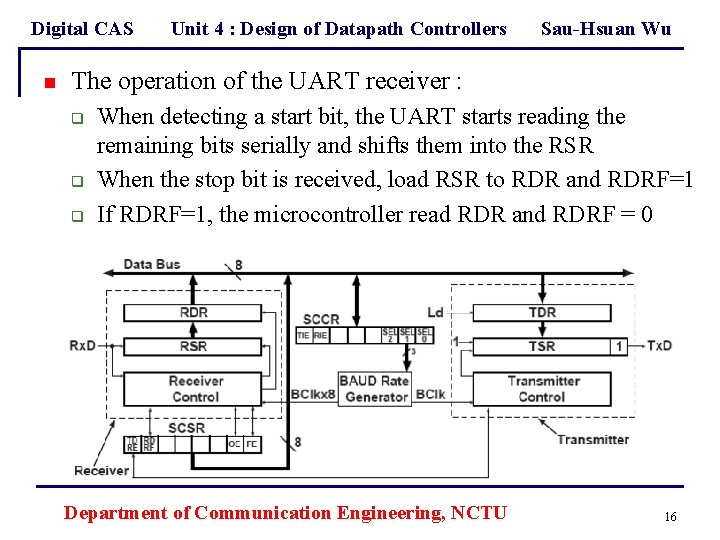

Digital CAS n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu Design of a simplified UART q q TDR : transmit data register, TSR : transmit shift register RDR : receive data register, RSR : receive shift register SCCR : serial communication control register SCSR : serial communications status register Department of Communication Engineering, NCTU 13

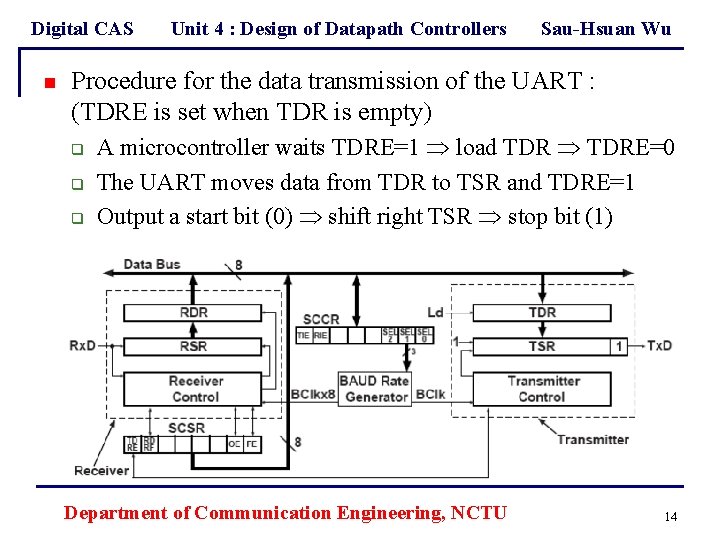

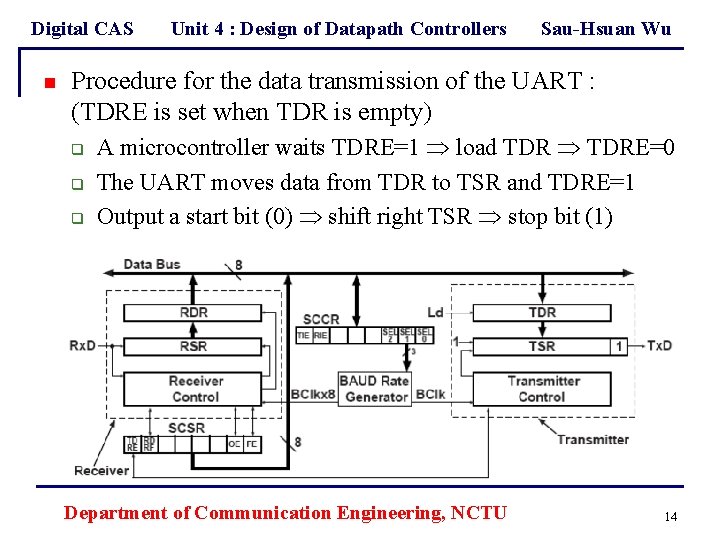

Digital CAS n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu Procedure for the data transmission of the UART : (TDRE is set when TDR is empty) q q q A microcontroller waits TDRE=1 load TDRE=0 The UART moves data from TDR to TSR and TDRE=1 Output a start bit (0) shift right TSR stop bit (1) Department of Communication Engineering, NCTU 14

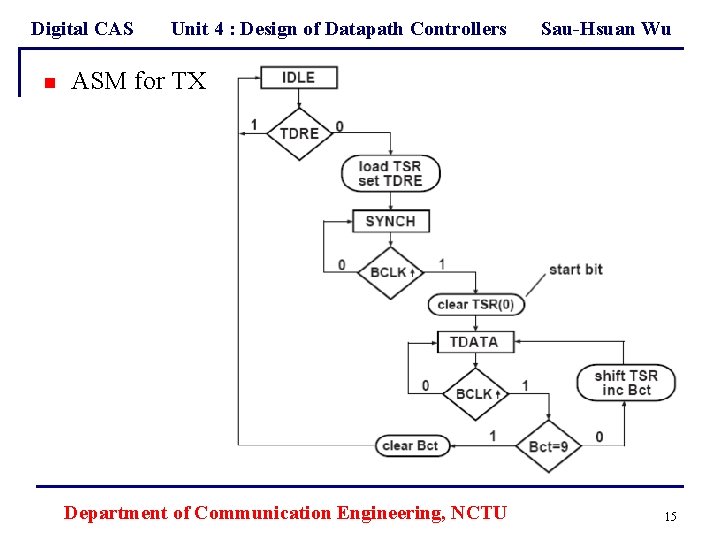

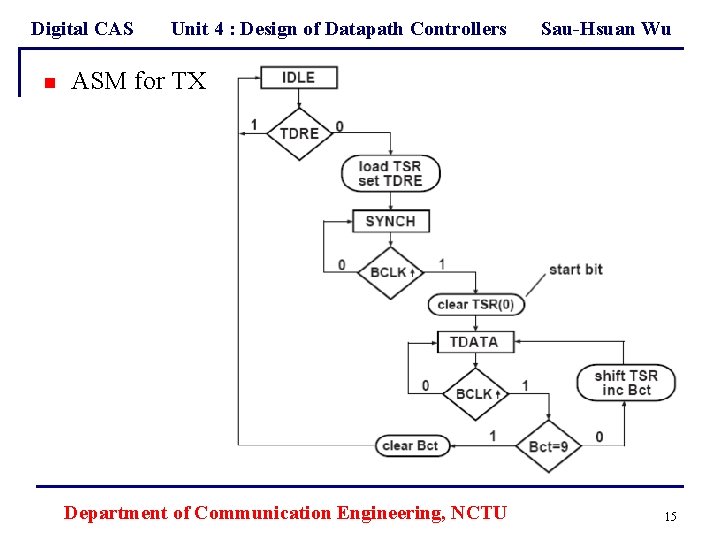

Digital CAS n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu ASM for TX Department of Communication Engineering, NCTU 15

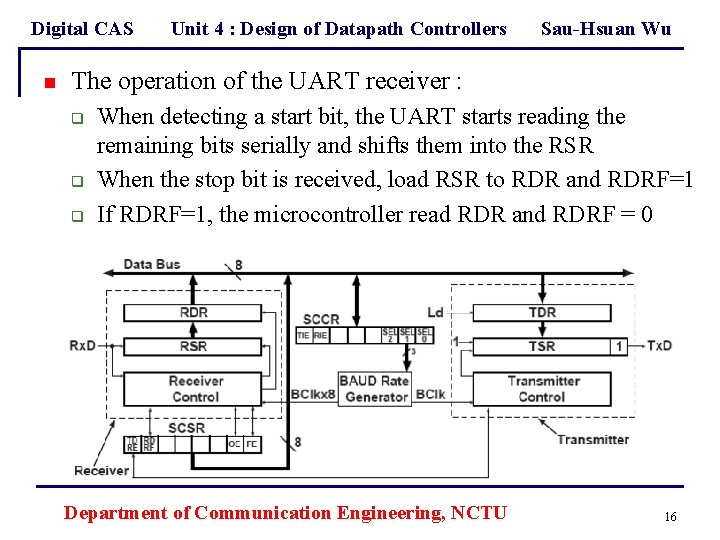

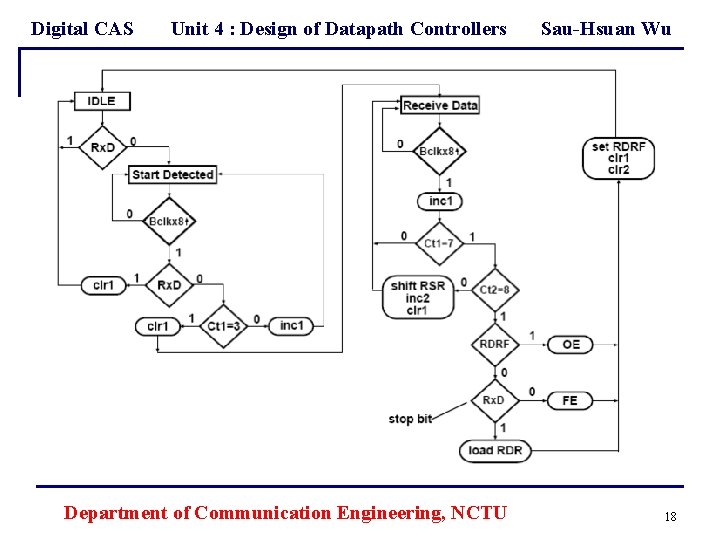

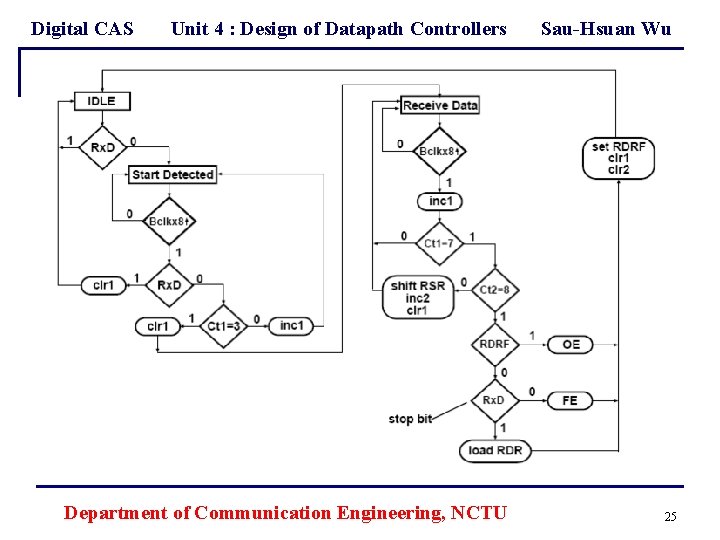

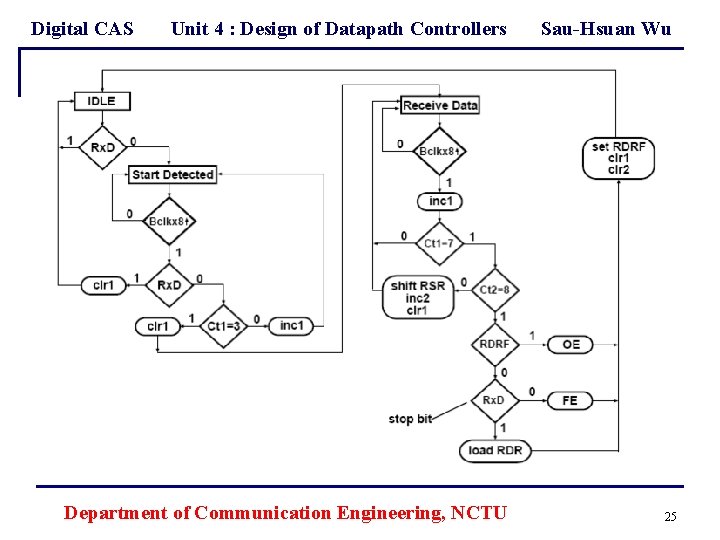

Digital CAS n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu The operation of the UART receiver : q q q When detecting a start bit, the UART starts reading the remaining bits serially and shifts them into the RSR When the stop bit is received, load RSR to RDR and RDRF=1 If RDRF=1, the microcontroller read RDR and RDRF = 0 Department of Communication Engineering, NCTU 16

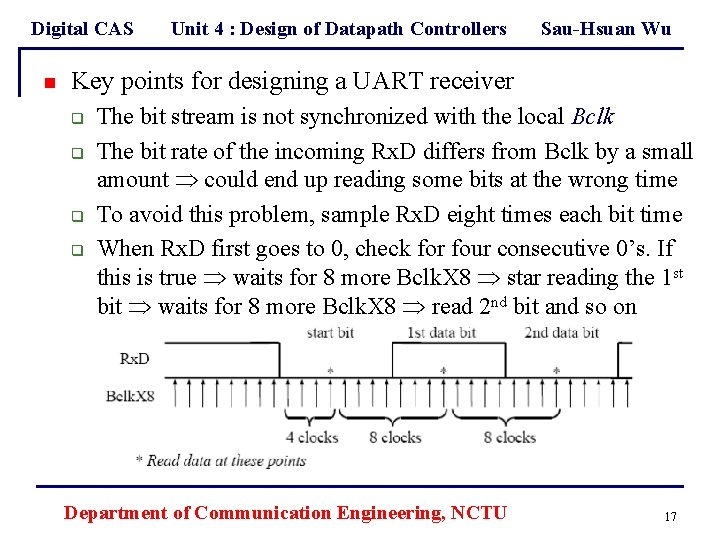

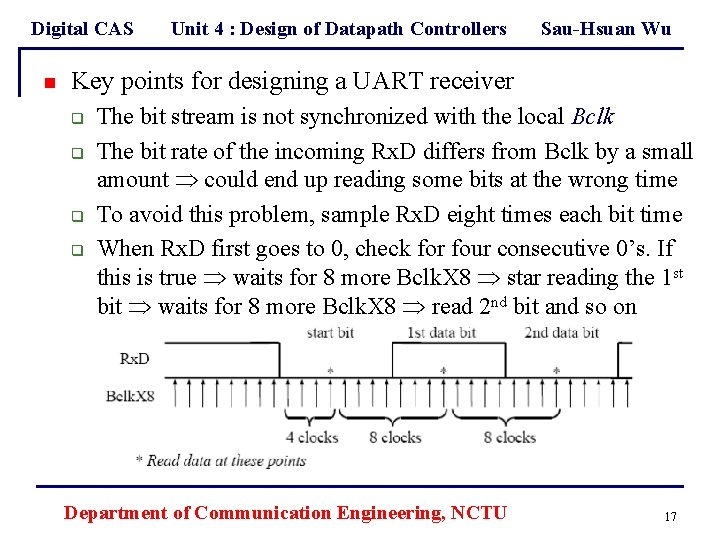

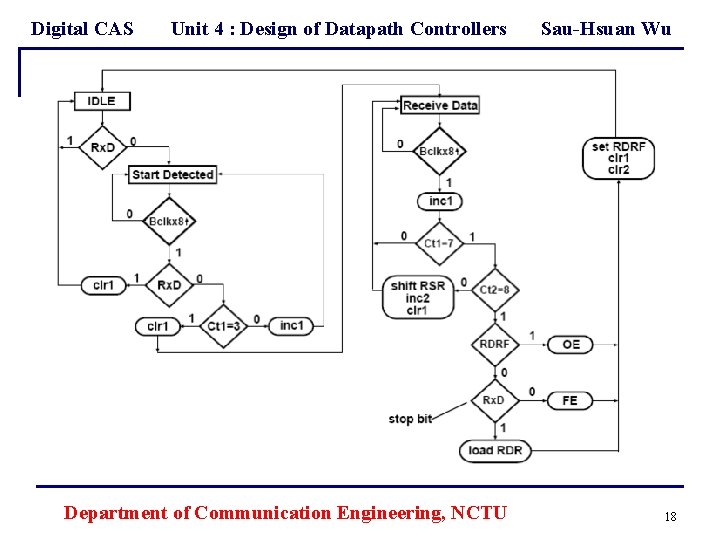

Digital CAS n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu Key points for designing a UART receiver q q The bit stream is not synchronized with the local Bclk The bit rate of the incoming Rx. D differs from Bclk by a small amount could end up reading some bits at the wrong time To avoid this problem, sample Rx. D eight times each bit time When Rx. D first goes to 0, check for four consecutive 0’s. If this is true waits for 8 more Bclk. X 8 star reading the 1 st bit waits for 8 more Bclk. X 8 read 2 nd bit and so on Department of Communication Engineering, NCTU 17

Digital CAS Unit 4 : Design of Datapath Controllers Department of Communication Engineering, NCTU Sau-Hsuan Wu 18

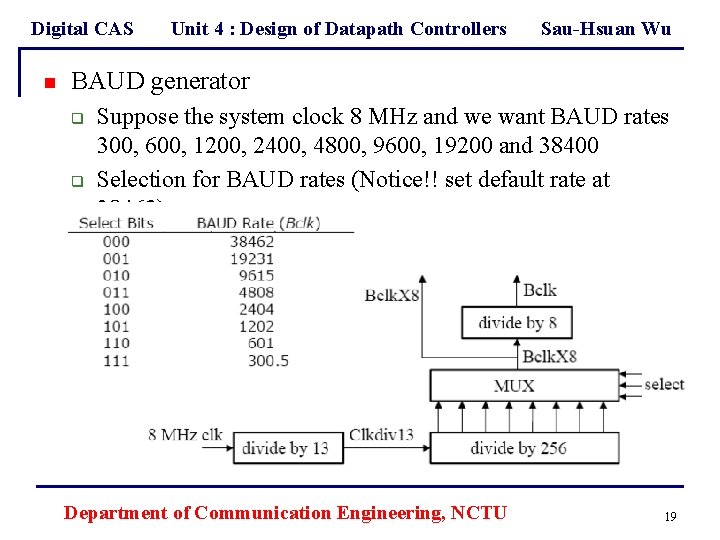

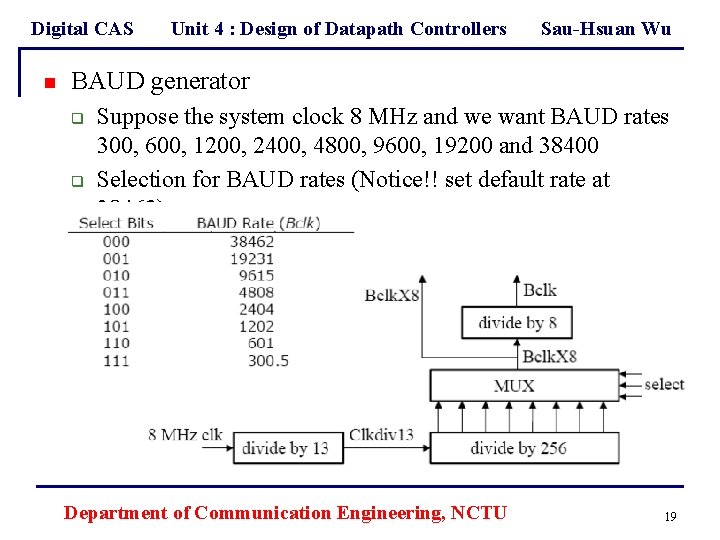

Digital CAS n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu BAUD generator q q Suppose the system clock 8 MHz and we want BAUD rates 300, 600, 1200, 2400, 4800, 9600, 19200 and 38400 Selection for BAUD rates (Notice!! set default rate at 38462) Department of Communication Engineering, NCTU 19

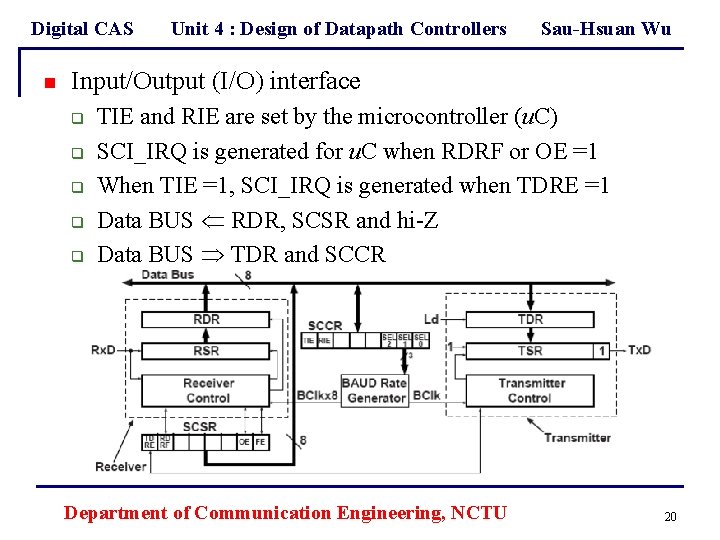

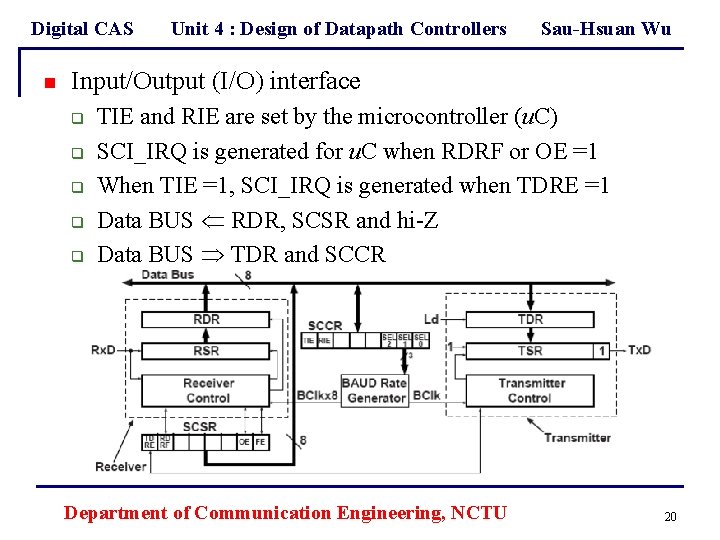

Digital CAS n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu Input/Output (I/O) interface q q q TIE and RIE are set by the microcontroller (u. C) SCI_IRQ is generated for u. C when RDRF or OE =1 When TIE =1, SCI_IRQ is generated when TDRE =1 Data BUS RDR, SCSR and hi-Z Data BUS TDR and SCCR Department of Communication Engineering, NCTU 20

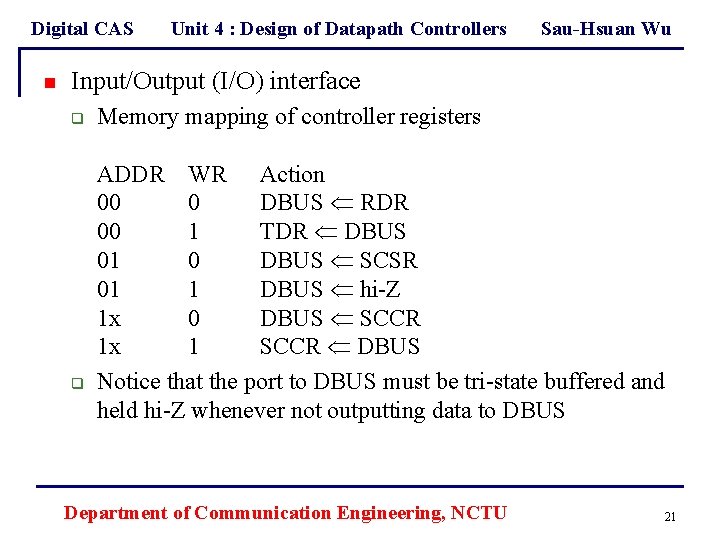

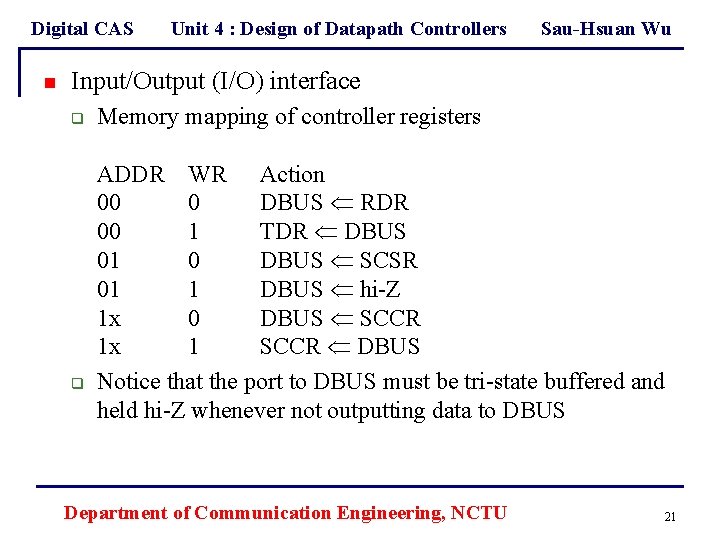

Digital CAS n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu Input/Output (I/O) interface q q Memory mapping of controller registers ADDR WR Action 00 0 DBUS RDR 00 1 TDR DBUS 01 0 DBUS SCSR 01 1 DBUS hi-Z 1 x 0 DBUS SCCR 1 x 1 SCCR DBUS Notice that the port to DBUS must be tri-state buffered and held hi-Z whenever not outputting data to DBUS Department of Communication Engineering, NCTU 21

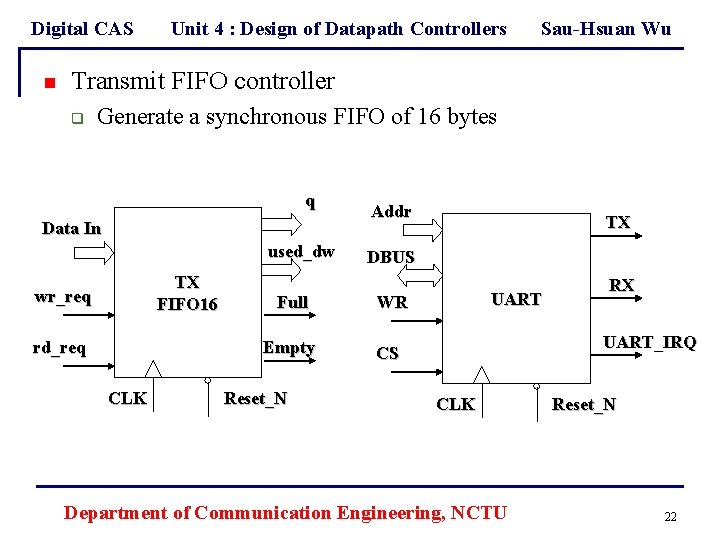

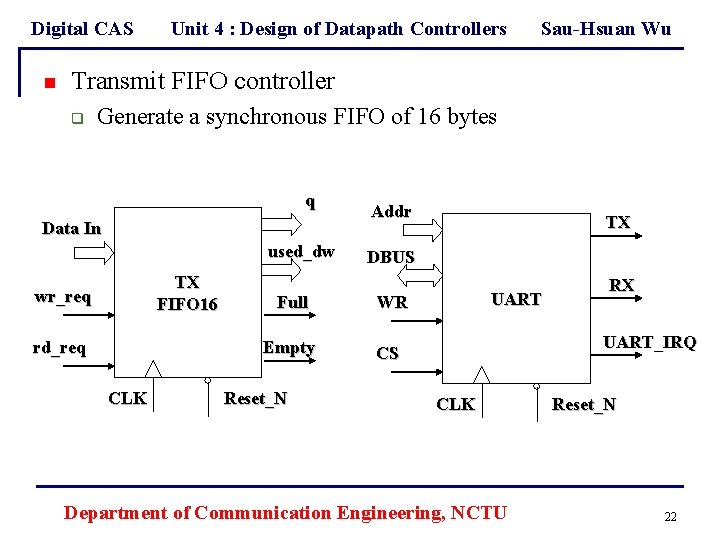

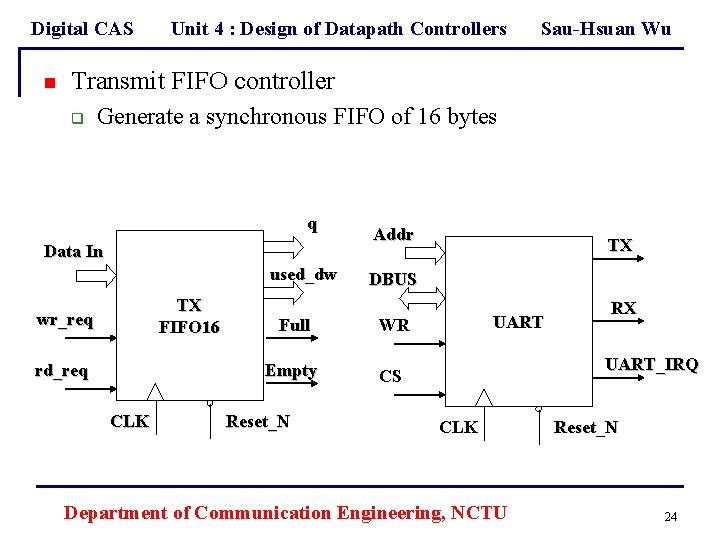

Digital CAS n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu Transmit FIFO controller q Generate a synchronous FIFO of 16 bytes q Data In used_dw TX FIFO 16 wr_req rd_req CLK Addr DBUS Full WR Empty CS Reset_N TX UART RX UART_IRQ CLK Department of Communication Engineering, NCTU Reset_N 22

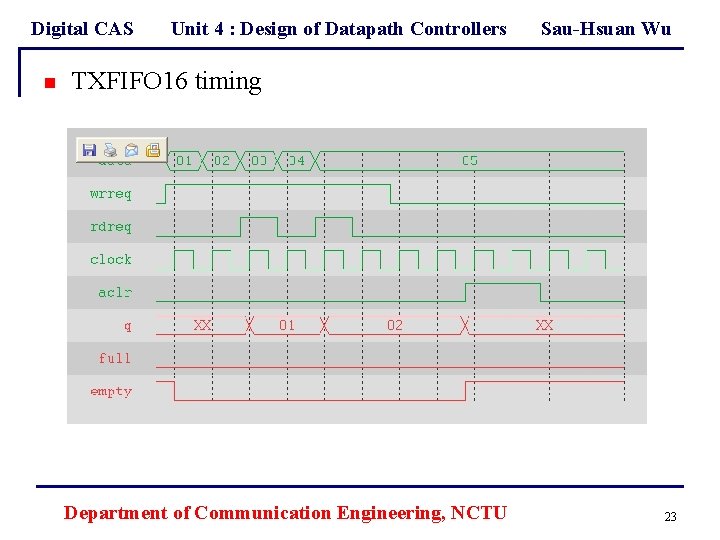

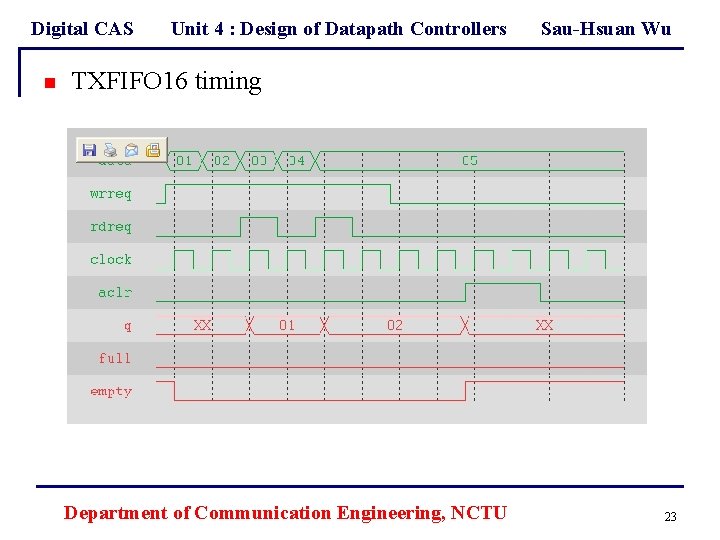

Digital CAS n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu TXFIFO 16 timing Department of Communication Engineering, NCTU 23

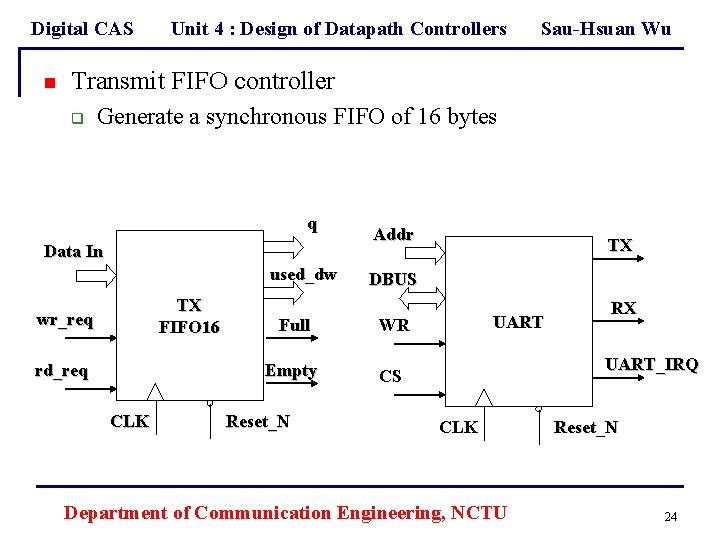

Digital CAS n Unit 4 : Design of Datapath Controllers Sau-Hsuan Wu Transmit FIFO controller q Generate a synchronous FIFO of 16 bytes q Data In used_dw TX FIFO 16 wr_req rd_req CLK Addr DBUS Full WR Empty CS Reset_N TX UART RX UART_IRQ CLK Department of Communication Engineering, NCTU Reset_N 24

Digital CAS Unit 4 : Design of Datapath Controllers Department of Communication Engineering, NCTU Sau-Hsuan Wu 25