UNIT 2 Central Processing Unit Teaching Plan Introduction

- Slides: 71

UNIT 2 Central Processing Unit

Teaching Plan Introduction of Unit, Machine Instruction Characteristics, Types of Operand operations, Instruction format and Types: 2 lectures Addressing Modes, Processor Organization, Instruction Cycle: 2 lectures 8086 Processor: Features, Block Diagram, Pin Configurations: 2 lectures Max/Min Mode, Read Write Cycle: 2 lectures

CPU Function CPU must: Fetch instructions Interpret instructions Fetch data Process data Write data

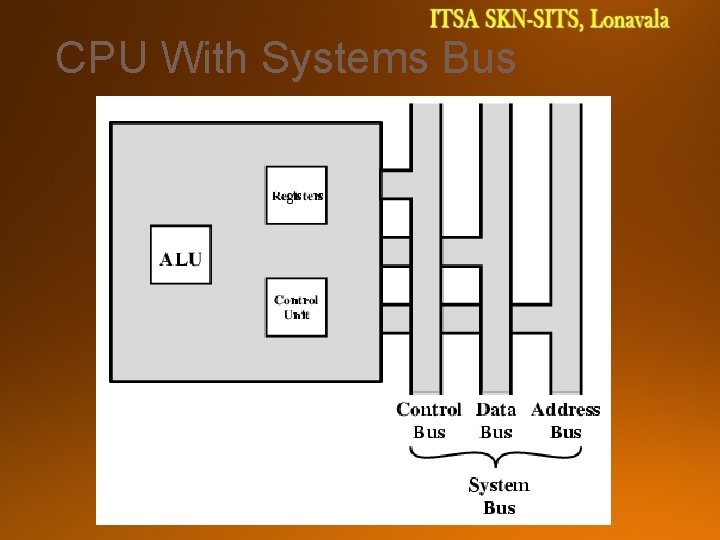

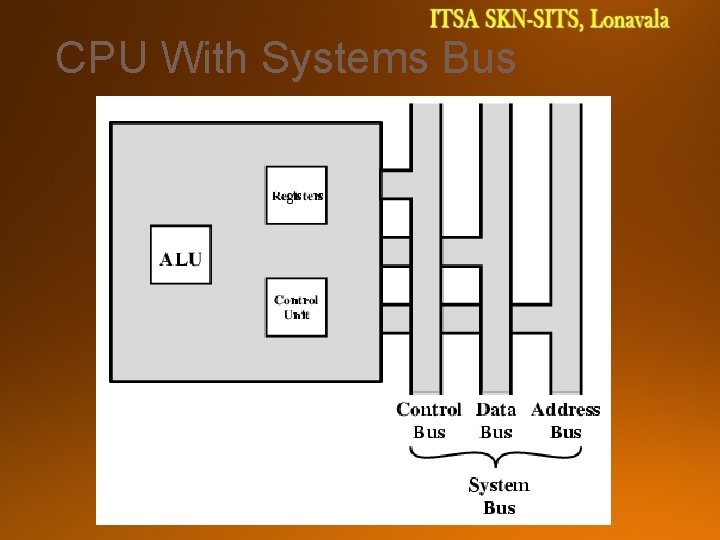

CPU With Systems Bus

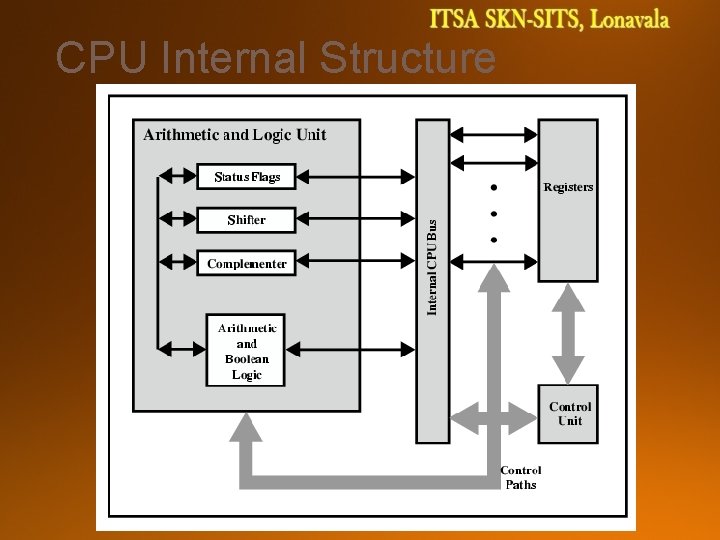

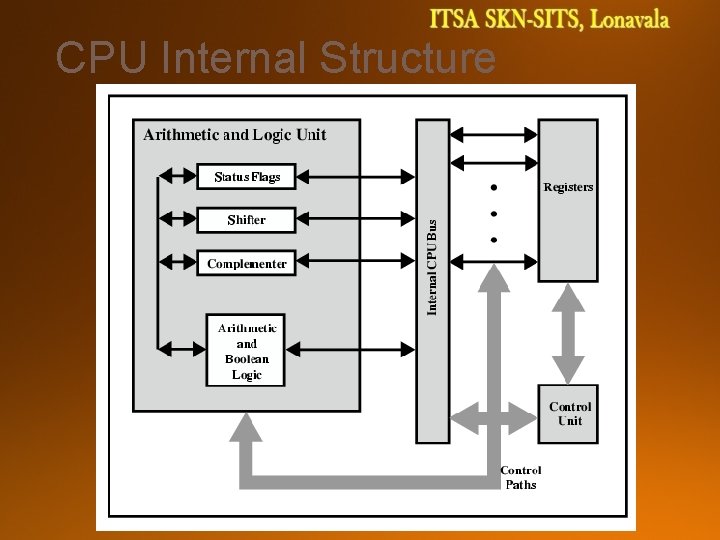

CPU Internal Structure

What is an instruction set? The complete collection of instructions that are understood by a CPU Machine Code Binary Usually represented by assembly codes

Elements of an Instruction Operation code (Op code) Do Source Operand reference To this Result Operand reference Put the answer here Next Instruction Reference When you have done that, do this. . .

Where have all the Operands gone? (Areas of source and result operands) Main memory (or virtual memory or cache) CPU register I/O device

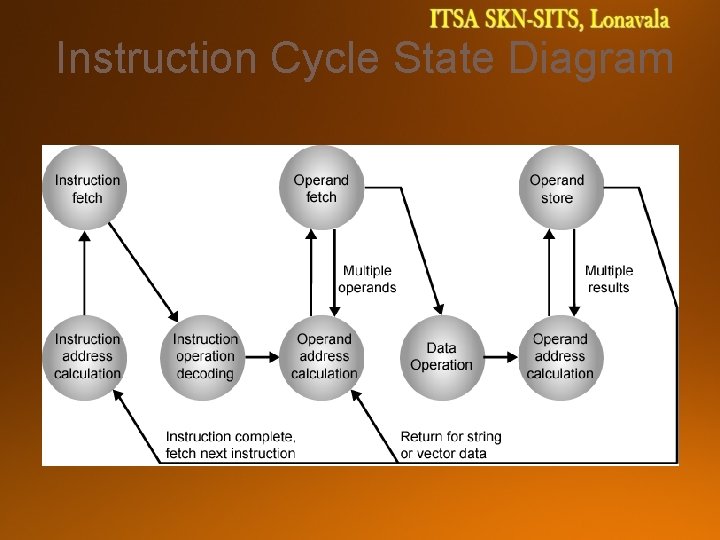

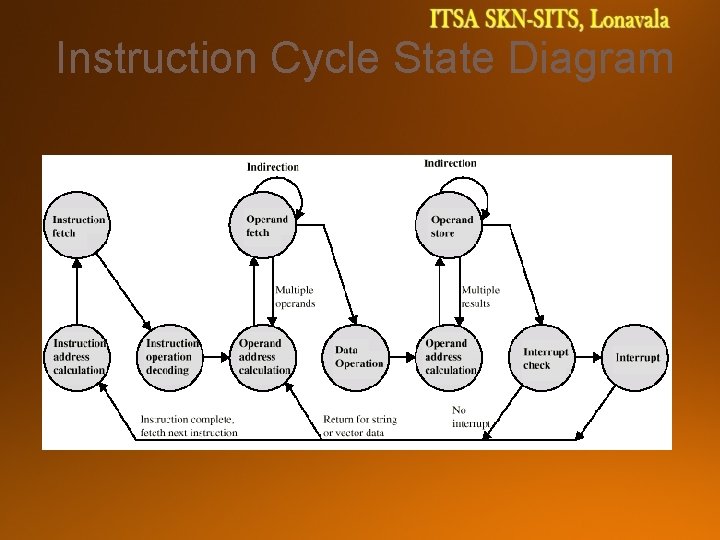

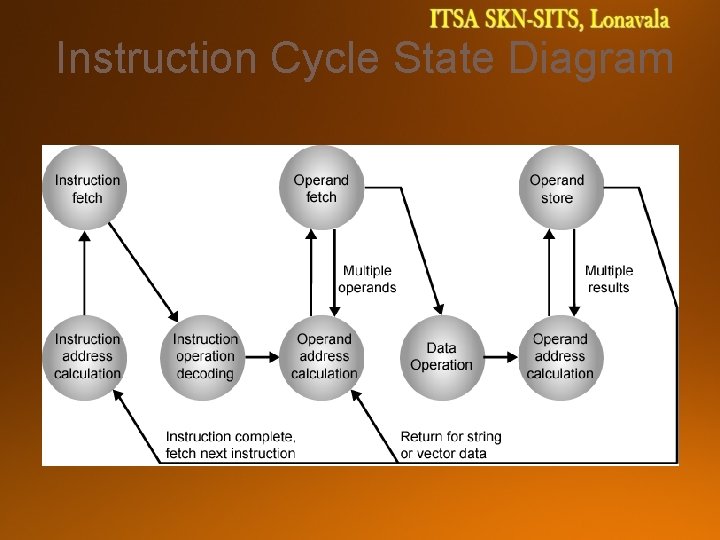

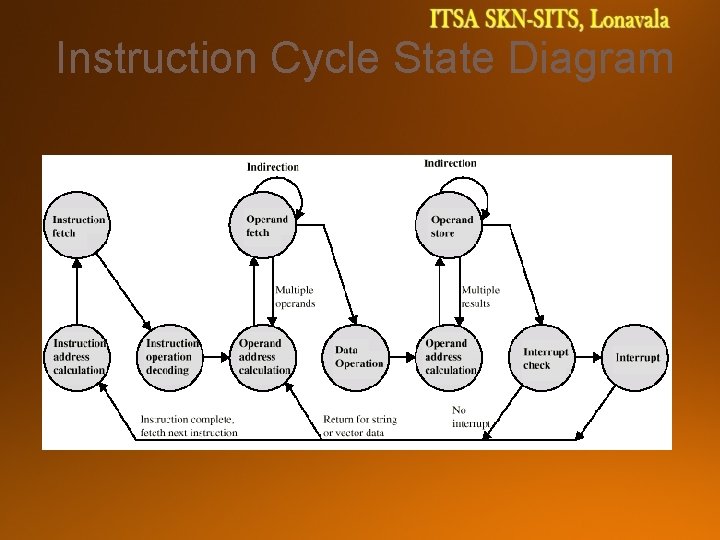

Instruction Cycle State Diagram

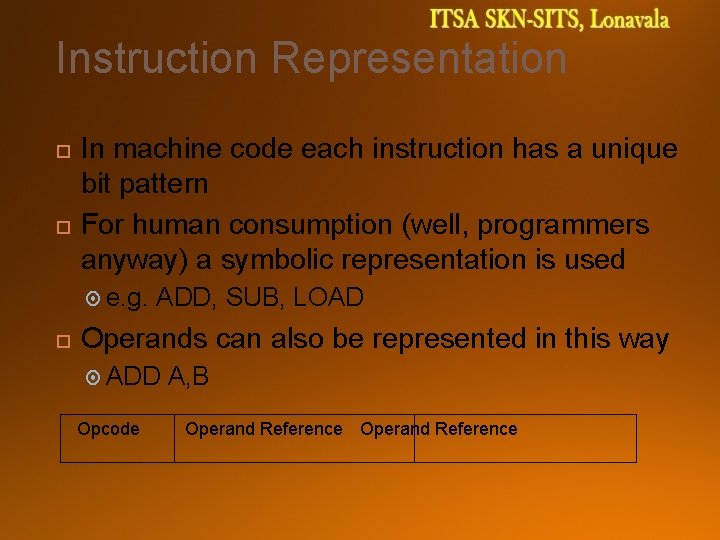

Instruction Representation In machine code each instruction has a unique bit pattern For human consumption (well, programmers anyway) a symbolic representation is used e. g. ADD, SUB, LOAD Operands can also be represented in this way ADD Opcode A, B Operand Reference

Instruction Types Ways of Classification According to function According to number of addresses Data processing Data storage (main memory) Data movement (I/O) Program flow control

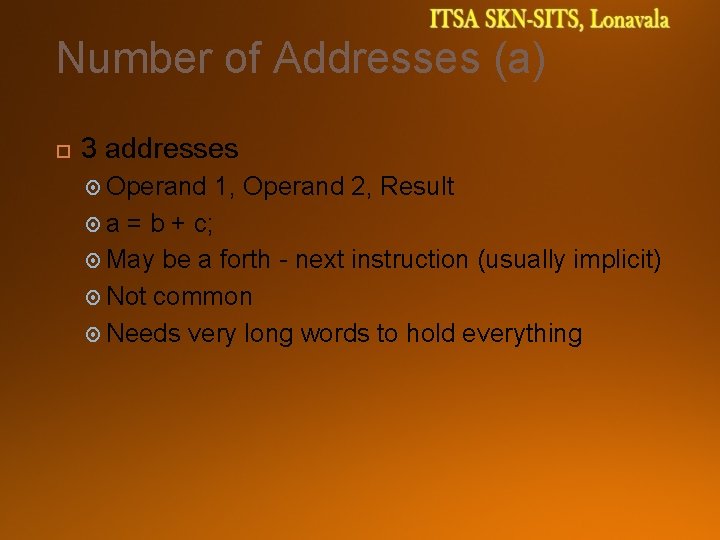

Number of Addresses (a) 3 addresses Operand a 1, Operand 2, Result = b + c; May be a forth - next instruction (usually implicit) Not common Needs very long words to hold everything

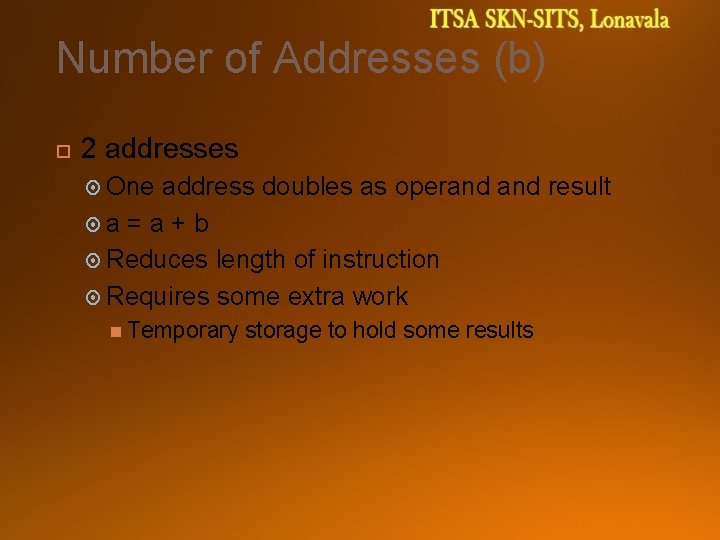

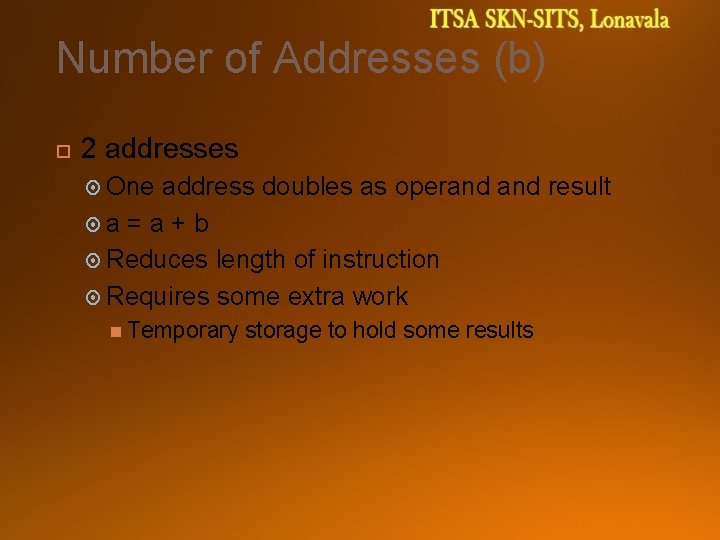

Number of Addresses (b) 2 addresses One address doubles as operand result a = a + b Reduces length of instruction Requires some extra work Temporary storage to hold some results

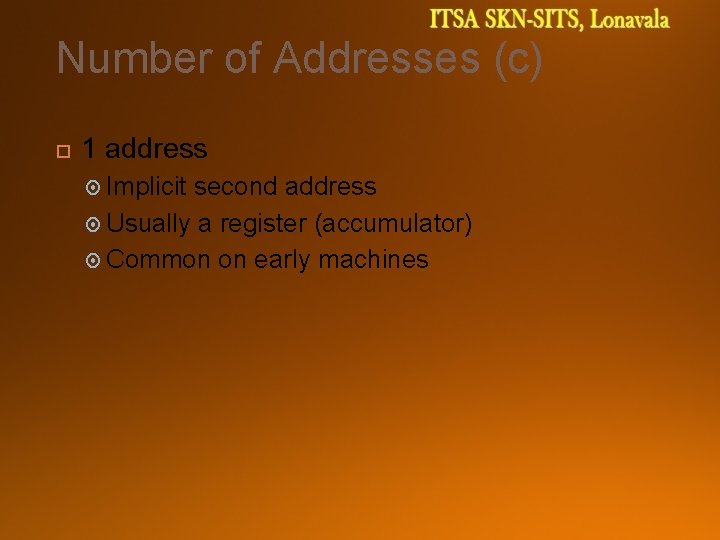

Number of Addresses (c) 1 address Implicit second address Usually a register (accumulator) Common on early machines

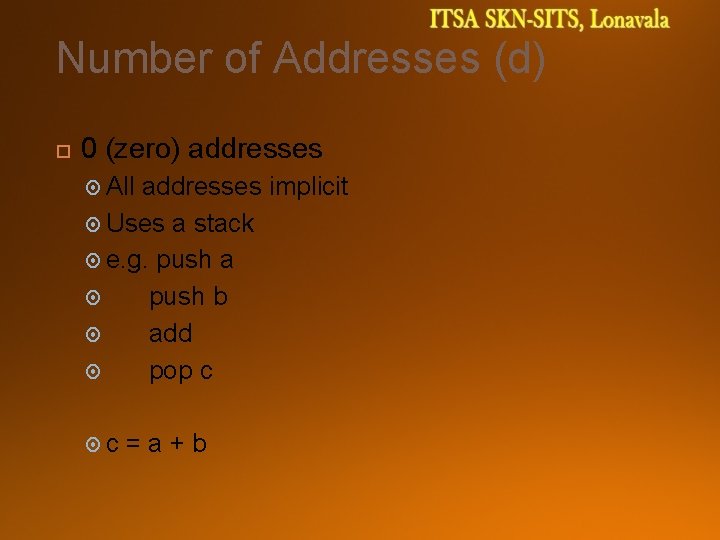

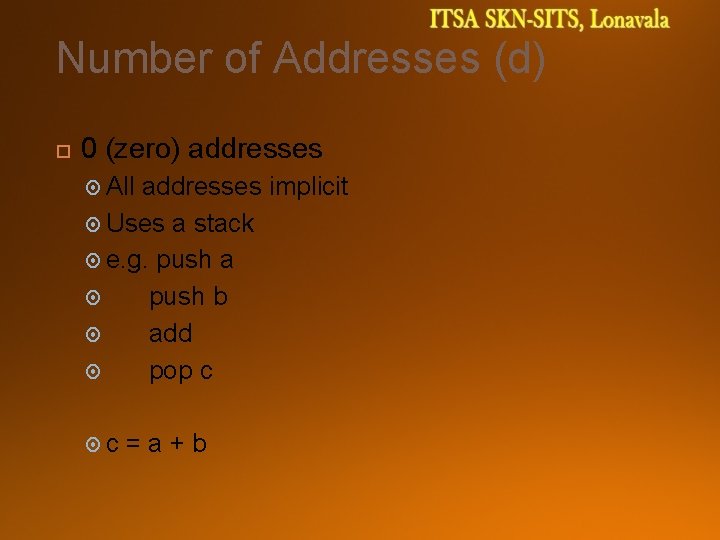

Number of Addresses (d) 0 (zero) addresses All addresses implicit Uses a stack e. g. push a push b add pop c c =a+b

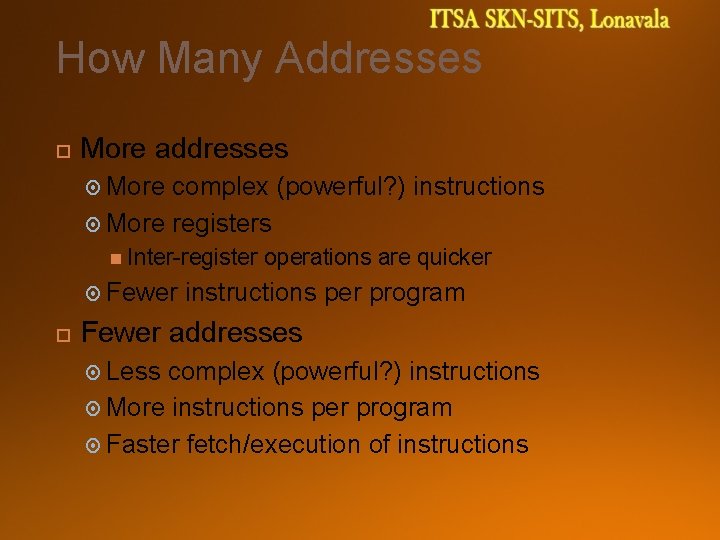

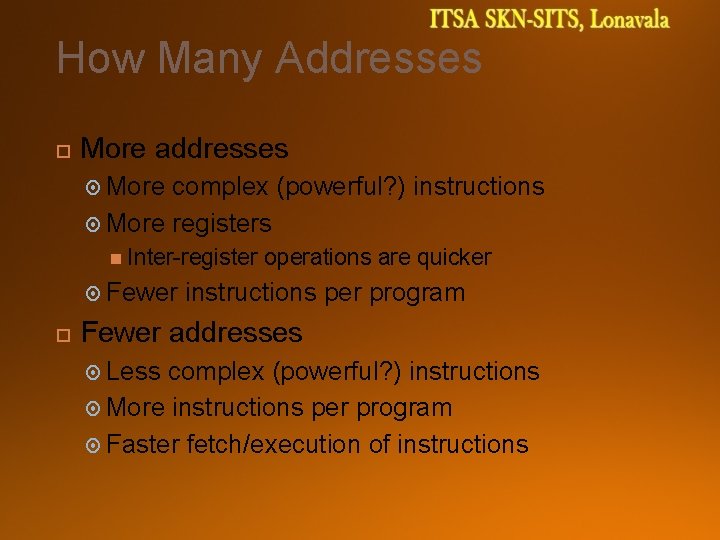

How Many Addresses More addresses More complex (powerful? ) instructions More registers Inter-register Fewer operations are quicker instructions per program Fewer addresses Less complex (powerful? ) instructions More instructions per program Faster fetch/execution of instructions

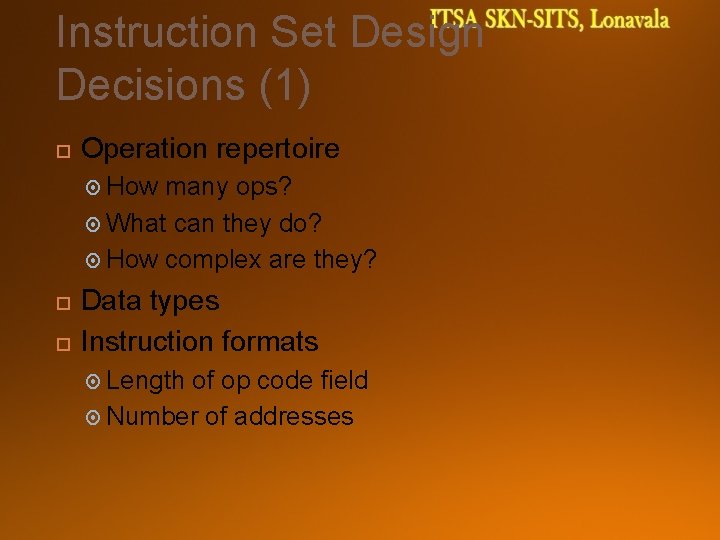

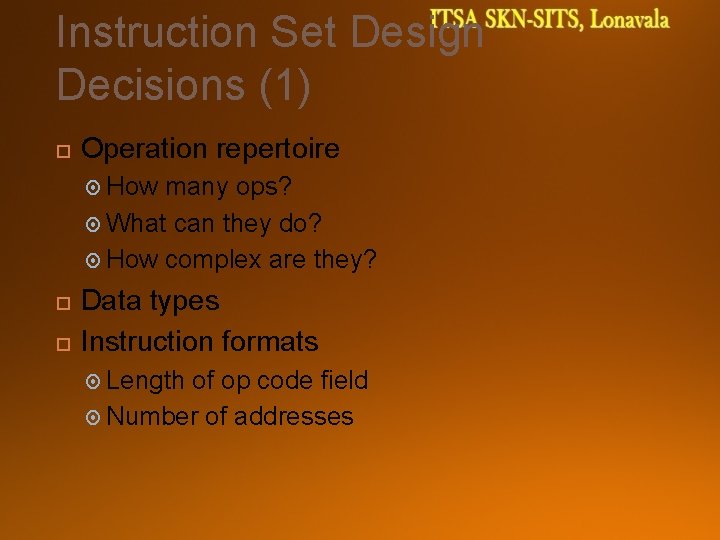

Instruction Set Design Decisions (1) Operation repertoire How many ops? What can they do? How complex are they? Data types Instruction formats Length of op code field Number of addresses

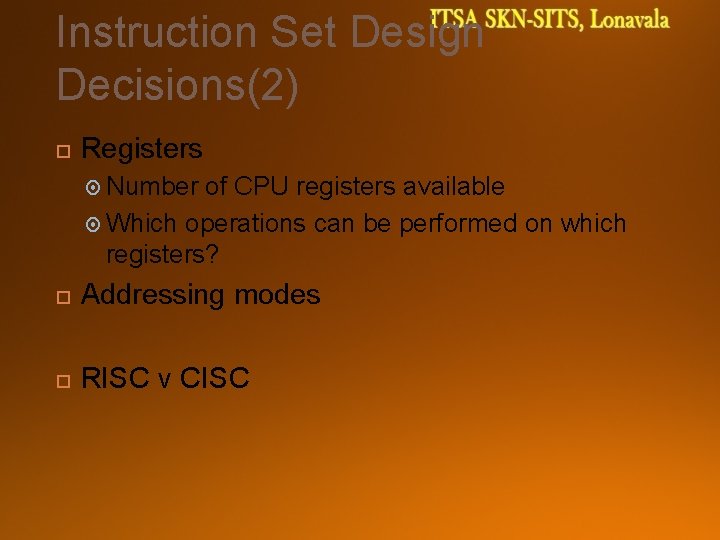

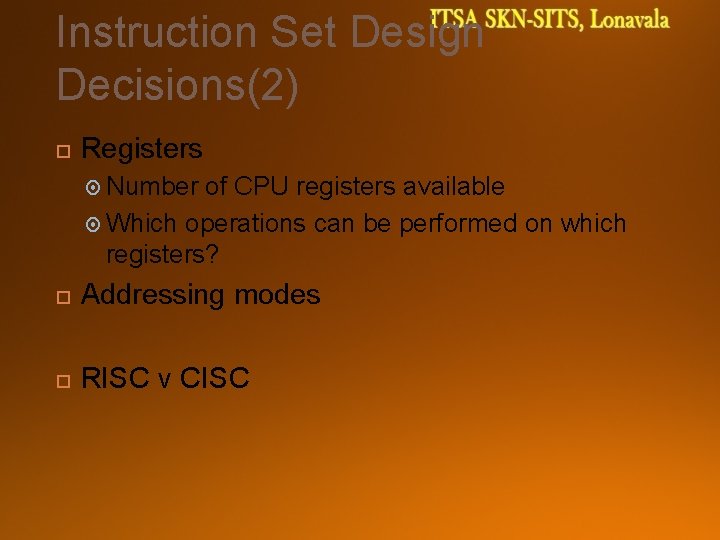

Instruction Set Design Decisions(2) Registers Number of CPU registers available Which operations can be performed on which registers? Addressing modes RISC v CISC

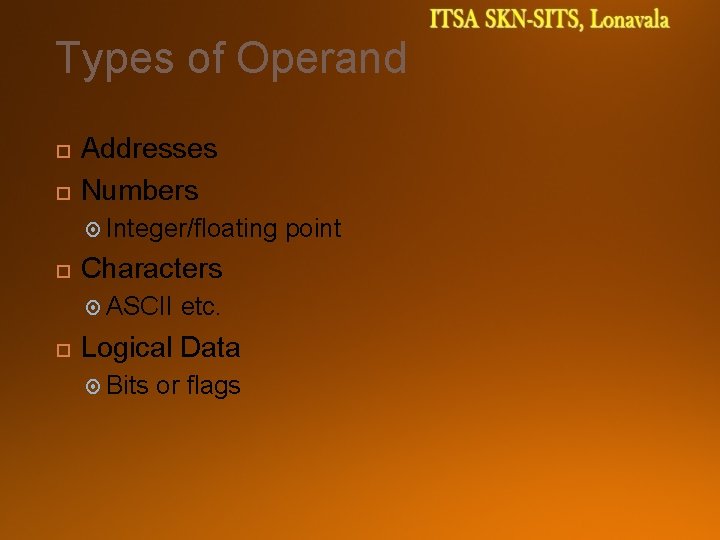

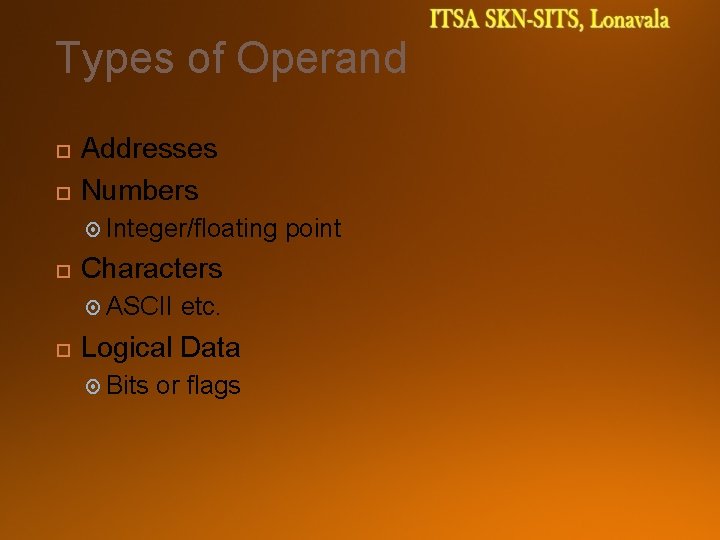

Types of Operand Addresses Numbers Integer/floating Characters ASCII etc. Logical Data Bits or flags point

Types of Operation Data Transfer Arithmetic Logical Conversion I/O System Control Transfer of Control

Data Transfer Specify Source Destination Amount May be different instructions for different movements e. g. of data IBM 370 Or one instruction and different addresses e. g. VAX

Arithmetic Add, Subtract, Multiply, Divide Signed Integer Floating point ? May include Increment (a++) Decrement (a--) Negate (-a)

Logical Bitwise operations AND, OR, NOT

Conversion E. g. Binary to Decimal

Input/Output May be specific instructions May be done using data movement instructions (memory mapped) May be done by a separate controller (DMA)

Systems Control Privileged instructions CPU needs to be in specific state Kernel mode For operating systems use

Transfer of Control Branch e. g. branch to x if result is zero Skip e. g. increment and skip if zero Branch xxxx ADD A Subroutine call c. f. interrupt call

Addressing Modes Immediate Direct Indirect Register Indirect Displacement (Indexed) Stack

Immediate Addressing Operand is part of instruction Operand = address field e. g. ADD 5 Add 5 to contents of accumulator 5 is operand No memory reference to fetch data Fast Limited range

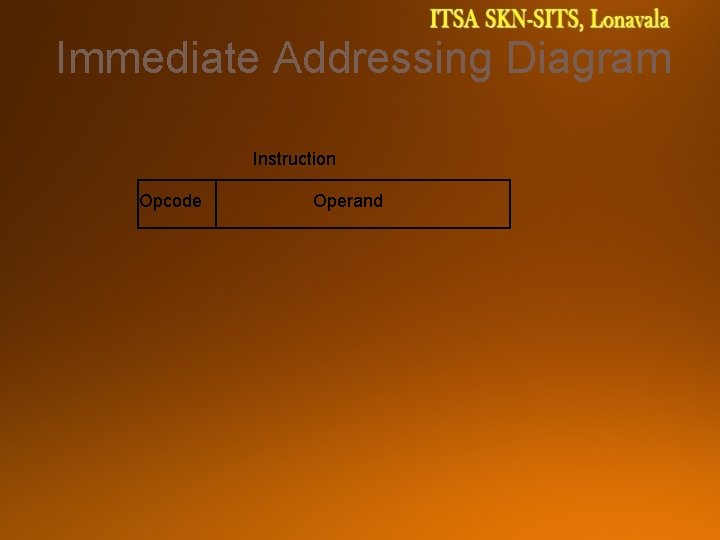

Immediate Addressing Diagram Instruction Opcode Operand

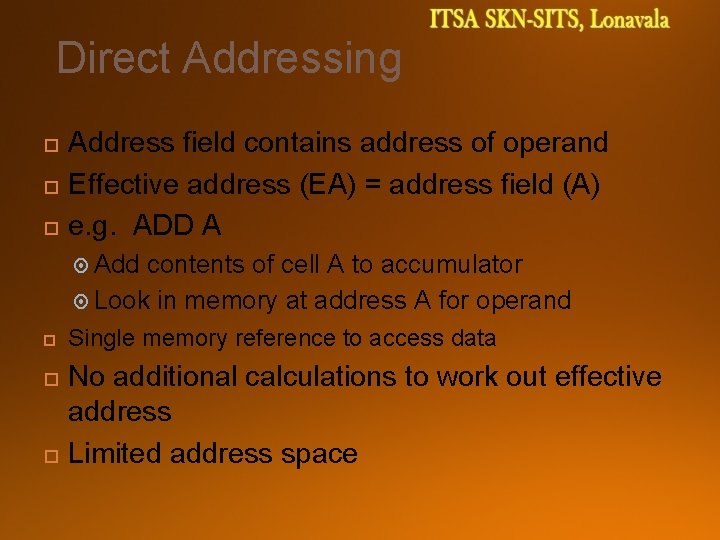

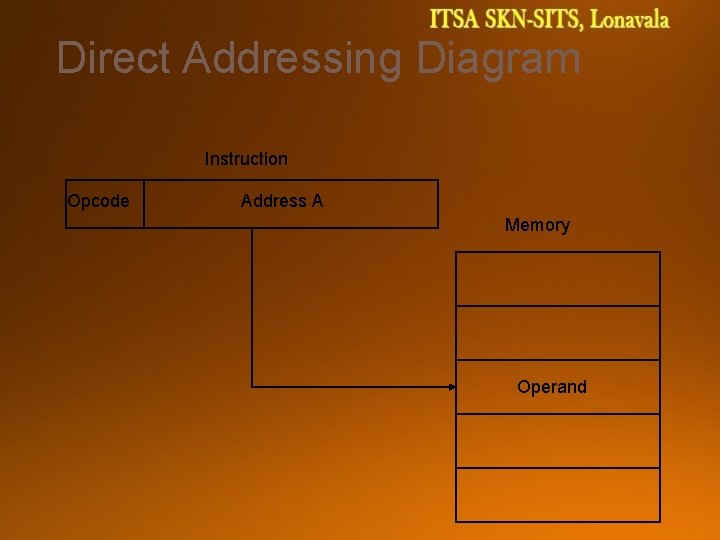

Direct Addressing Address field contains address of operand Effective address (EA) = address field (A) e. g. ADD A Add contents of cell A to accumulator Look in memory at address A for operand Single memory reference to access data No additional calculations to work out effective address Limited address space

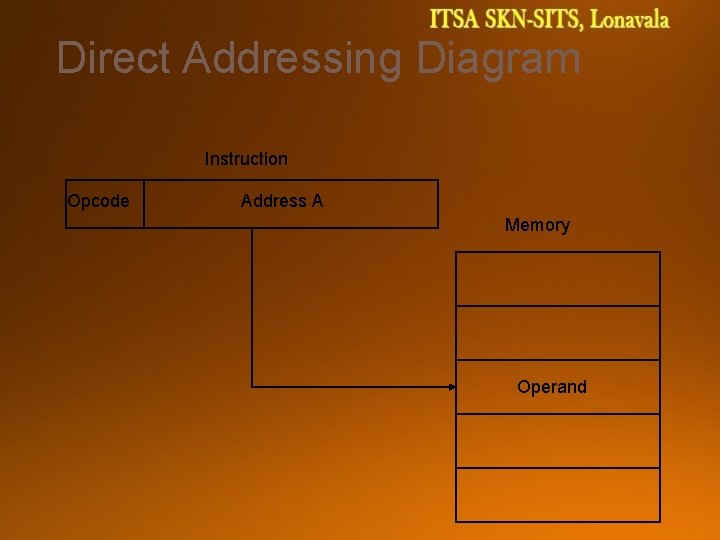

Direct Addressing Diagram Instruction Opcode Address A Memory Operand

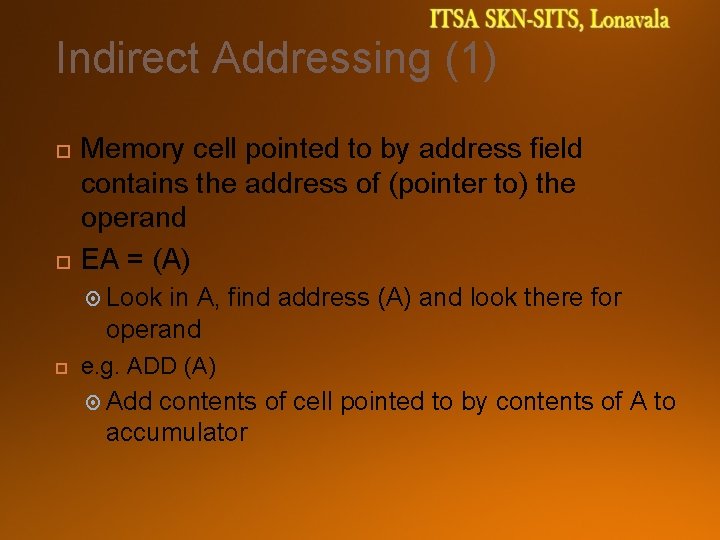

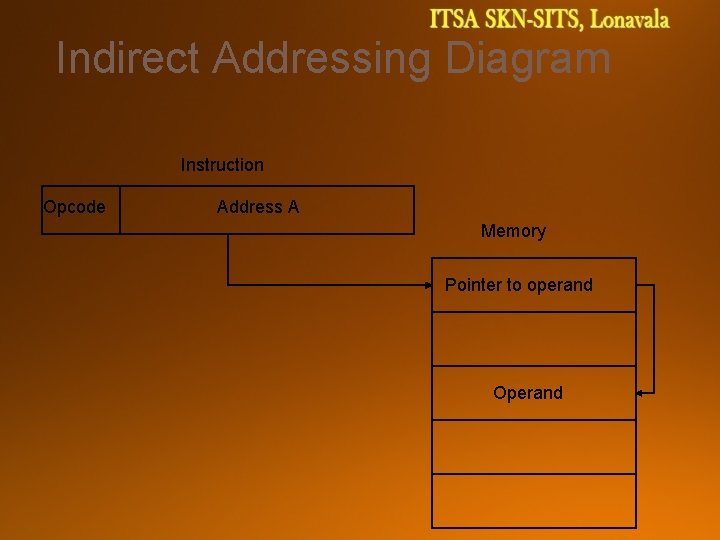

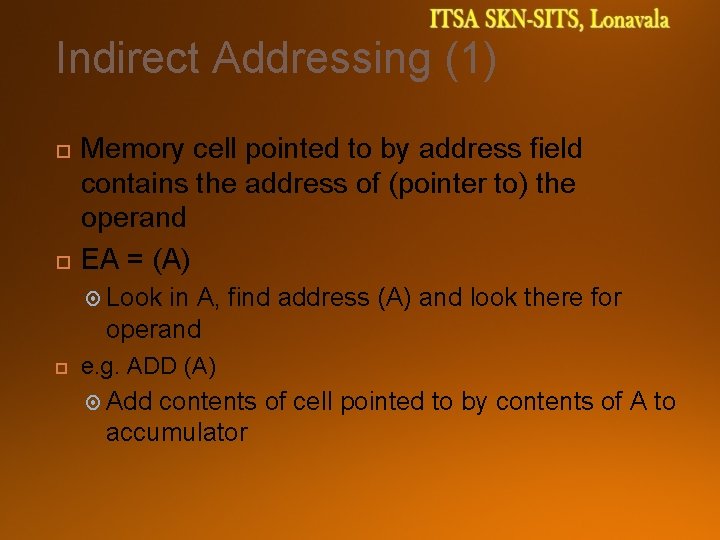

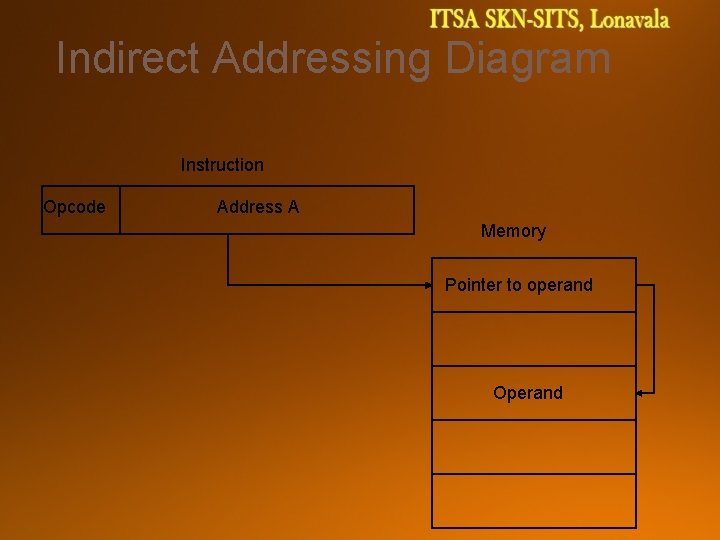

Indirect Addressing (1) Memory cell pointed to by address field contains the address of (pointer to) the operand EA = (A) Look in A, find address (A) and look there for operand e. g. ADD (A) Add contents of cell pointed to by contents of A to accumulator

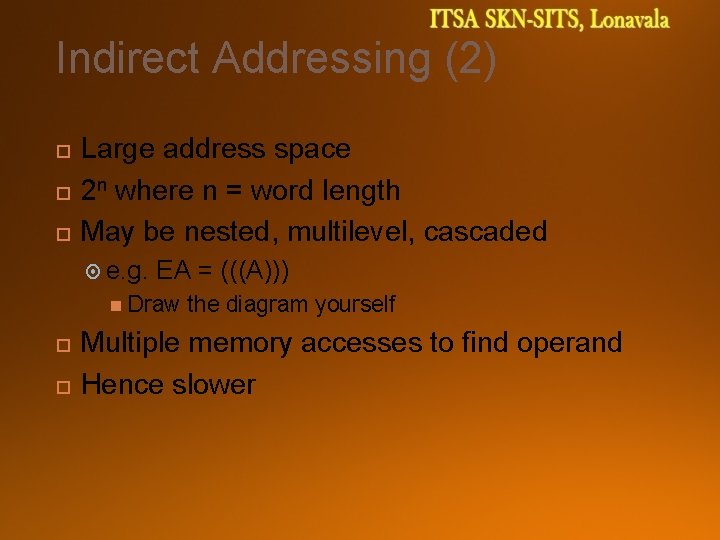

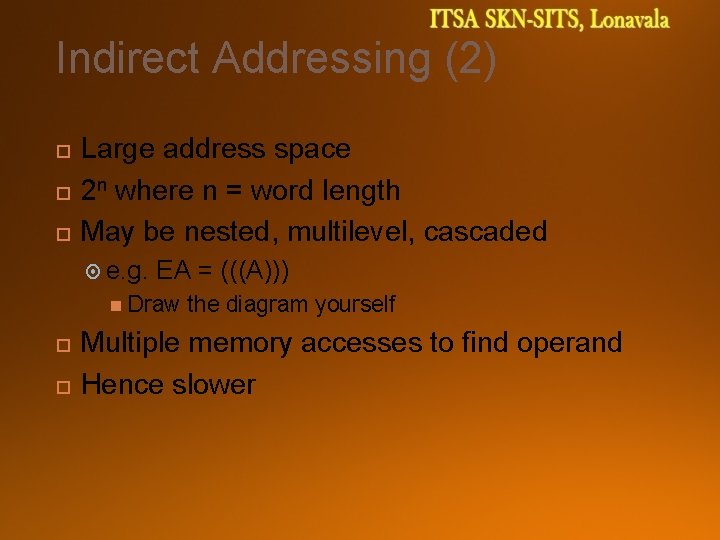

Indirect Addressing (2) Large address space 2 n where n = word length May be nested, multilevel, cascaded e. g. EA = (((A))) Draw the diagram yourself Multiple memory accesses to find operand Hence slower

Indirect Addressing Diagram Instruction Opcode Address A Memory Pointer to operand Operand

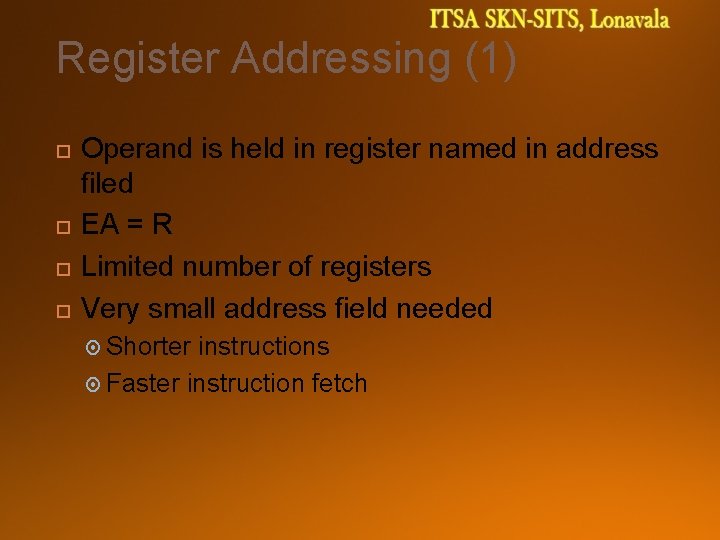

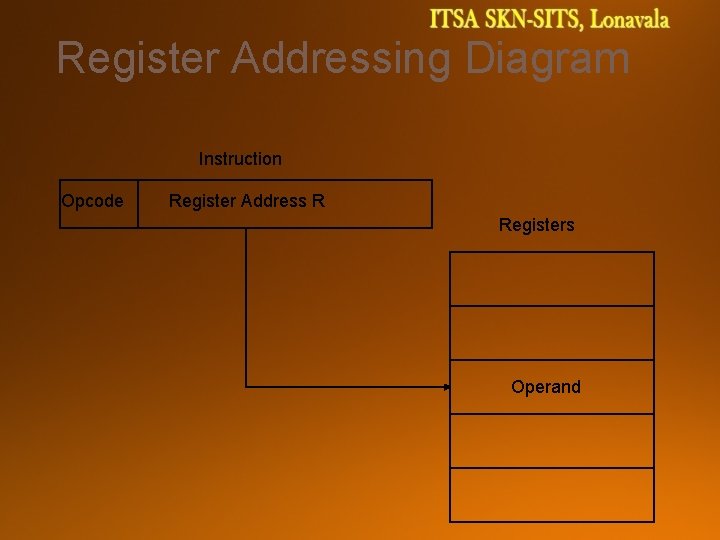

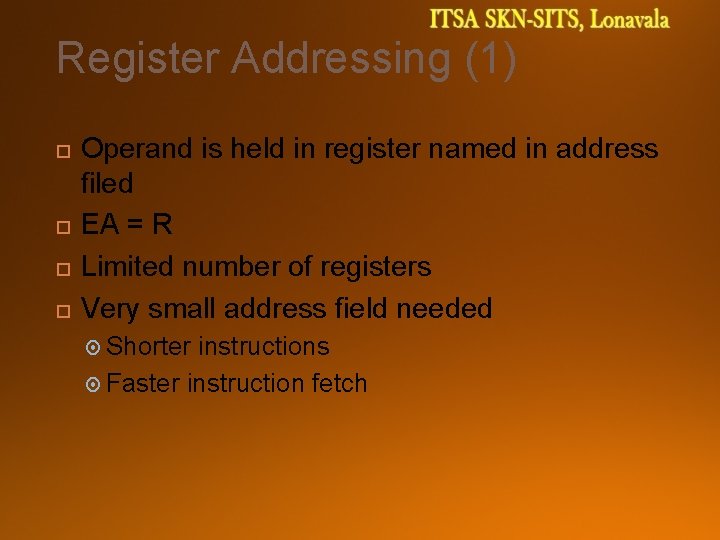

Register Addressing (1) Operand is held in register named in address filed EA = R Limited number of registers Very small address field needed Shorter instructions Faster instruction fetch

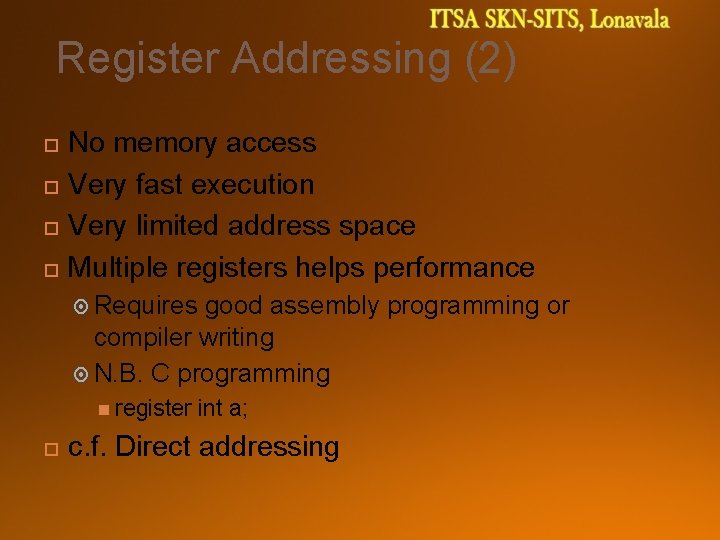

Register Addressing (2) No memory access Very fast execution Very limited address space Multiple registers helps performance Requires good assembly programming or compiler writing N. B. C programming register int a; c. f. Direct addressing

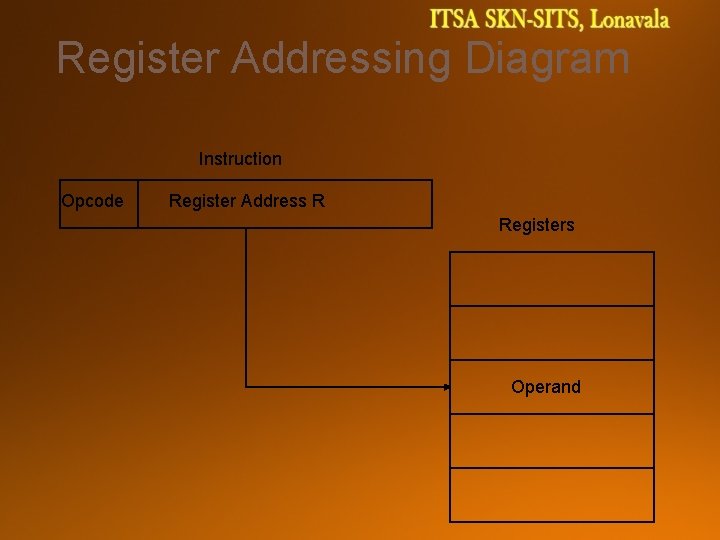

Register Addressing Diagram Instruction Opcode Register Address R Registers Operand

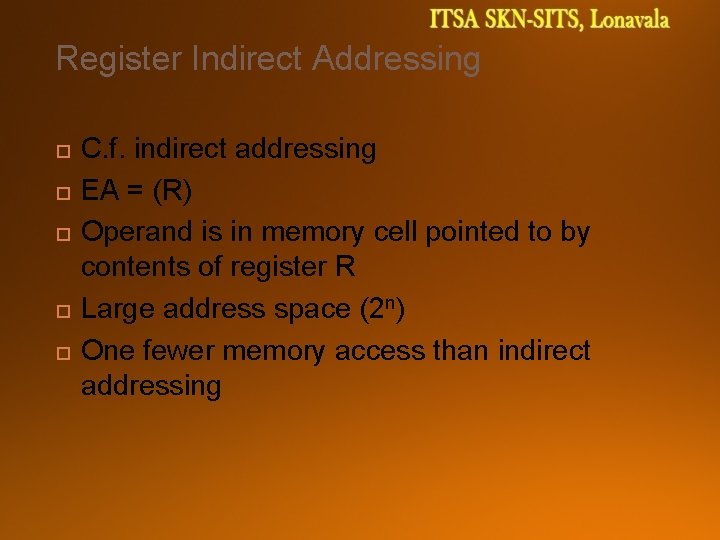

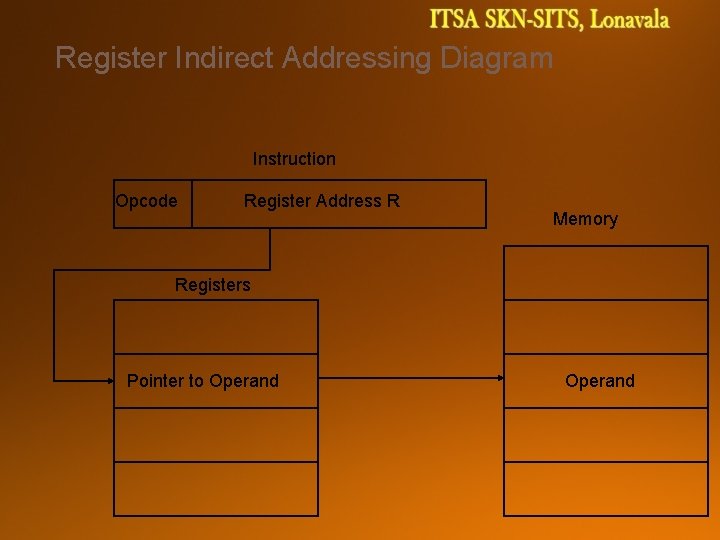

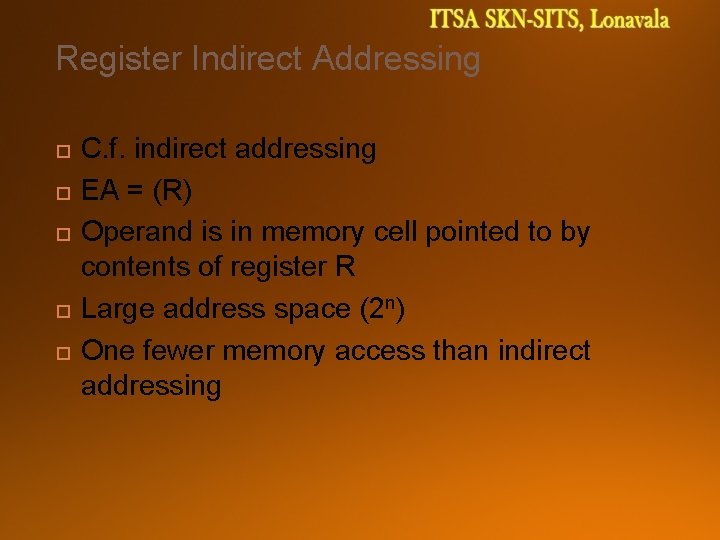

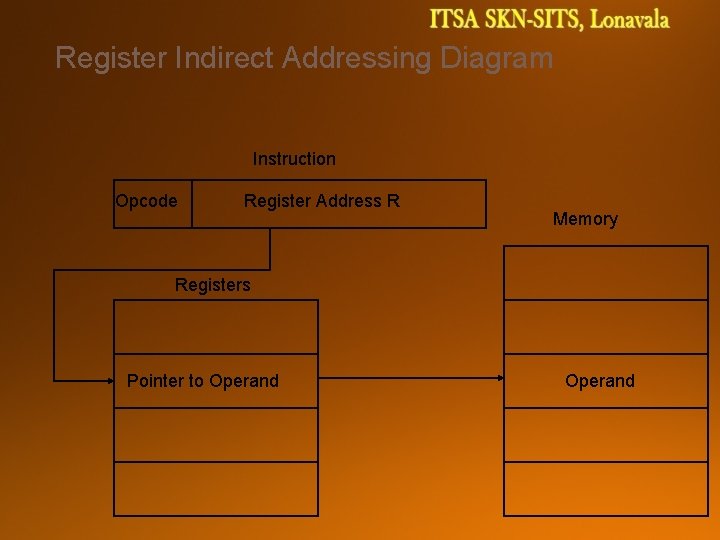

Register Indirect Addressing C. f. indirect addressing EA = (R) Operand is in memory cell pointed to by contents of register R Large address space (2 n) One fewer memory access than indirect addressing

Register Indirect Addressing Diagram Instruction Opcode Register Address R Memory Registers Pointer to Operand

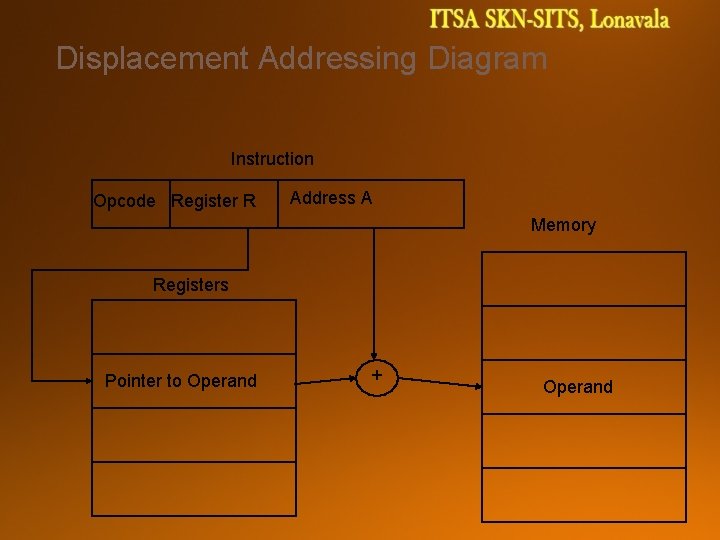

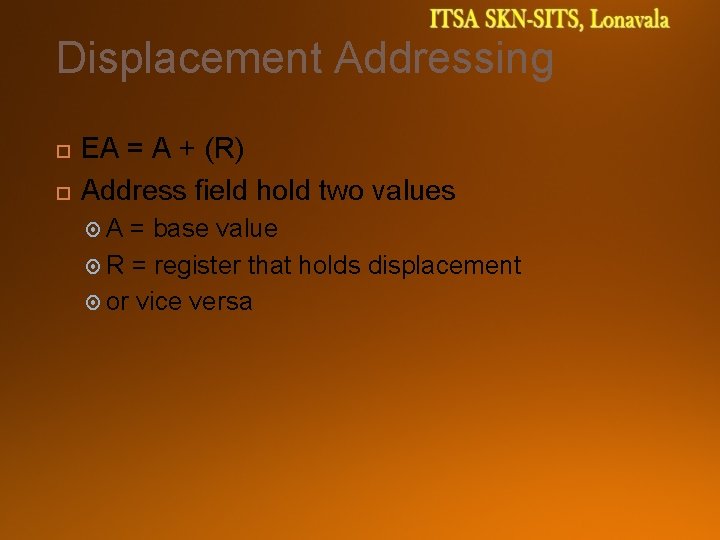

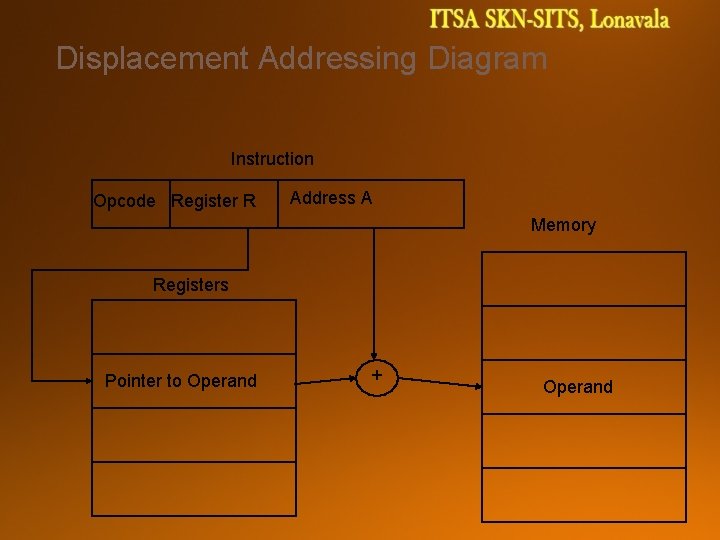

Displacement Addressing EA = A + (R) Address field hold two values A = base value R = register that holds displacement or vice versa

Displacement Addressing Diagram Instruction Opcode Register R Address A Memory Registers Pointer to Operand + Operand

Relative Addressing A version of displacement addressing R = Program counter, PC EA = A + (PC) i. e. get operand from A cells from current location pointed to by PC c. f locality of reference & cache usage

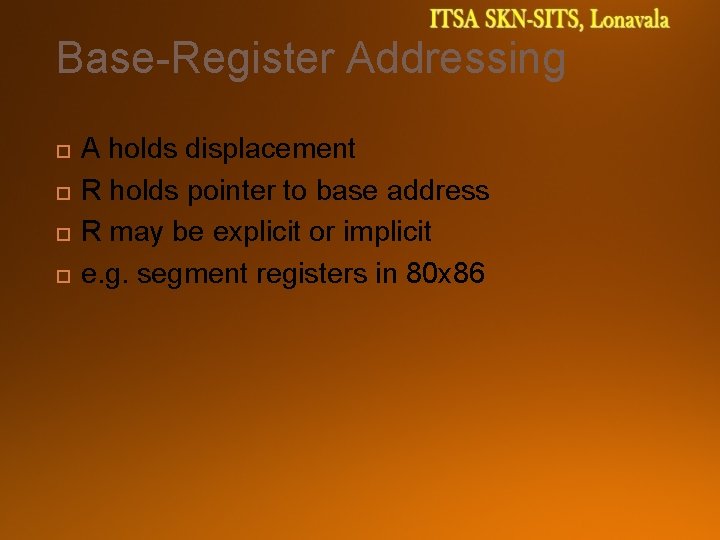

Base-Register Addressing A holds displacement R holds pointer to base address R may be explicit or implicit e. g. segment registers in 80 x 86

Indexed Addressing A = base R = displacement EA = A + R Good for accessing arrays EA =A+R R++

Combinations Postindex EA = (A) + (R) Preindex EA = (A+(R))

Stack Addressing Operand is (implicitly) on top of stack e. g. ADD Pop two items from stack and add

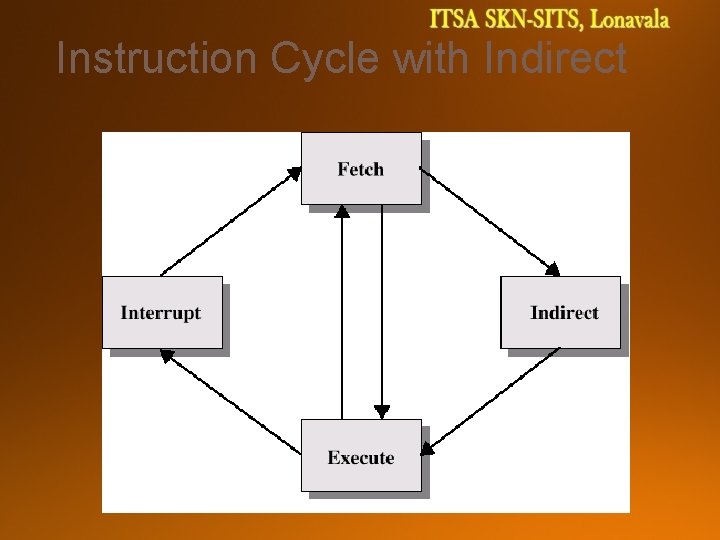

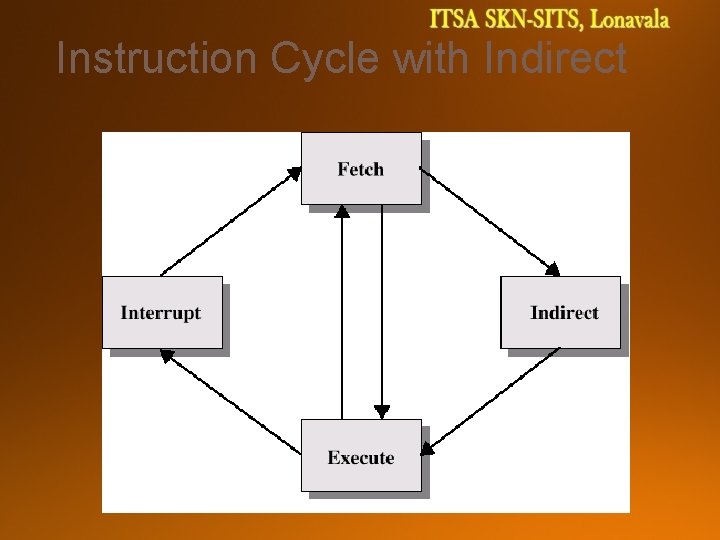

Instruction Cycle Fetch Indirect Interrupt Decode Execute

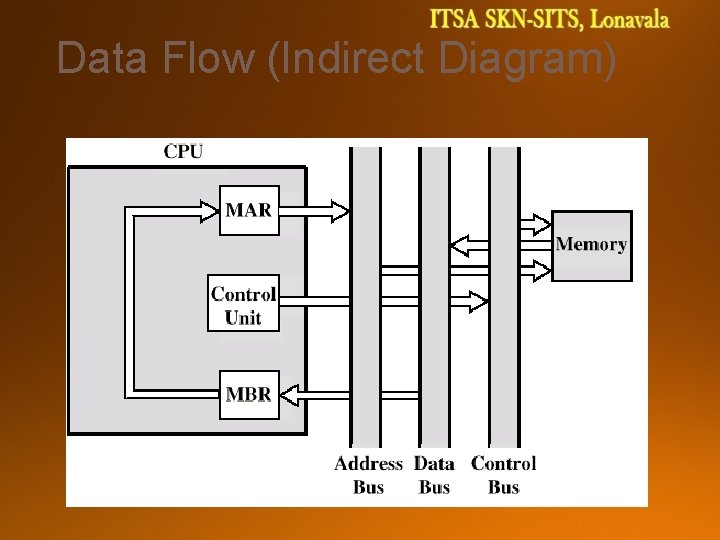

Indirect Cycle May require memory access to fetch operands Indirect addressing requires more memory accesses Can be thought of as additional instruction subcycle

Instruction Cycle with Indirect

Instruction Cycle State Diagram

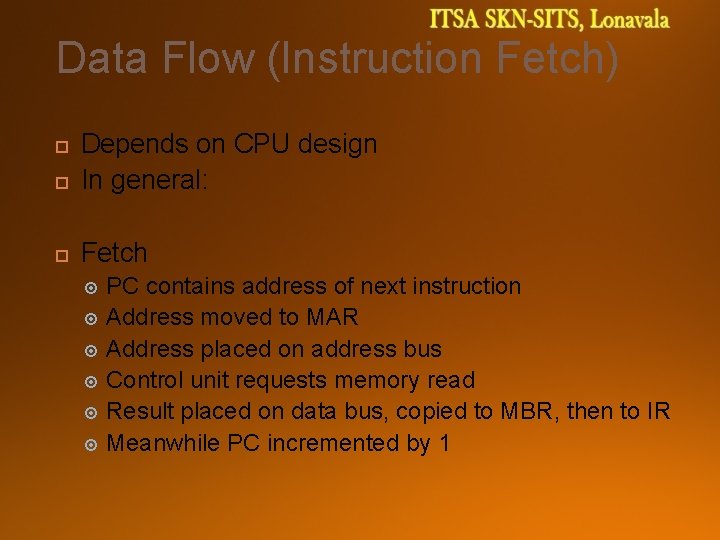

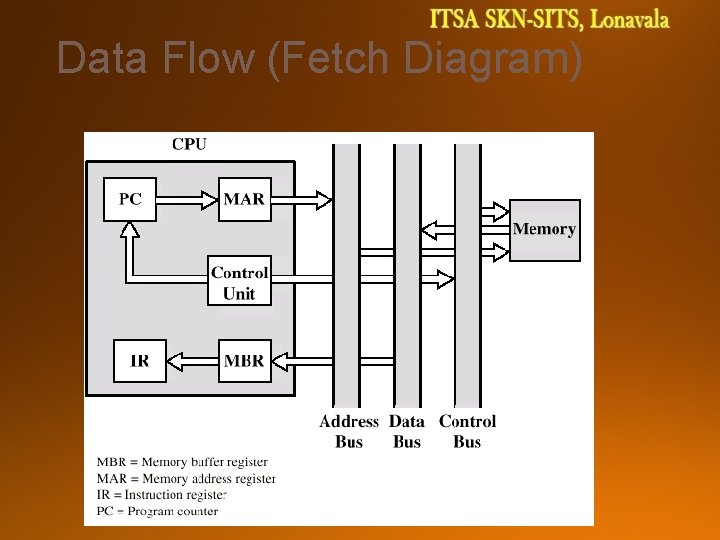

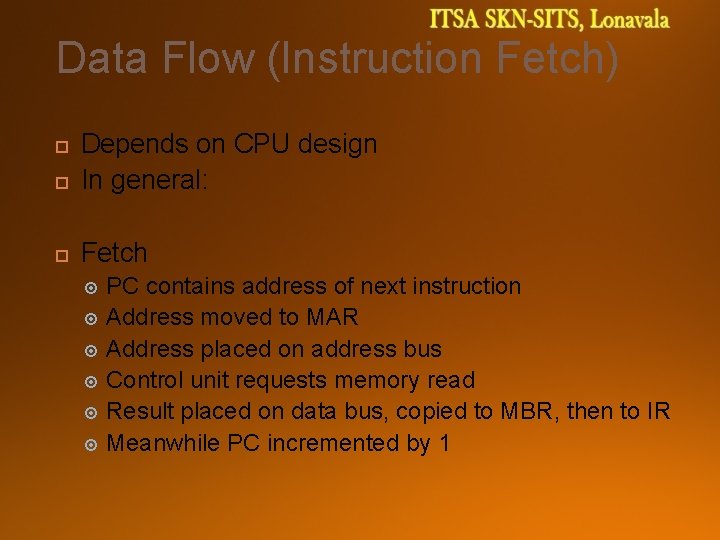

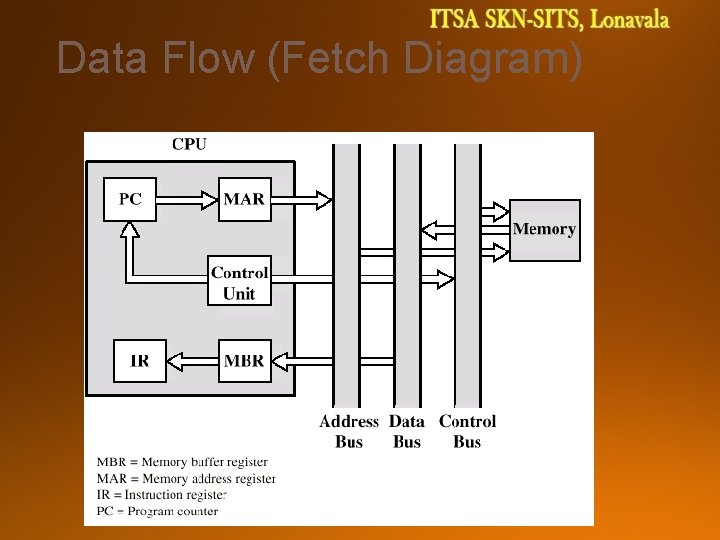

Data Flow (Instruction Fetch) Depends on CPU design In general: Fetch PC contains address of next instruction Address moved to MAR Address placed on address bus Control unit requests memory read Result placed on data bus, copied to MBR, then to IR Meanwhile PC incremented by 1

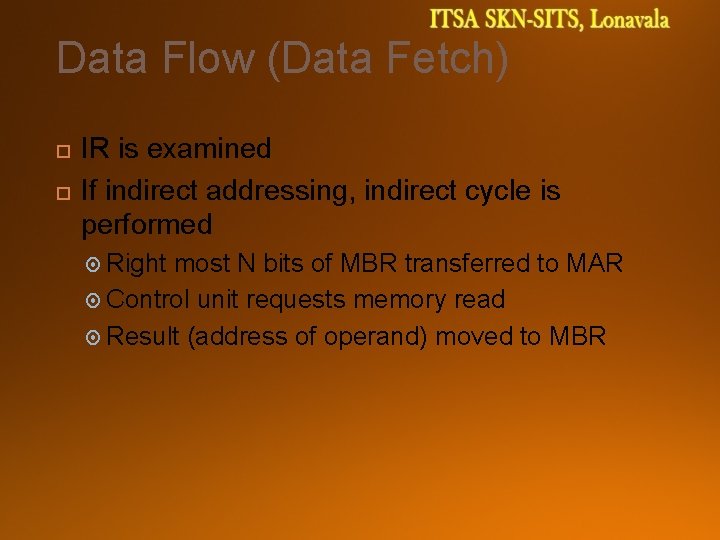

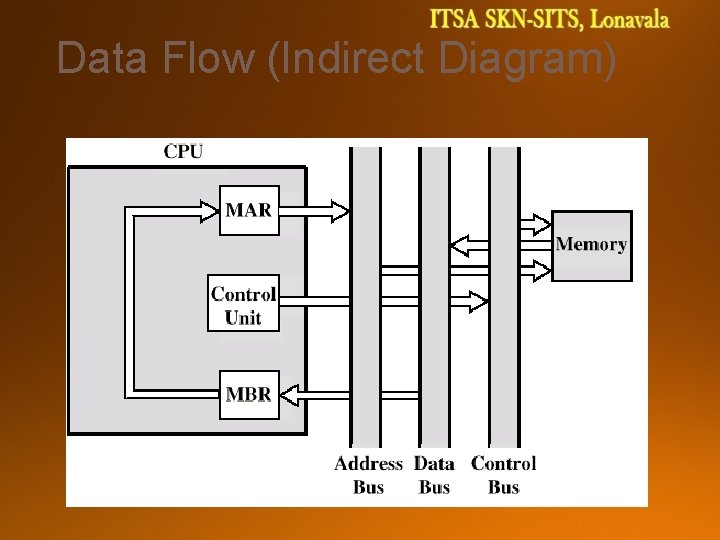

Data Flow (Data Fetch) IR is examined If indirect addressing, indirect cycle is performed Right most N bits of MBR transferred to MAR Control unit requests memory read Result (address of operand) moved to MBR

Data Flow (Fetch Diagram)

Data Flow (Indirect Diagram)

Data Flow (Execute) May take many forms Depends on instruction being executed May include Memory read/write Input/Output Register transfers ALU operations

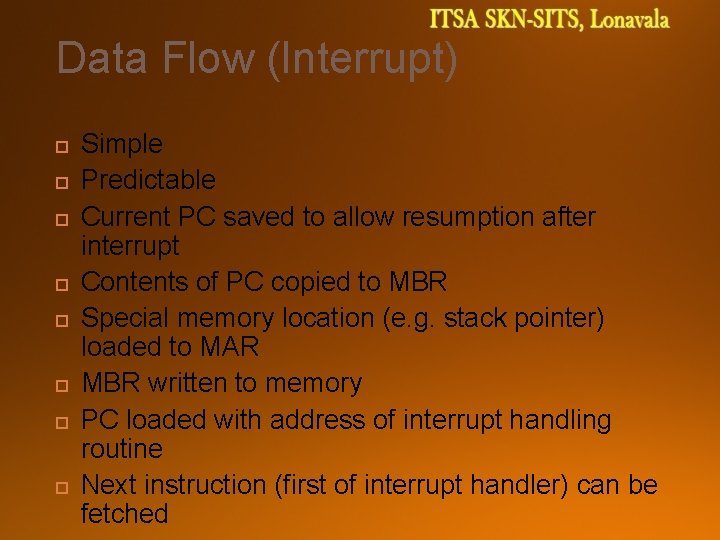

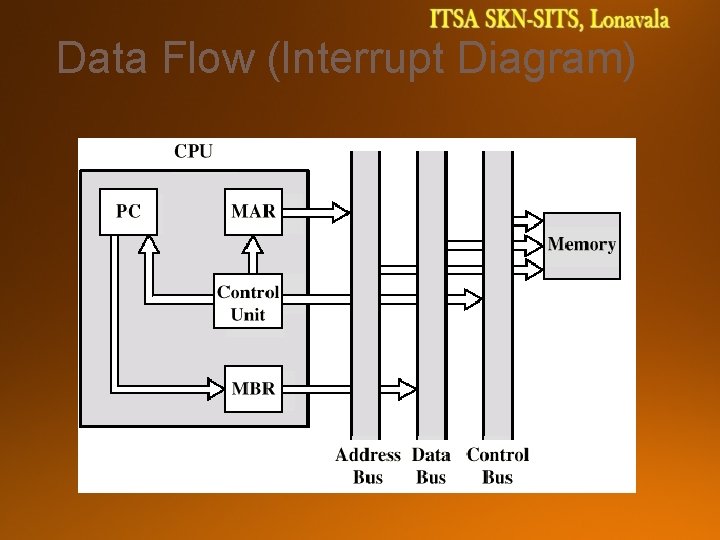

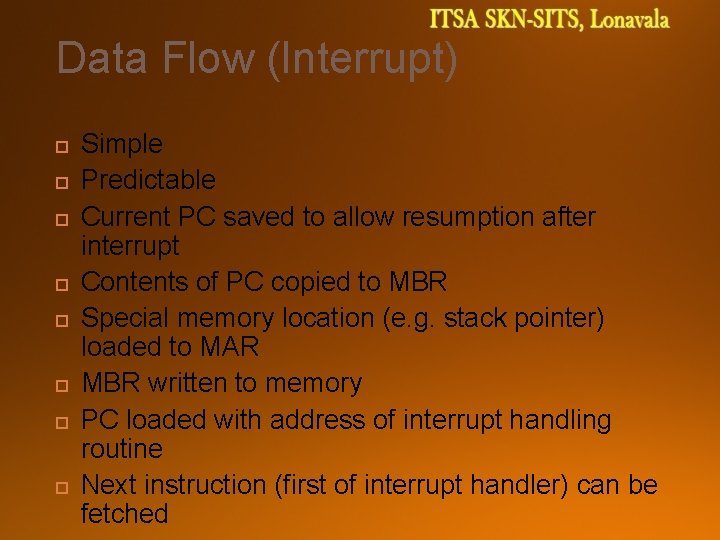

Data Flow (Interrupt) Simple Predictable Current PC saved to allow resumption after interrupt Contents of PC copied to MBR Special memory location (e. g. stack pointer) loaded to MAR MBR written to memory PC loaded with address of interrupt handling routine Next instruction (first of interrupt handler) can be fetched

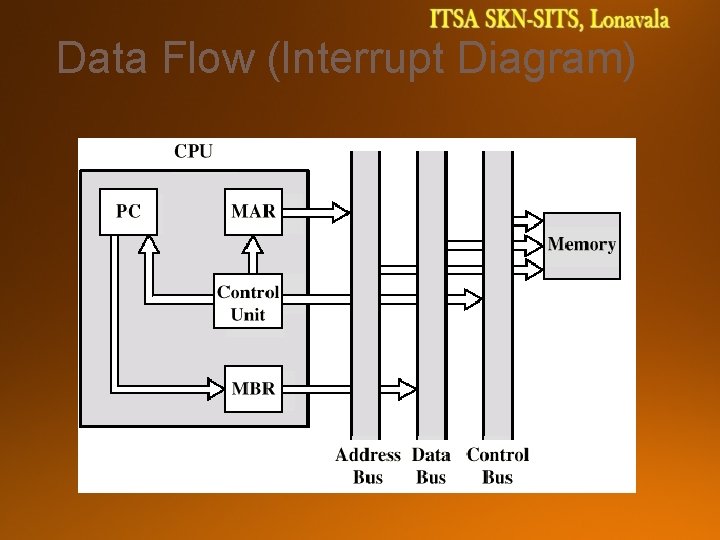

Data Flow (Interrupt Diagram)

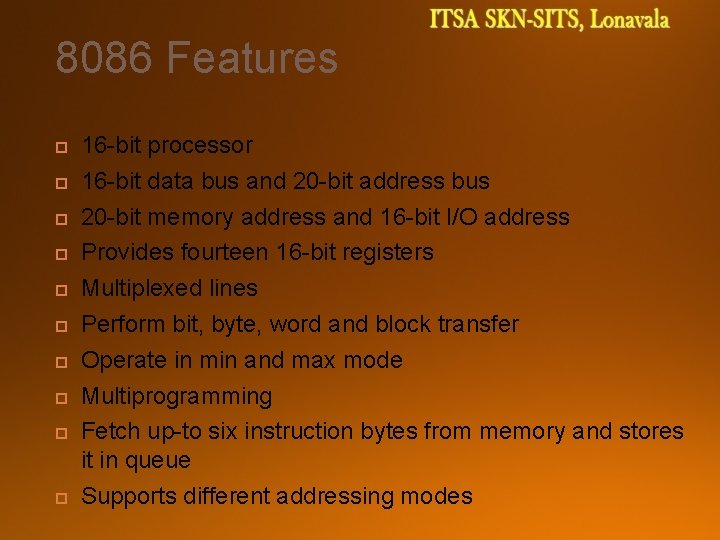

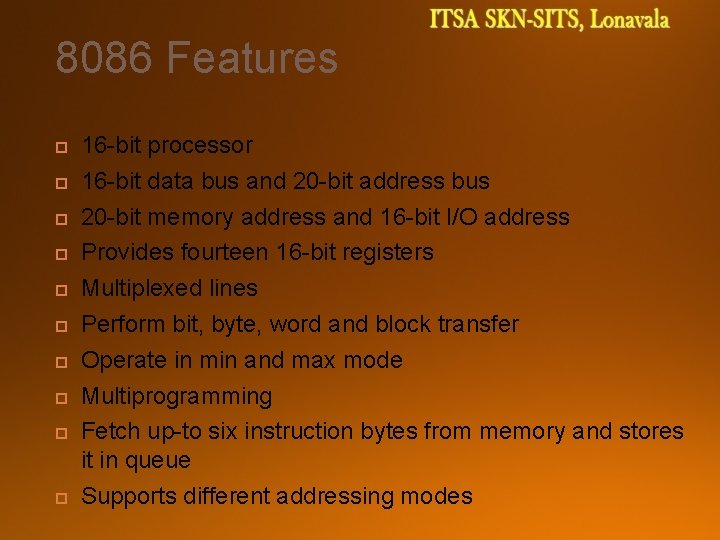

8086 Features 16 -bit processor 16 -bit data bus and 20 -bit address bus 20 -bit memory address and 16 -bit I/O address Provides fourteen 16 -bit registers Multiplexed lines Perform bit, byte, word and block transfer Operate in min and max mode Multiprogramming Fetch up-to six instruction bytes from memory and stores it in queue Supports different addressing modes

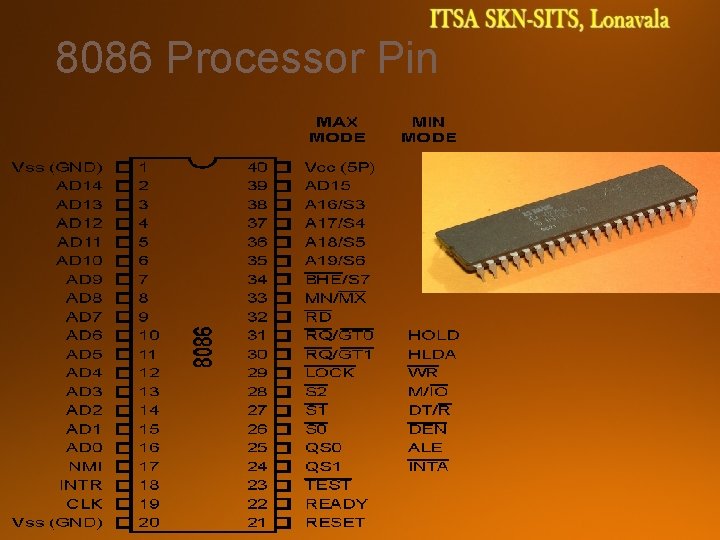

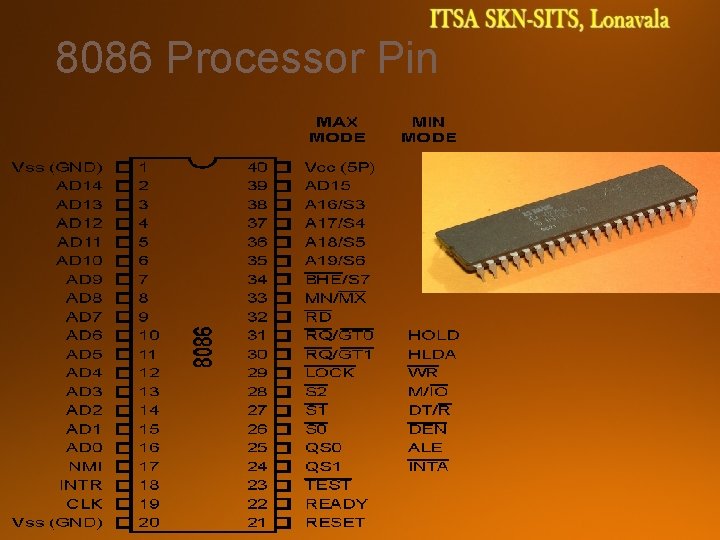

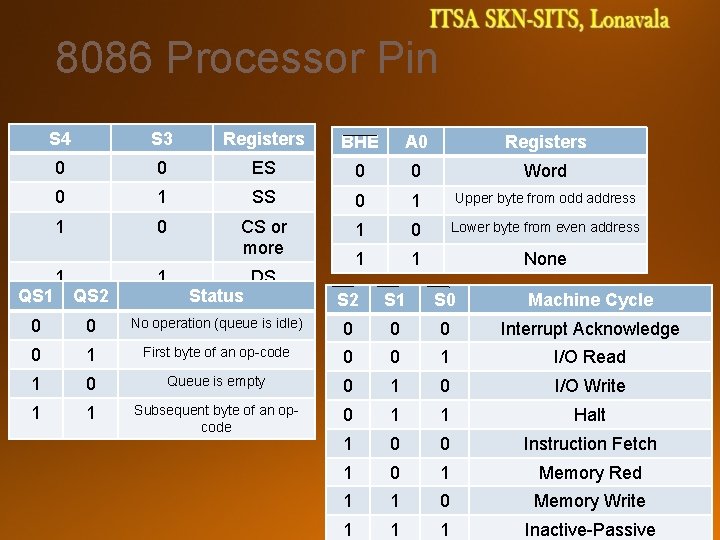

8086 Processor Pin

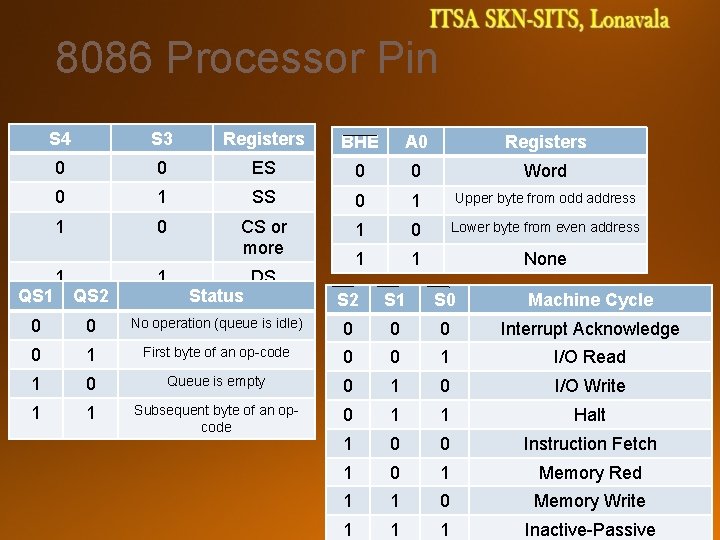

8086 Processor Pin S 4 S 3 Registers BHE A 0 Registers 0 0 ES 0 0 Word 0 1 SS 0 1 Upper byte from odd address 1 0 CS or more 1 0 Lower byte from even address 1 1 None QS 1 1 QS 2 1 Status DS S 2 S 1 S 0 Machine Cycle 0 0 No operation (queue is idle) 0 0 0 Interrupt Acknowledge 0 1 First byte of an op-code 0 0 1 I/O Read 1 0 Queue is empty 0 1 0 I/O Write 1 1 Subsequent byte of an opcode 0 1 1 Halt 1 0 0 Instruction Fetch 1 0 1 Memory Red 1 1 0 Memory Write 1 1 1 Inactive-Passive

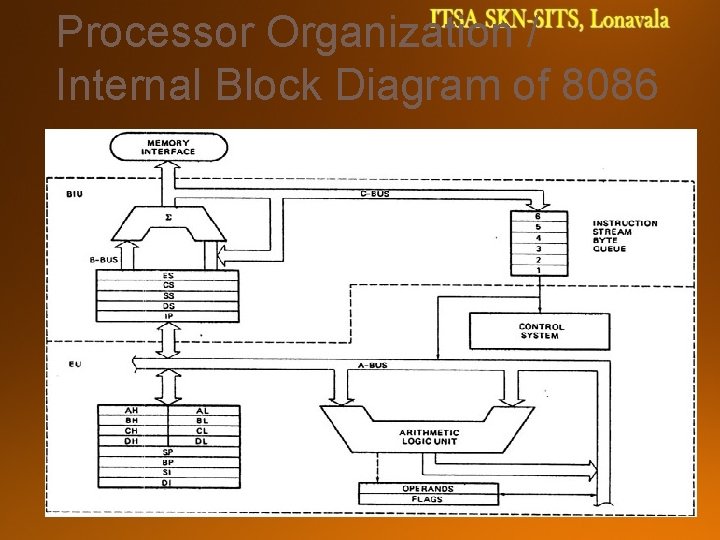

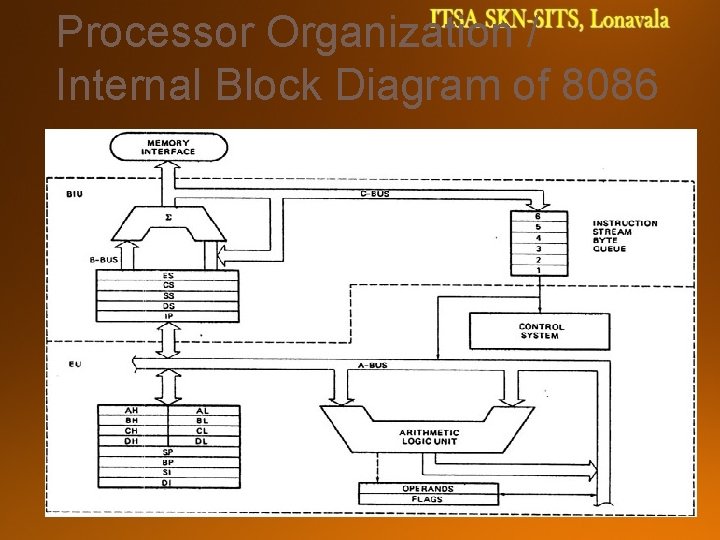

Processor Organization / Internal Block Diagram of 8086

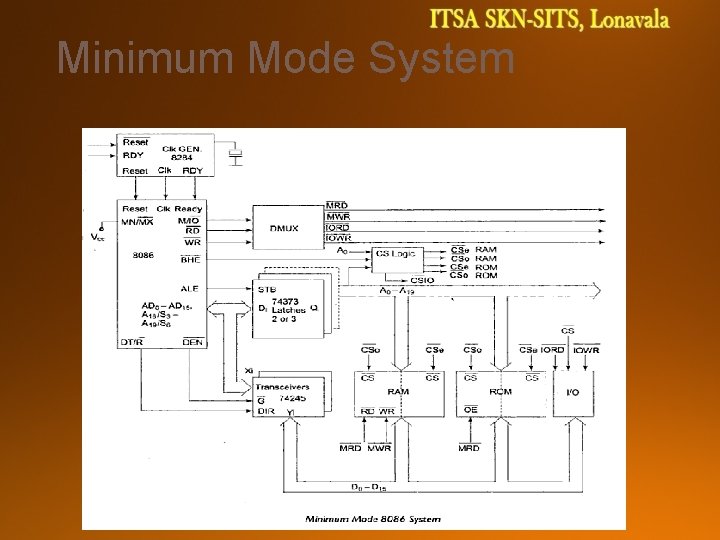

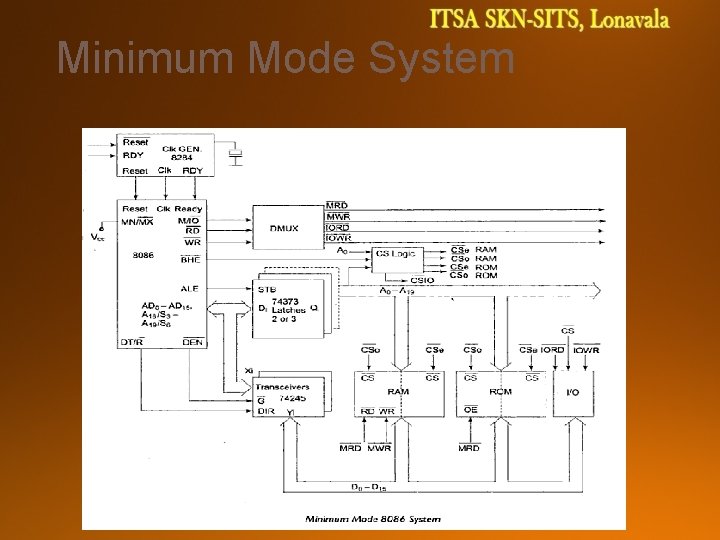

Minimum Mode System

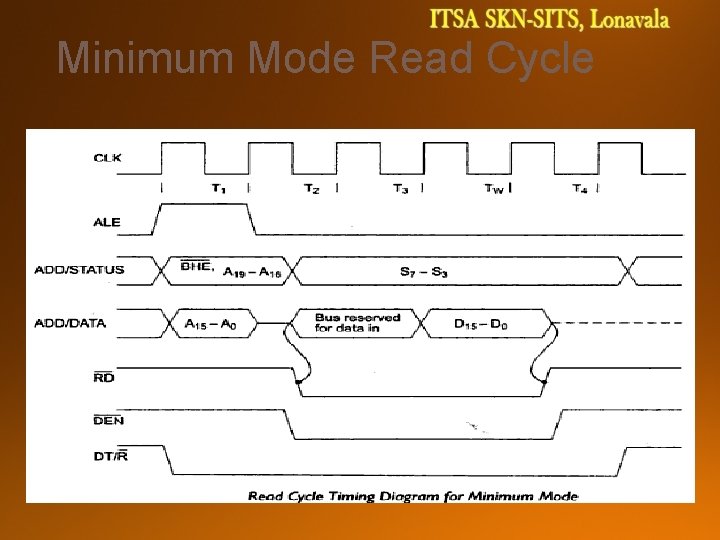

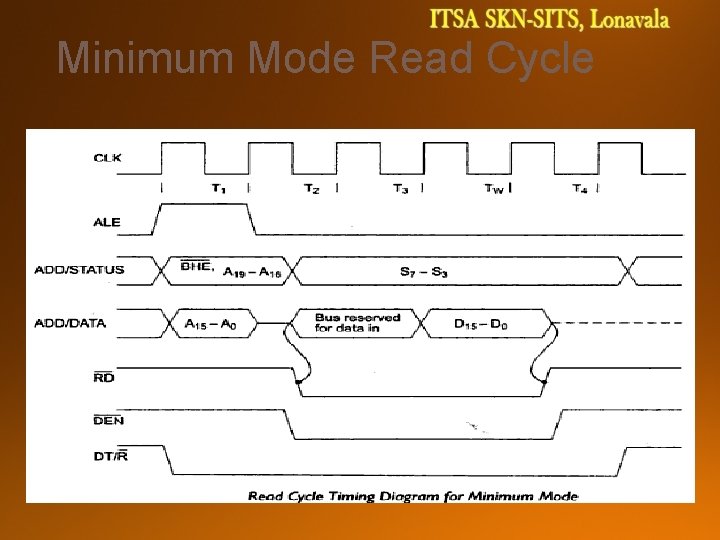

Minimum Mode Read Cycle

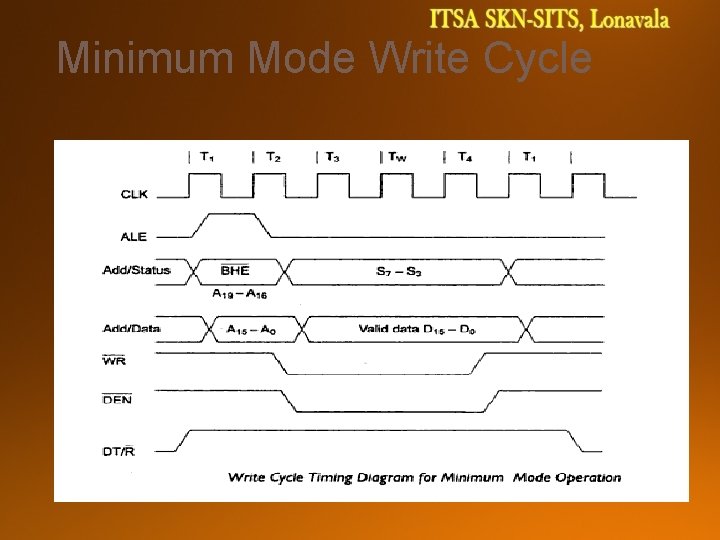

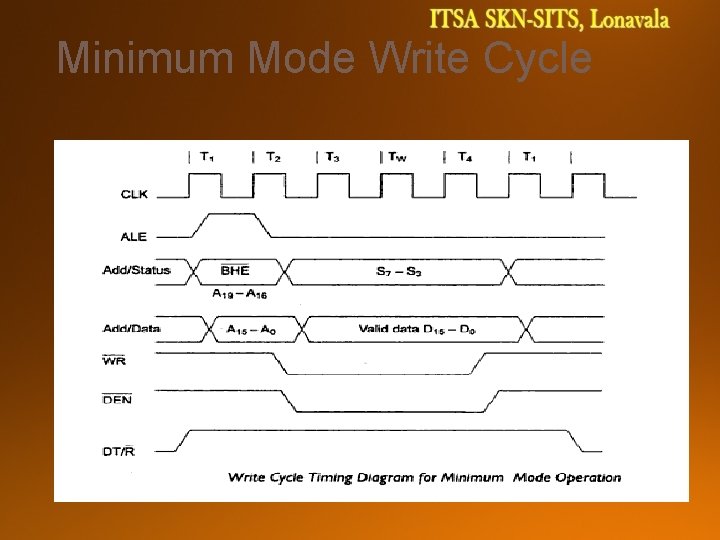

Minimum Mode Write Cycle

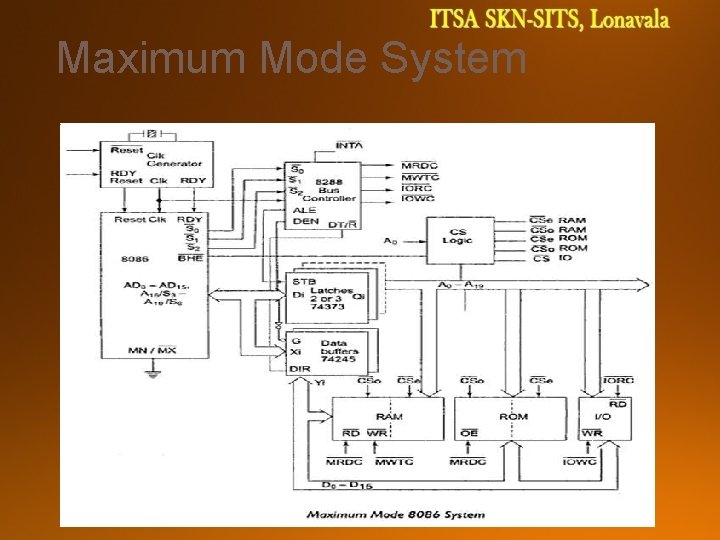

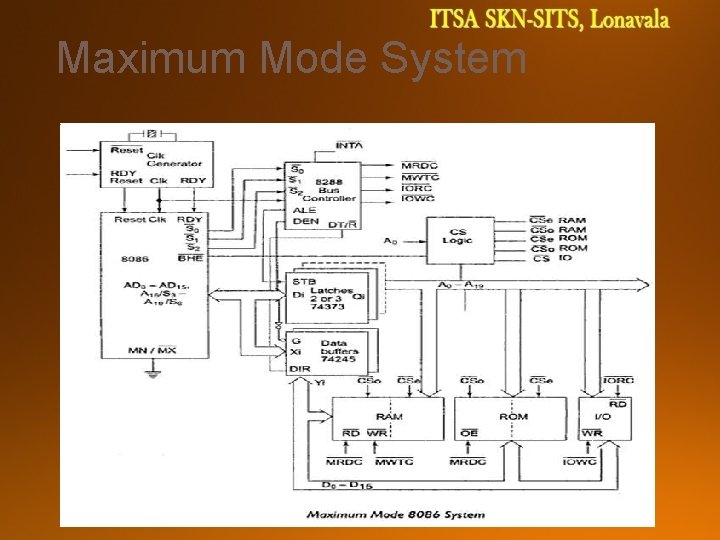

Maximum Mode System

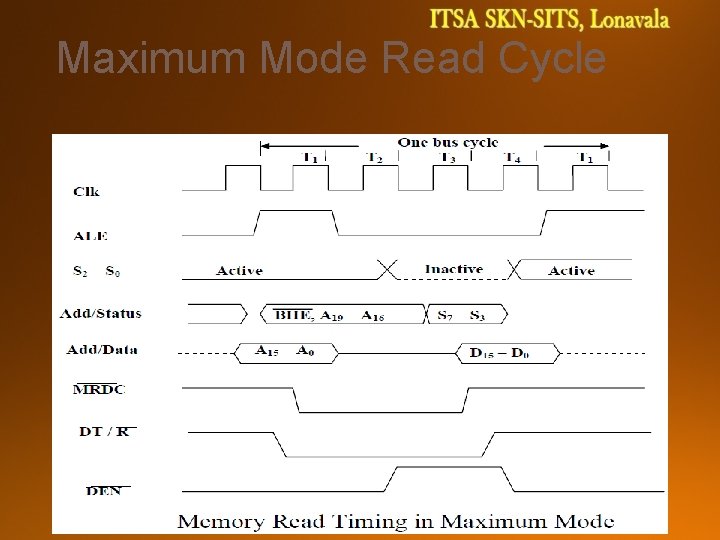

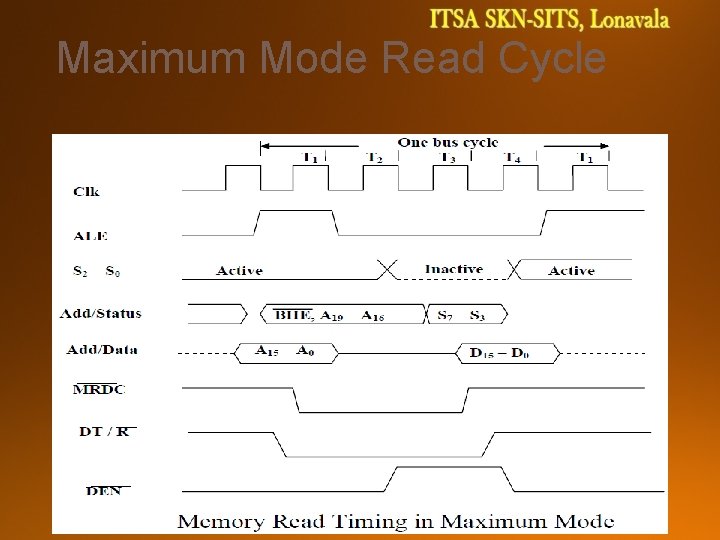

Maximum Mode Read Cycle

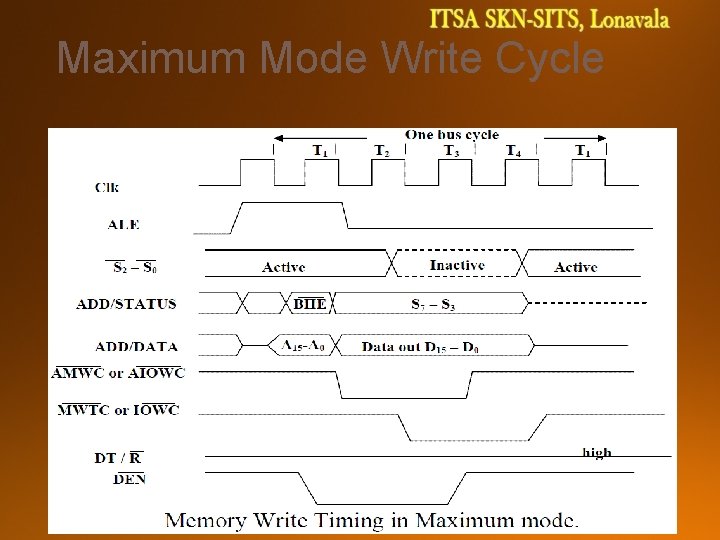

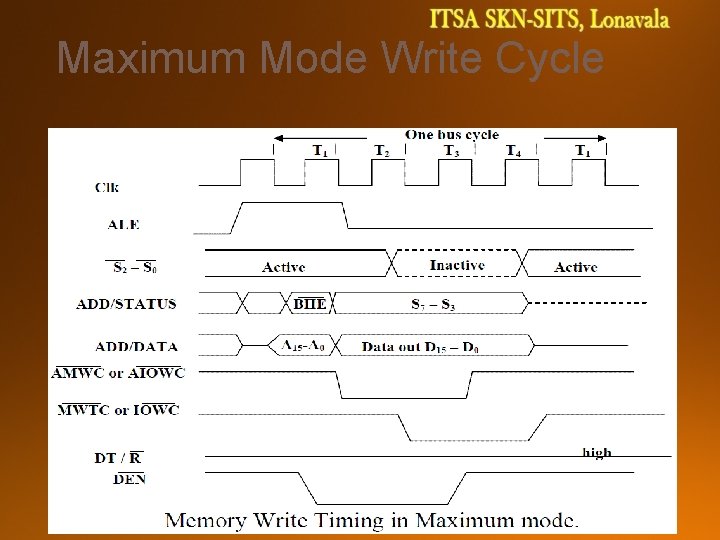

Maximum Mode Write Cycle

Probable Questions Explain different addressing modes. Explain instruction cycle state diagram. Explain different types of instructions. Explain the different ways of instruction classification with its types. Explain the instruction set design criteria's with example. Explain different types of operand operations.

Probable Questions Explain the instruction cycle with block diagram of different cycles. Write short note on, Fetch Cycle, Indirect Cycle, Interrupt Cycle. Explain the processor model/block diagram of 8086. Explain the minimum mode system with read and write cycle. Explain the maximum mode system with read and write cycle