UNIT 2 Basic Language Constructs of VHDL Advanced

UNIT – 2 Basic Language Constructs of VHDL Advanced Digital System Design

Contents üSkeleton/syntax of VHDL program, üElements and program format, üObjects, Data type and operators, üConcurrent Signal Assignment, üCombinational versus sequential circuits, üSignal assignment statements, üconditional signal assignment, üSelected signal assignment, üConditional versus selected signal assignment statements

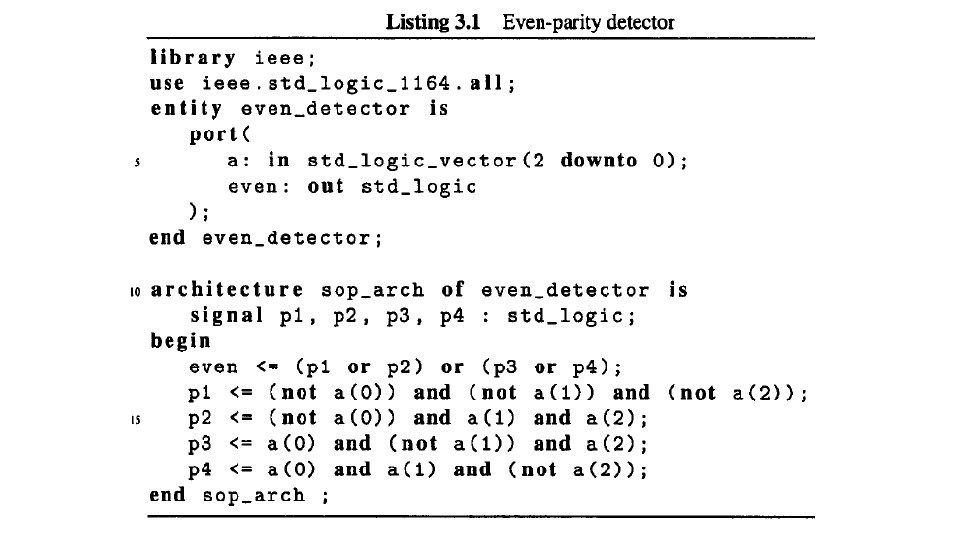

Skeleton / Syntax of VHDL program q. A VHDL program is composed of a collection of Design Units q. A synthesizable VHDL program needs at least two design units: q. An Entity declaration q. An Architecture body q. Skeleton of typical VHDL program can be best explained by an example – even_detector as discussed earlier

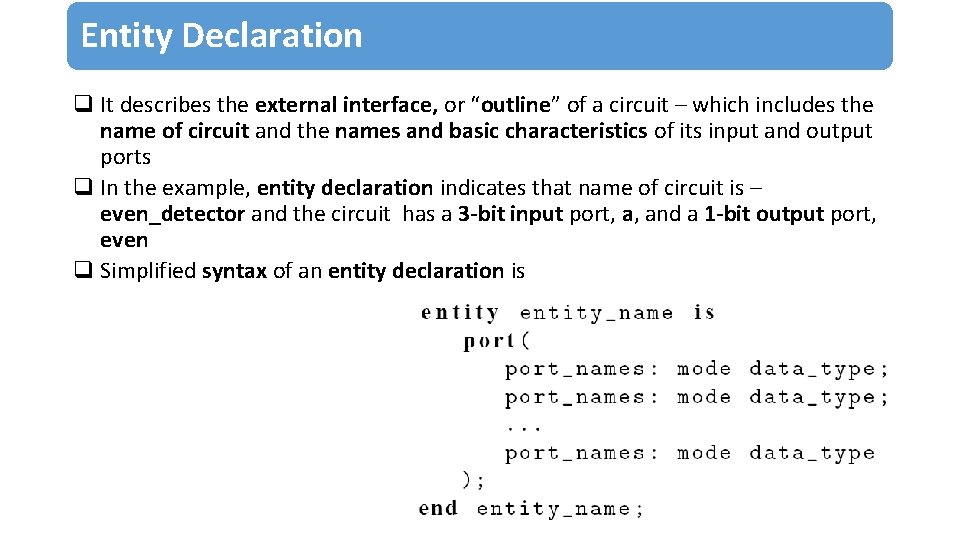

Entity Declaration q It describes the external interface, or “outline” of a circuit – which includes the name of circuit and the names and basic characteristics of its input and output ports q In the example, entity declaration indicates that name of circuit is – even_detector and the circuit has a 3 -bit input port, a, and a 1 -bit output port, even q Simplified syntax of an entity declaration is

Entity Declaration q. Port declaration contains following terms: q. Port_names, q. Mode q. Data_type q Mode term indicates direction of signal, which can be in, out or inout q The in and out keywords indicate that signal flows “into” and “out of” the circuit respectively q The inout keyword indicates that signal flows in both directions and that corresponding port is bidirectional q Mode term can also be buffer q Port declaration above has 2 parts: q a port – input signal having data type std_logic_vector(2 downto 0) which represents a 3 -bit bus q even port – output port having data type std_logic q Note that any port with out mode cannot be used as an input signal

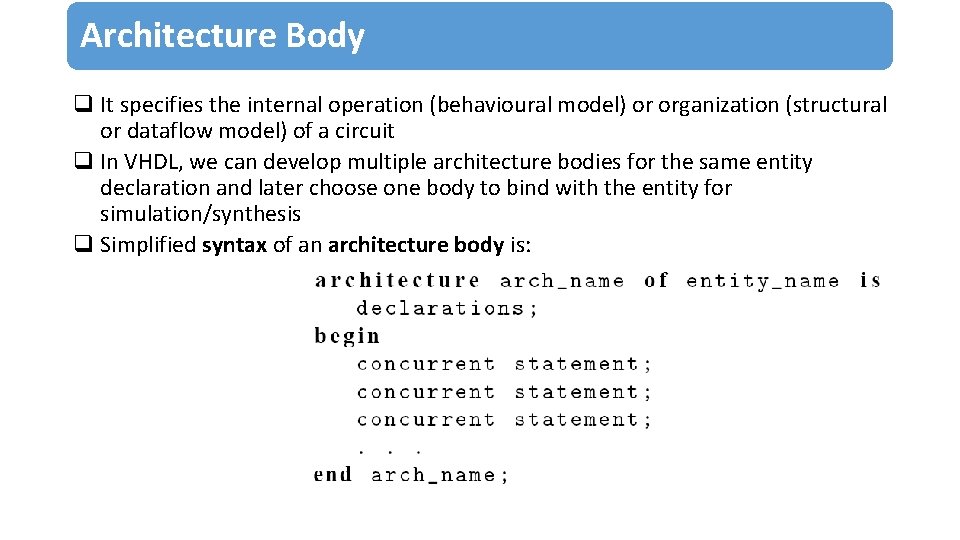

Architecture Body q It specifies the internal operation (behavioural model) or organization (structural or dataflow model) of a circuit q In VHDL, we can develop multiple architecture bodies for the same entity declaration and later choose one body to bind with the entity for simulation/synthesis q Simplified syntax of an architecture body is:

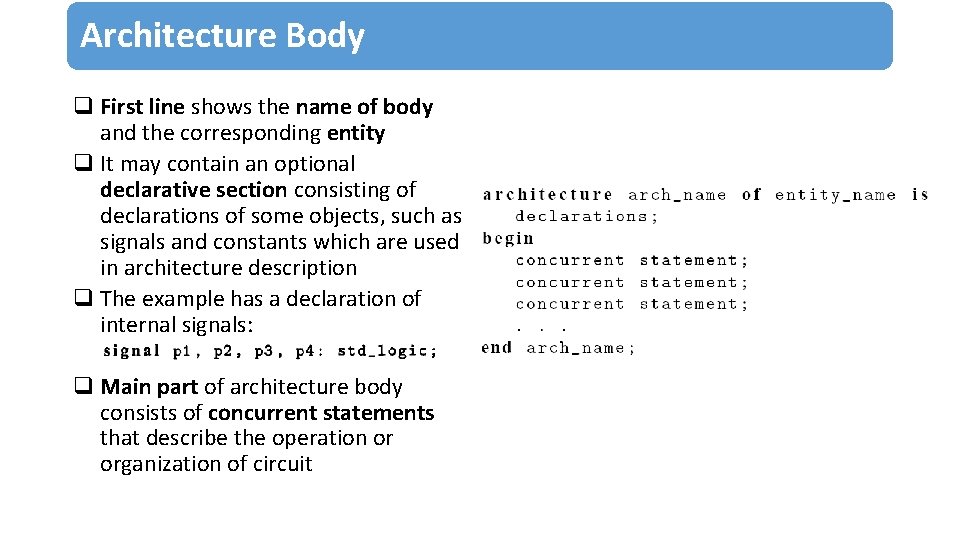

Architecture Body q First line shows the name of body and the corresponding entity q It may contain an optional declarative section consisting of declarations of some objects, such as signals and constants which are used in architecture description q The example has a declaration of internal signals: q Main part of architecture body consists of concurrent statements that describe the operation or organization of circuit

Design Units q Design units are fundamental building blocks in VHDL program q When a program is processed, it is broken into individual design units and each unit is analysed and stored independently. q The 5 kinds of design units are: q Entity Declaration q Architecture Body q Package Declaration q Package Body q Configuration q Entity declaration and Architecture body have been discussed earlier

Design Units – Package Declaration q. Package of VHDL normally contains a collection of commonly used items such as – q Data types q Subprograms q Components q. These items are needed by many VHDL programs q. As the name suggests, a package declaration consists of declaration of these items q. A package body normally contains the implementation and code of the subprograms

Design Units – Configuration q. In VHDL, many architecture bodies can be associated with an entity declaration q. A Configuration specifies which architecture body is to be bound with the entity declaration

Library q. A VHDL Library is a place to store the design units q. It is mapped into a directory (folder) in the computer’s hard disk q. The software defines the mapping between VHDL library name and the physical directory q. By VHDL default, the design units are stored in a library named ‘work’. q. To facilitate the synthesis, IEEE has developed several VHDL packages, including the std_logic_1164 package q. To use a predefined package, we must include the library and use statements before the entity declaration

Library q. The first 2 lines of the example are for this purpose: library ieee; use ieee. std_logic_1164. all; Ø The first line invokes a library named ieee, and Ø The second line makes the std_logic_1164 package visible to the subsequent design unit. Ø We must invoke this library because we want to use some predefined data types, std_logic and std_logic_vector, of the std_logic_1164 package

Lexical Elements and Program Format q. Lexical Elements - Basic syntactical units in a VHDL program Ø Comments Ø Identifiers Ø Reserved Words Ø Numbers Ø Characters Ø Strings

Lexical Elements and Program Format q. Comments q Starts with 2 dashes, --, followed by the text. q Anything after the -- symbol in the same line will be ignored q Comment is for documentation purposes only and has no effect on code q E. g. – we have added comments to the previous VHDL code:

Lexical Elements and Program Format q. Identifiers – name of an object in VHDL q. Basic rules to form an identifier are: Ø It can contain only alphabetic letters, decimal digits and underscores Ø First character must be a letter (e. g. a, b, c, A, B, C) Ø Last character cannot be an underscore (__) Ø Two successive underscores (_ _) are not allowed q. Following identifiers are valid: A 10, next_state, Next. State, mem_addr_enable q Following identifiers violate the rules and will cause syntax error sig#3, _ X 1 0 , ‘ 7 segment, X 10_, hi_ _there

Lexical Elements and Program Format q. Identifiers As VHDL is not case-sensitive, following identifiers are same: nextstate , Next. State , NEXTSTATE, n. EXTs. TATE q It is a good practice to be consistent with the case q It is also a good practice to use descriptive identifier for better readability

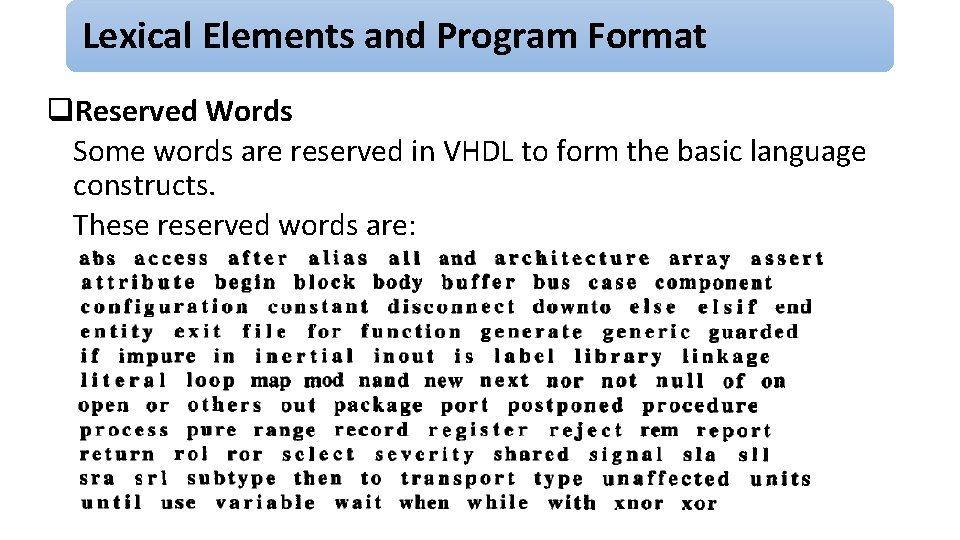

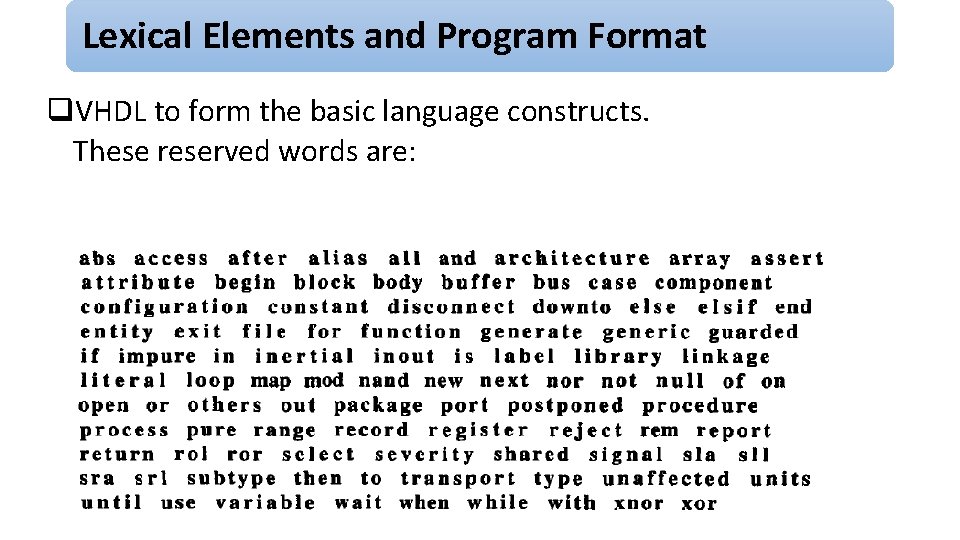

Lexical Elements and Program Format q. Reserved Words Some words are reserved in VHDL to form the basic language constructs. These reserved words are:

Lexical Elements and Program Format q. VHDL to form the basic language constructs. These reserved words are:

- Slides: 19