UNIDAD 2 DISEO LGICO DE PROCESADORES UNIDAD ARITMTICOLGICA

- Slides: 31

UNIDAD 2. DISEÑO LÓGICO DE PROCESADORES: UNIDAD ARITMÉTICO-LÓGICA Ing. Elizabeth Guerrero V.

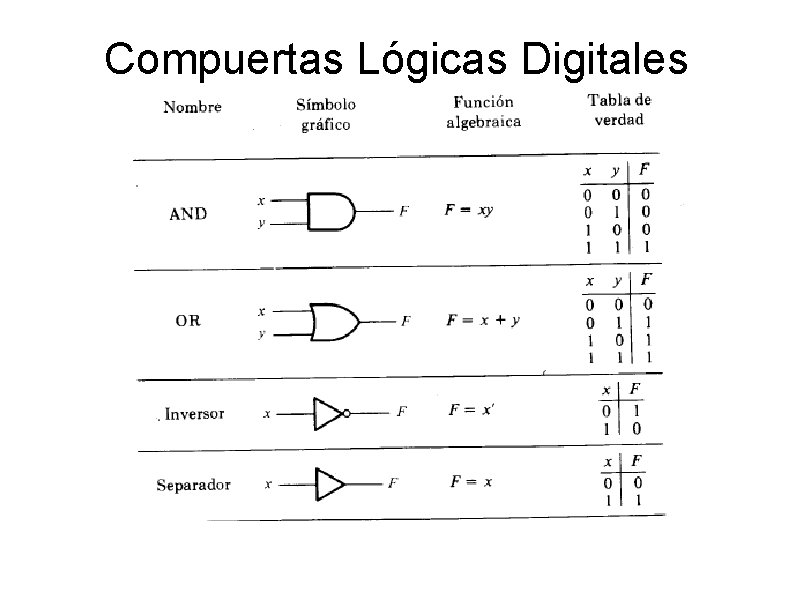

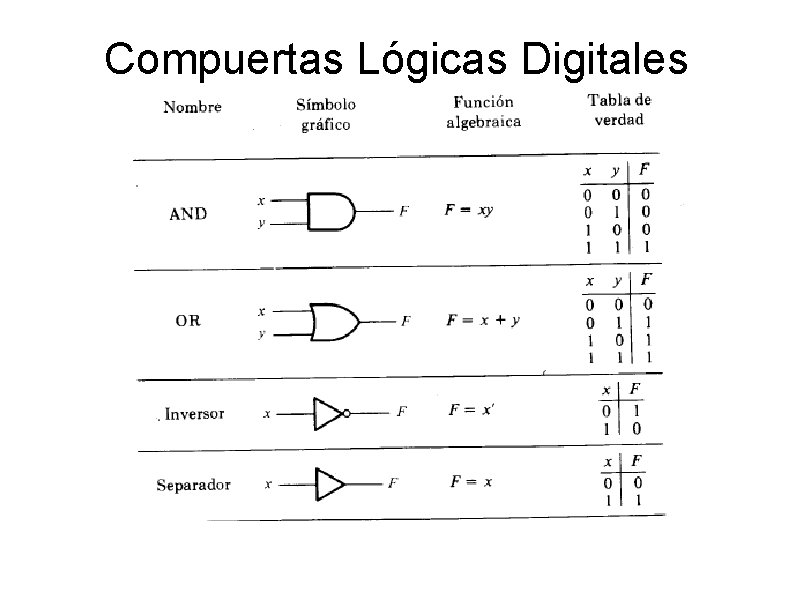

Compuertas Lógicas Digitales

Compuertas lógicas digitales

Ejecución de funciones con compuertas

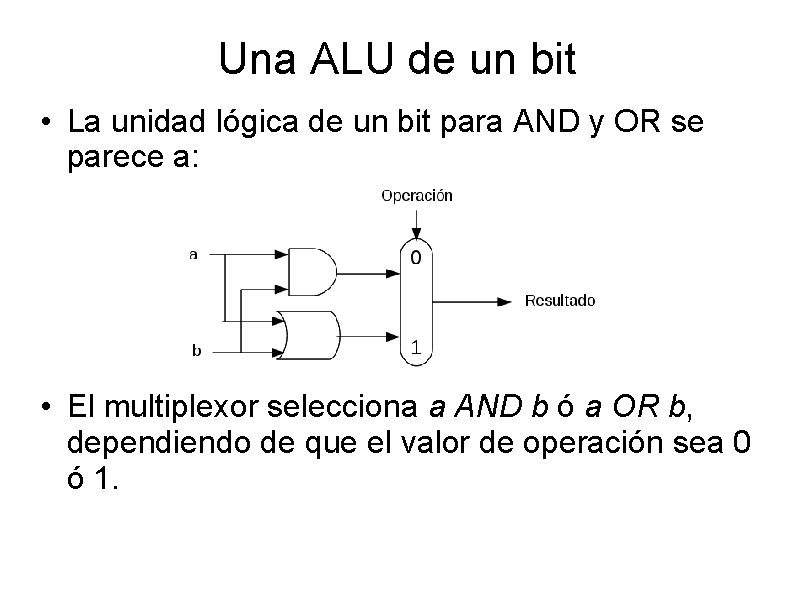

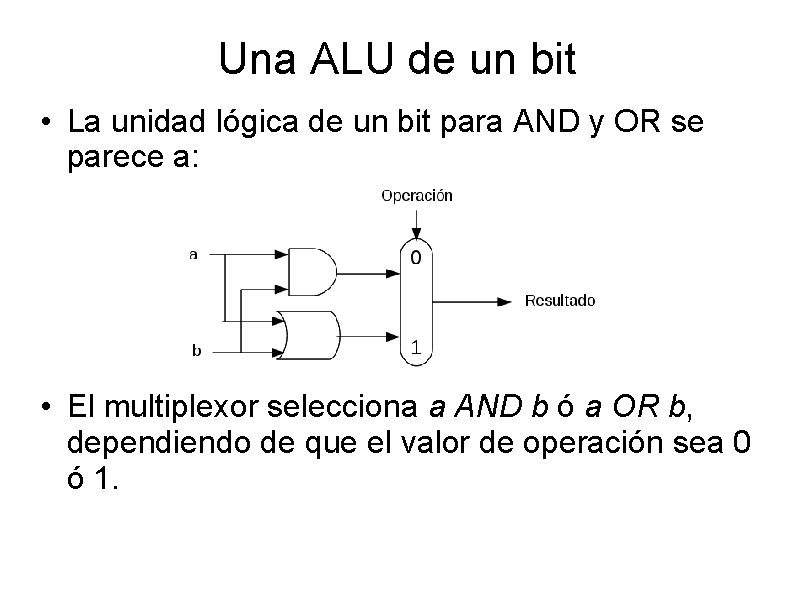

Una ALU de un bit • La unidad lógica de un bit para AND y OR se parece a: • El multiplexor selecciona a AND b ó a OR b, dependiendo de que el valor de operación sea 0 ó 1.

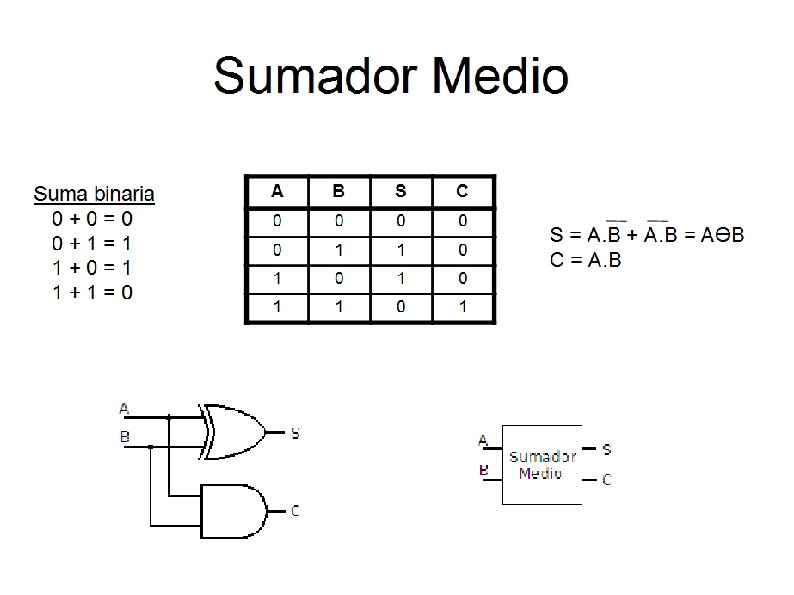

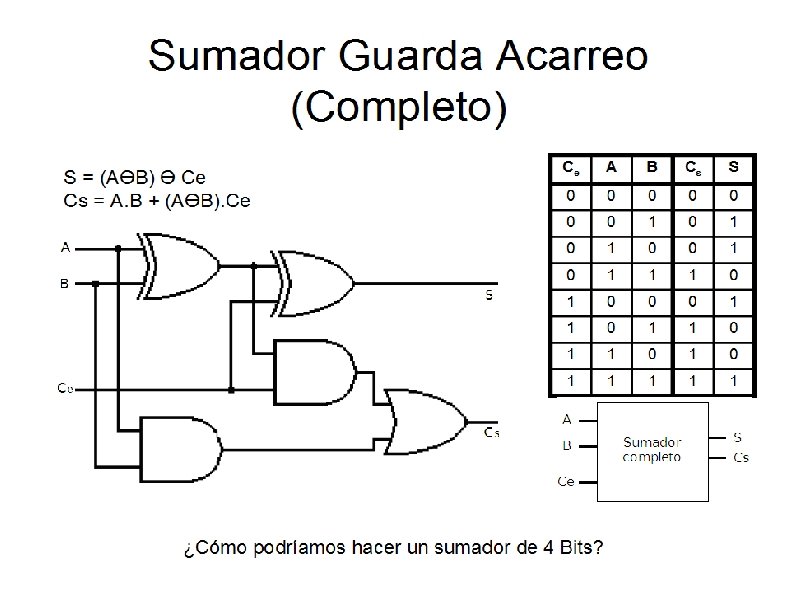

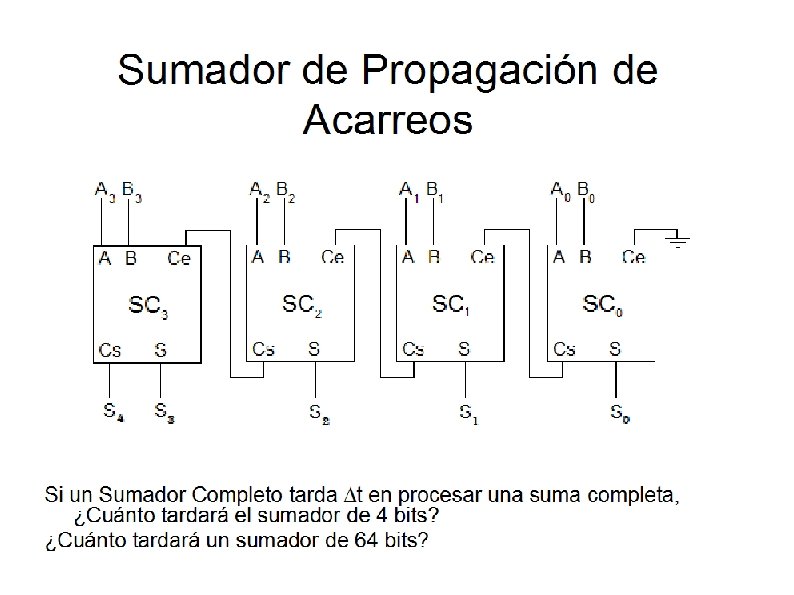

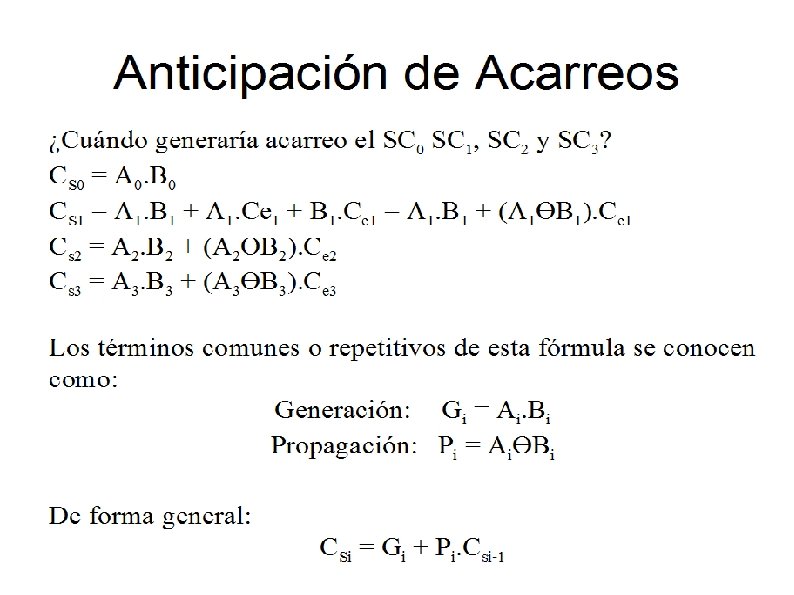

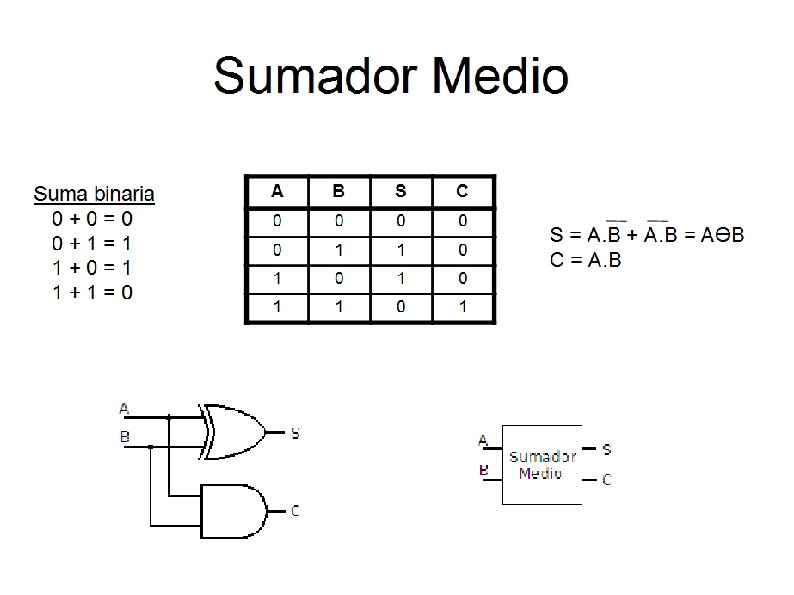

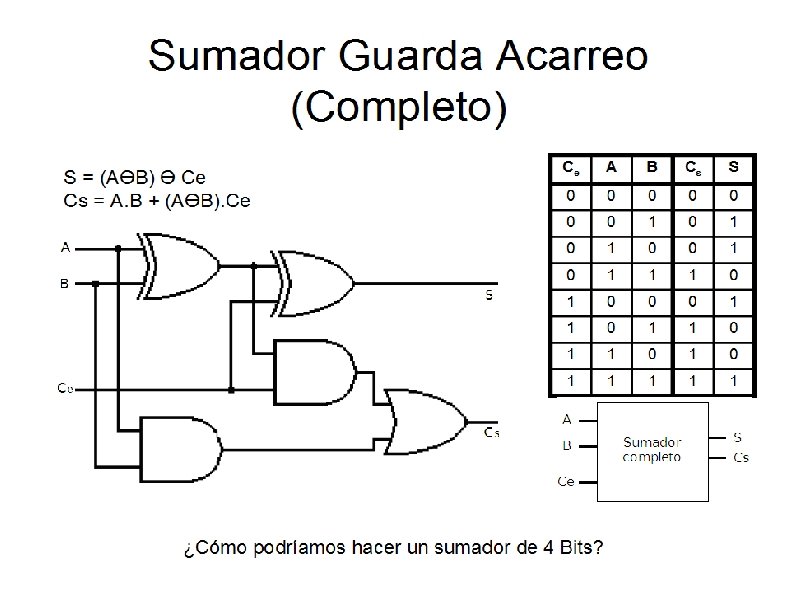

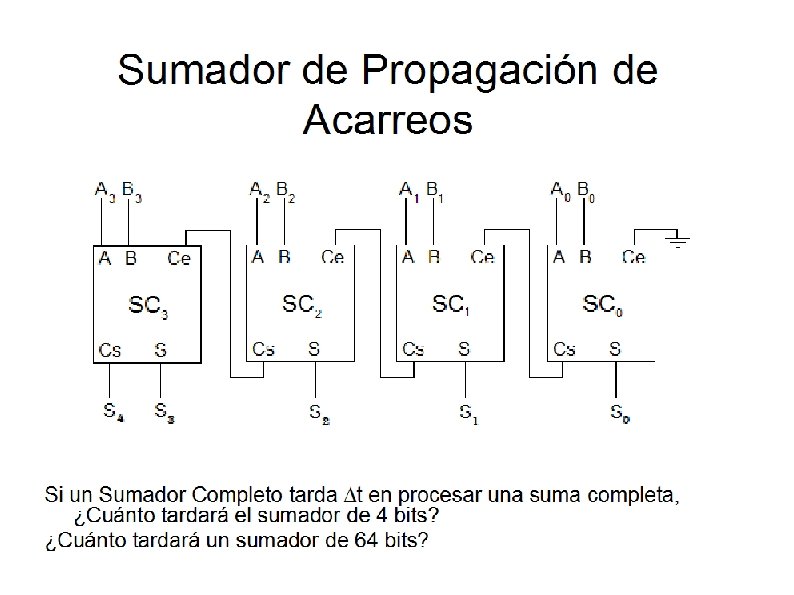

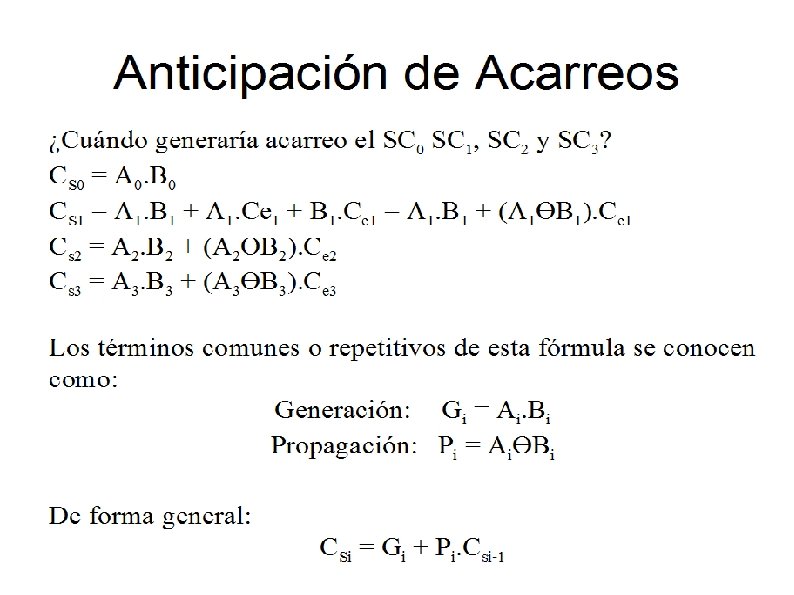

Sumador • Debe tener dos entradas para los operandos y una salida de un solo bit para la suma. • Debe haber una segunda salida para el arrastre, denominada Carry. Out. • Debe haber una tercera entrada denominada Carry. In.

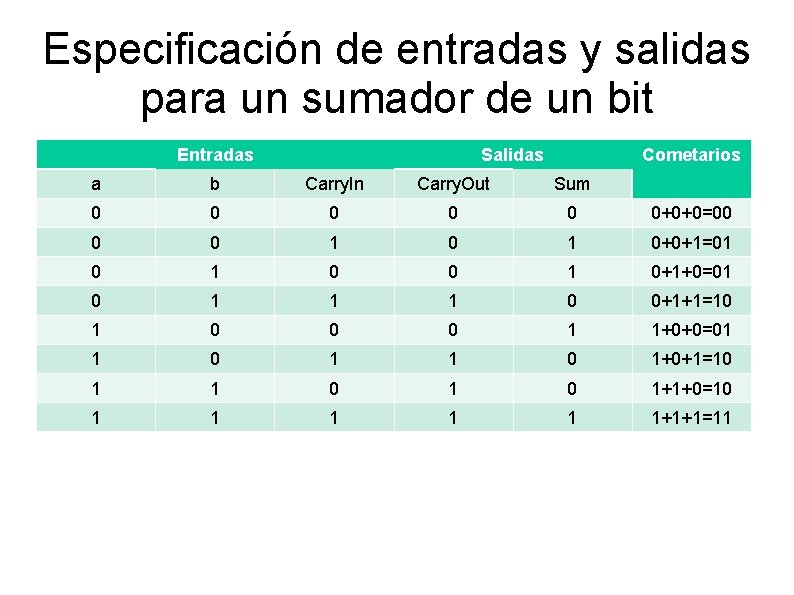

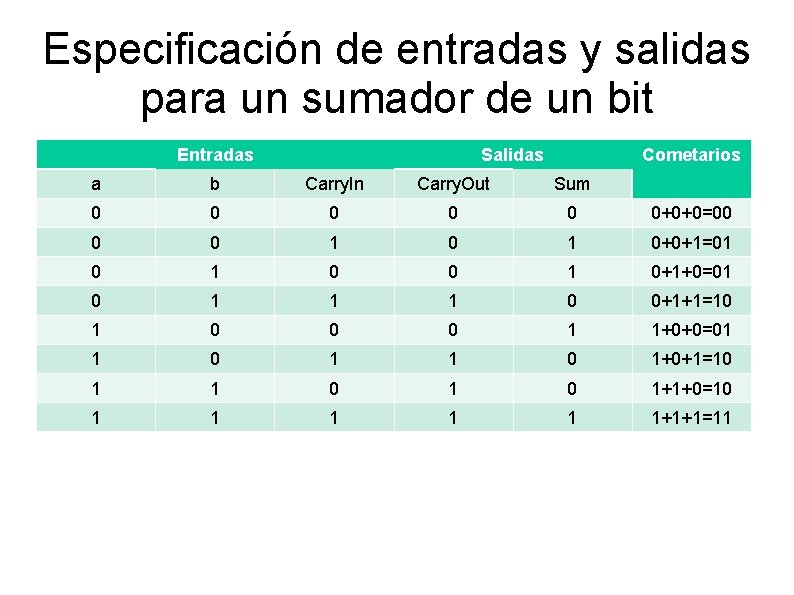

Especificación de entradas y salidas para un sumador de un bit Entradas Salidas Cometarios a b Carry. In Carry. Out Sum 0 0 0+0+0=00 0 0 1 0+0+1=01 0 0 1 0+1+0=01 0 1 1 1 0 0+1+1=10 1 0 0 0 1 1+0+0=01 1 0 1+0+1=10 1 1 0 1+1+0=10 1 1 1+1+1=11

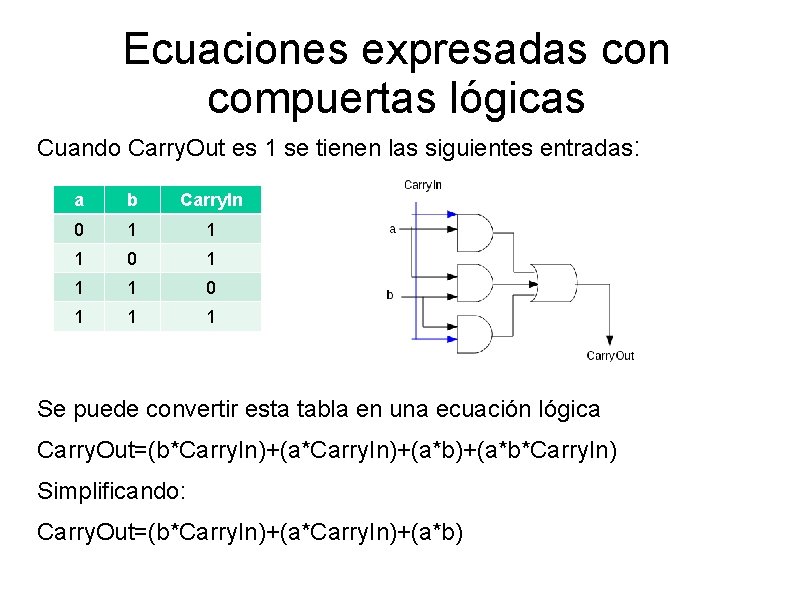

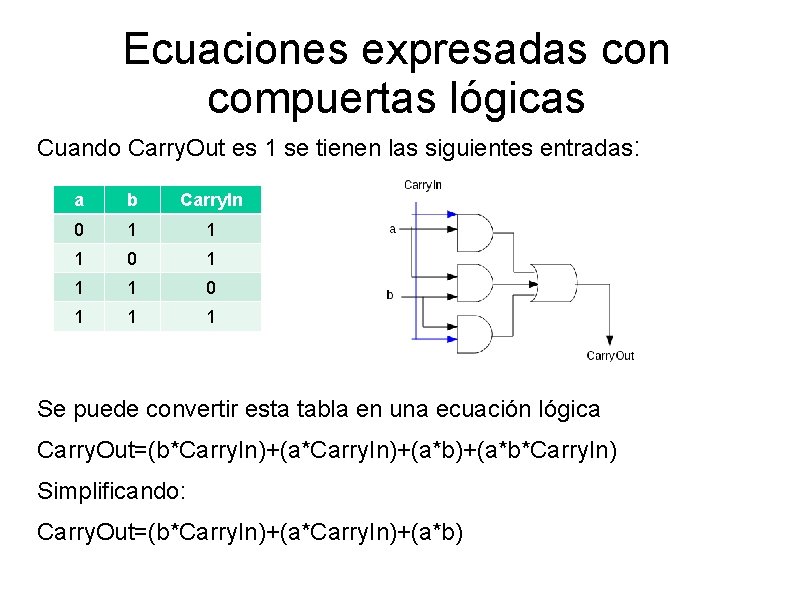

Ecuaciones expresadas con compuertas lógicas Cuando Carry. Out es 1 se tienen las siguientes entradas: a b Carry. In 0 1 1 1 Se puede convertir esta tabla en una ecuación lógica Carry. Out=(b*Carry. In)+(a*b)+(a*b*Carry. In) Simplificando: Carry. Out=(b*Carry. In)+(a*b)

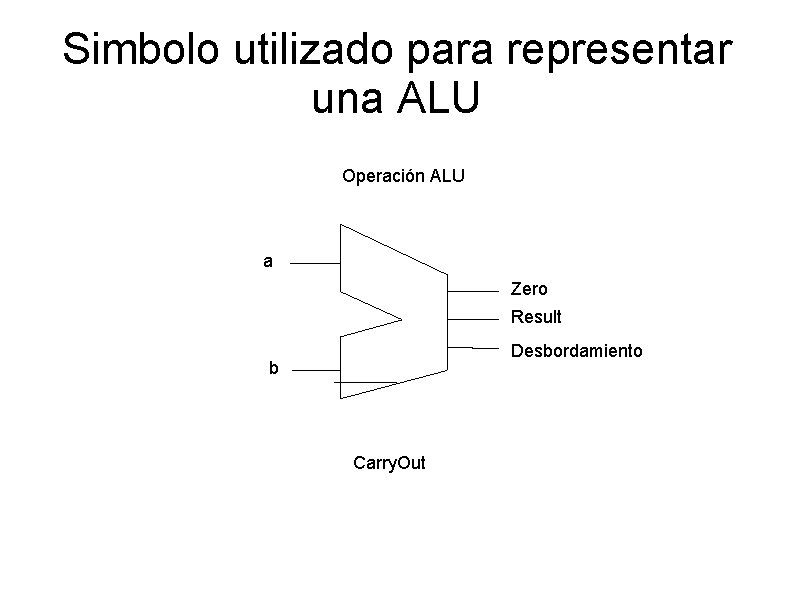

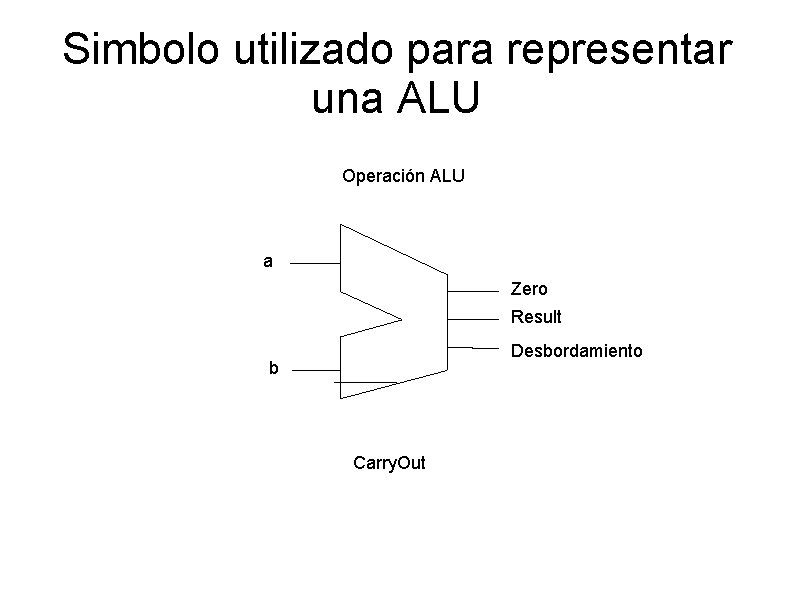

Simbolo utilizado para representar una ALU Operación ALU a Zero Result Desbordamiento b Carry. Out

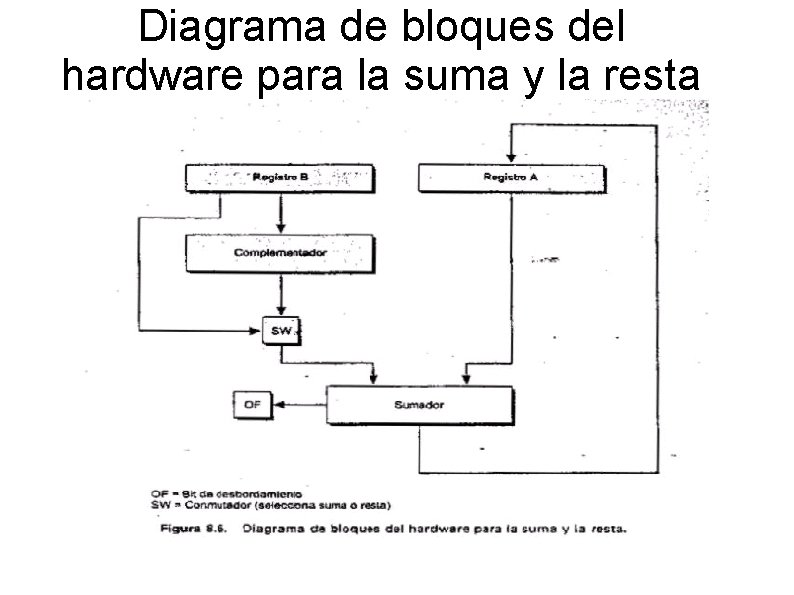

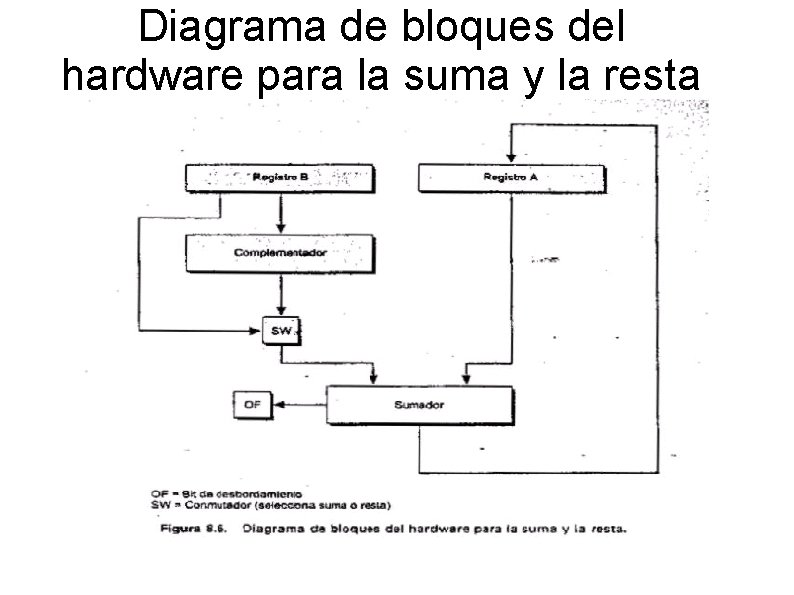

Diagrama de bloques del hardware para la suma y la resta

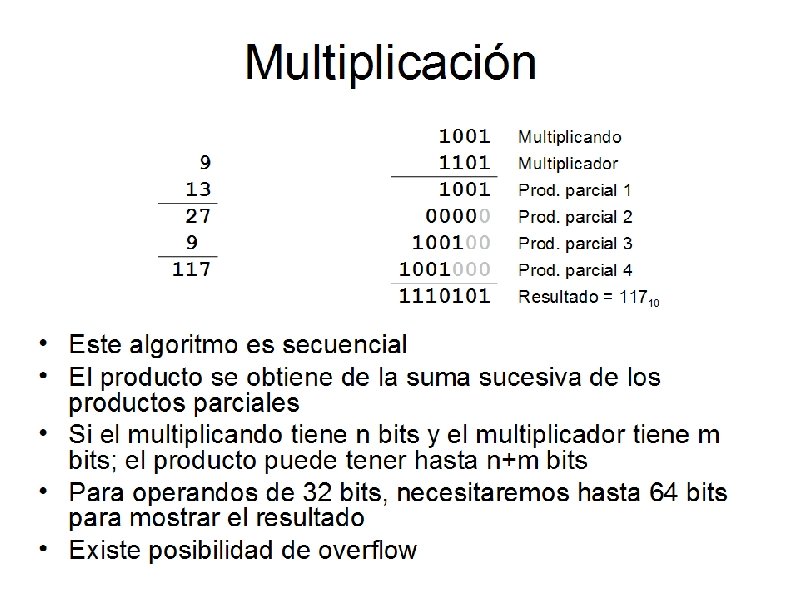

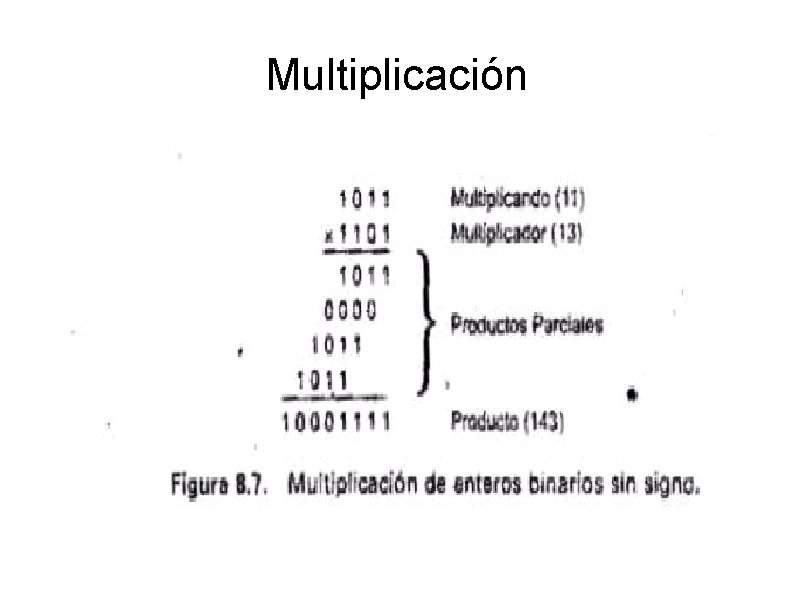

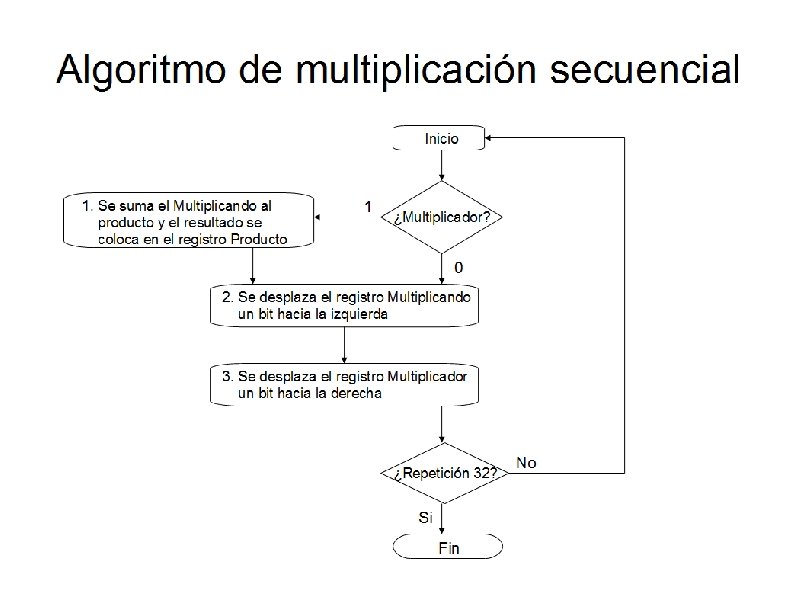

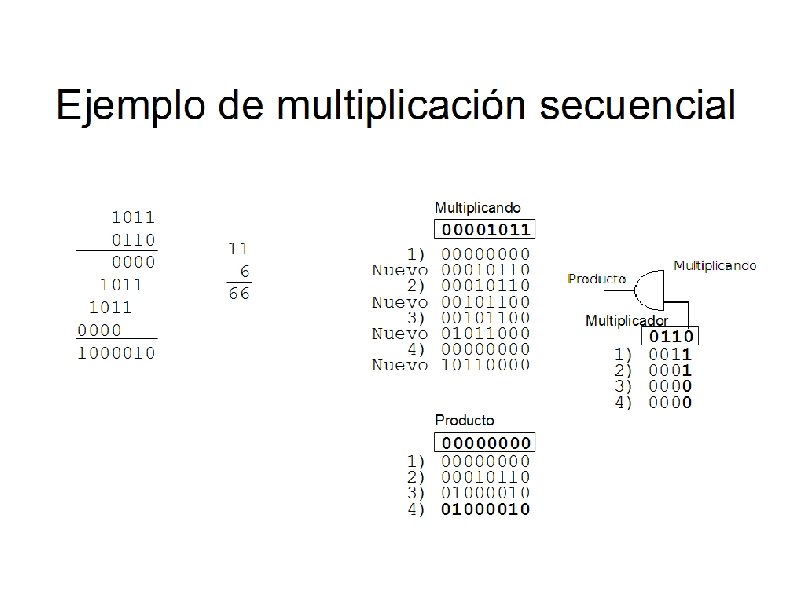

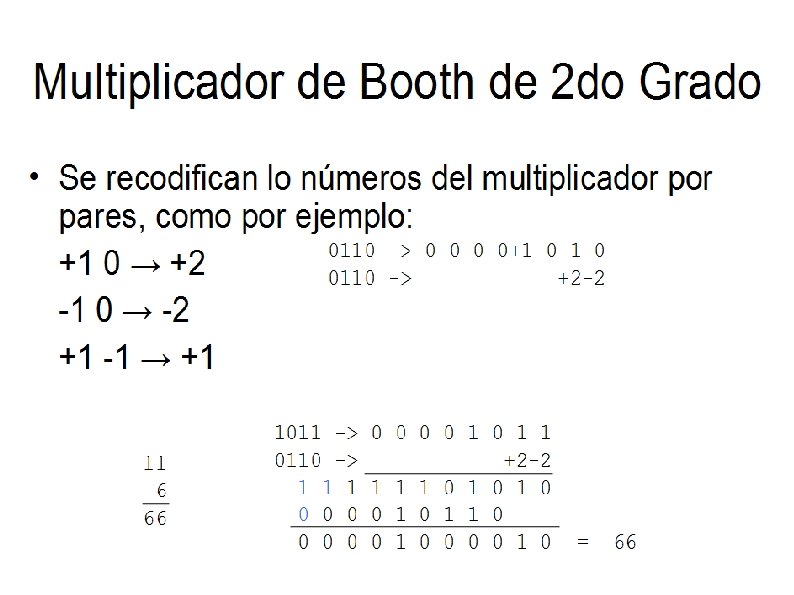

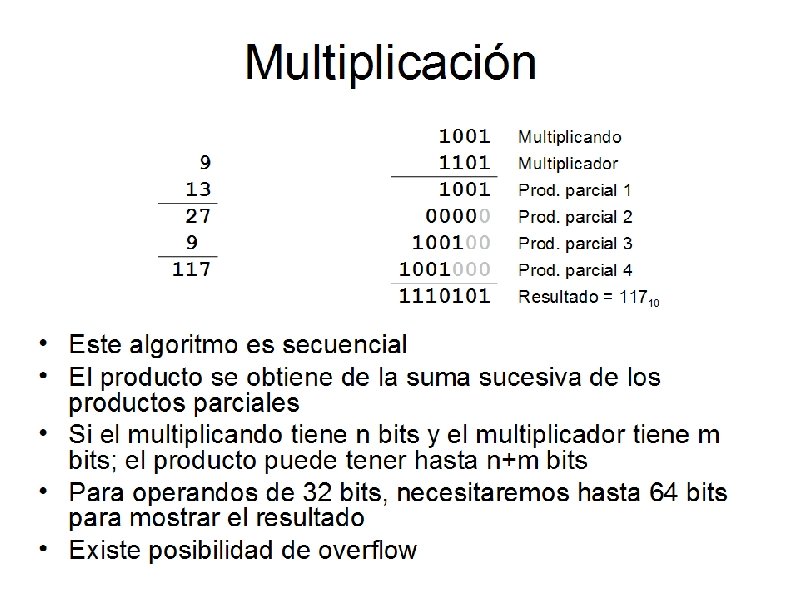

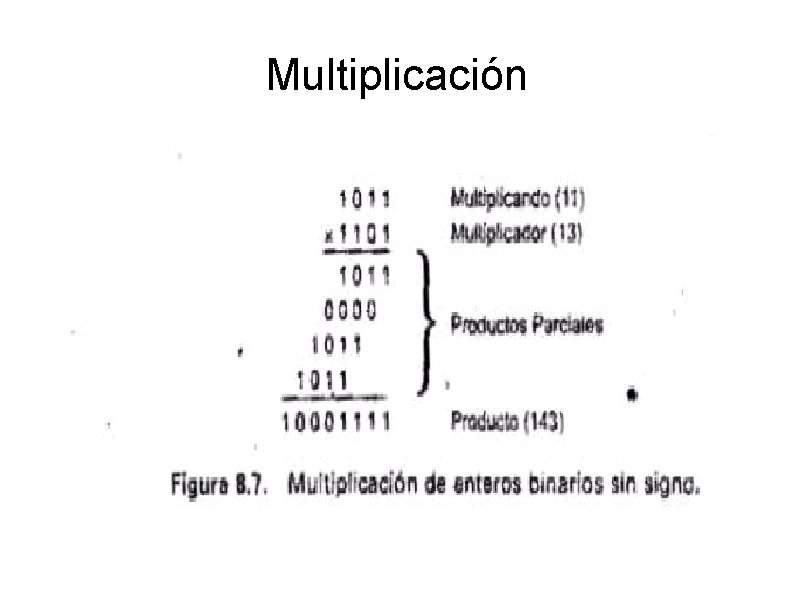

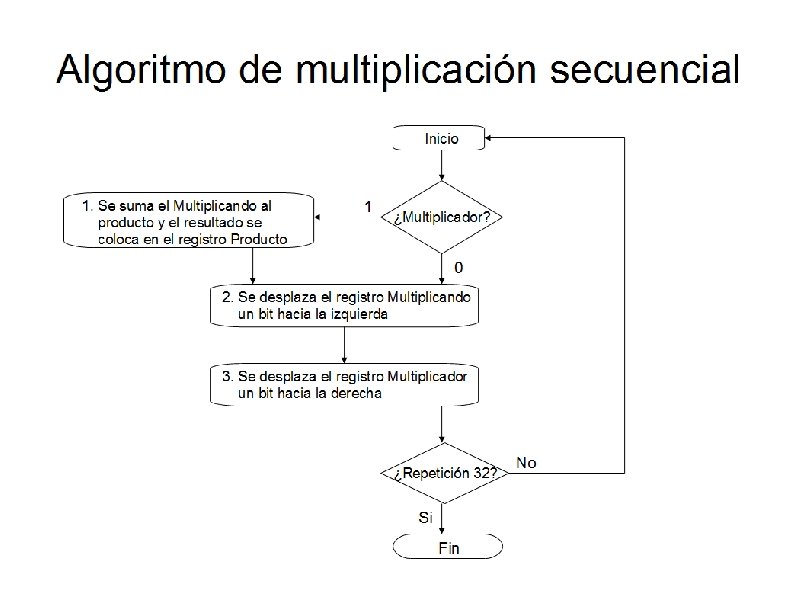

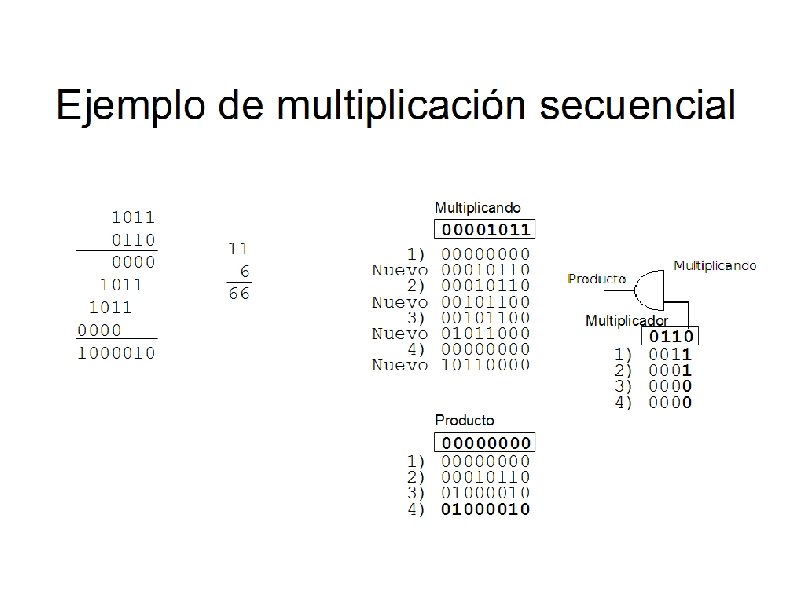

Multiplicación Comparada con la suma y la resta, la multiplicación es una operación compleja, ya se realice en hardware o software. Enteros binarios sin signo: 1. La multiplicación implica la generación de productos parciales, uno para cada digito del multiplicador. Estos productos parciales se suman después para obtener el producto final. 2. Los productos parciales se definen fácilmente. Cuando el bit del multiplicador es 0, el producto parcial es 0. Cuando el multiplicador es 1, el producto parcial es el multiplicando

Multiplicación 3. El producto total se obtiene sumando los productos parciales. Para esta operación cada producto parcial sucesivo se desplaza una posición hacia la izquierda con respecto al producto parcial precedente. 4. El producto de dos enteros binarios sin signo de n bits da como resultado un producto de hasta 2 n bits de longitud.

Multiplicación

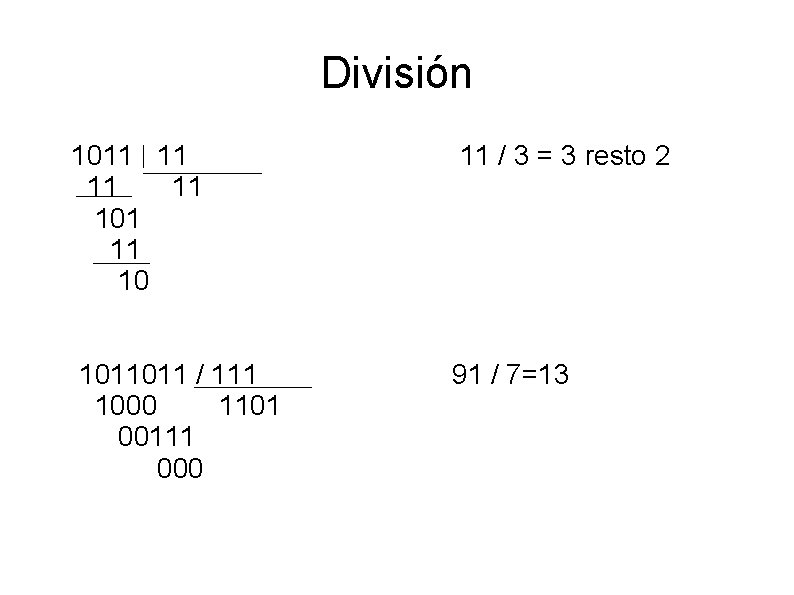

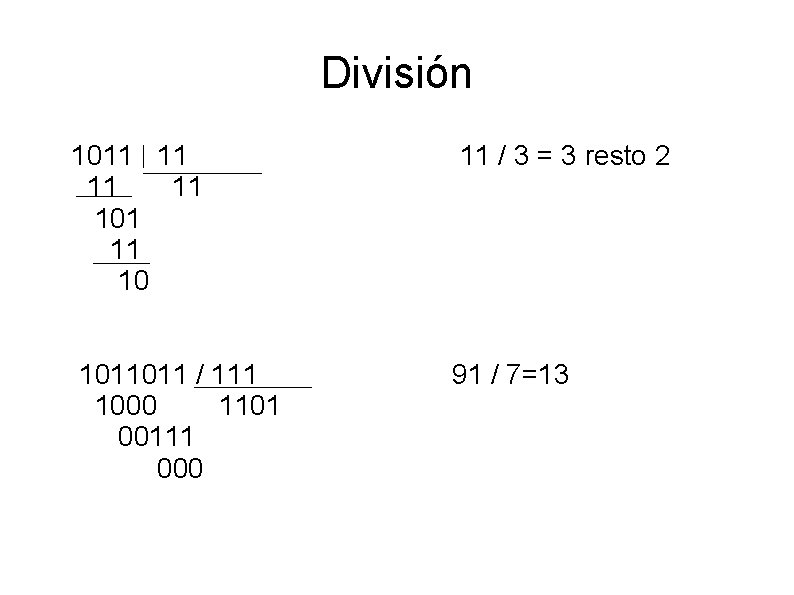

División 1011 11 101 11 10 11 / 3 = 3 resto 2 1011011 / 111 1000 1101 00111 000 91 / 7=13