Understanding and Comparisons of High Speed ADC and

- Slides: 17

Understanding and Comparisons of High Speed ADC and DAC Architectures TIPL 4706 Presented by Richard Prentice Prepared by Richard Prentice 1

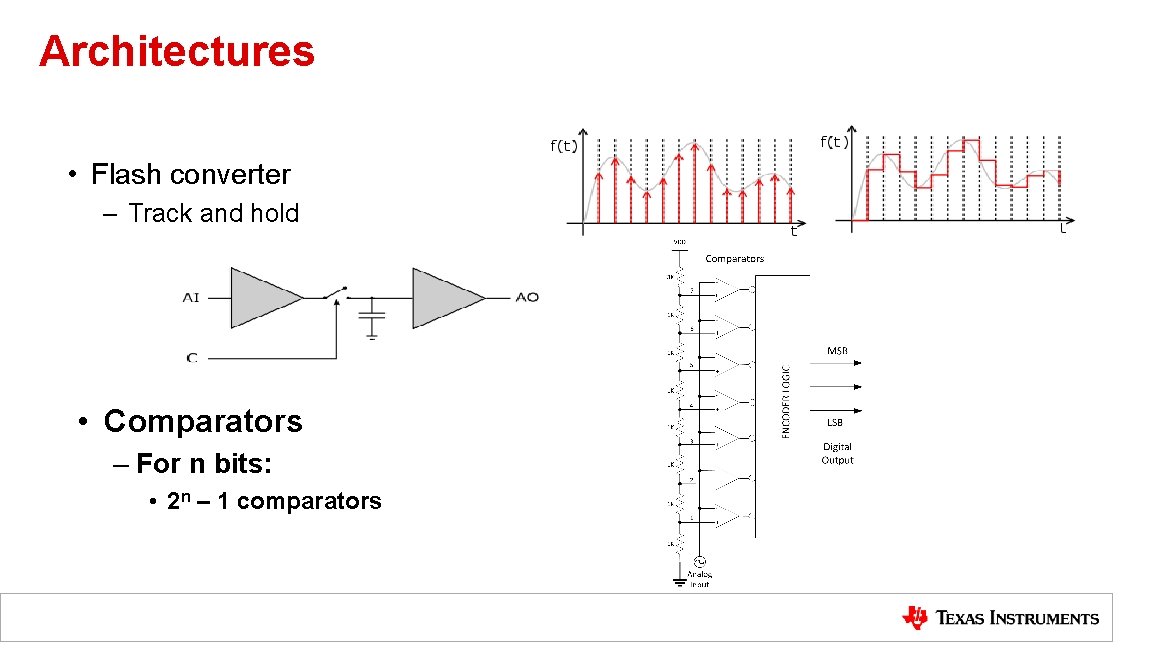

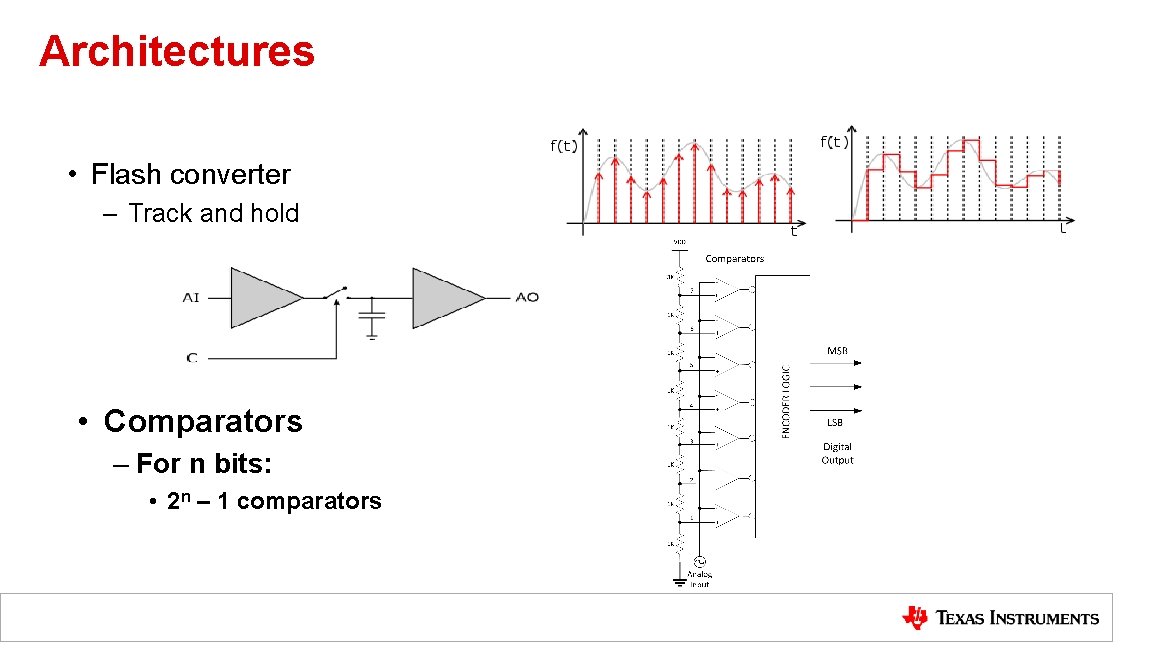

Architectures • Flash converter – Track and hold • Comparators – For n bits: • 2 n – 1 comparators

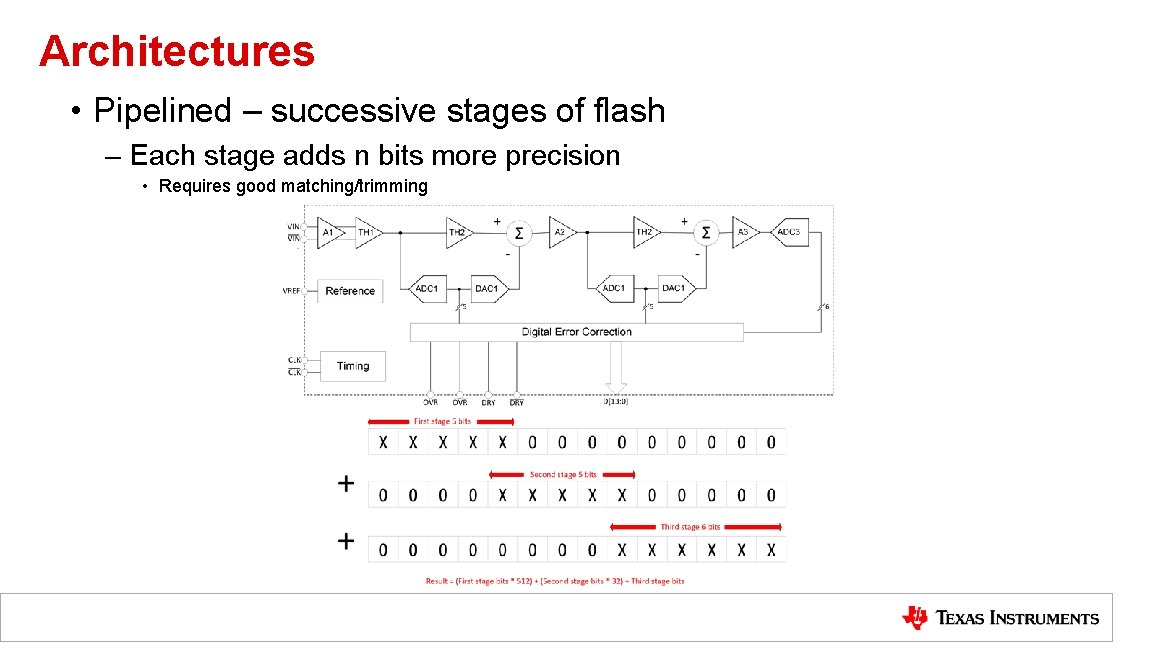

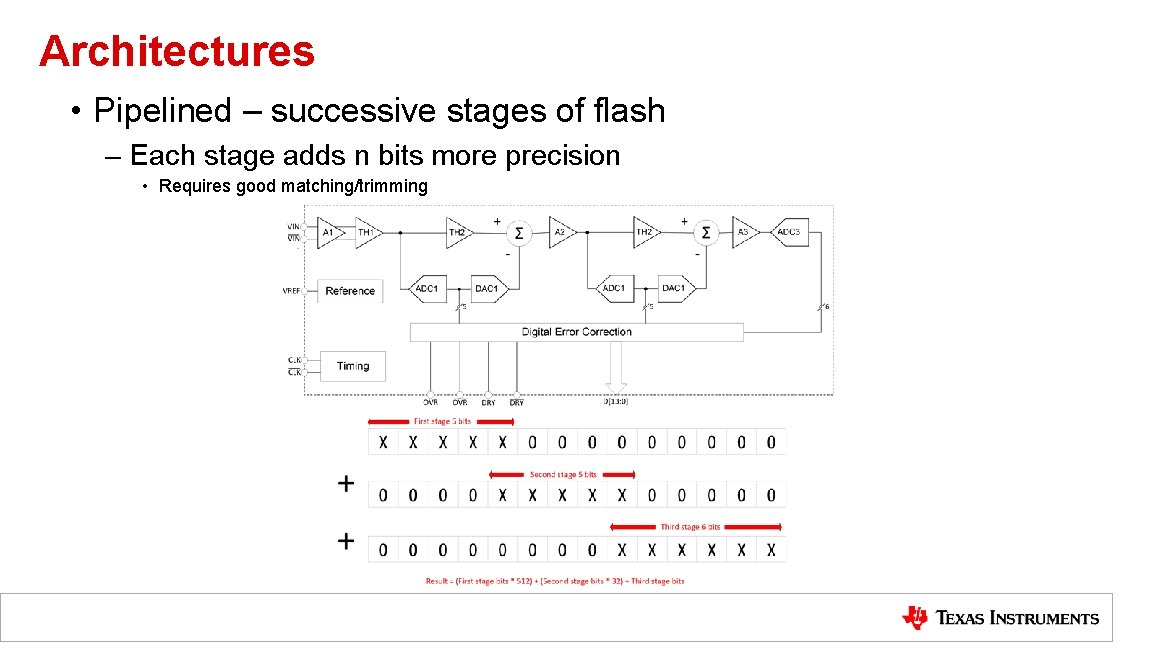

Architectures • Pipelined – successive stages of flash – Each stage adds n bits more precision • Requires good matching/trimming

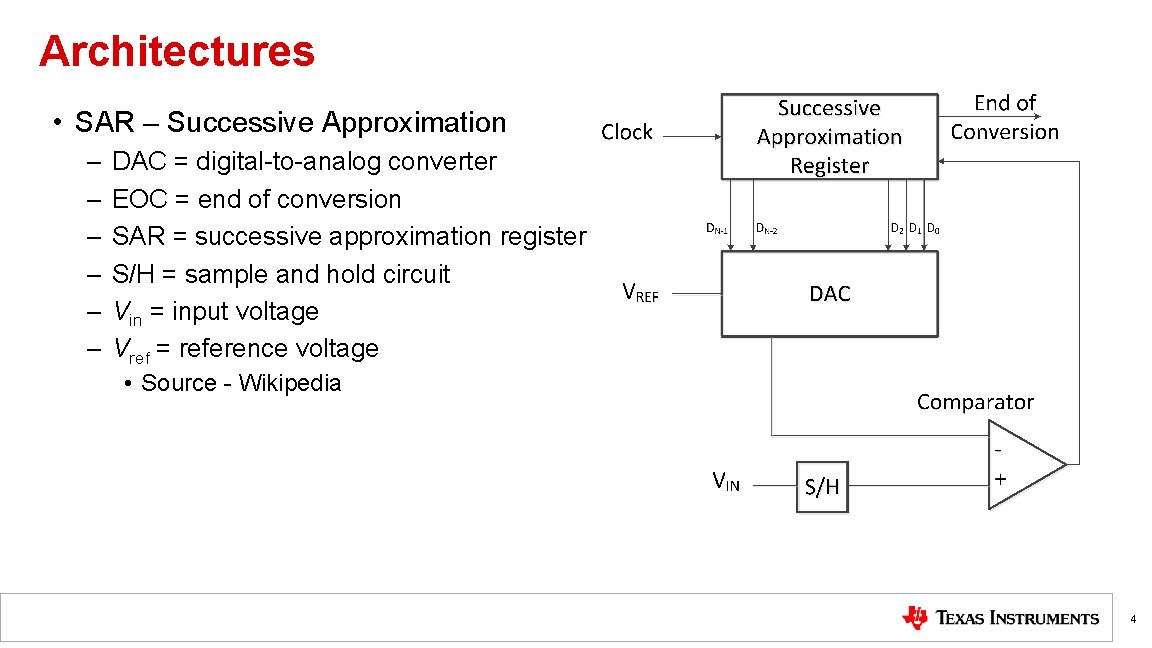

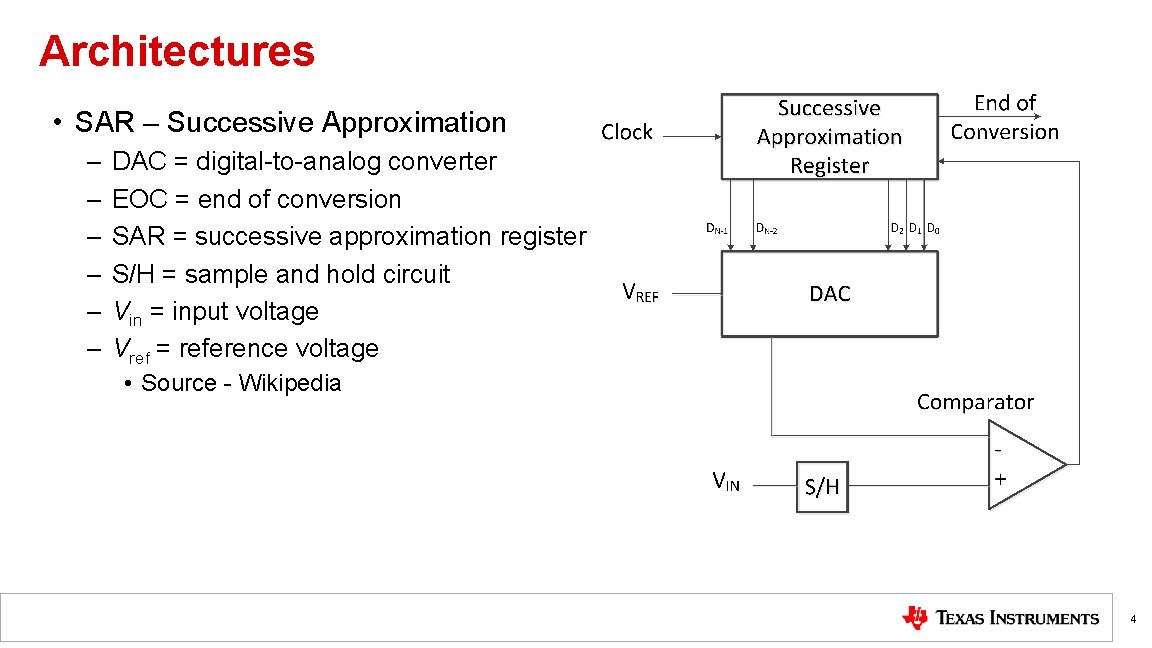

Architectures • SAR – Successive Approximation – – – DAC = digital-to-analog converter EOC = end of conversion SAR = successive approximation register S/H = sample and hold circuit Vin = input voltage Vref = reference voltage • Source - Wikipedia 4

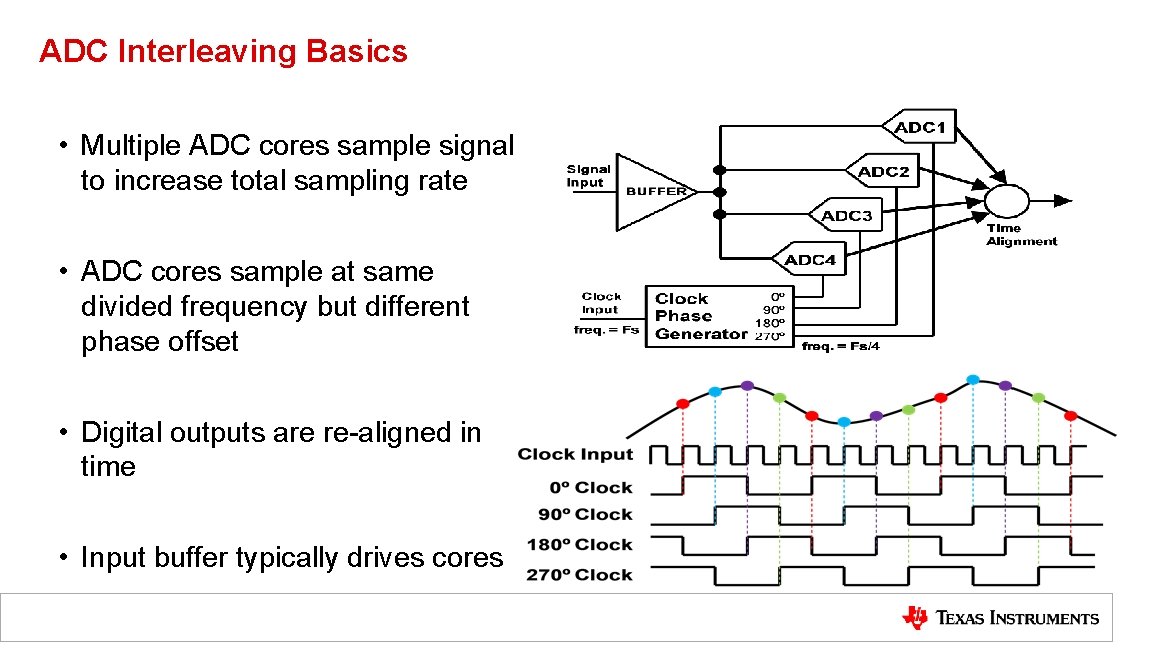

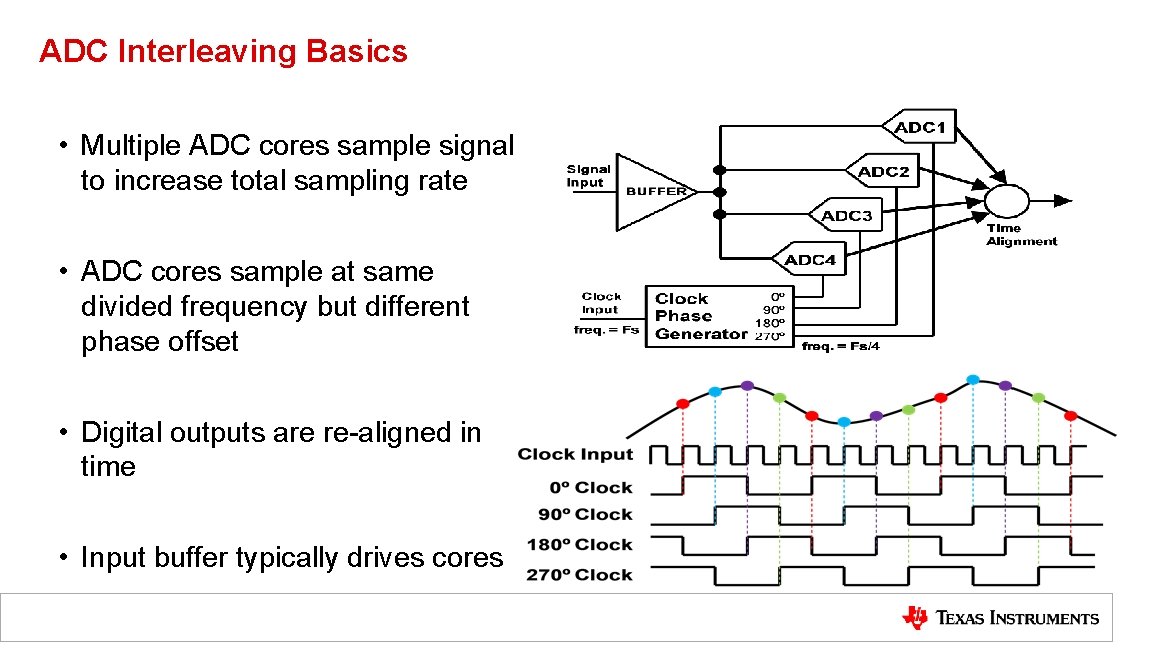

ADC Interleaving Basics • Multiple ADC cores sample signal to increase total sampling rate • ADC cores sample at same divided frequency but different phase offset • Digital outputs are re-aligned in time • Input buffer typically drives cores

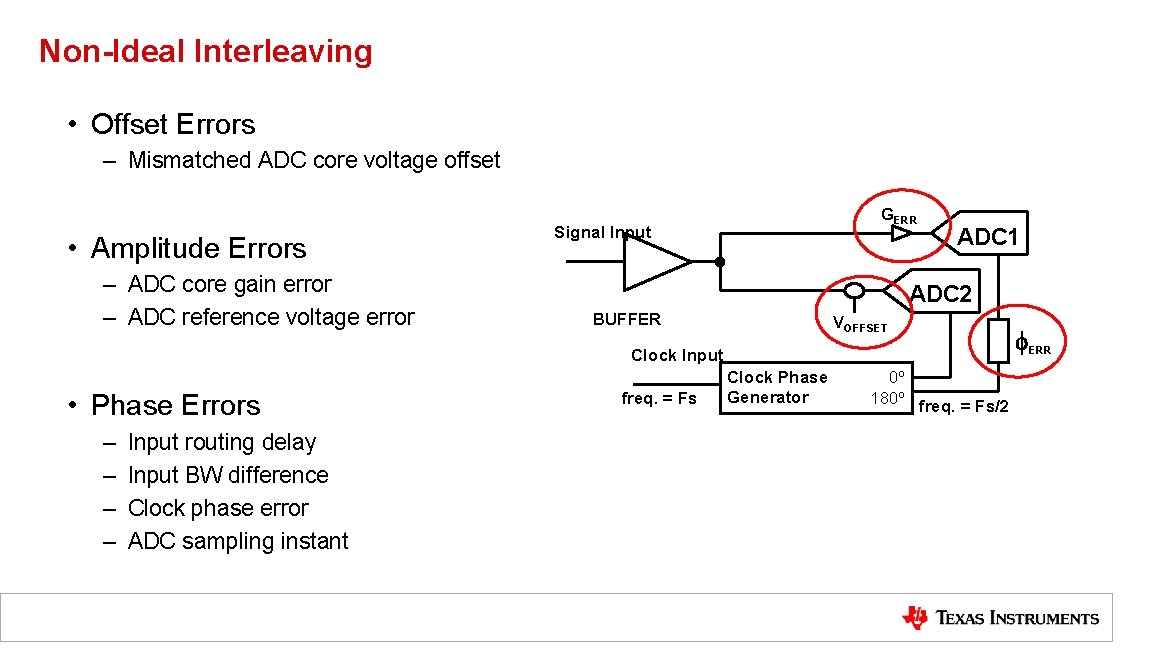

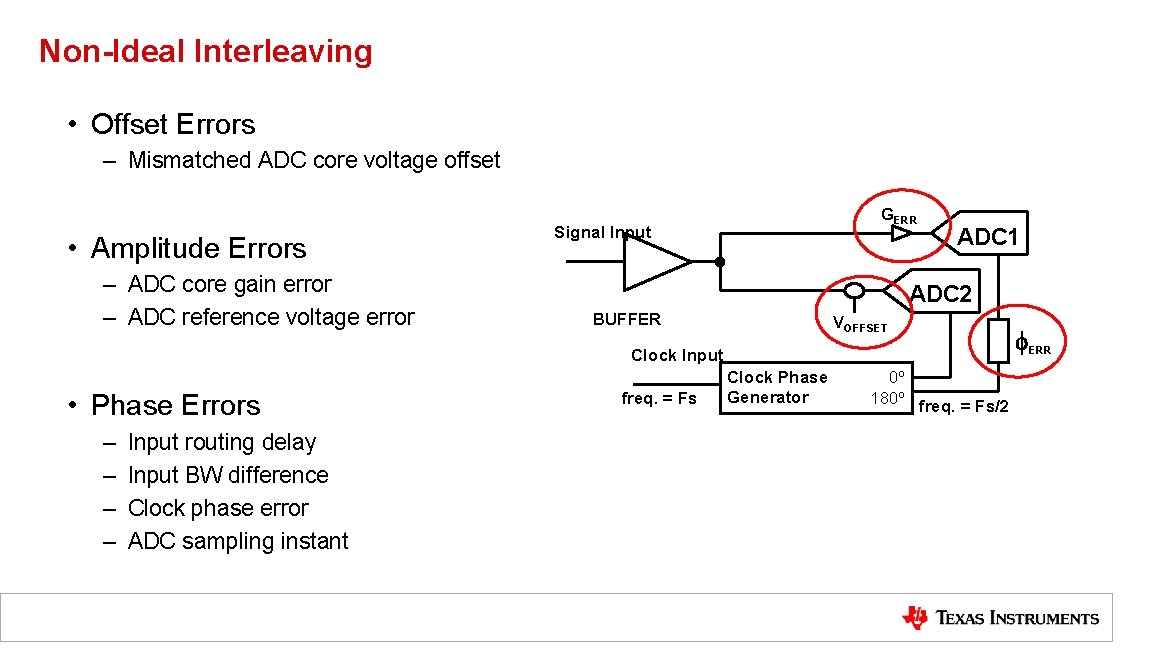

Non-Ideal Interleaving • Offset Errors – Mismatched ADC core voltage offset • Amplitude Errors – ADC core gain error – ADC reference voltage error GERR Signal Input ADC 1 ADC 2 BUFFER VOFFSET Clock Input • Phase Errors – – Input routing delay Input BW difference Clock phase error ADC sampling instant freq. = Fs Clock Phase Generator 0º 180º freq. = Fs/2 ERR

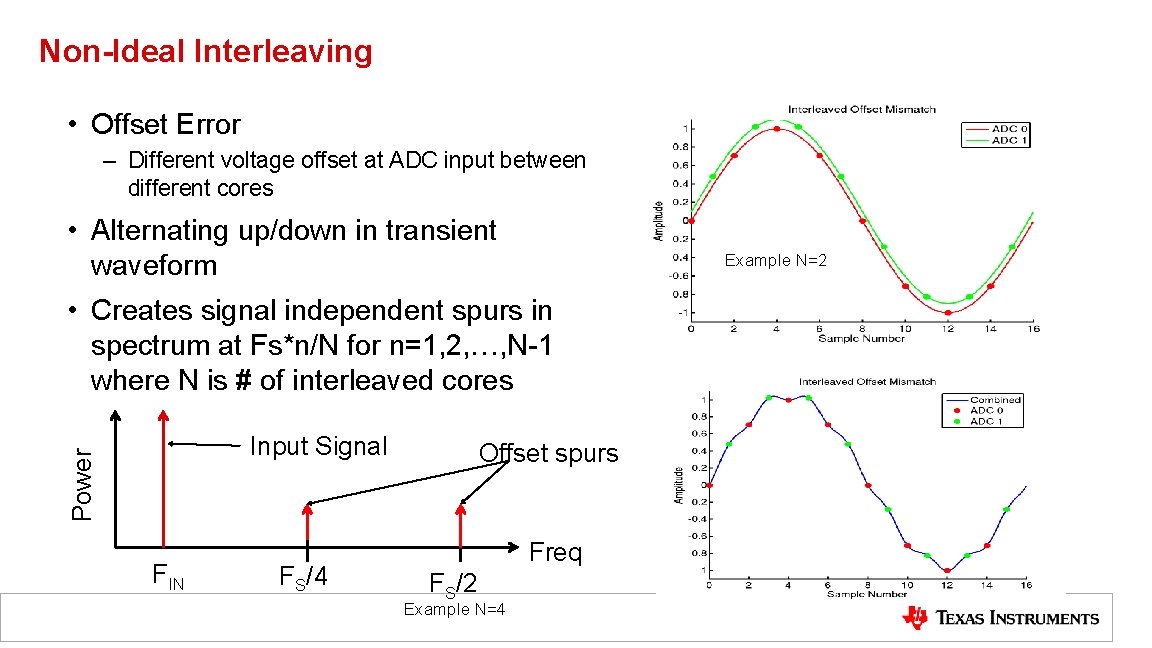

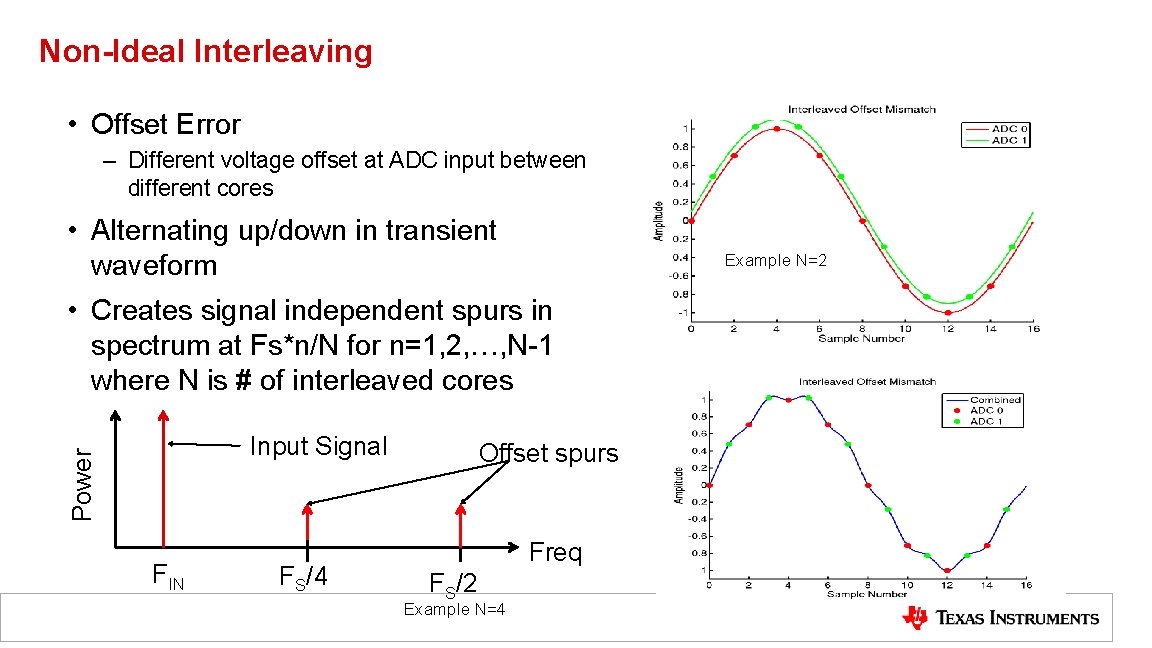

Non-Ideal Interleaving • Offset Error – Different voltage offset at ADC input between different cores • Alternating up/down in transient waveform Example N=2 • Creates signal independent spurs in spectrum at Fs*n/N for n=1, 2, …, N-1 where N is # of interleaved cores Power Input Signal FIN FS/4 Offset spurs Freq FS/2 Example N=4

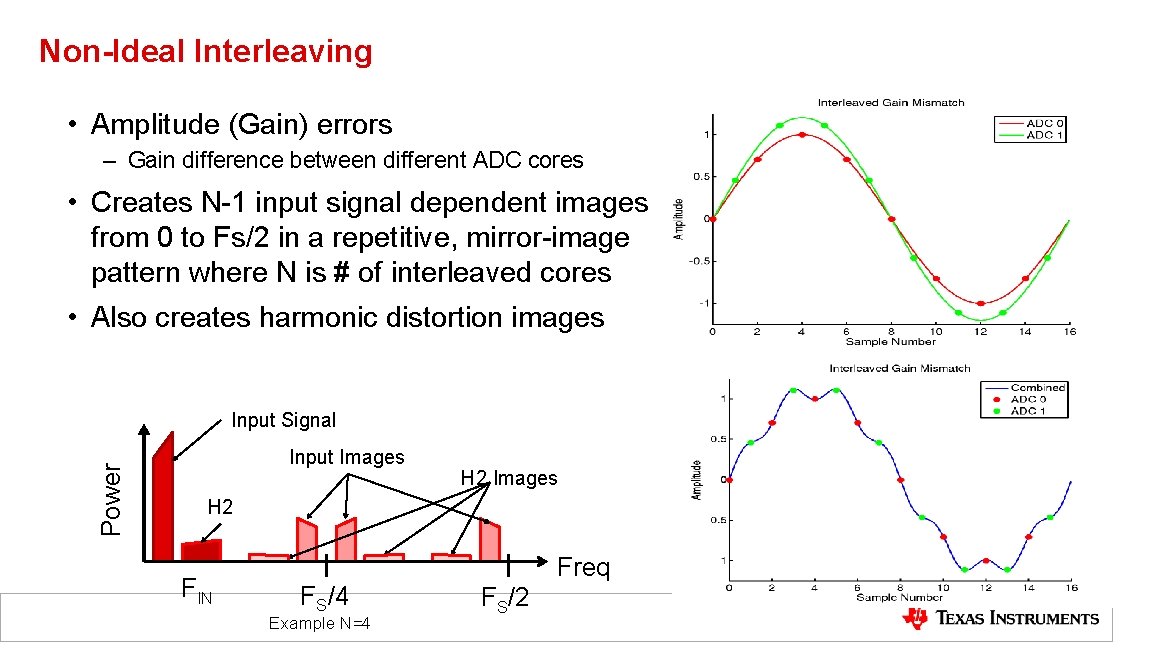

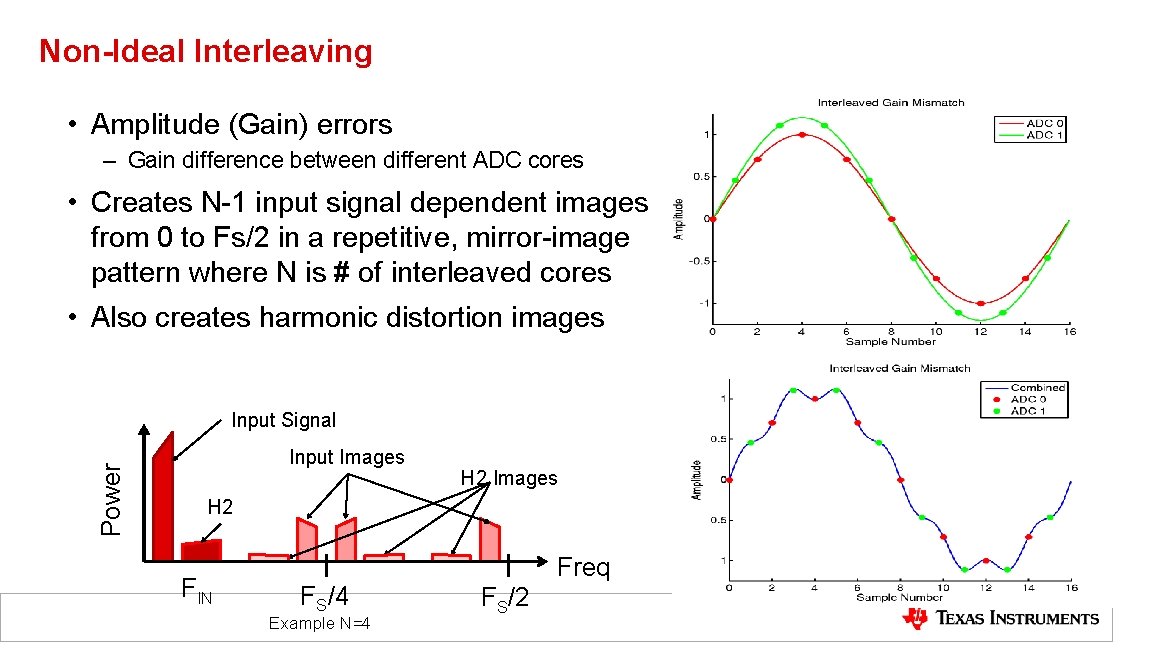

Non-Ideal Interleaving • Amplitude (Gain) errors – Gain difference between different ADC cores • Creates N-1 input signal dependent images from 0 to Fs/2 in a repetitive, mirror-image pattern where N is # of interleaved cores • Also creates harmonic distortion images Power Input Signal Input Images H 2 FIN FS/4 Example N=4 Freq FS/2

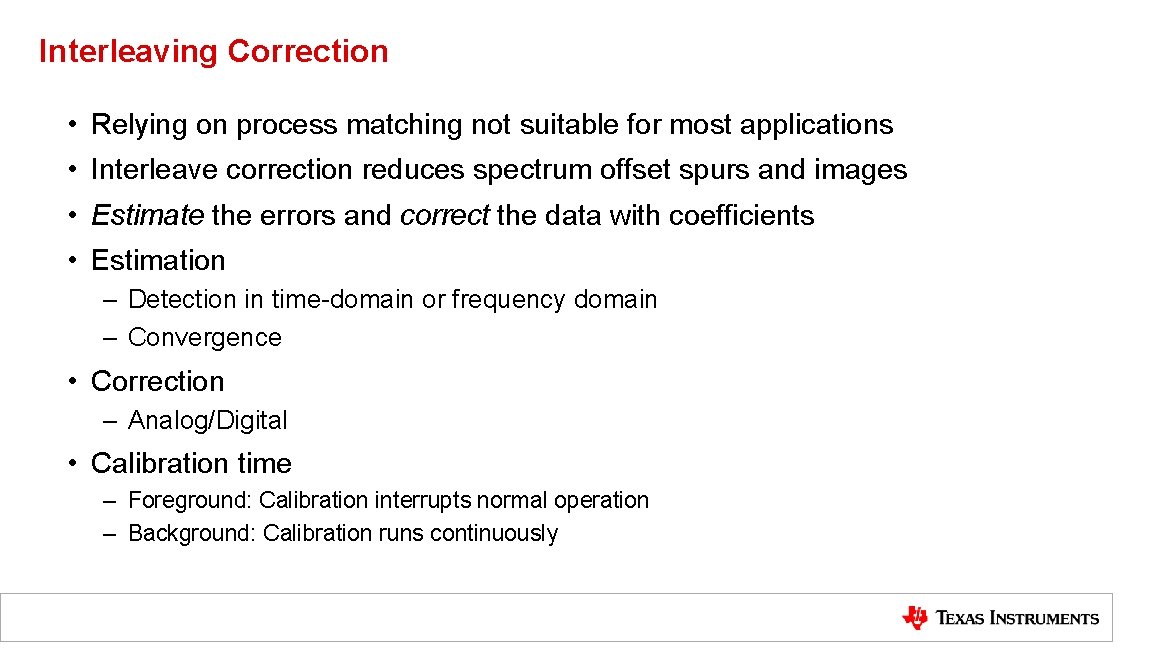

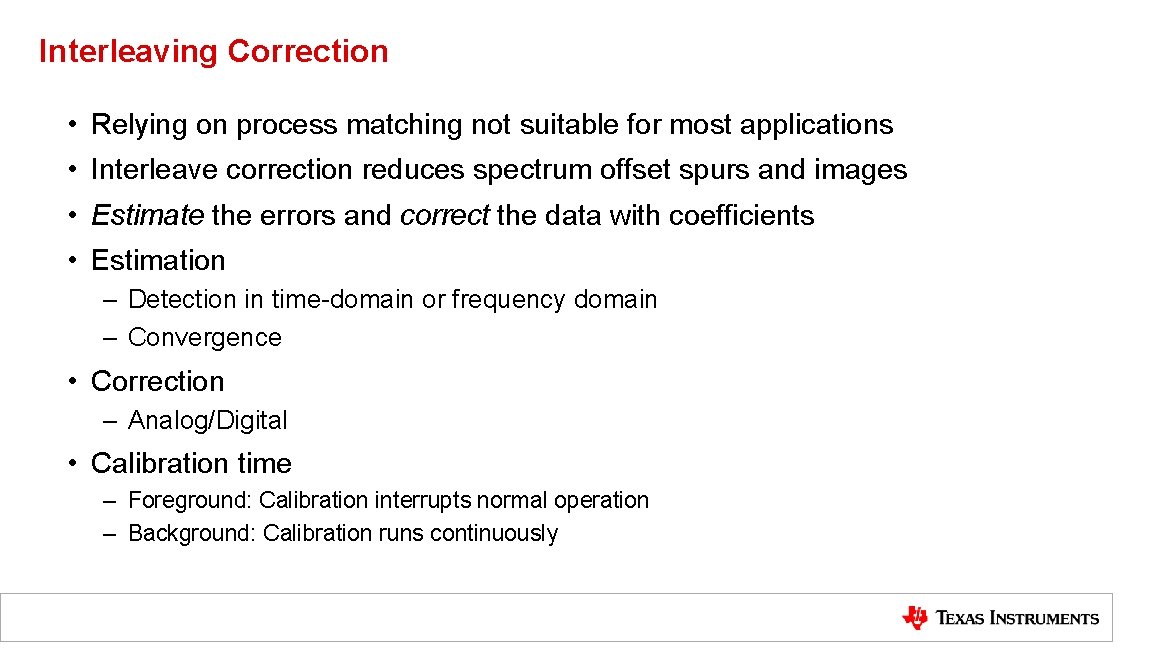

Interleaving Correction • Relying on process matching not suitable for most applications • Interleave correction reduces spectrum offset spurs and images • Estimate the errors and correct the data with coefficients • Estimation – Detection in time-domain or frequency domain – Convergence • Correction – Analog/Digital • Calibration time – Foreground: Calibration interrupts normal operation – Background: Calibration runs continuously

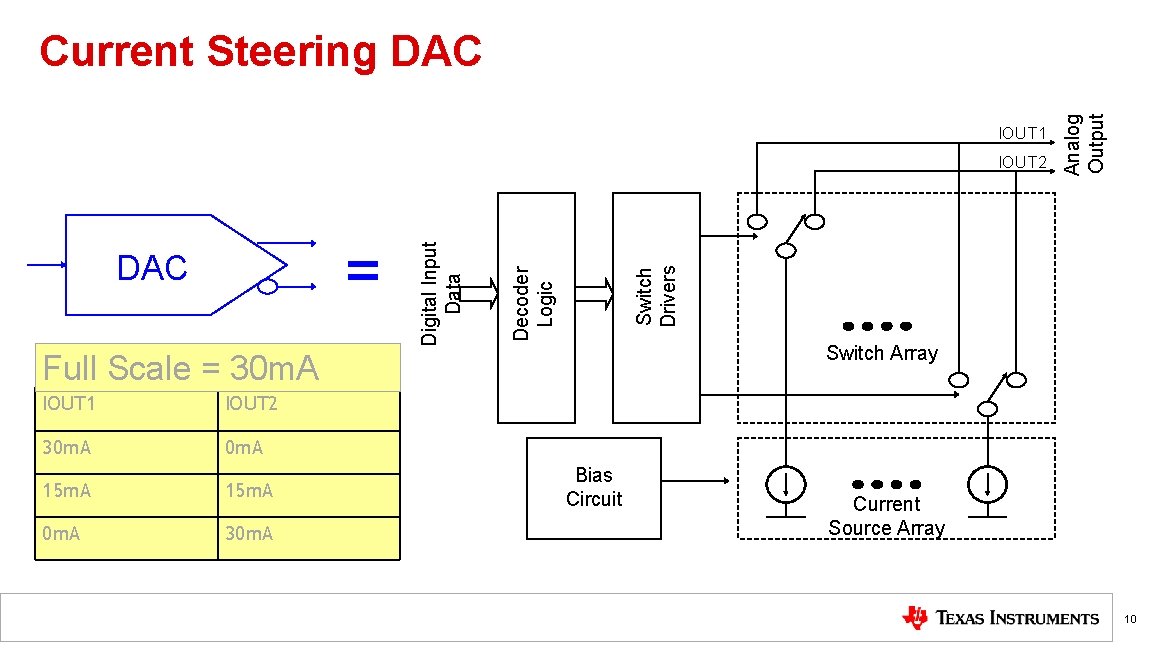

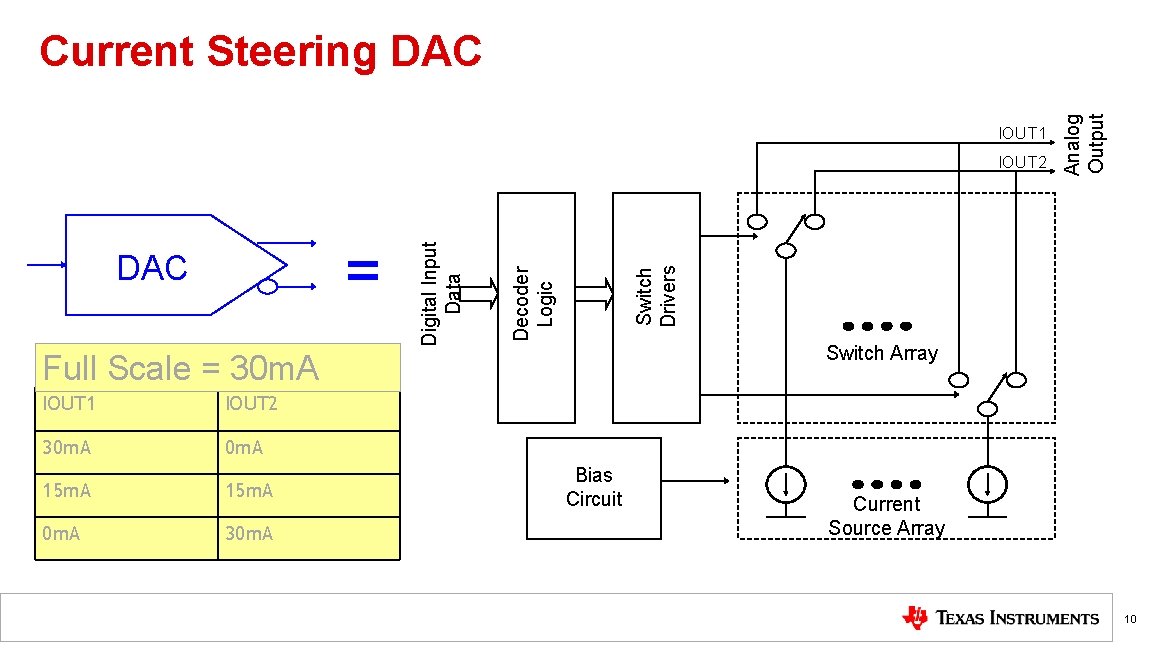

IOUT 1 Switch Drivers Decoder Logic = DAC Digital Input Data IOUT 2 Switch Array Full Scale = 30 m. A IOUT 1 IOUT 2 30 m. A 15 m. A 0 m. A 30 m. A Analog Output Current Steering DAC Bias Circuit Current Source Array 10

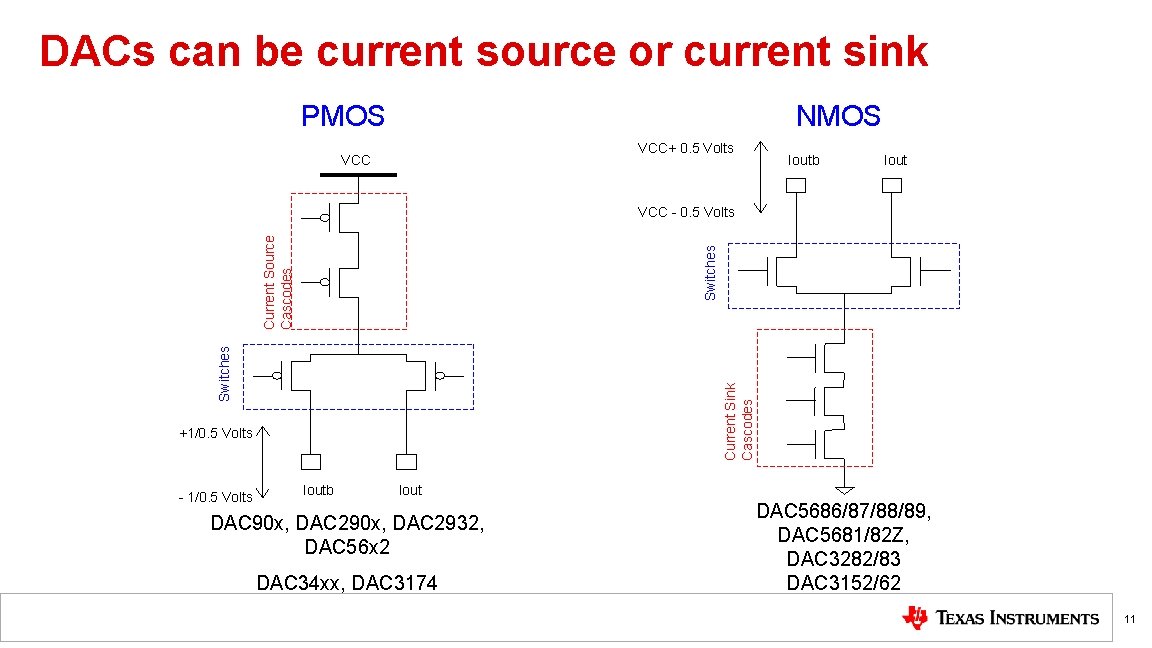

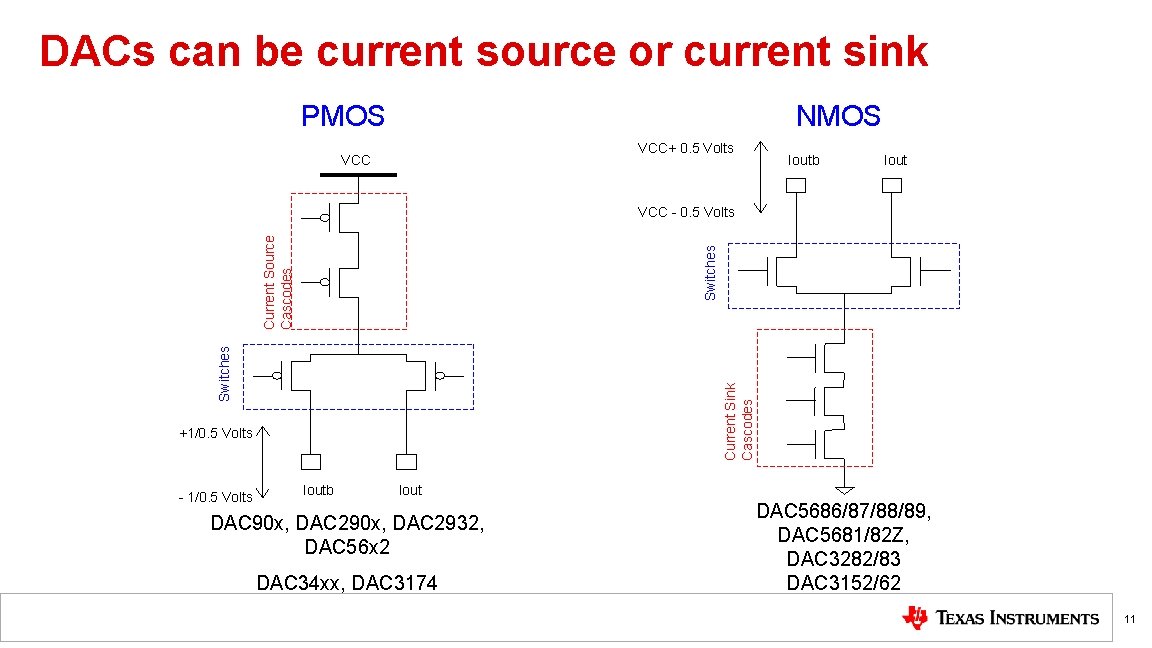

DACs can be current source or current sink PMOS NMOS VCC+ 0. 5 Volts VCC Ioutb Iout Current Sink Cascodes Switches Current Source Cascodes VCC - 0. 5 Volts +1/0. 5 Volts - 1/0. 5 Volts Ioutb Iout DAC 90 x, DAC 2932, DAC 56 x 2 DAC 34 xx, DAC 3174 DAC 5686/87/88/89, DAC 5681/82 Z, DAC 3282/83 DAC 3152/62 11

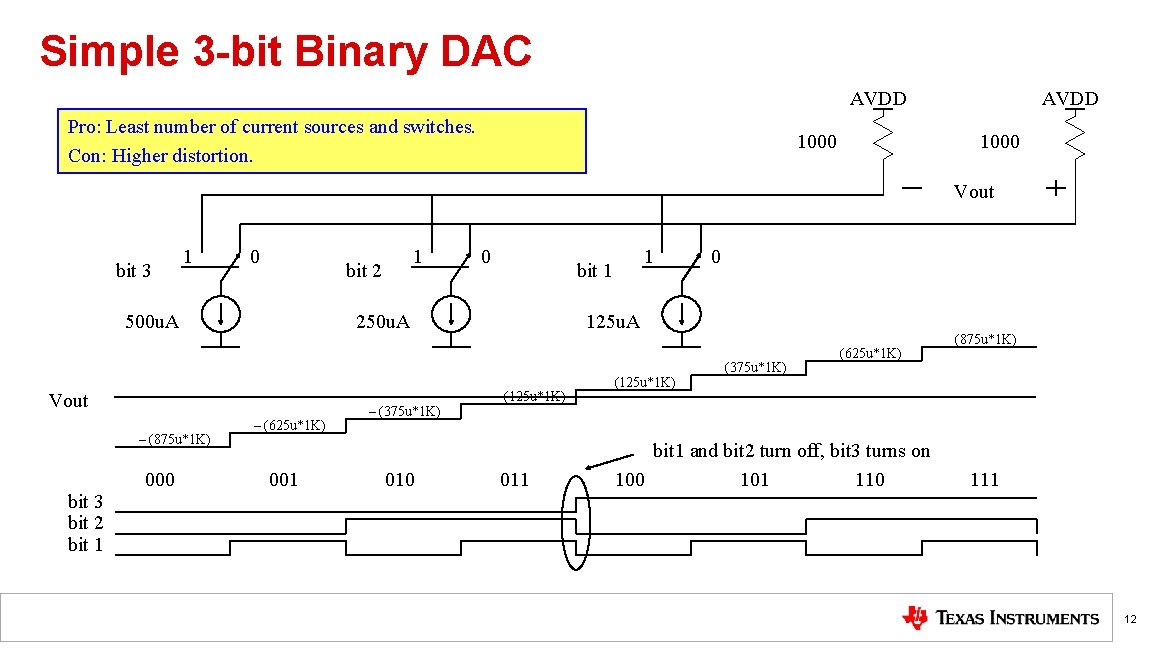

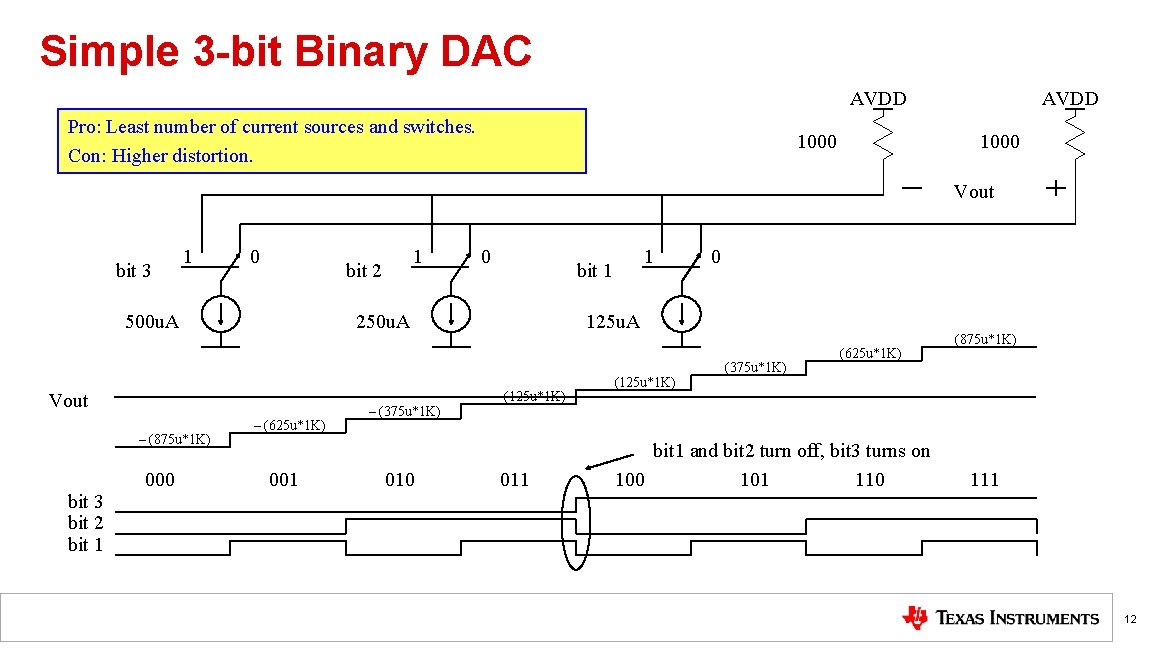

Simple 3 -bit Binary DAC AVDD Pro: Least number of current sources and switches. Con: Higher distortion. 1000 AVDD 1000 Vout bit 3 1 0 bit 2 500 u. A bit 3 bit 2 bit 1 000 0 – (625 u*1 K) 001 – (375 u*1 K) 010 1 bit 1 250 u. A Vout – (875 u*1 K) 1 0 125 u. A – (125 u*1 K) 011 (125 u*1 K) (375 u*1 K) (625 u*1 K) bit 1 and bit 2 turn off, bit 3 turns on 100 101 110 (875 u*1 K) 111 12

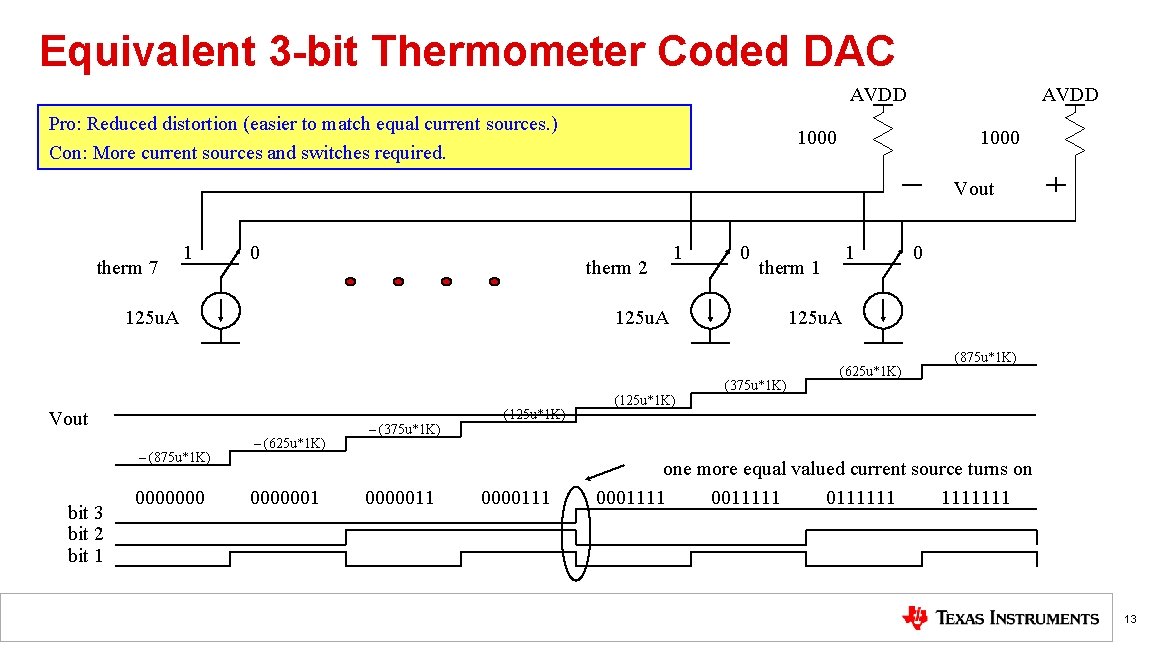

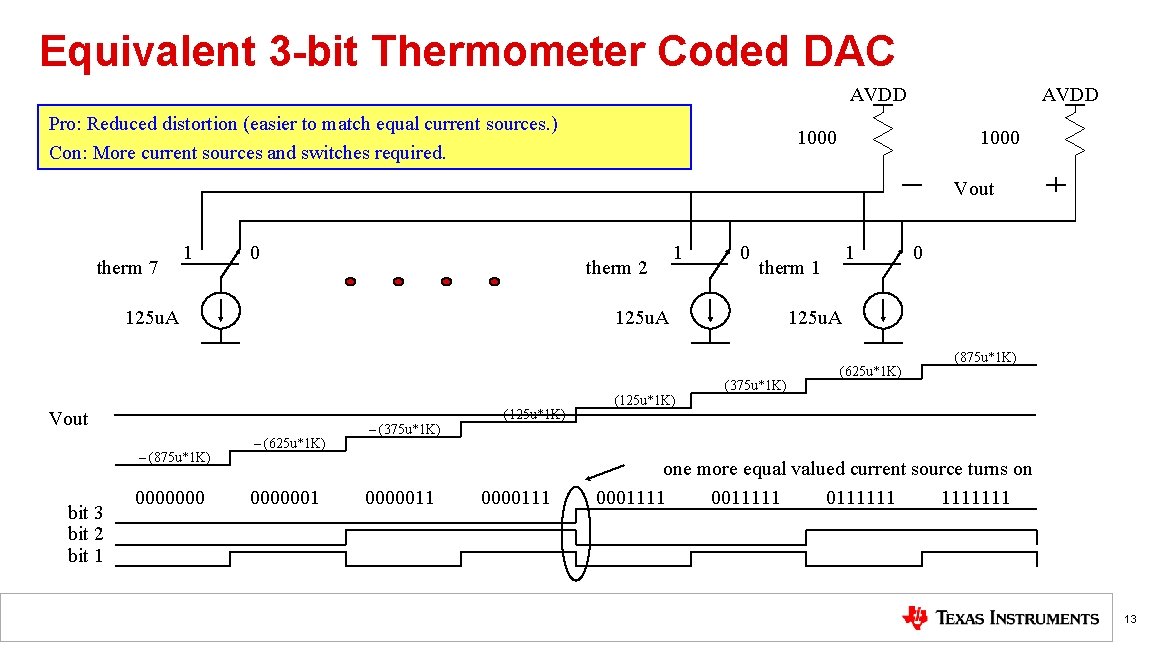

Equivalent 3 -bit Thermometer Coded DAC AVDD Pro: Reduced distortion (easier to match equal current sources. ) Con: More current sources and switches required. AVDD 1000 Vout therm 7 1 0 therm 2 125 u. A bit 3 bit 2 bit 1 0000000 0 – (625 u*1 K) 0000001 – (375 u*1 K) 0000011 – (125 u*1 K) 0000111 (125 u*1 K) 1 therm 1 125 u. A Vout – (875 u*1 K) 1 0 125 u. A (375 u*1 K) (625 u*1 K) (875 u*1 K) one more equal valued current source turns on 00011111 0111111 13

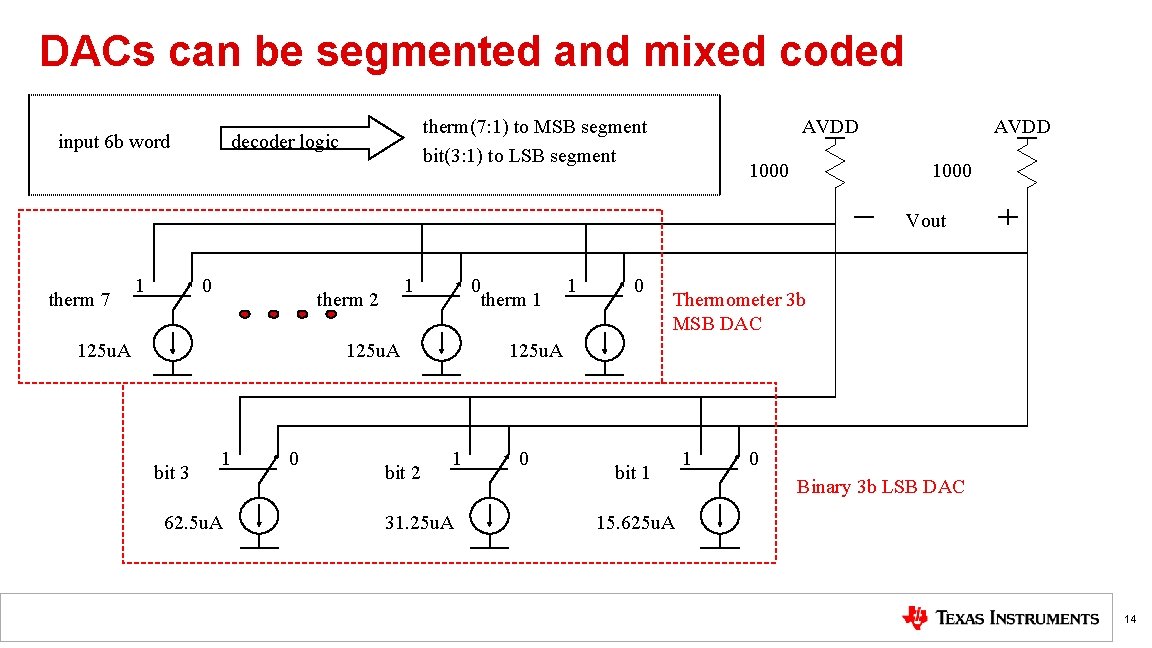

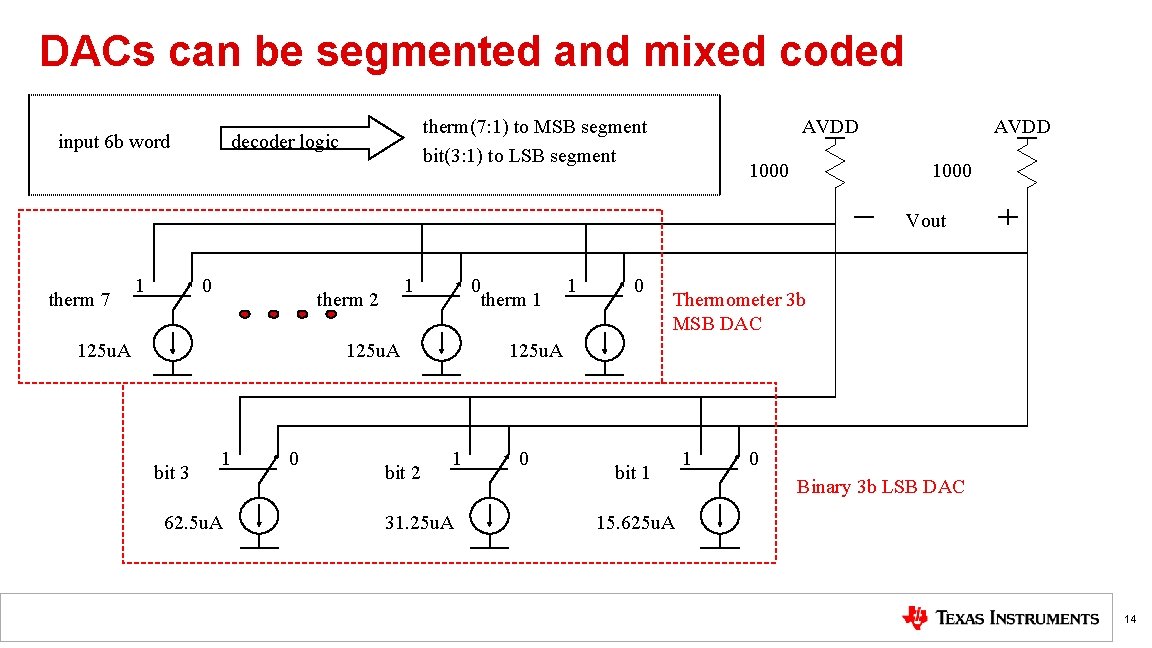

DACs can be segmented and mixed coded input 6 b word therm(7: 1) to MSB segment bit(3: 1) to LSB segment decoder logic AVDD 1000 Vout therm 7 1 0 1 therm 2 125 u. A 0 therm 1 125 u. A bit 3 1 62. 5 u. A 0 bit 2 1 0 Thermometer 3 b MSB DAC 125 u. A 1 31. 25 u. A 0 bit 1 1 0 Binary 3 b LSB DAC 15. 625 u. A 14

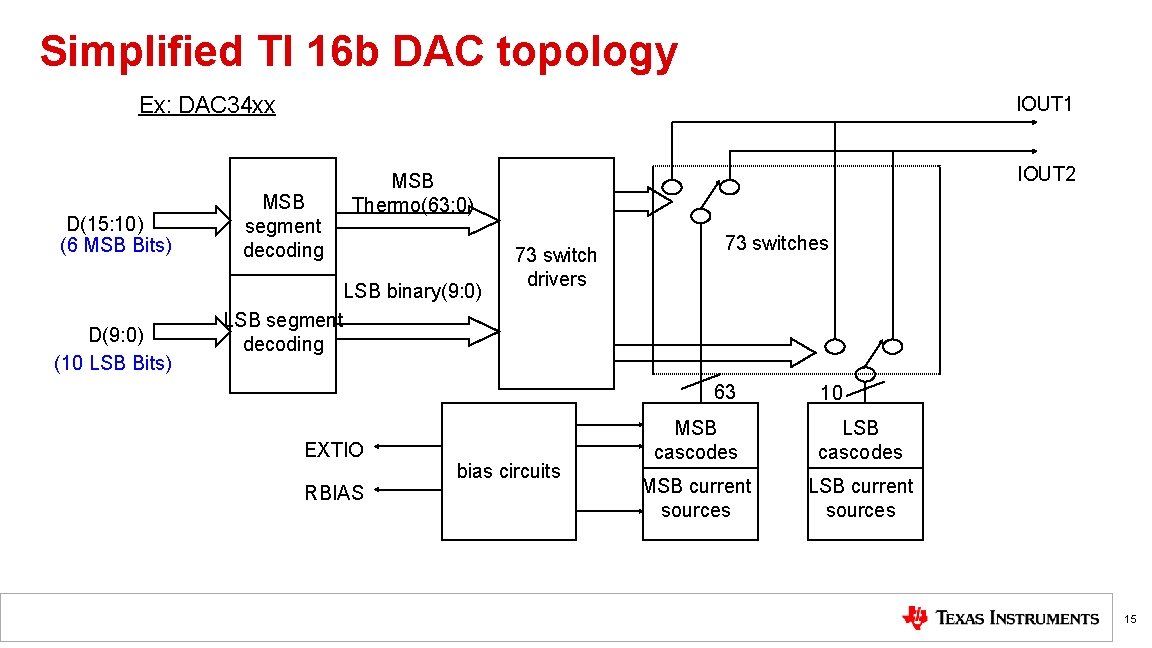

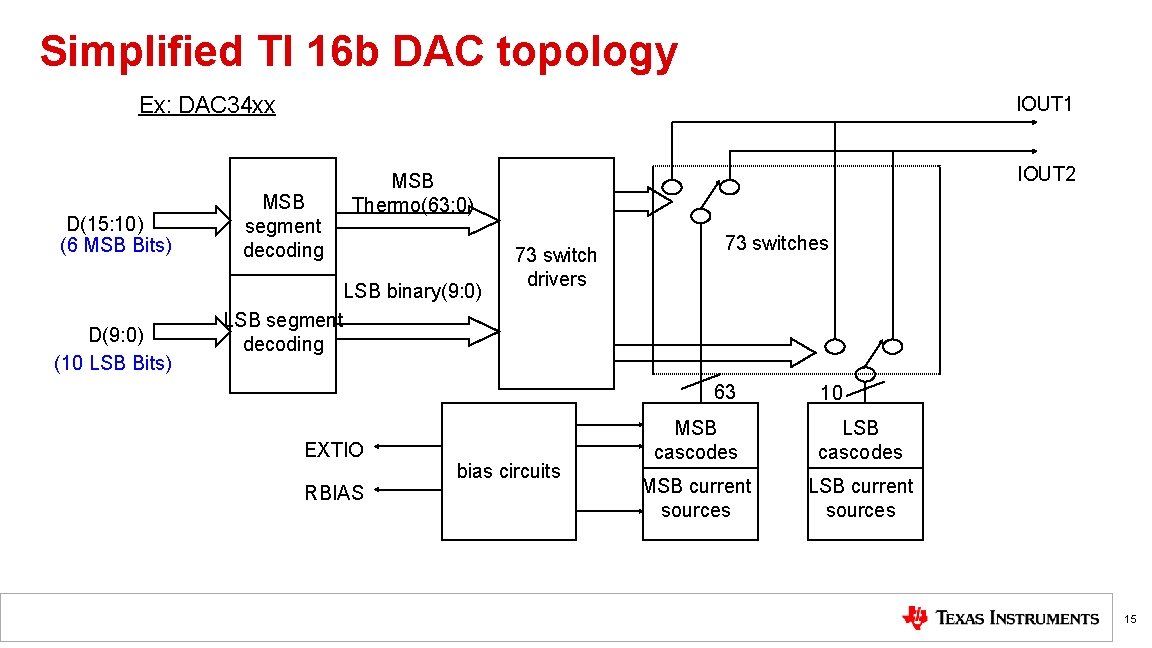

Simplified TI 16 b DAC topology Ex: DAC 34 xx D(15: 10) (6 MSB Bits) IOUT 1 MSB segment decoding LSB binary(9: 0) D(9: 0) (10 LSB Bits) IOUT 2 MSB Thermo(63: 0) 73 switch drivers 73 switches LSB segment decoding 63 EXTIO RBIAS bias circuits 10 MSB cascodes LSB cascodes MSB current sources LSB current sources 15

Thanks for your time! 16

© Copyright 2017 Texas Instruments Incorporated. All rights reserved. This material is provided strictly “as-is, ” for informational purposes only, and without any warranty. Use of this material is subject to TI’s Terms of Use, viewable at TI. com