ULTIMATE 1 ULTIMATE 2 n Objective ensure perfect

ULTIMATE 1 ULTIMATE 2 n Objective: ensure perfect function of sensor (yield 100%! ? ) Ä n Avoid even a minimal risk Modifications points: VLCP (V clamping) avec ESD (electrostatic discharge) projected PAD Ä Improve VCLP regulator performance, Iout 7 -8 m. A (~< 0. 2 m. A in the current design) Ä n n Ä 1 column or 1 row dead pixels: VCLP current ~ 3 m. A 1 block (16 columns or rows) dead pixels: VCLP current ~ 4 m. A Modify in layout to minimise the coupling between READ and bias of analogue buffer n n Improve analogue output performance, if possible up to 160 MHz Investigate the problem of analogue marker Investigate the possibility to implement Power On Reset Ä Improve READ & READb delay dispersion of column-level discriminators Ä ID code Ä Ä 15/09/2011 Pixel optimisation STAR LBNL/IPHC Tel. Meeting IPHC christine. hu@ires. in 2 p 3. fr 1

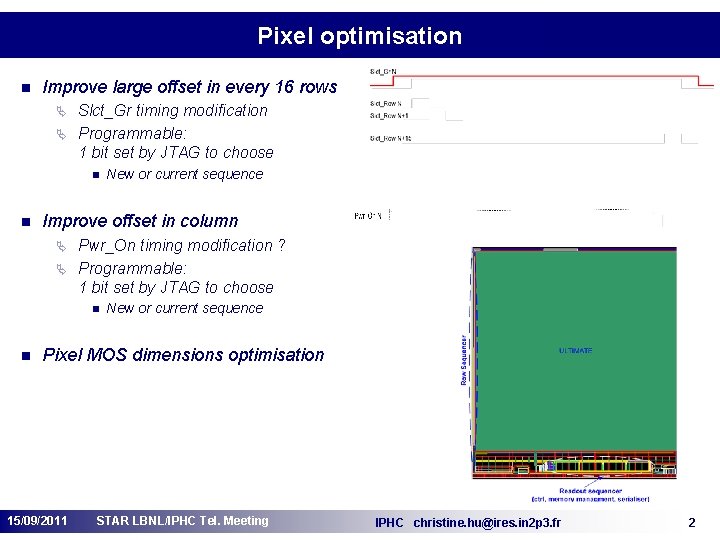

Pixel optimisation n Improve large offset in every 16 rows Slct_Gr timing modification Ä Programmable: 1 bit set by JTAG to choose Ä n n New or current sequence Improve offset in column Pwr_On timing modification ? Ä Programmable: 1 bit set by JTAG to choose Ä n n New or current sequence Pixel MOS dimensions optimisation 15/09/2011 STAR LBNL/IPHC Tel. Meeting IPHC christine. hu@ires. in 2 p 3. fr 2

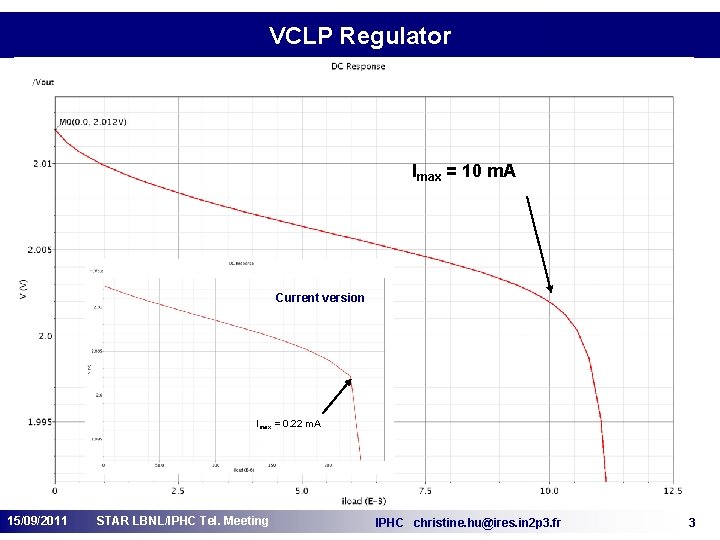

VCLP Regulator Imax = 10 m. A Current version Imax = 0. 22 m. A 15/09/2011 STAR LBNL/IPHC Tel. Meeting IPHC christine. hu@ires. in 2 p 3. fr 3

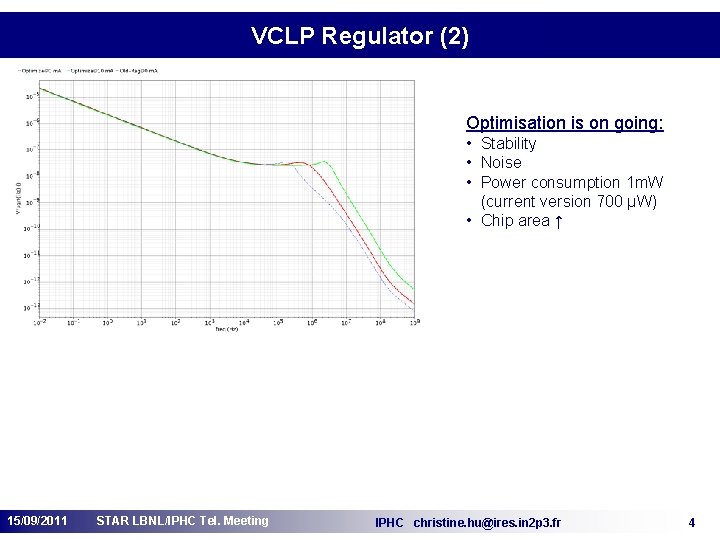

VCLP Regulator (2) Optimisation is on going: • Stability • Noise • Power consumption 1 m. W (current version 700 µW) • Chip area ↑ 15/09/2011 STAR LBNL/IPHC Tel. Meeting IPHC christine. hu@ires. in 2 p 3. fr 4

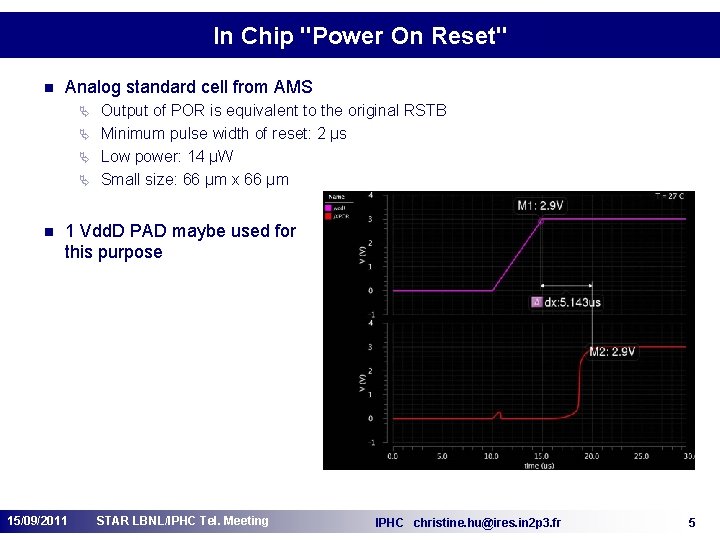

In Chip "Power On Reset" n Analog standard cell from AMS Output of POR is equivalent to the original RSTB Ä Minimum pulse width of reset: 2 µs Ä Low power: 14 µW Ä Small size: 66 µm x 66 µm Ä n 1 Vdd. D PAD maybe used for this purpose 15/09/2011 STAR LBNL/IPHC Tel. Meeting IPHC christine. hu@ires. in 2 p 3. fr 5

- Slides: 5