Ulrich Uwer LHCC Review University of Heidelberg CERN

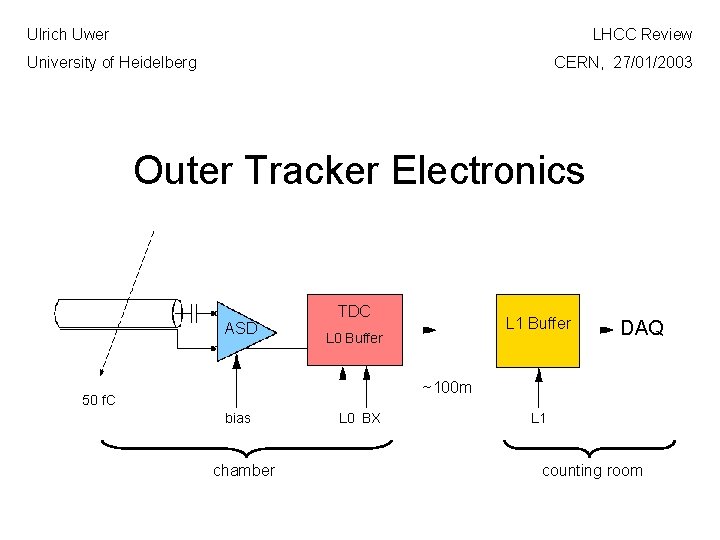

Ulrich Uwer LHCC Review University of Heidelberg CERN, 27/01/2003 Outer Tracker Electronics ASD TDC L 1 Buffer L 0 Buffer DAQ ~100 m 50 f. C bias chamber L 0 BX L 1 counting room

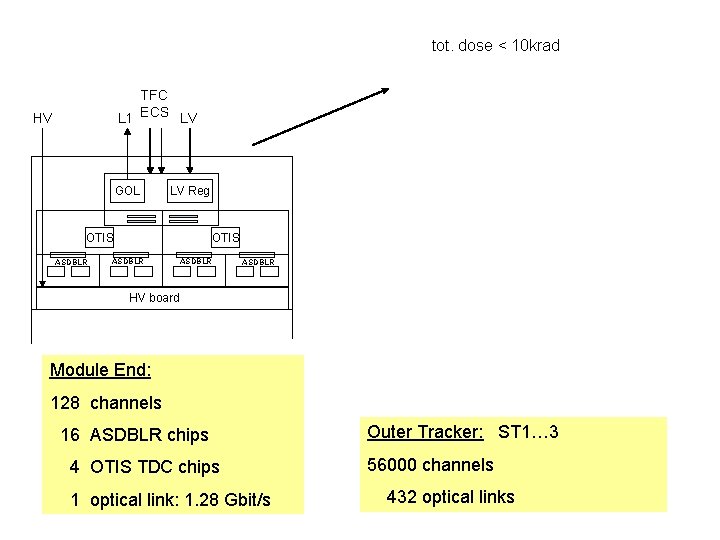

tot. dose < 10 krad TFC L 1 ECS LV HV GOL LV Reg OTIS ASDBLR HV board Module End: 128 channels 16 ASDBLR chips 4 OTIS TDC chips 1 optical link: 1. 28 Gbit/s Outer Tracker: ST 1… 3 56000 channels 432 optical links

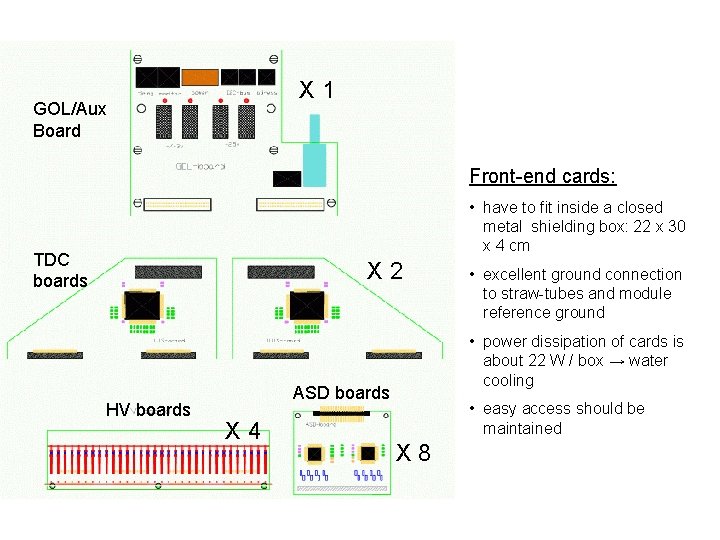

X 1 GOL/Aux Board Front-end cards: • have to fit inside a closed metal shielding box: 22 x 30 x 4 cm TDC boards X 2 HV boards • power dissipation of cards is about 22 W / box → water cooling ASD boards X 4 • excellent ground connection to straw-tubes and module reference ground • easy access should be maintained X 8

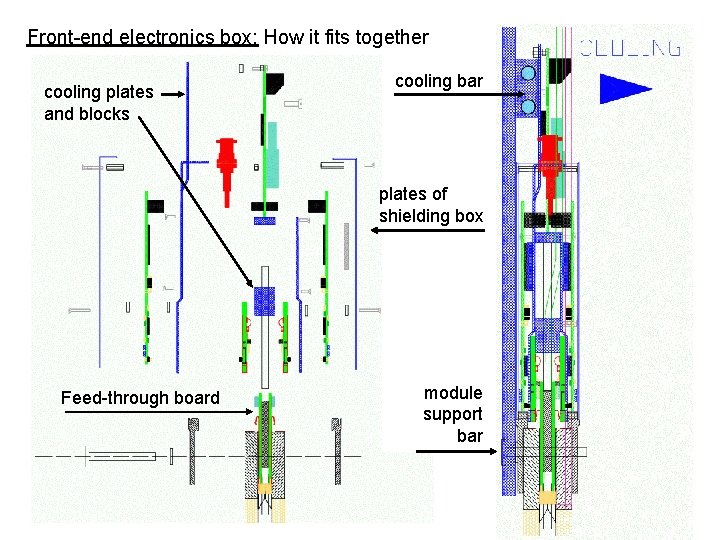

Front-end electronics box: How it fits together cooling plates and blocks cooling bar plates of shielding box Feed-through board module support bar

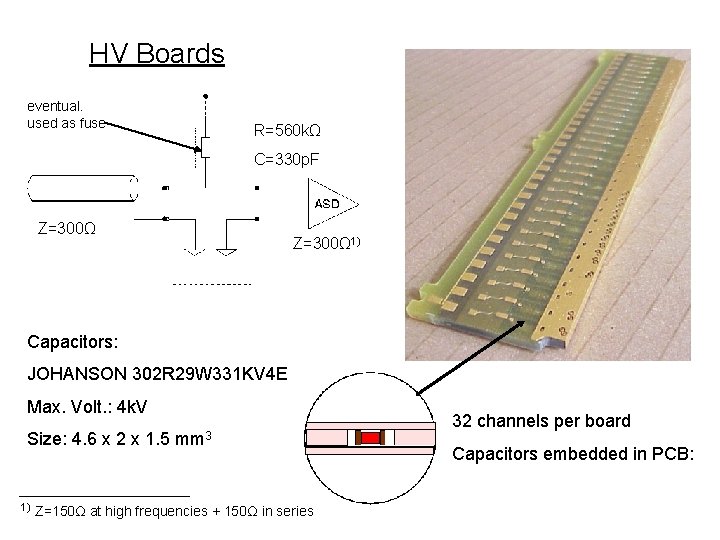

HV Boards eventual. used as fuse R=560 kΩ C=330 p. F Z=300Ω 1) Capacitors: JOHANSON 302 R 29 W 331 KV 4 E Max. Volt. : 4 k. V Size: 4. 6 x 2 x 1. 5 1) mm 3 Z=150Ω at high frequencies + 150Ω in series 32 channels per board Capacitors embedded in PCB:

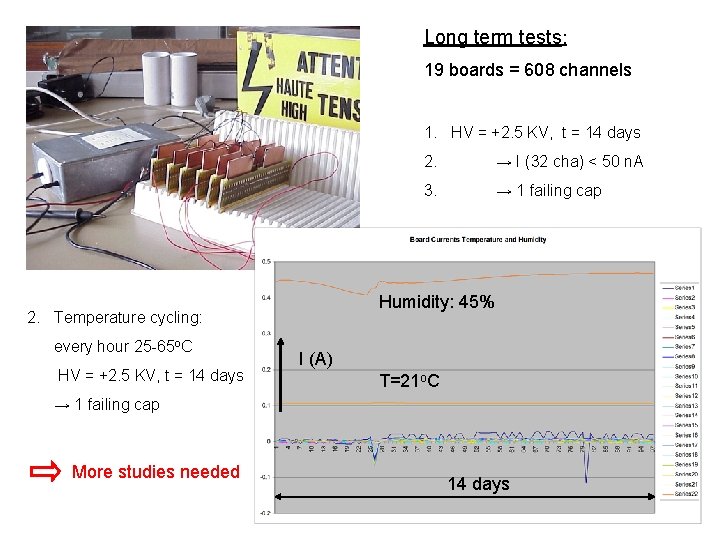

Long term tests: 19 boards = 608 channels 1. HV = +2. 5 KV, t = 14 days → I (32 cha) < 50 n. A 3. → 1 failing cap Humidity: 45% 2. Temperature cycling: every hour 25 -65 o. C 2. I (A) T=21 o. C → 1 failing cap More studies needed 14 days

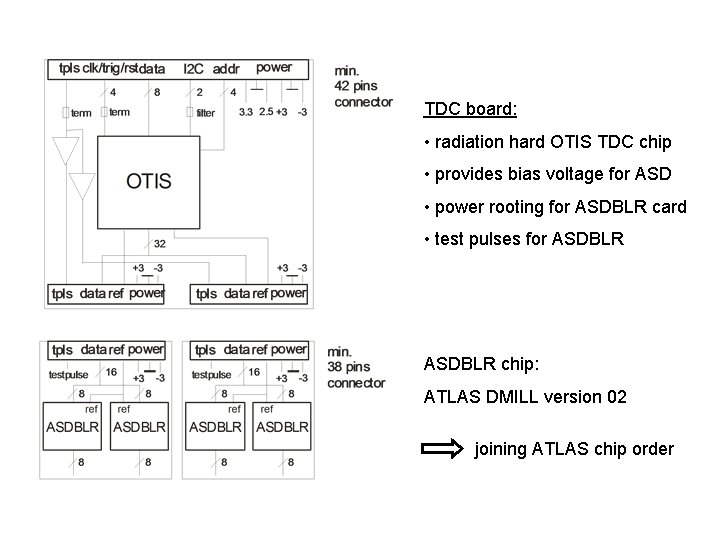

TDC board: • radiation hard OTIS TDC chip • provides bias voltage for ASD • power rooting for ASDBLR card • test pulses for ASDBLR chip: ATLAS DMILL version 02 joining ATLAS chip order

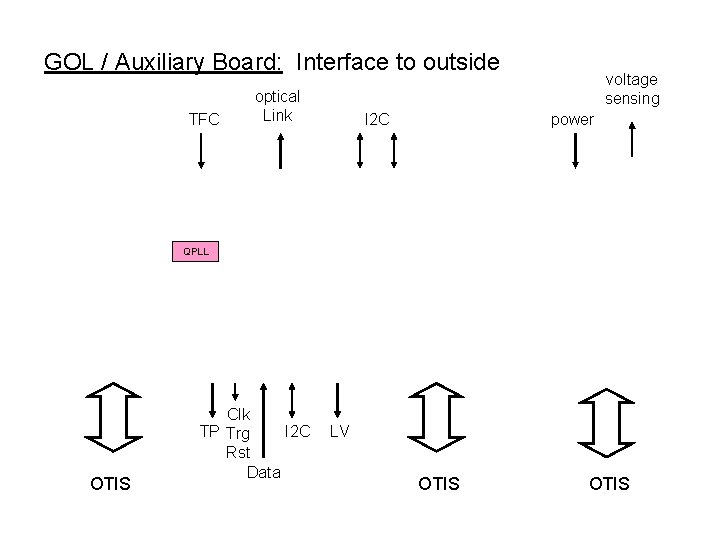

GOL / Auxiliary Board: Interface to outside TFC optical Link I 2 C voltage sensing power QPLL OTIS Clk TP Trg I 2 C Rst Data LV OTIS

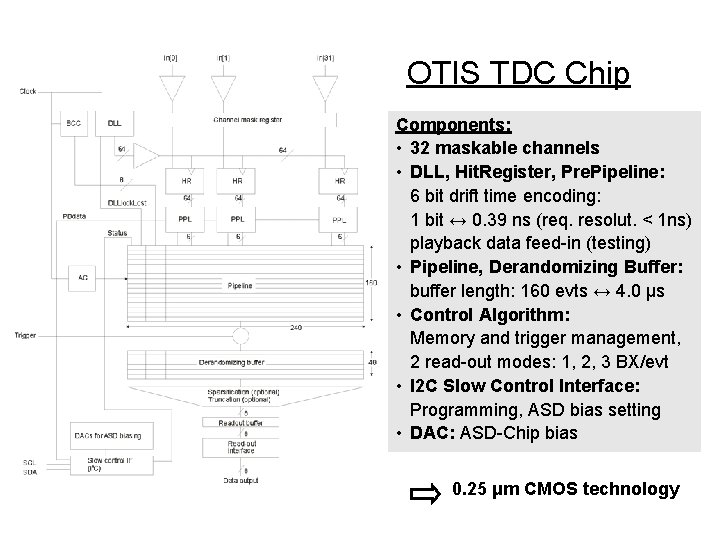

OTIS TDC Chip Components: • 32 maskable channels • DLL, Hit. Register, Pre. Pipeline: 6 bit drift time encoding: 1 bit ↔ 0. 39 ns (req. resolut. < 1 ns) playback data feed-in (testing) • Pipeline, Derandomizing Buffer: buffer length: 160 evts ↔ 4. 0 μs • Control Algorithm: Memory and trigger management, 2 read-out modes: 1, 2, 3 BX/evt • I 2 C Slow Control Interface: Programming, ASD bias setting • DAC: ASD-Chip bias 0. 25 μm CMOS technology

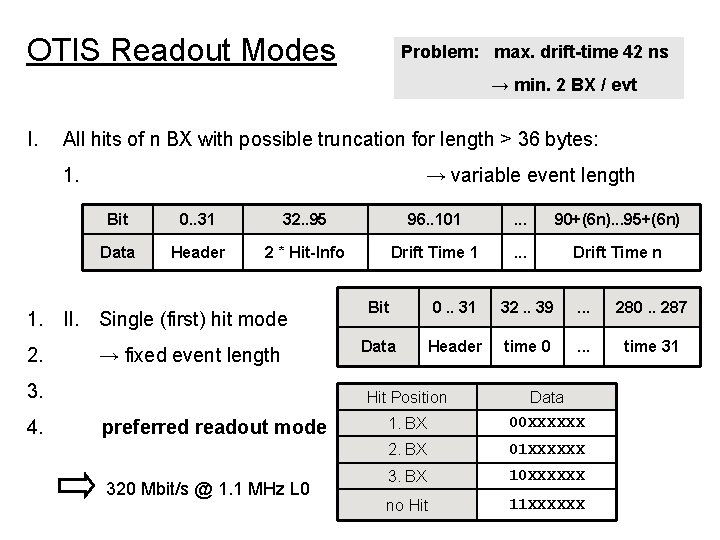

OTIS Readout Modes Problem: max. drift-time 42 ns → min. 2 BX / evt I. All hits of n BX with possible truncation for length > 36 bytes: 1. → variable event length Bit 0. . 31 32. . 95 96. . 101 . . . 90+(6 n). . . 95+(6 n) Data Header 2 * Hit-Info Drift Time 1 . . . Drift Time n 1. II. Single (first) hit mode 2. → fixed event length 3. 4. preferred readout mode 320 Mbit/s @ 1. 1 MHz L 0 Bit 0. . 31 32. . 39 . . . 280. . 287 Data Header time 0 . . . time 31 Hit Position Data 1. BX 00 XXXXXX 2. BX 01 XXXXXX 3. BX 10 XXXXXX no Hit 11 XXXXXX

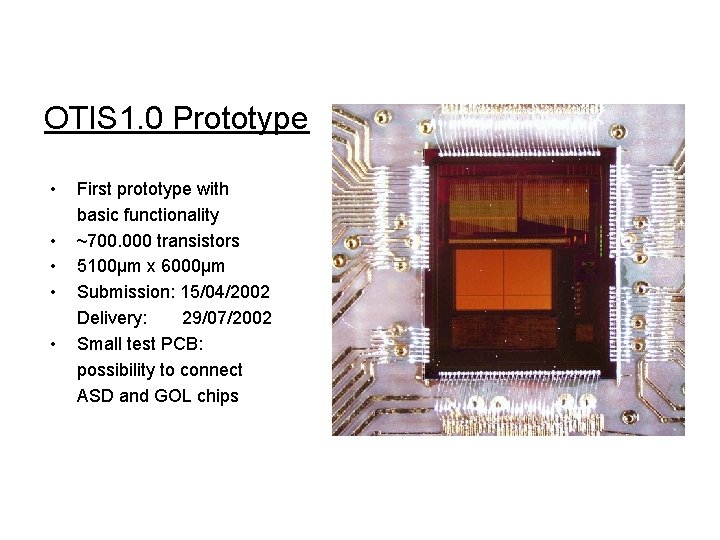

OTIS 1. 0 Prototype • • • First prototype with basic functionality ~700. 000 transistors 5100µm x 6000µm Submission: 15/04/2002 Delivery: 29/07/2002 Small test PCB: possibility to connect ASD and GOL chips

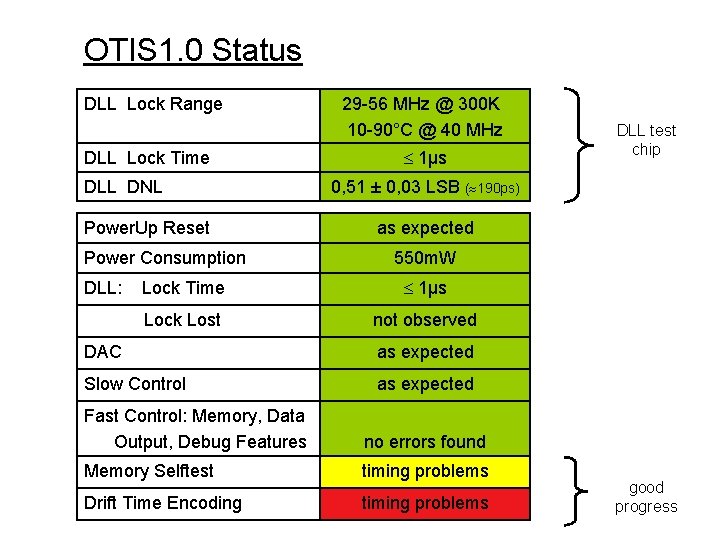

OTIS 1. 0 Status DLL Lock Range DLL Lock Time DLL DNL Power. Up Reset Power Consumption DLL: 29 -56 MHz @ 300 K 10 -90°C @ 40 MHz 1µs DLL test chip 0, 51 ± 0, 03 LSB ( 190 ps) as expected 550 m. W Lock Time 1µs Lock Lost not observed DAC as expected Slow Control as expected Fast Control: Memory, Data Output, Debug Features no errors found Memory Selftest timing problems Drift Time Encoding timing problems good progress

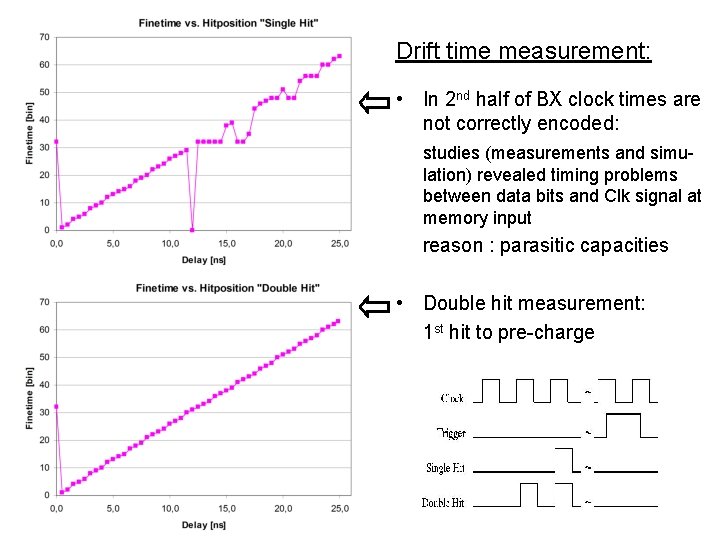

Drift time measurement: • In 2 nd half of BX clock times are not correctly encoded: studies (measurements and simulation) revealed timing problems between data bits and Clk signal at memory input reason : parasitic capacities • Double hit measurement: 1 st hit to pre-charge

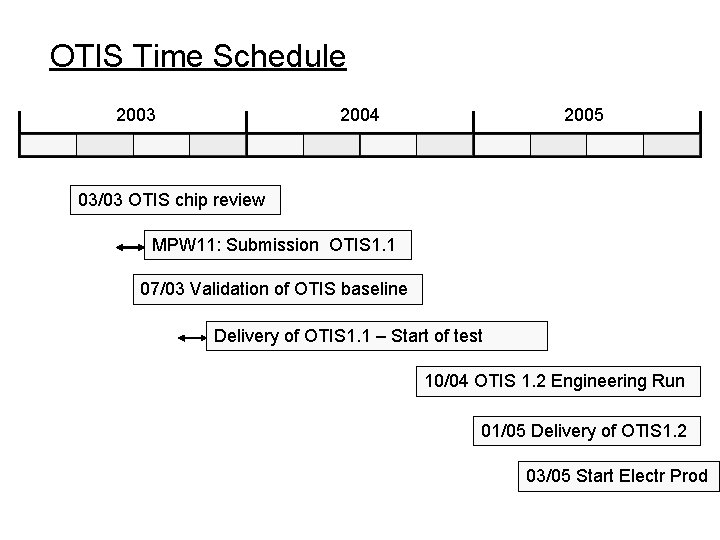

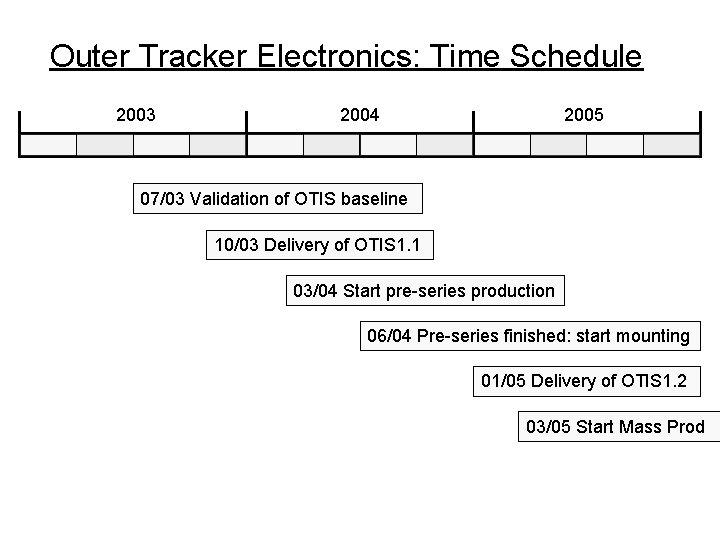

OTIS Time Schedule 2003 2004 2005 03/03 OTIS chip review MPW 11: Submission OTIS 1. 1 07/03 Validation of OTIS baseline Delivery of OTIS 1. 1 – Start of test 10/04 OTIS 1. 2 Engineering Run 01/05 Delivery of OTIS 1. 2 03/05 Start Electr Prod

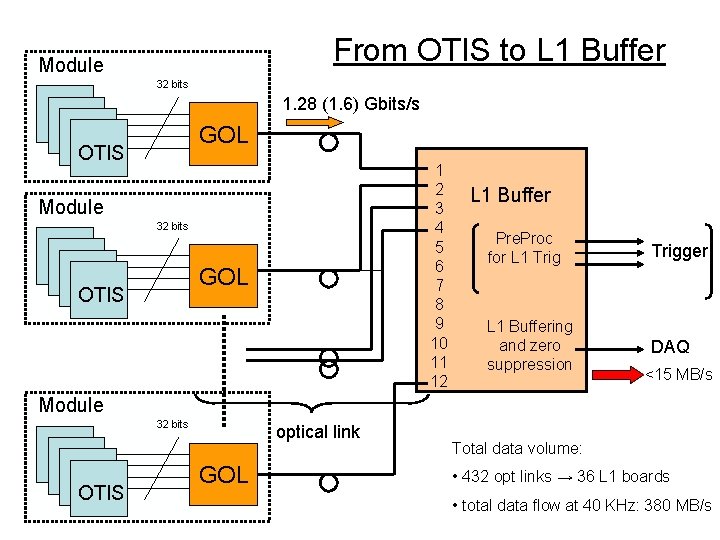

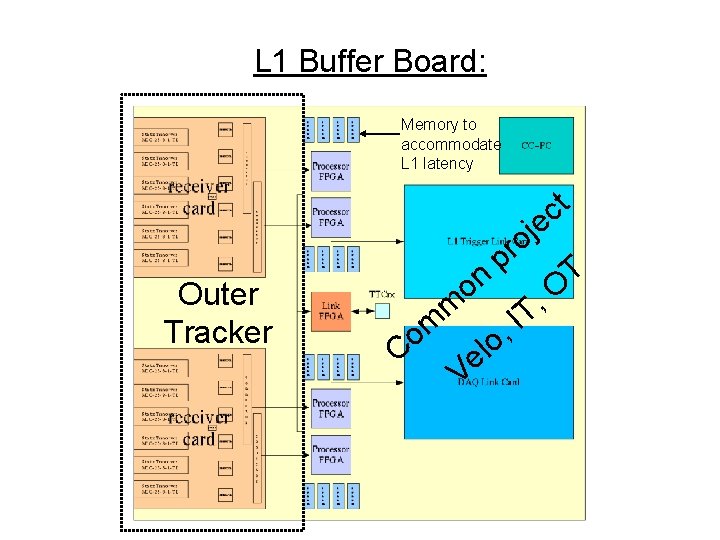

From OTIS to L 1 Buffer Module 32 bits 1. 28 (1. 6) Gbits/s GOL OTIS 1 2 3 4 5 6 7 8 9 10 11 12 Module 32 bits GOL OTIS L 1 Buffer Pre. Proc for L 1 Trigger L 1 Buffering and zero suppression DAQ <15 MB/s Module 32 bits OTIS optical link GOL Total data volume: • 432 opt links → 36 L 1 boards • total data flow at 40 KHz: 380 MB/s

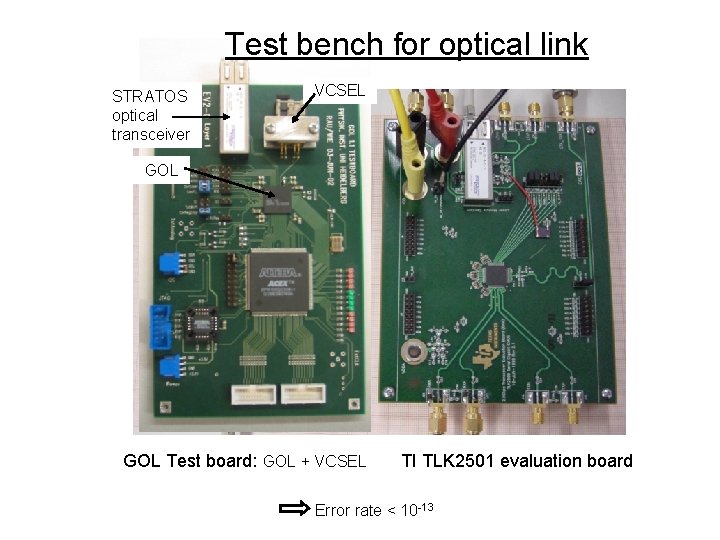

Test bench for optical link STRATOS optical transceiver VCSEL GOL Test board: GOL + VCSEL TI TLK 2501 evaluation board Error rate < 10 -13

L 1 Buffer Board: Memory to accommodate L 1 latency t c je Outer Tracker on m C om o r p V I , o l e O , T T

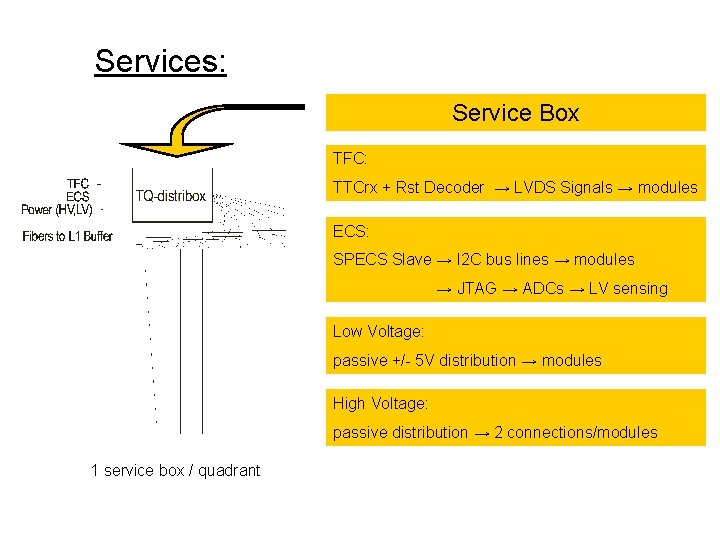

Services: Service Box TFC: TTCrx + Rst Decoder → LVDS Signals → modules ECS: SPECS Slave → I 2 C bus lines → modules → JTAG → ADCs → LV sensing Low Voltage: passive +/- 5 V distribution → modules High Voltage: passive distribution → 2 connections/modules 1 service box / quadrant

Outer Tracker Electronics: Time Schedule 2003 2004 2005 07/03 Validation of OTIS baseline 10/03 Delivery of OTIS 1. 1 03/04 Start pre-series production 06/04 Pre-series finished: start mounting 01/05 Delivery of OTIS 1. 2 03/05 Start Mass Prod

- Slides: 19